1111 / 10101010

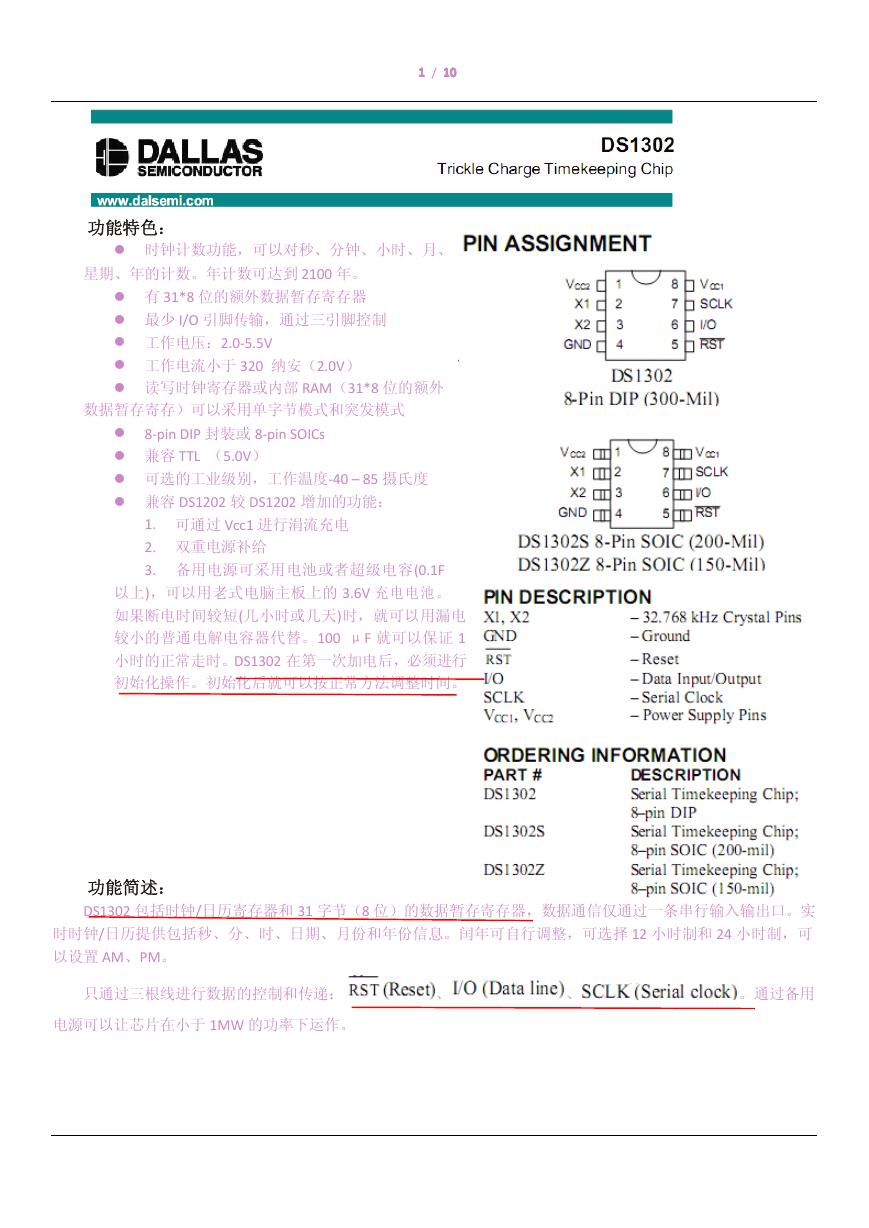

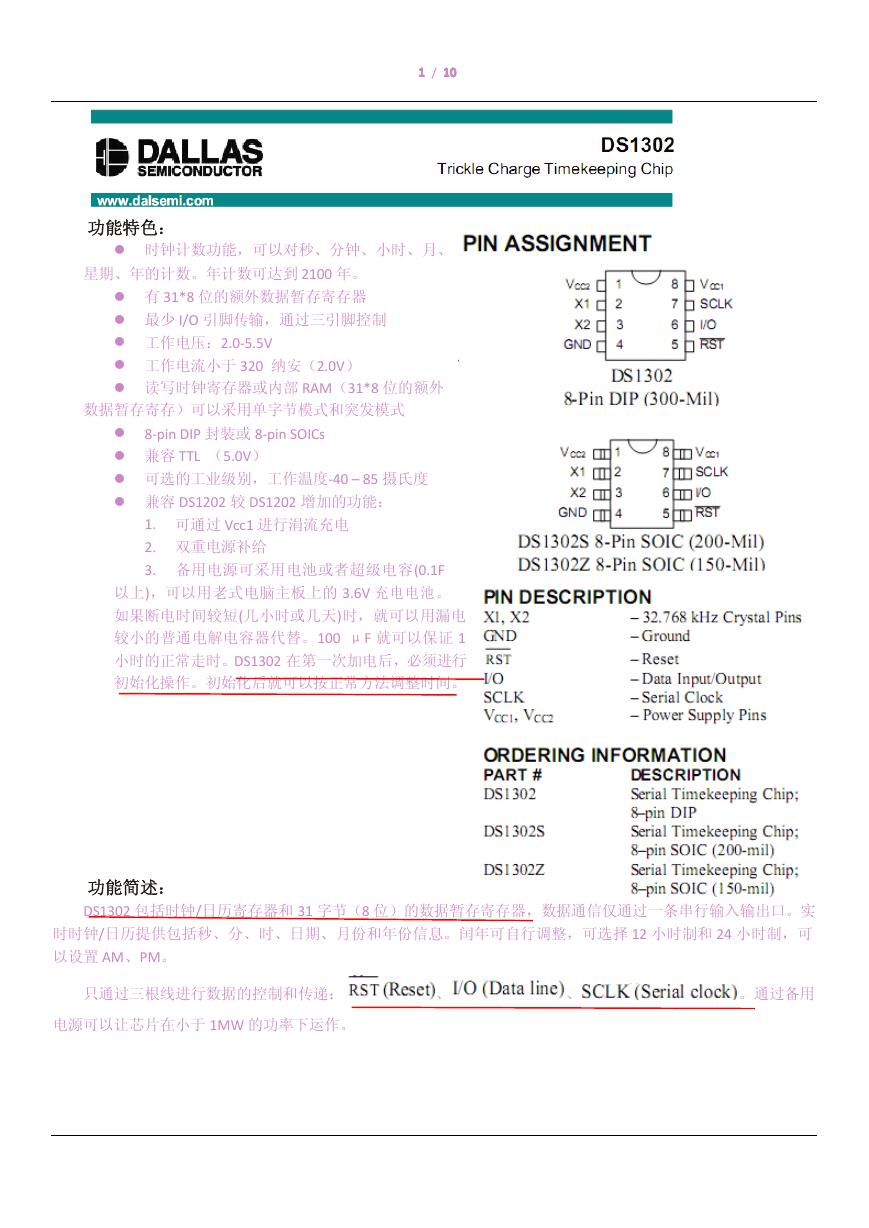

功能特色:

� 时钟计数功能,可以对秒、分钟、小时、月、

星期、年的计数。年计数可达到 2100 年。

� 有 31*8 位的额外数据暂存寄存器

� 最少 I/O 引脚传输,通过三引脚控制

� 工作电压:2.0-5.5V

� 工作电流小于 320 纳安(2.0V)

� 读写时钟寄存器或内部 RAM(31*8 位的额外

数据暂存寄存)可以采用单字节模式和突发模式

� 8-pin DIP 封装或 8-pin SOICs

� 兼容 TTL (5.0V)

� 可选的工业级别,工作温度-40 – 85 摄氏度

� 兼容 DS1202 较 DS1202 增加的功能:

1. 可通过 Vcc1 进行涓流充电

2. 双重电源补给

3. 备用电源可采用电池或者超级电容(0.1F

以上),可以用老式电脑主板上的 3.6V 充电电 池。

如果断电时间较短(几小时或几天)时,就可以用漏电

较小的普通电解电容器代替。100 μF 就可以保证 1

小时的正常走时。DS1302 在第一次加电后,必须进行

初始化操作。初始化后就可以按正常方法调整时间。

功能简述:

DS1302 包括时钟/日历寄存器和 31 字节(8 位)的数据暂存寄存器,数据通信仅通过一条串行输入输出口。实

时时钟/日历提供包括秒、分、时、日期、月份和年份信息。闰年可自行调整,可选择 12 小时制和 24 小时制,可

以设置 AM、PM。

只通过三根线进行数据的控制和传递:

、

、

。通过备用

电源可以让芯片在小于 1MW 的功率下运作。

�

2222 / 10101010

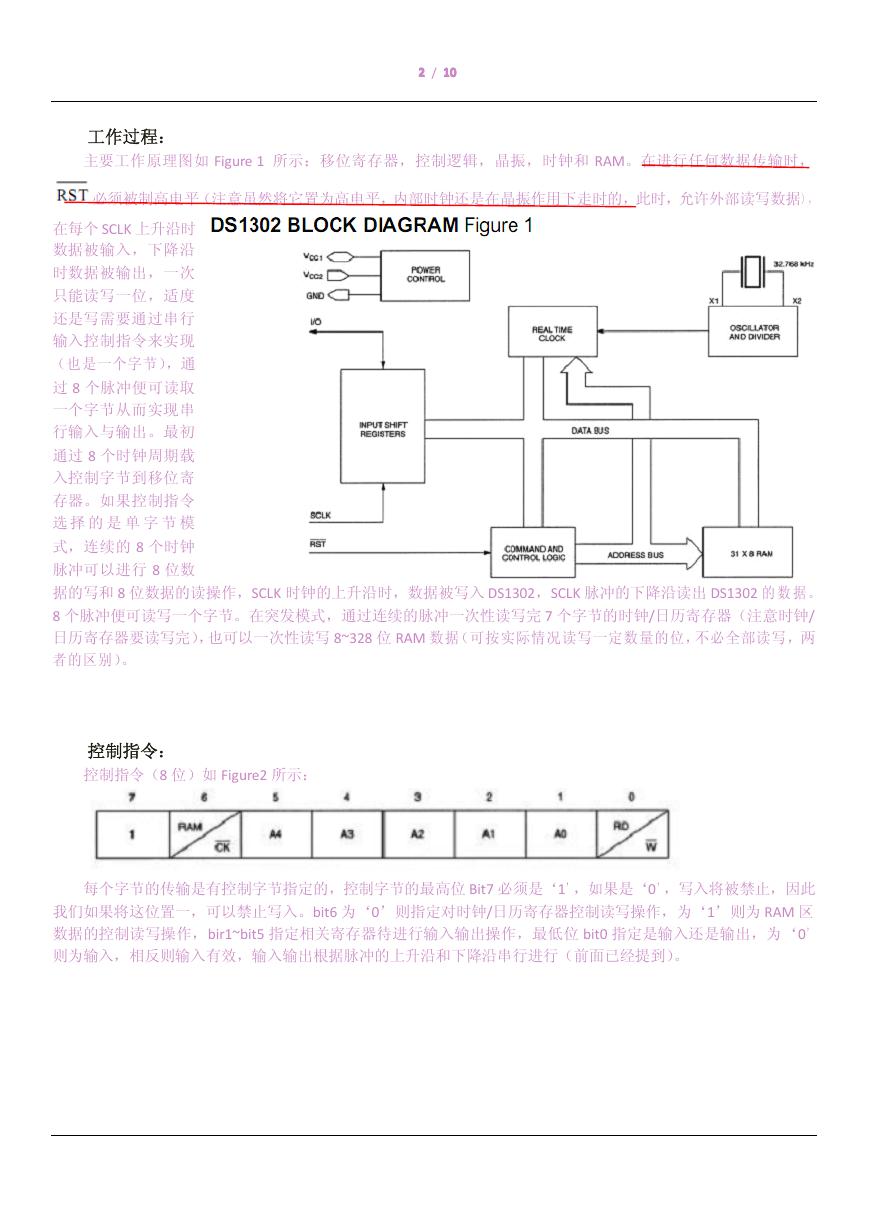

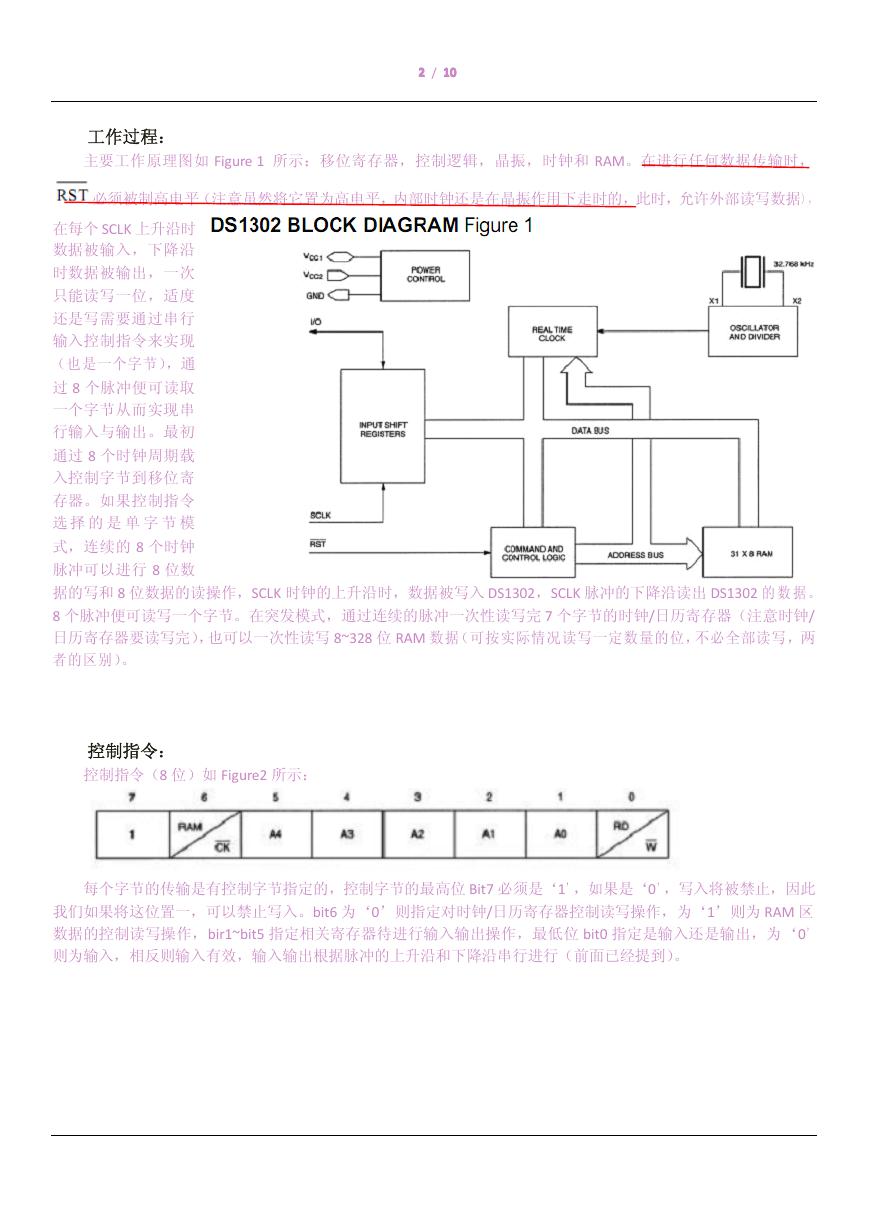

工作过程:

主要工作原理图如 Figure 1 所示:移位寄存器,控制逻辑,晶振,时钟和 RAM。在进行任何数据传输时,

必须被制高电平(注意虽然将它置为高电平,内部时钟还是在晶振作用下走时的,此时,允许外部读写数据),

在每个 SCLK 上升沿时

数据被输入,下降沿

时数据被输出,一次

只能读写一位,适度

还是写需要通过串行

输入控制指令来实现

(也是一个字节),通

过 8 个脉冲便可读取

一个字节从而实现串

行输入与输出。最初

通过 8 个时钟周期载

入控制字节到移位寄

存器。如果控制指令

选 择 的 是 单 字 节 模

式,连续的 8 个时钟

脉冲可以进行 8 位数

据的写和 8 位数据的读操作,SCLK 时钟的上升沿时,数据被写入 DS1302,SCLK 脉冲的下降沿读出 DS1302 的 数 据。

8 个脉冲便可读写一个字节。在突发模式,通过连续的脉冲一次性读写完 7 个字节的时钟/日历寄存器(注意时钟/

日历寄存器要读写完),也可以一次性读写 8~328 位 RAM 数据(可按实际情况读写一定数量的位,不必全部读写,两

者的区别)。

控制指令:

控制指令(8 位)如 Figure2 所示:

每个字节的传输是有控制字节指定的,控制字节的最高位 Bit7 必须是‘1’,如果是‘0’,写入将被禁止,因此

我们如果将这位置一,可以禁止写入。bit6 为‘0’则指定对时钟/日历寄存器控制读写操作,为‘1’则为 RAM 区

数据的控制读写操作,bir1~bit5 指定相关寄存器待进行输入输出操作,最低位 bit0 指定是输入还是输出,为‘0’

则为输入,相反则输入有效,输入输出根据脉冲的上升沿和下降沿串行进行(前面已经提到)。

�

3333 / 10101010

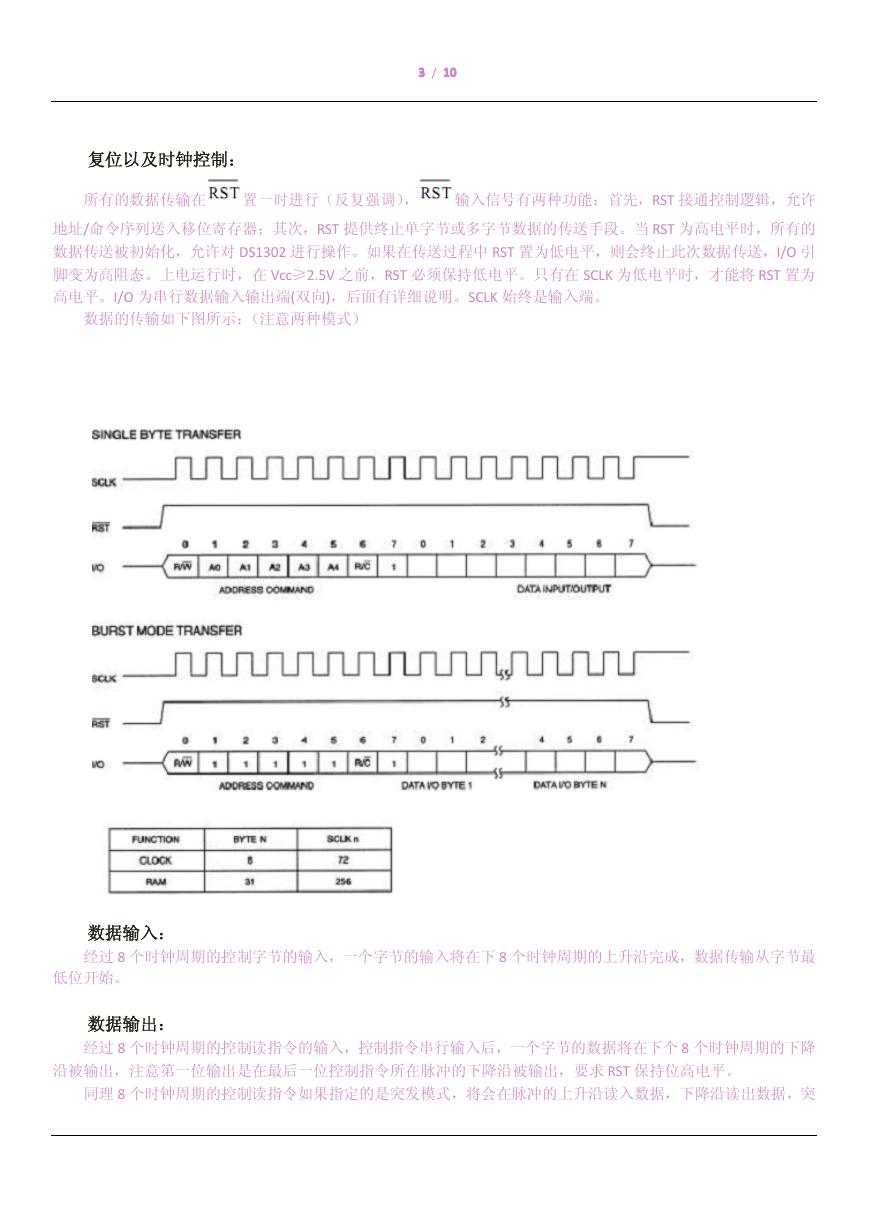

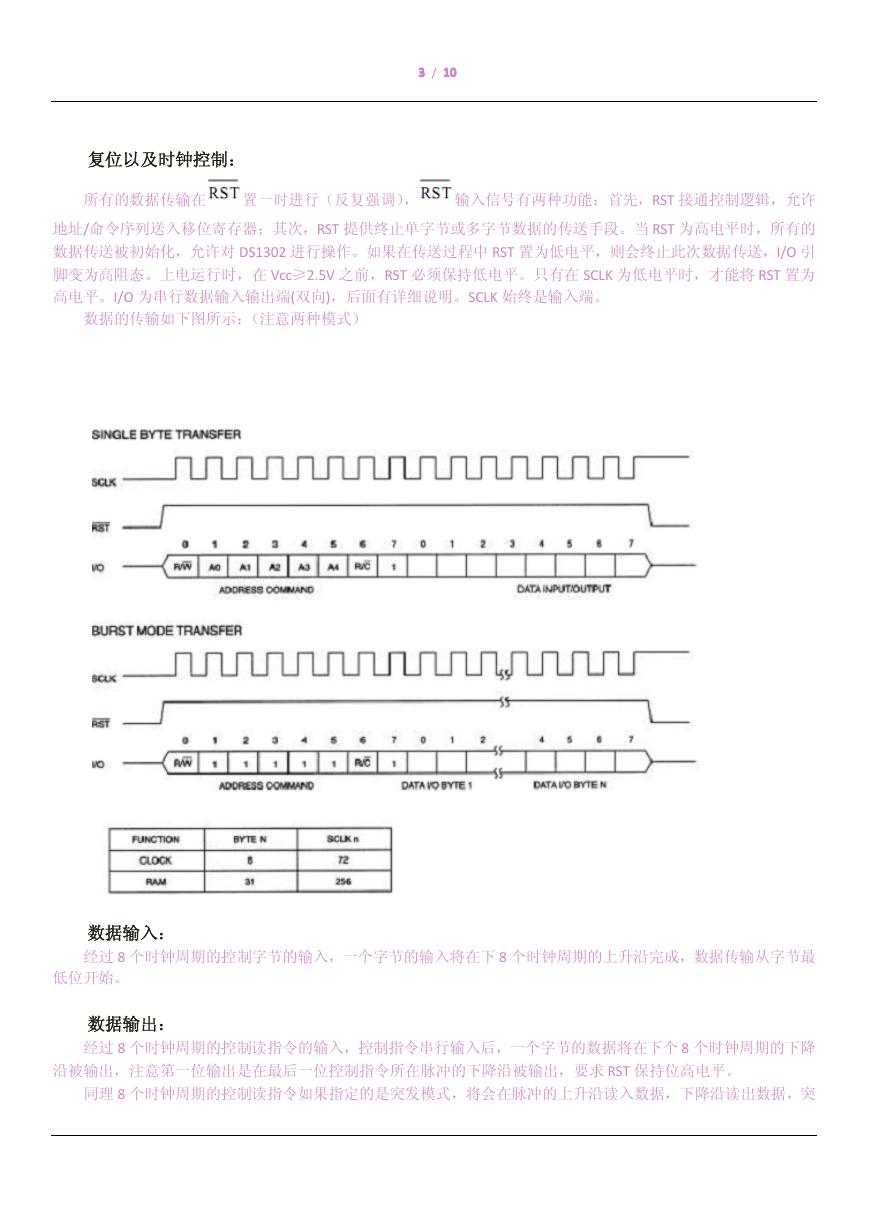

复位以及时钟控制:

所有的数据传输在

置一时进行(反复强调),

输入信号有两种功能:首先,RST 接通控制逻辑,允许

地址/命令序列送入移位寄存器;其次,RST 提供终止单字节或多字节数据的传送手段。当 RST 为高电平时,所有的

数据传送被初始化,允许对 DS1302 进行操作。如果在传送过程中 RST 置为低电平,则会终止此次数据传送,I/O 引

脚变为高阻态。上电运行时,在 Vcc≥2.5V 之前,RST 必须保持低电平。只有在 SCLK 为低电平时,才能将 RST 置为

高电平。I/O 为串行数据输入输出端(双向),后面有详细说明。SCLK 始终是输入端。

数据的传输如下图所示:(注意两种模式)

数据输入:

经过 8 个时钟周期的控制字节的输入,一个字节的输入将在下 8 个时钟周期的上升沿完成,数据传输从字节最

低位开始。

数据输出:

经过 8 个时钟周期的控制读指令的输入,控制指令串行输入后,一个字节的数据将在下个 8 个时钟周期的下降

沿被输出,注意第一位输出是在最后一位控制指令所在脉冲的下降沿被输出,要求 RST 保持位高电平。

同理 8 个时钟周期的控制读指令如果指定的是突发模式,将会在脉冲的上升沿读入数据,下降沿读出数据,突

�

4444 / 10101010

发模式一次可进行多字节数据的一次性读写,只要控制好脉冲就行了。

突发模式:

上面已经提到过的突发模式可以指定为任何时钟/日历或 RAM 的寄存器,与以前一样,位 6 指定时钟或 RAM,

位 0 指定读或写。读取或写入的突发模式开始在位 0 地址 0 。

对于 DS1202 来说,在突发模式下写时钟寄存器,起始的 8 个寄存器用来写入相关数据,必须写完。然而,在

突发模式下写 RAM 数据时,没有必要全部写完。每个字节都将被写入而不论 31 字节是否写完。

时钟////日历:

时钟/日历包含在 7 个寄存器中 ,如 Figure4 所示。数据在时钟/日历寄存器是二进制编码的十进制格式(BCD 码 )。

时钟停止标志:

�

5555 / 10101010

秒寄存器的 bit7 是时钟停止标志位,如果这位是‘1’,时钟晶振停止起振,DS1302 进入低功耗待命模式,耗

用电流小于 100 nanoamps,如果这位是‘0’,晶振开始起振。

AM-PM/12-24

AM-PM/12-24

AM-PM/12-24

AM-PM/12-24 模式选择:

小时寄存器的 bit7 是 AM-PM/12-24 模式选择选择位,这一位为‘1’时,选择了 12 小时制,为‘0’时,选择

了 24 小时制,在 12 小时制下,bit 为‘1’选择了 PM,在 24 小时制下,bit5 选择了 20~23 小时段。

写保护位:

控制字节的 bit7 是写保护位(前面已经提到),低 7 位(bit0~bit6),被置 0,在任何写操作前,bit7 都应该置

‘0’。

涓流充电寄存器:

该寄存器决定了 DS1302 的充电特性,结构简图如下图所示,涓流充电选择位为 bit4~7,置 1010 时使涓流充电 ,

其他选择将禁止涓流充电。DS1302 刚上电时无涓流充电。二极管选择位 diode select(DS)bit2~3,将在 Vcc1 和 Vcc2

之间选择 1 或 2 个 diode ,如果 DS 是 01,只有一个二极管被选择,如果 DS 四 10,将选择两个 diode,具体电路如

下面图示,如果是 00 或 11,无涓流充电能力。还有电阻选择位 RS(bit0~1)将会选择 Vcc1 和 Vcc2 之间的电阻,具体

如下表:

RS 和 DS 是有外部 Vcc1 和 Vcc2(如超级电容,第一页已经提到)最大充电电流来决定的,其最大充电电流由一

下方法计算:例如 Vcc2 电压为 5V,Vcc1 连接一个超级电容,假如涓流充电禁止,且 VCC1、VCC2 之间只有一个二

极管和一个电阻 R1,则其最大电流为:

�

6666 / 10101010

显然,超级电容充电时,VCC1、VCC2 之间的压降将会减少,其充电电流也将会减少。

时钟////日历突发模式:

由时钟/日历指令字节来指定其突发模式操作。在该模式下,其实的 8 个时钟/日历寄存器将被连续的读和写,

详细见前面表格(“时钟/日历”处),起始与地址 0 和位 0。

如果些保护位被置‘1’,则在突发模式下,无任何字节将会被读写,涓流充电不可以在突发模式下选择。

RAMRAMRAMRAM:

The static RAM is 31 x 8 bytes addressed consecutively in the RAM address space.

RAMRAMRAMRAM 突发模式:

由 RAM 控制指令字节来指定其突发模式操作。在该模式下,31 个 RAM 静态寄存器将可以被连续的读或写,起

始与地址 0 和位 0.

寄存器概况:

详细见前面表格(“时钟/日历”处)

晶体振荡器的选择:

一个 32.768KHZ 的晶振可以直接接在 DS1302 的 2、3 管脚之间,可以设定规定载荷电容位 6pF。

电源控制:

VCC1 可提供单电源控制也可以用来作为备用电源,VCC2 为主电源。在主电源关闭的情况下,也能保持时钟的

连续运行。DS1302 由 Vcc1 或 Vcc2 两者中的较大者供电。当 Vcc2 大于 Vcc1+0.2V 时,Vcc2 给 DS1302 供电。当 Vcc2

小于 Vcc1 时,DS1302 由 Vcc1 供电。

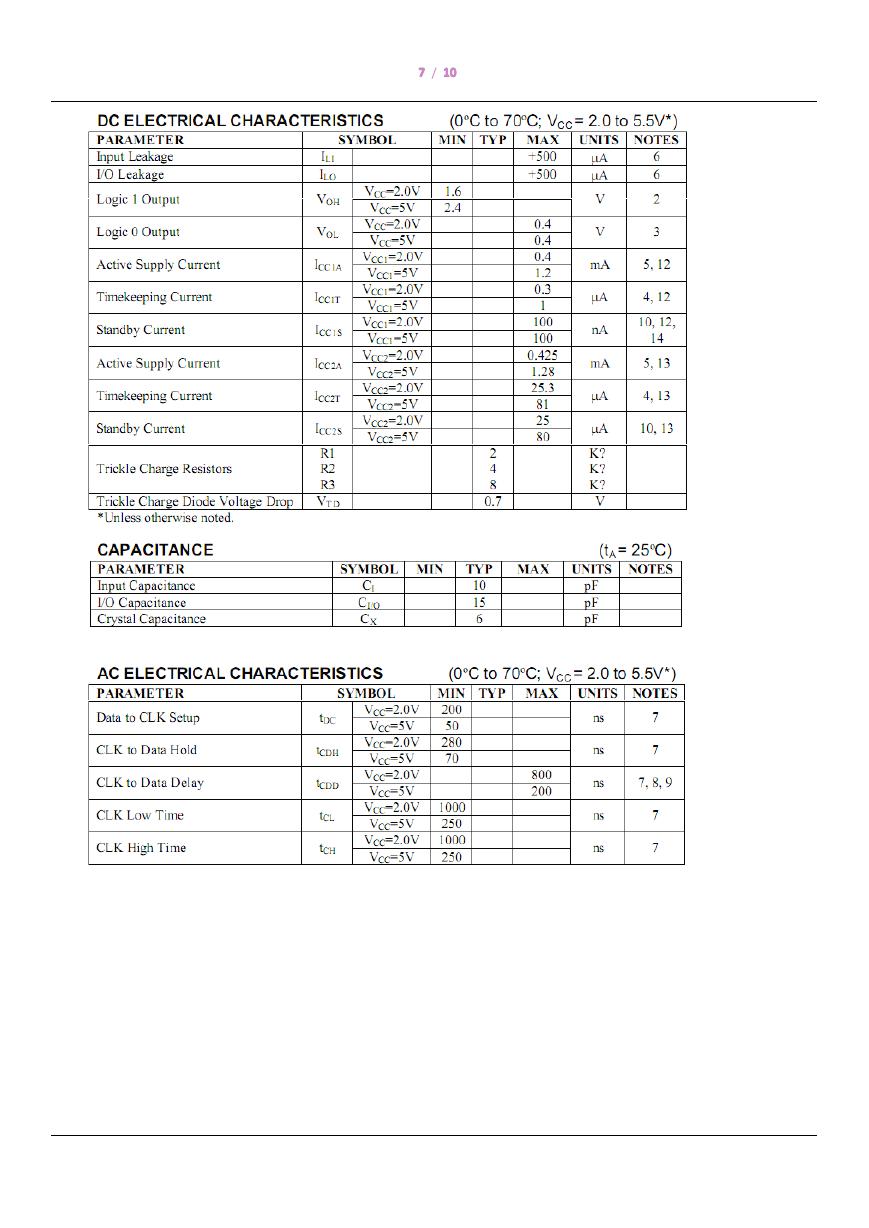

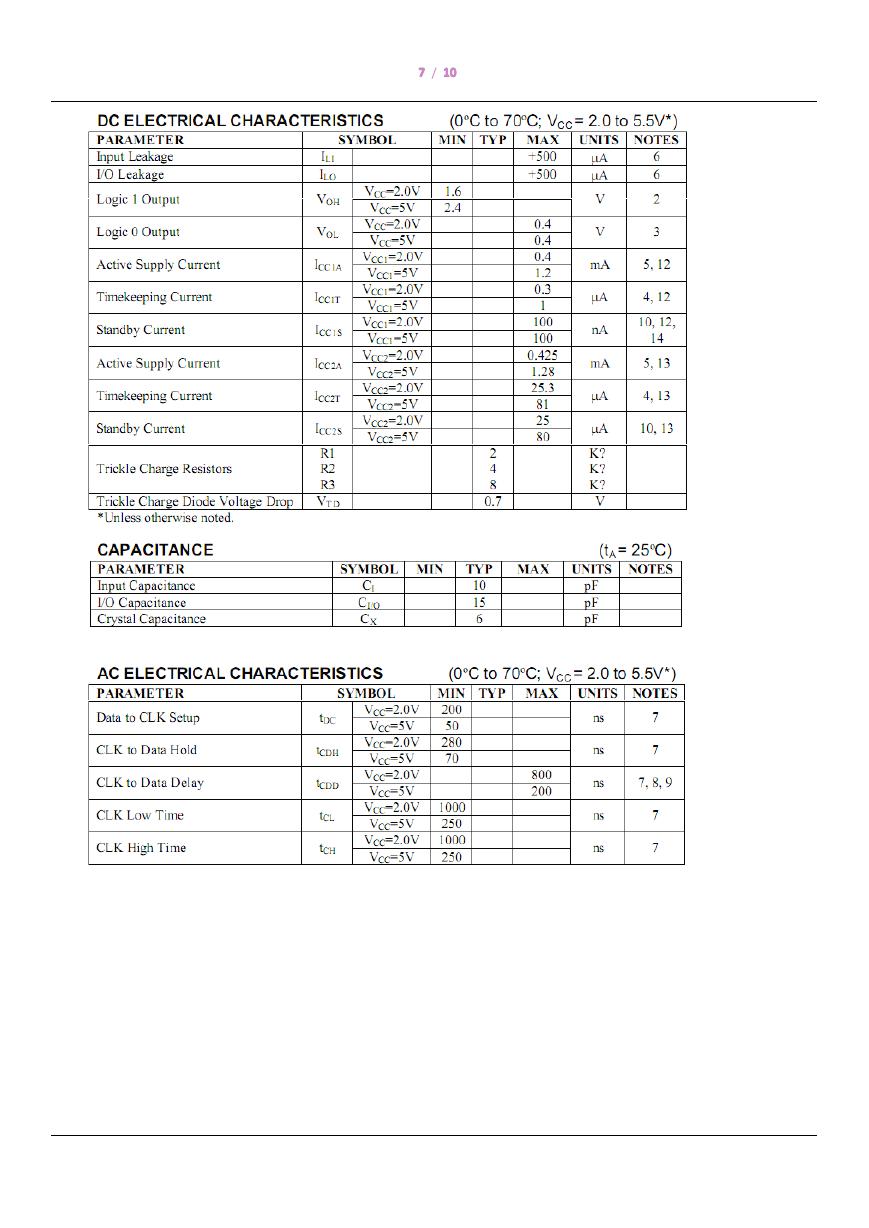

最大绝对额定值:

管脚电压(相对于 GND)

工作温度

存储温度

焊接温度

-0.5V ~ 7.5 V

0°C ~ 70°C

–55°C ~ 125°C

260°C for 10 seconds

�

7777 / 10101010

�

8888 / 10101010

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf