CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

EZ-USB FX2LP™ USB Microcontroller

— Programmable waveform descriptors and configu-

ration registers to define waveforms

— Supports multiple Ready (RDY) inputs and Control

(CTL) outputs

• Integrated, industry-standard enhanced 8051

— 48-MHz, 24-MHz, or 12-MHz CPU operation

— Four clocks per instruction cycle

— Two USARTS

— Three counter/timers

— Expanded interrupt system

— Two data pointers

• 3.3V operation with 5V tolerant inputs

• Vectored USB interrupts and GPIF/FIFO interrupts

• Separate data buffers for the Set-up and Data portions

of a CONTROL transfer

• Integrated I2C controller, runs at 100 or 400 kHz

• Four integrated FIFOs

— Integrated glue logic and FIFOs lower system cost

— Automatic conversion to and from 16-bit buses

— Master or slave operation

— Uses external clock or asynchronous strobes

— Easy interface to ASIC and DSP ICs

• Available in Commercial and Industrial temperature

grade (all packages except VFBGA)

Features (CY7C68013A/14A/15A/16A)

1.0

• USB 2.0–USB-IF high speed certified (TID # 40440111)

• Single-chip integrated USB 2.0 transceiver, smart SIE,

and enhanced 8051 microprocessor

• Fit, form and function compatible with the FX2

— Pin-compatible

— Object-code-compatible

— Functionally-compatible (FX2LP is a superset)

• Ultra Low power: ICC no more than 85 mA in any mode

— Ideal for bus and battery powered applications

• Software: 8051 code runs from:

— Internal RAM, which is downloaded via USB

— Internal RAM, which is loaded from EEPROM

— External memory device (128 pin package)

• 16 KBytes of on-chip Code/Data RAM

• Four programmable BULK/INTERRUPT/ISOCHRO-

NOUS endpoints

— Buffering options: double, triple, and quad

• Additional programmable (BULK/INTERRUPT) 64-byte

endpoint

• 8- or 16-bit external data interface

• Smart Media Standard ECC generation

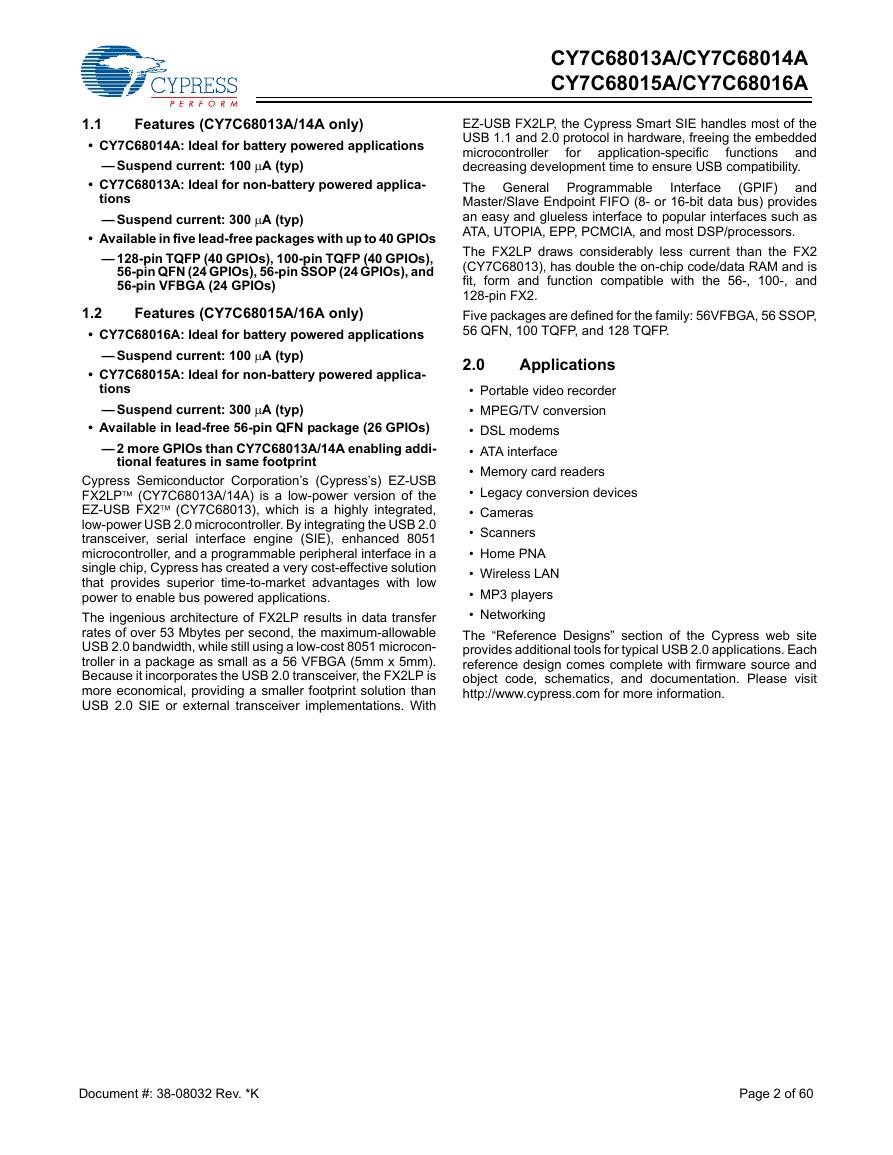

• GPIF (General Programmable Interface)

— Allows direct connection to most parallel interface

24 MHz

Ext. XTAL

High-performance micro

using standard tools

with lower-power options

FX2LP

VCC

x20

PLL

/0.5

/1.0

/2.0

1.5k

connected for

full speed

D+

D–

USB

2.0

XCVR

Integrated

full- and high-speed

XCVR

CY

Smart

USB

1.1/2.0

Engine

)

6

1

(

s

s

e

r

d

d

A

)

8

(

t

a

a

D

8051 Core

12/24/48 MHz,

four clocks/cycle

)

8

(

s

u

B

a

a

D

t

I2C

Master

Additional I/Os (24)

/

)

6

1

(

s

s

e

r

d

d

A

ECC

GPIF

ADDR (9)

RDY (6)

CTL (6)

16 KB

RAM

Abundant I/O

including two USARTS

General

programmable I/F

to ASIC/DSP or bus

standards such as

ATAPI, EPP, etc.

4 kB

FIFO

8/16

Up to 96 MBytes/s

burst rate

Enhanced USB core

Simplifies 8051 code

“Soft Configuration”

Easy firmware changes

FIFO and endpoint memory

(master or slave operation)

Figure 1-1. Block Diagram

Cypress Semiconductor Corporation

Document #: 38-08032 Rev. *K

•

198 Champion Court

•

San Jose, CA 95134-1709

•

408-943-2600

Revised January 26, 2006

�

Features (CY7C68013A/14A only)

1.1

• CY7C68014A: Ideal for battery powered applications

— Suspend current: 100 µA (typ)

• CY7C68013A: Ideal for non-battery powered applica-

tions

— Suspend current: 300 µA (typ)

• Available in five lead-free packages with up to 40 GPIOs

— 128-pin TQFP (40 GPIOs), 100-pin TQFP (40 GPIOs),

56-pin QFN (24 GPIOs), 56-pin SSOP (24 GPIOs), and

56-pin VFBGA (24 GPIOs)

Features (CY7C68015A/16A only)

1.2

• CY7C68016A: Ideal for battery powered applications

— Suspend current: 100 µA (typ)

• CY7C68015A: Ideal for non-battery powered applica-

tions

— Suspend current: 300 µA (typ)

• Available in lead-free 56-pin QFN package (26 GPIOs)

— 2 more GPIOs than CY7C68013A/14A enabling addi-

tional features in same footprint

Cypress Semiconductor Corporation’s (Cypress’s) EZ-USB

FX2LP™ (CY7C68013A/14A) is a low-power version of the

EZ-USB FX2™ (CY7C68013), which is a highly integrated,

low-power USB 2.0 microcontroller. By integrating the USB 2.0

transceiver, serial interface engine (SIE), enhanced 8051

microcontroller, and a programmable peripheral interface in a

single chip, Cypress has created a very cost-effective solution

that provides superior time-to-market advantages with low

power to enable bus powered applications.

The ingenious architecture of FX2LP results in data transfer

rates of over 53 Mbytes per second, the maximum-allowable

USB 2.0 bandwidth, while still using a low-cost 8051 microcon-

troller in a package as small as a 56 VFBGA (5mm x 5mm).

Because it incorporates the USB 2.0 transceiver, the FX2LP is

more economical, providing a smaller footprint solution than

USB 2.0 SIE or external transceiver implementations. With

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Interface

for application-specific

EZ-USB FX2LP, the Cypress Smart SIE handles most of the

USB 1.1 and 2.0 protocol in hardware, freeing the embedded

microcontroller

functions and

decreasing development time to ensure USB compatibility.

(GPIF) and

The General Programmable

Master/Slave Endpoint FIFO (8- or 16-bit data bus) provides

an easy and glueless interface to popular interfaces such as

ATA, UTOPIA, EPP, PCMCIA, and most DSP/processors.

The FX2LP draws considerably less current than the FX2

(CY7C68013), has double the on-chip code/data RAM and is

fit, form and function compatible with the 56-, 100-, and

128-pin FX2.

Five packages are defined for the family: 56VFBGA, 56 SSOP,

56 QFN, 100 TQFP, and 128 TQFP.

2.0

Applications

• Portable video recorder

• MPEG/TV conversion

• DSL modems

• ATA interface

• Memory card readers

• Legacy conversion devices

• Cameras

• Scanners

• Home PNA

• Wireless LAN

• MP3 players

• Networking

The “Reference Designs” section of the Cypress web site

provides additional tools for typical USB 2.0 applications. Each

reference design comes complete with firmware source and

object code, schematics, and documentation. Please visit

http://www.cypress.com for more information.

Document #: 38-08032 Rev. *K

Page 2 of 60

�

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

The CLKOUT pin, which can be three-stated and inverted

using internal control bits, outputs the 50% duty cycle 8051

clock, at the selected 8051 clock frequency—48, 24, or 12

MHz.

USARTS

3.2.2

FX2LP contains two standard 8051 USARTs, addressed via

Special Function Register (SFR) bits. The USART interface

pins are available on separate I/O pins, and are not multi-

plexed with port pins.

UART0 and UART1 can operate using an internal clock at

230 KBaud with no more than 1% baud rate error. 230-KBaud

operation is achieved by an internally derived clock source that

generates overflow pulses at the appropriate time. The

internal clock adjusts for the 8051 clock rate (48, 24, 12 MHz)

such that it always presents the correct frequency for

230-KBaud operation.[1]

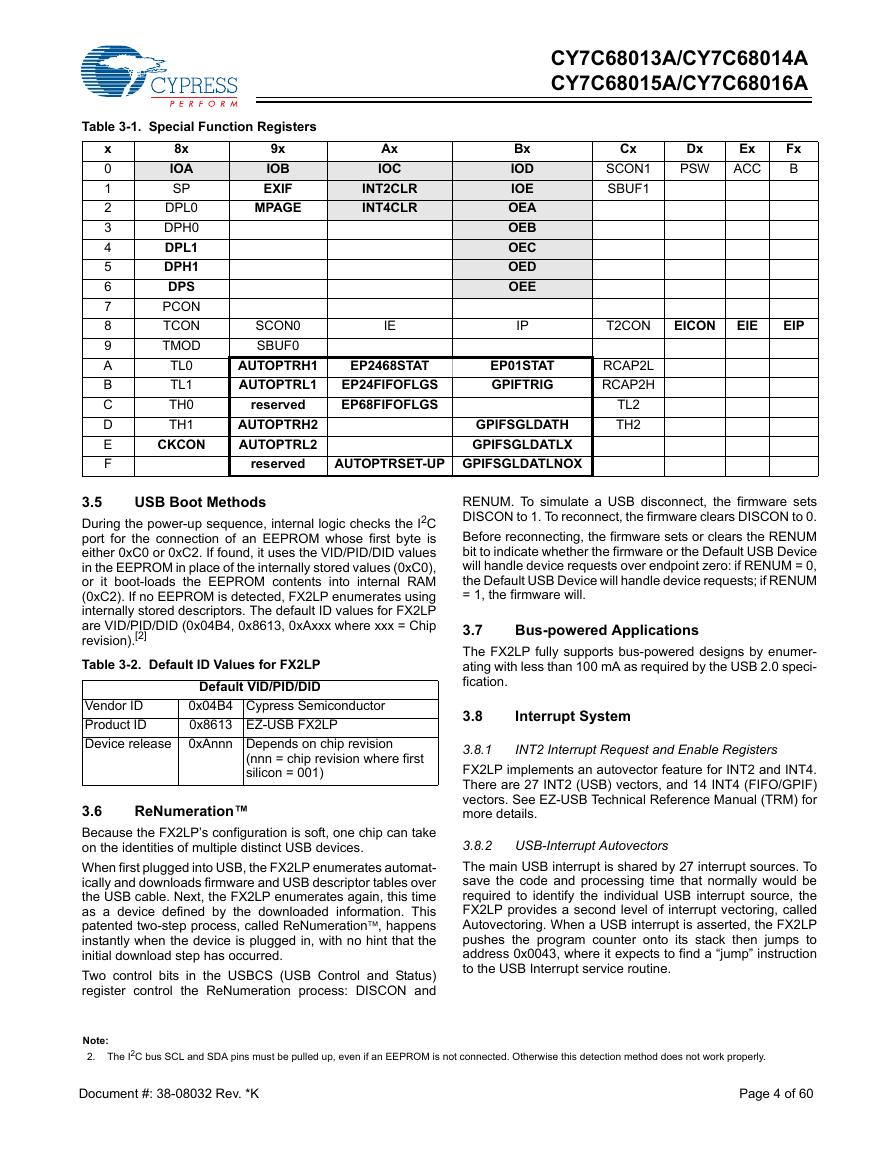

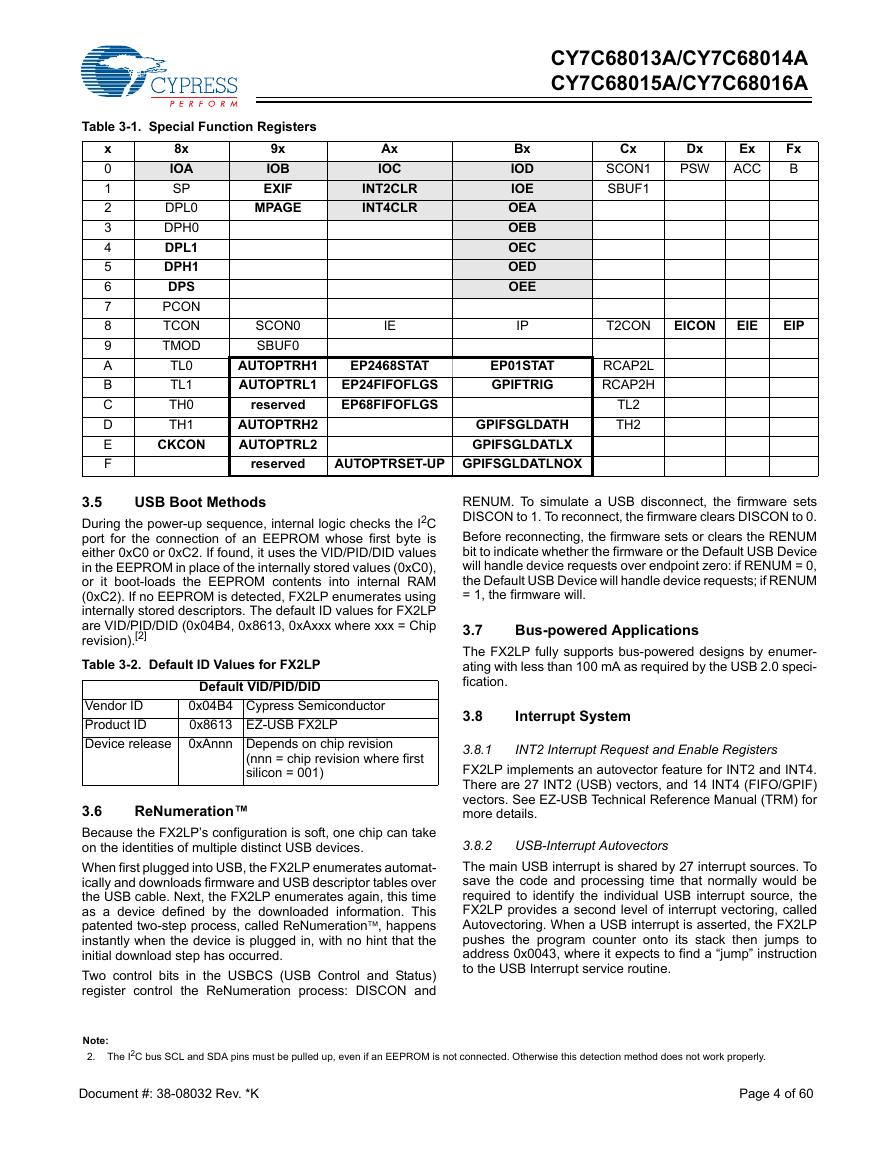

Special Function Registers

3.2.3

Certain 8051 SFR addresses are populated to provide fast

access to critical FX2LP functions. These SFR additions are

shown in Table 3-1. Bold type indicates non-standard,

enhanced 8051 registers. The two SFR rows that end with “0”

and “8” contain bit-addressable registers. The four I/O ports

A–D use the SFR addresses used in the standard 8051 for

ports 0–3, which are not implemented in FX2LP. Because of

the faster and more efficient SFR addressing, the FX2LP I/O

ports are not addressable in external RAM space (using the

MOVX instruction).

I2C Bus

3.3

FX2LP supports the I2C bus as a master only at 100-/400-KHz.

SCL and SDA pins have open-drain outputs and hysteresis

inputs. These signals must be pulled up to 3.3V, even if no I2C

device is connected.

Buses

3.4

All packages: 8- or 16-bit “FIFO” bidirectional data bus, multi-

plexed on I/O ports B and D. 128-pin package: adds 16-bit

output-only 8051 address bus, 8-bit bidirectional data bus.

3.0

Functional Overview

USB Signaling Speed

3.1

FX2LP operates at two of the three rates defined in the USB

Specification Revision 2.0, dated April 27, 2000:

• Full speed, with a signaling bit rate of 12 Mbps

• High speed, with a signaling bit rate of 480 Mbps.

FX2LP does not support the low-speed signaling mode of

1.5 Mbps.

8051 Microprocessor

3.2

The 8051 microprocessor embedded in the FX2LP family has

256 bytes of register RAM, an expanded interrupt system,

three timer/counters, and two USARTs.

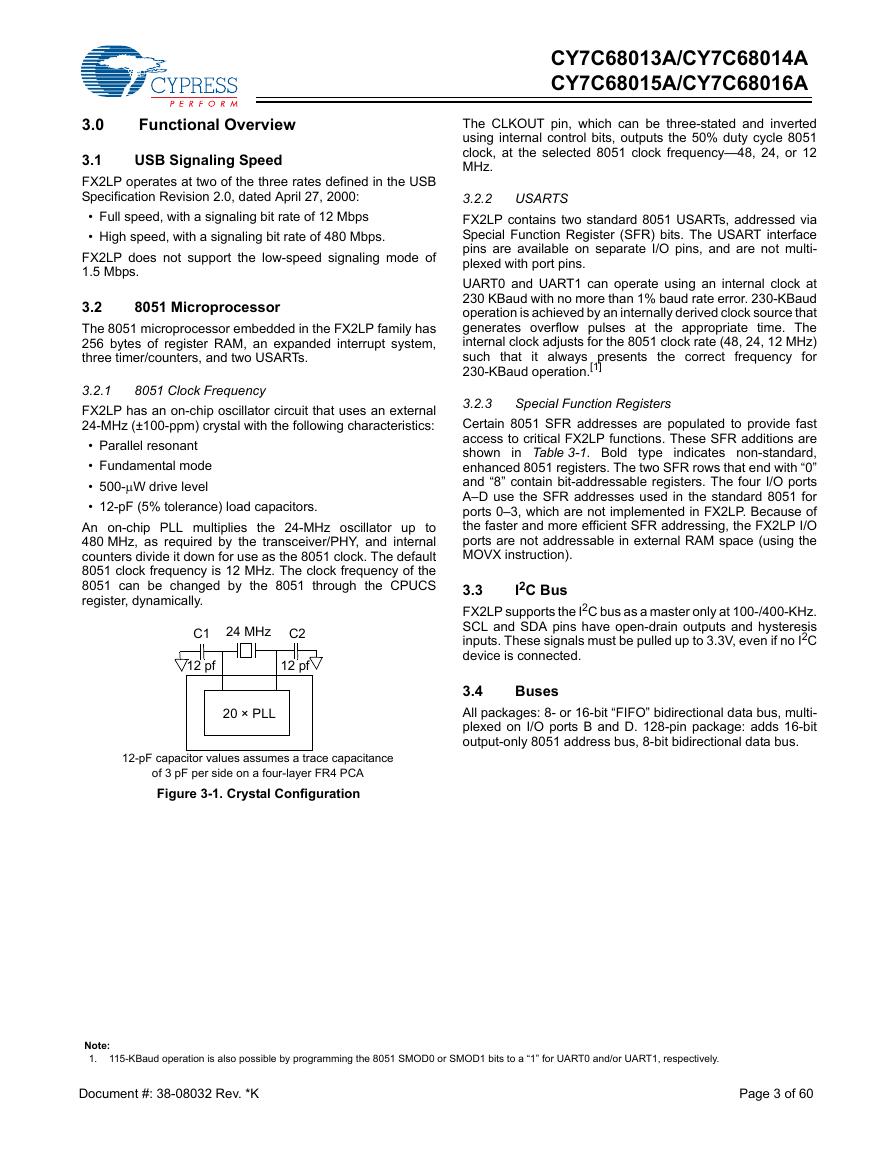

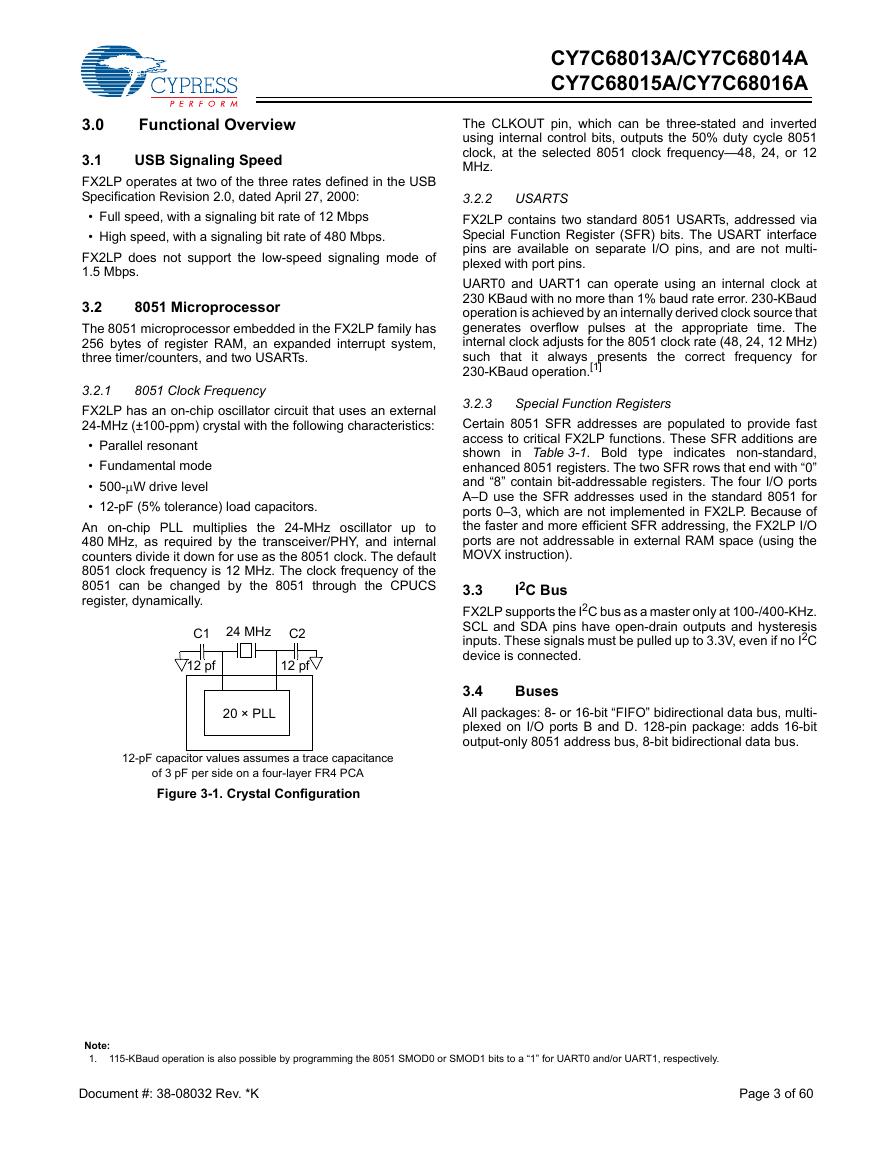

8051 Clock Frequency

3.2.1

FX2LP has an on-chip oscillator circuit that uses an external

24-MHz (±100-ppm) crystal with the following characteristics:

• Parallel resonant

• Fundamental mode

• 500-µW drive level

• 12-pF (5% tolerance) load capacitors.

An on-chip PLL multiplies the 24-MHz oscillator up to

480 MHz, as required by the transceiver/PHY, and internal

counters divide it down for use as the 8051 clock. The default

8051 clock frequency is 12 MHz. The clock frequency of the

8051 can be changed by the 8051 through the CPUCS

register, dynamically.

C1

24 MHz

C2

12 pf

12 pf

20 × PLL

12-pF capacitor values assumes a trace capacitance

of 3 pF per side on a four-layer FR4 PCA

Figure 3-1. Crystal Configuration

Note:

1.

115-KBaud operation is also possible by programming the 8051 SMOD0 or SMOD1 bits to a “1” for UART0 and/or UART1, respectively.

Document #: 38-08032 Rev. *K

Page 3 of 60

�

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Table 3-1. Special Function Registers

8x

IOA

SP

DPL0

DPH0

DPL1

DPH1

DPS

PCON

TCON

TMOD

TL0

TL1

TH0

TH1

CKCON

x

0

1

2

3

4

5

6

7

8

9

A

B

C

D

E

F

9x

IOB

EXIF

MPAGE

Ax

IOC

INT2CLR

INT4CLR

IE

EP2468STAT

EP24FIFOFLGS

EP68FIFOFLGS

SCON0

SBUF0

AUTOPTRH1

AUTOPTRL1

reserved

AUTOPTRH2

AUTOPTRL2

Bx

IOD

IOE

OEA

OEB

OEC

OED

OEE

IP

Cx

SCON1

SBUF1

Dx

Ex

PSW ACC

Fx

B

T2CON

EICON

EIE

EIP

EP01STAT

GPIFTRIG

GPIFSGLDATH

GPIFSGLDATLX

RCAP2L

RCAP2H

TL2

TH2

reserved

AUTOPTRSET-UP GPIFSGLDATLNOX

USB Boot Methods

3.5

During the power-up sequence, internal logic checks the I2C

port for the connection of an EEPROM whose first byte is

either 0xC0 or 0xC2. If found, it uses the VID/PID/DID values

in the EEPROM in place of the internally stored values (0xC0),

or it boot-loads the EEPROM contents into internal RAM

(0xC2). If no EEPROM is detected, FX2LP enumerates using

internally stored descriptors. The default ID values for FX2LP

are VID/PID/DID (0x04B4, 0x8613, 0xAxxx where xxx = Chip

revision).[2]

Table 3-2. Default ID Values for FX2LP

Default VID/PID/DID

Vendor ID

Product ID

Device release

0x04B4 Cypress Semiconductor

0x8613 EZ-USB FX2LP

0xAnnn Depends on chip revision

(nnn = chip revision where first

silicon = 001)

ReNumeration™

3.6

Because the FX2LP’s configuration is soft, one chip can take

on the identities of multiple distinct USB devices.

When first plugged into USB, the FX2LP enumerates automat-

ically and downloads firmware and USB descriptor tables over

the USB cable. Next, the FX2LP enumerates again, this time

as a device defined by the downloaded information. This

patented two-step process, called ReNumeration™, happens

instantly when the device is plugged in, with no hint that the

initial download step has occurred.

Two control bits in the USBCS (USB Control and Status)

register control the ReNumeration process: DISCON and

RENUM. To simulate a USB disconnect, the firmware sets

DISCON to 1. To reconnect, the firmware clears DISCON to 0.

Before reconnecting, the firmware sets or clears the RENUM

bit to indicate whether the firmware or the Default USB Device

will handle device requests over endpoint zero: if RENUM = 0,

the Default USB Device will handle device requests; if RENUM

= 1, the firmware will.

Bus-powered Applications

3.7

The FX2LP fully supports bus-powered designs by enumer-

ating with less than 100 mA as required by the USB 2.0 speci-

fication.

3.8

Interrupt System

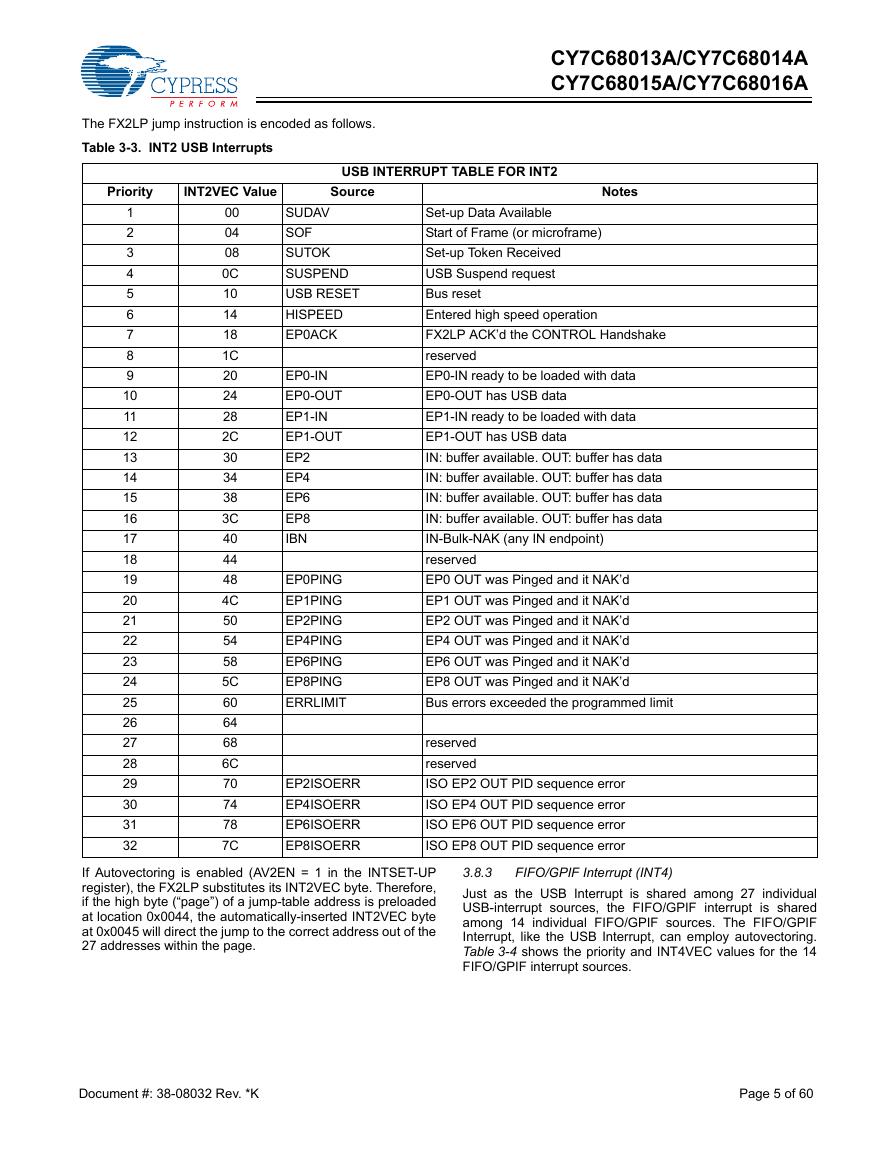

INT2 Interrupt Request and Enable Registers

3.8.1

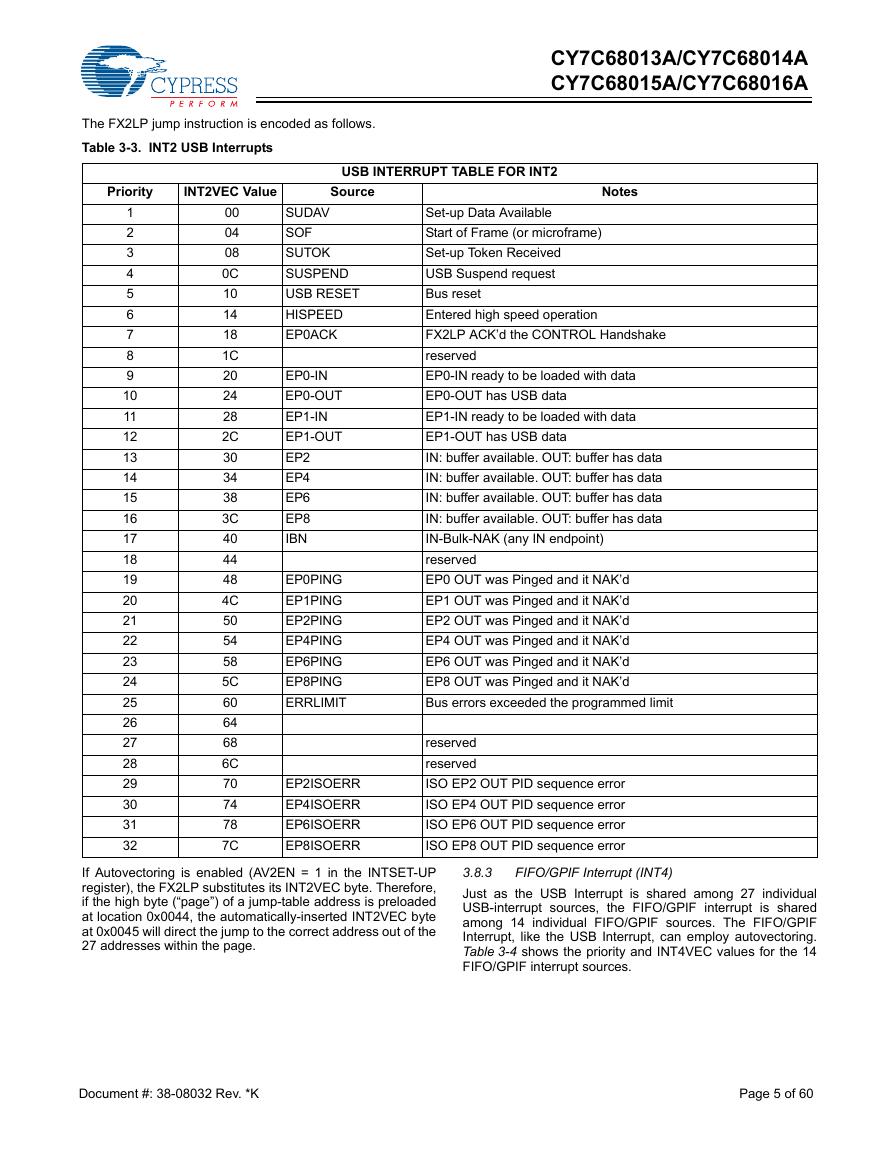

FX2LP implements an autovector feature for INT2 and INT4.

There are 27 INT2 (USB) vectors, and 14 INT4 (FIFO/GPIF)

vectors. See EZ-USB Technical Reference Manual (TRM) for

more details.

USB-Interrupt Autovectors

3.8.2

The main USB interrupt is shared by 27 interrupt sources. To

save the code and processing time that normally would be

required to identify the individual USB interrupt source, the

FX2LP provides a second level of interrupt vectoring, called

Autovectoring. When a USB interrupt is asserted, the FX2LP

pushes the program counter onto its stack then jumps to

address 0x0043, where it expects to find a “jump” instruction

to the USB Interrupt service routine.

Note:

2. The I2C bus SCL and SDA pins must be pulled up, even if an EEPROM is not connected. Otherwise this detection method does not work properly.

Document #: 38-08032 Rev. *K

Page 4 of 60

�

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

The FX2LP jump instruction is encoded as follows.

Table 3-3. INT2 USB Interrupts

Priority

INT2VEC Value

Source

Notes

USB INTERRUPT TABLE FOR INT2

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

00

04

08

0C

10

14

18

1C

20

24

28

2C

30

34

38

3C

40

44

48

4C

50

54

58

5C

60

64

68

6C

70

74

78

7C

SUDAV

SOF

SUTOK

SUSPEND

USB RESET

HISPEED

EP0ACK

EP0-IN

EP0-OUT

EP1-IN

EP1-OUT

EP2

EP4

EP6

EP8

IBN

EP0PING

EP1PING

EP2PING

EP4PING

EP6PING

EP8PING

ERRLIMIT

EP2ISOERR

EP4ISOERR

EP6ISOERR

EP8ISOERR

Set-up Data Available

Start of Frame (or microframe)

Set-up Token Received

USB Suspend request

Bus reset

Entered high speed operation

FX2LP ACK’d the CONTROL Handshake

reserved

EP0-IN ready to be loaded with data

EP0-OUT has USB data

EP1-IN ready to be loaded with data

EP1-OUT has USB data

IN: buffer available. OUT: buffer has data

IN: buffer available. OUT: buffer has data

IN: buffer available. OUT: buffer has data

IN: buffer available. OUT: buffer has data

IN-Bulk-NAK (any IN endpoint)

reserved

EP0 OUT was Pinged and it NAK’d

EP1 OUT was Pinged and it NAK’d

EP2 OUT was Pinged and it NAK’d

EP4 OUT was Pinged and it NAK’d

EP6 OUT was Pinged and it NAK’d

EP8 OUT was Pinged and it NAK’d

Bus errors exceeded the programmed limit

reserved

reserved

ISO EP2 OUT PID sequence error

ISO EP4 OUT PID sequence error

ISO EP6 OUT PID sequence error

ISO EP8 OUT PID sequence error

If Autovectoring is enabled (AV2EN = 1 in the INTSET-UP

register), the FX2LP substitutes its INT2VEC byte. Therefore,

if the high byte (“page”) of a jump-table address is preloaded

at location 0x0044, the automatically-inserted INT2VEC byte

at 0x0045 will direct the jump to the correct address out of the

27 addresses within the page.

FIFO/GPIF Interrupt (INT4)

3.8.3

Just as the USB Interrupt is shared among 27 individual

USB-interrupt sources, the FIFO/GPIF interrupt is shared

among 14 individual FIFO/GPIF sources. The FIFO/GPIF

Interrupt, like the USB Interrupt, can employ autovectoring.

Table 3-4 shows the priority and INT4VEC values for the 14

FIFO/GPIF interrupt sources.

Document #: 38-08032 Rev. *K

Page 5 of 60

�

Priority

INT4VEC Value

Table 3-4. Individual FIFO/GPIF Interrupt Sources

Source

EP2PF

EP4PF

EP6PF

EP8PF

EP2EF

EP4EF

EP6EF

EP8EF

EP2FF

EP4FF

EP6FF

EP8FF

GPIFDONE

GPIFWF

1

2

3

4

5

6

7

8

9

10

11

12

13

14

80

84

88

8C

90

94

98

9C

A0

A4

A8

AC

B0

B4

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Notes

Endpoint 2 Programmable Flag

Endpoint 4 Programmable Flag

Endpoint 6 Programmable Flag

Endpoint 8 Programmable Flag

Endpoint 2 Empty Flag

Endpoint 4 Empty Flag

Endpoint 6 Empty Flag

Endpoint 8 Empty Flag

Endpoint 2 Full Flag

Endpoint 4 Full Flag

Endpoint 6 Full Flag

Endpoint 8 Full Flag

GPIF Operation Complete

GPIF Waveform

If Autovectoring is enabled (AV4EN = 1 in the INTSET-UP

register), the FX 2LP substitutes its INT4VEC byte. Therefore,

if the high byte (“page”) of a jump-table address is preloaded

at location 0x0054, the automatically-inserted INT4VEC byte

at 0x0055 will direct the jump to the correct address out of the

14 addresses within the page. When the ISR occurs, the

FX2LP pushes the program counter onto its stack then jumps

to address 0x0053, where it expects to find a “jump” instruction

to the ISR Interrupt service routine.

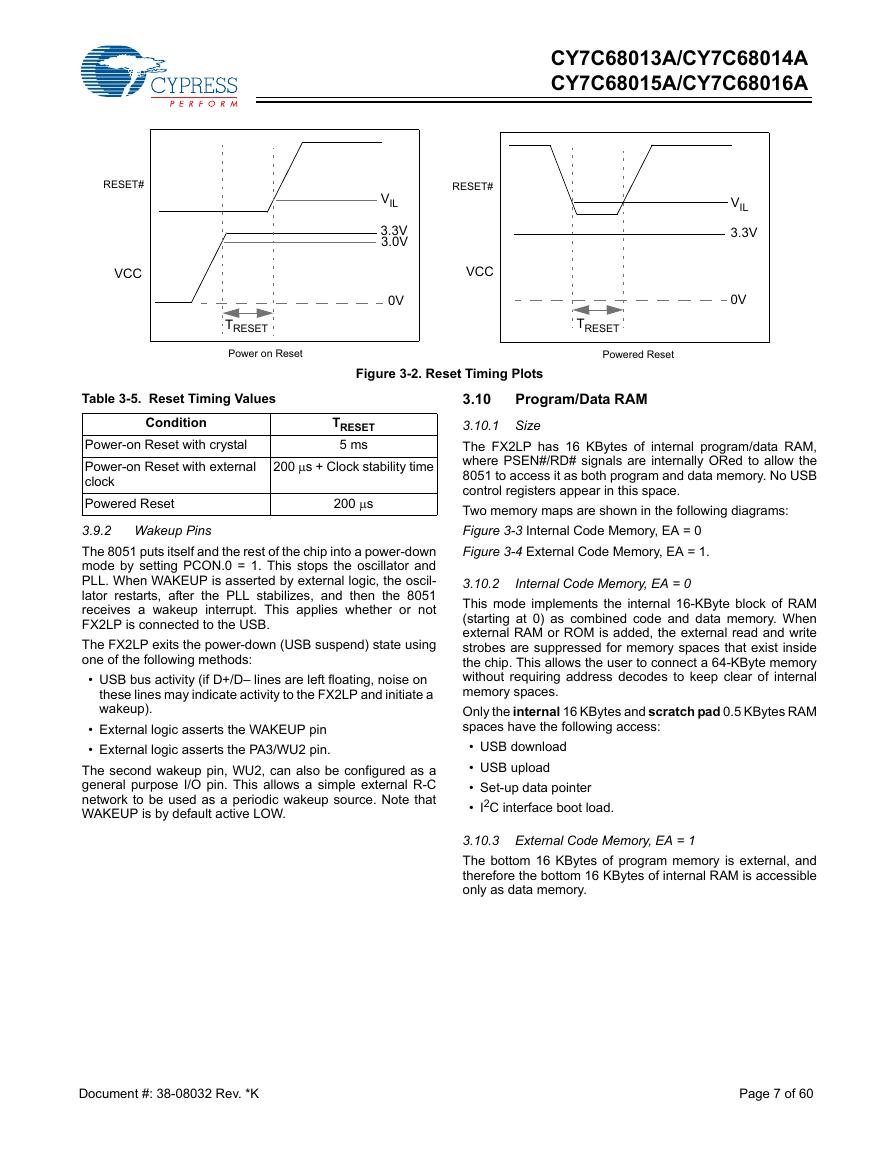

Reset and Wakeup

Reset Pin

3.9

3.9.1

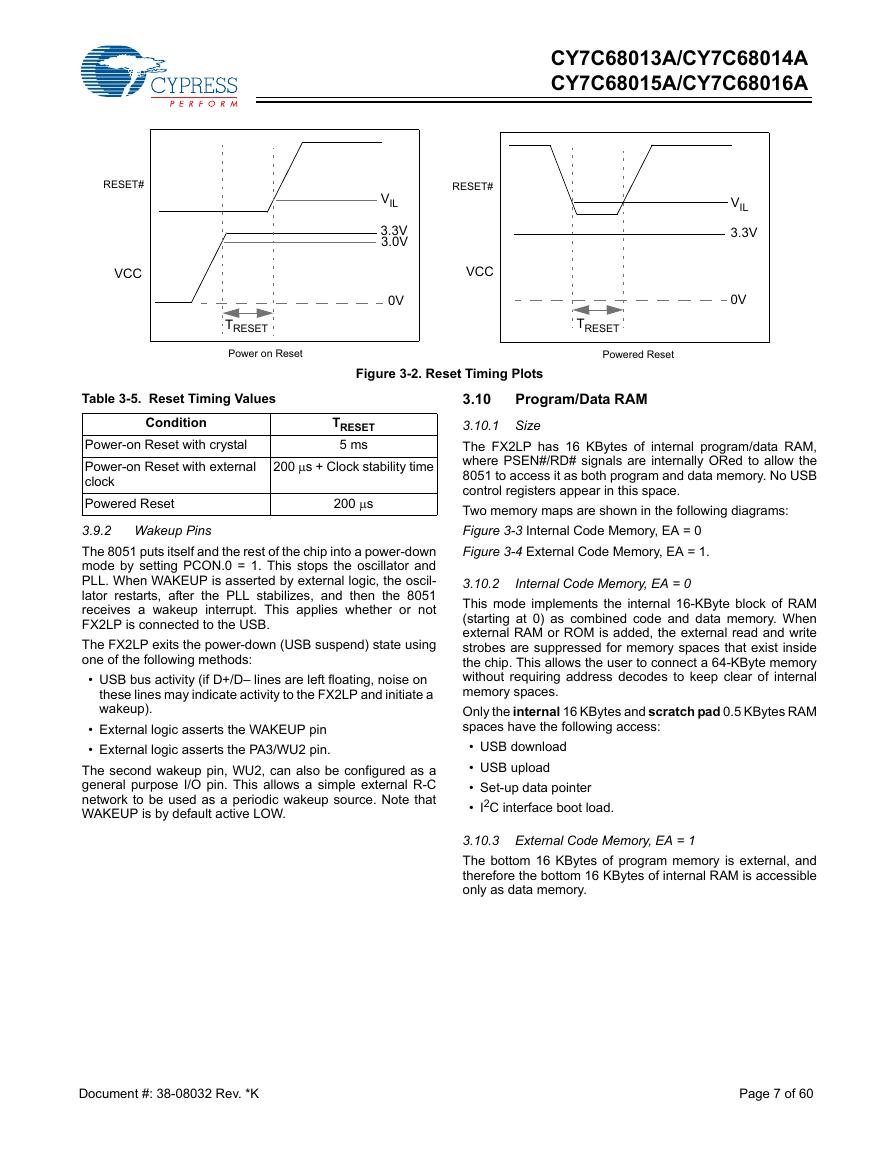

The input pin, RESET#, will reset the FX2LP when asserted.

This pin has hysteresis and is active LOW. When a crystal is

used with the CY7C680xxA the reset period must allow for the

stabilization of the crystal and the PLL. This reset period

should be approximately 5 ms after VCC has reached 3.0V. If

the crystal input pin is driven by a clock signal the internal PLL

stabilizes in 200 µs after VCC has reached 3.0V[3]. Figure 3-2

shows a power-on reset condition and a reset applied during

operation. A power-on reset is defined as the time reset is

asserted while power is being applied to the circuit. A powered

reset is defined to be when the FX2LP has previously been

powered on and operating and the RESET# pin is asserted.

Cypress provides an application note which describes and

recommends power on reset implementation and can be found

on the Cypress web site. For more information on reset imple-

mentation

the

http://www.cypress.com.

family of products visit

the FX2

for

Note:

3.

If the external clock is powered at the same time as the CY7C680xxA and has a stabilization wait period, it must be added to the 200 µs.

Document #: 38-08032 Rev. *K

Page 6 of 60

�

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

RESET#

VCC

RESET#

VCC

VIL

3.3V

3.0V

0V

VIL

3.3V

0V

TRESET

Power on Reset

TRESET

Powered Reset

Figure 3-2. Reset Timing Plots

Table 3-5. Reset Timing Values

Condition

Power-on Reset with crystal

Power-on Reset with external

clock

Powered Reset

TRESET

5 ms

200 µs + Clock stability time

200 µs

3.9.2 Wakeup Pins

The 8051 puts itself and the rest of the chip into a power-down

mode by setting PCON.0 = 1. This stops the oscillator and

PLL. When WAKEUP is asserted by external logic, the oscil-

lator restarts, after the PLL stabilizes, and then the 8051

receives a wakeup interrupt. This applies whether or not

FX2LP is connected to the USB.

The FX2LP exits the power-down (USB suspend) state using

one of the following methods:

• USB bus activity (if D+/D– lines are left floating, noise on

these lines may indicate activity to the FX2LP and initiate a

wakeup).

• External logic asserts the WAKEUP pin

• External logic asserts the PA3/WU2 pin.

The second wakeup pin, WU2, can also be configured as a

general purpose I/O pin. This allows a simple external R-C

network to be used as a periodic wakeup source. Note that

WAKEUP is by default active LOW.

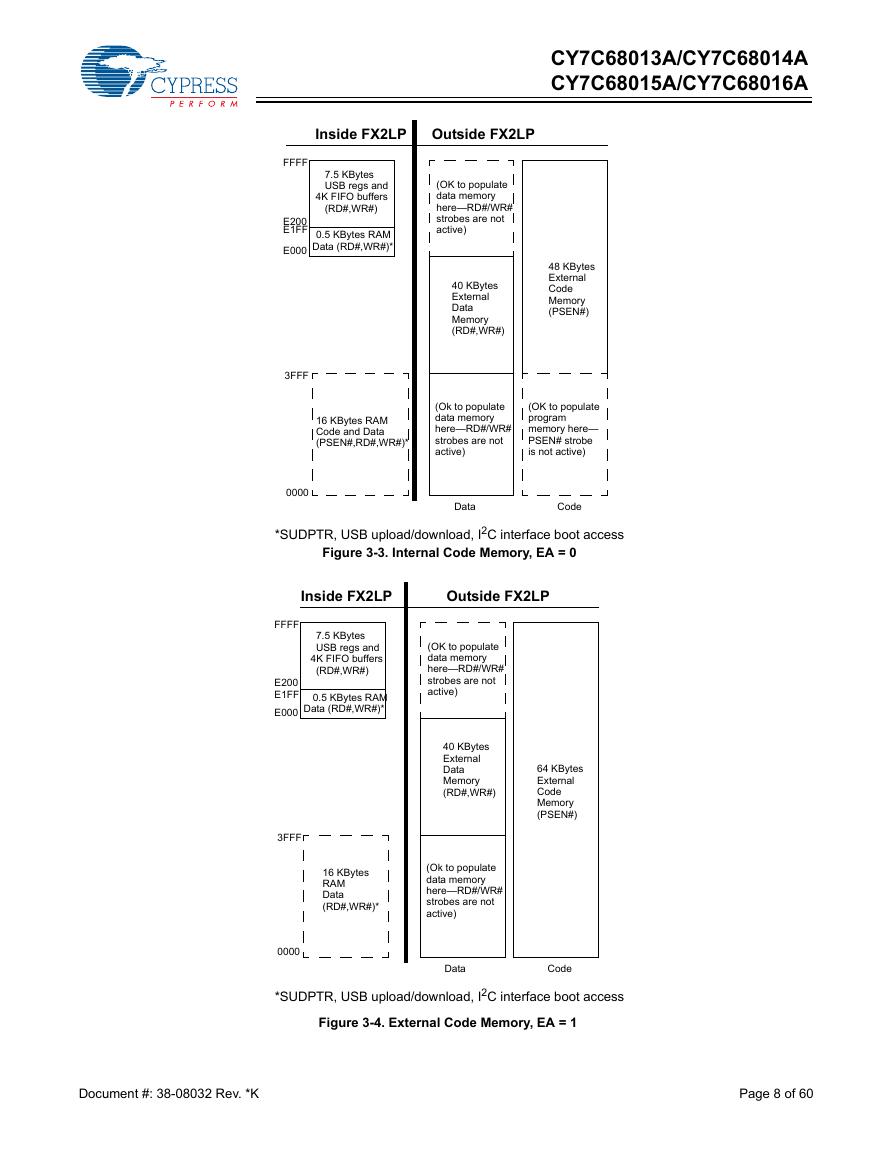

Program/Data RAM

3.10

3.10.1 Size

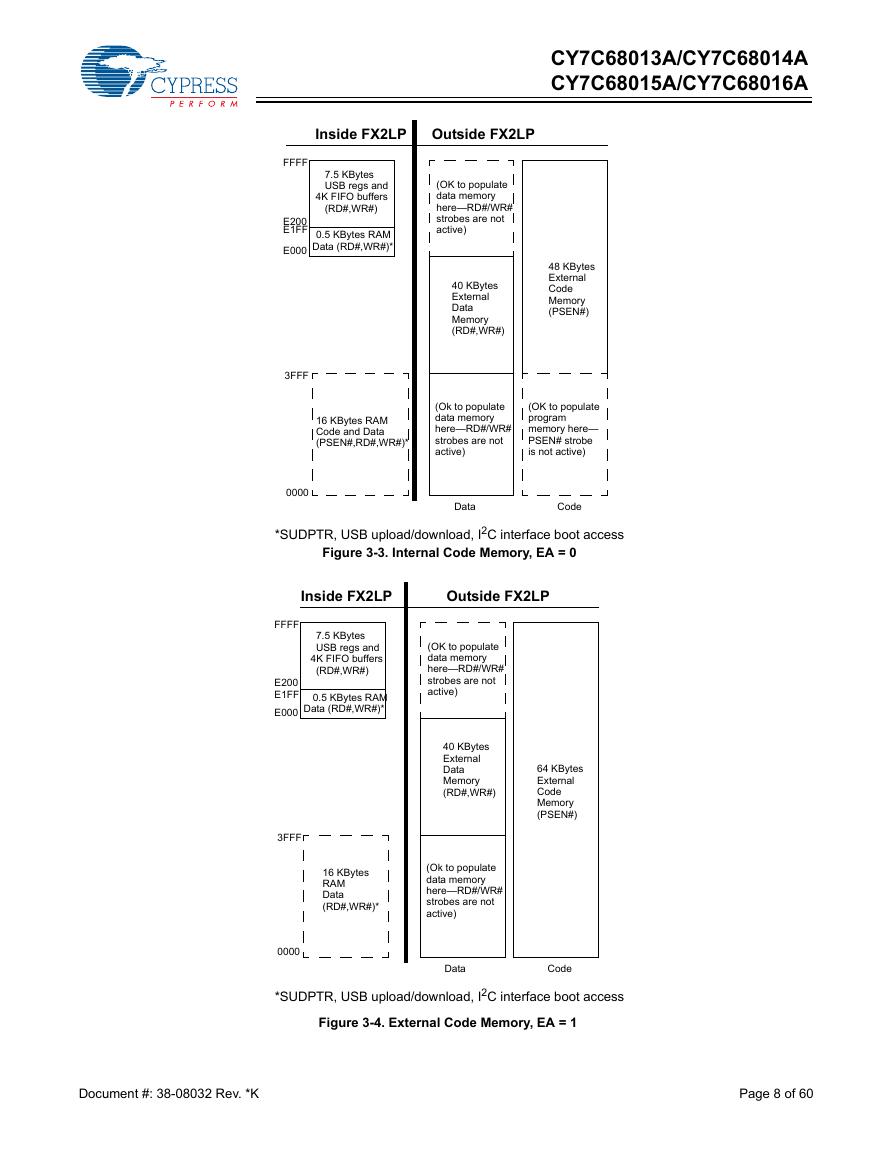

The FX2LP has 16 KBytes of internal program/data RAM,

where PSEN#/RD# signals are internally ORed to allow the

8051 to access it as both program and data memory. No USB

control registers appear in this space.

Two memory maps are shown in the following diagrams:

Figure 3-3 Internal Code Memory, EA = 0

Figure 3-4 External Code Memory, EA = 1.

Internal Code Memory, EA = 0

3.10.2

This mode implements the internal 16-KByte block of RAM

(starting at 0) as combined code and data memory. When

external RAM or ROM is added, the external read and write

strobes are suppressed for memory spaces that exist inside

the chip. This allows the user to connect a 64-KByte memory

without requiring address decodes to keep clear of internal

memory spaces.

Only the internal 16 KBytes and scratch pad 0.5 KBytes RAM

spaces have the following access:

• USB download

• USB upload

• Set-up data pointer

• I2C interface boot load.

3.10.3 External Code Memory, EA = 1

The bottom 16 KBytes of program memory is external, and

therefore the bottom 16 KBytes of internal RAM is accessible

only as data memory.

Document #: 38-08032 Rev. *K

Page 7 of 60

�

CY7C68013A/CY7C68014A

CY7C68015A/CY7C68016A

Inside FX2LP

Outside FX2LP

FFFF

E200

E1FF

E000

7.5 KBytes

USB regs and

4K FIFO buffers

(RD#,WR#)

0.5 KBytes RAM

Data (RD#,WR#)*

(OK to populate

data memory

here—RD#/WR#

strobes are not

active)

40 KBytes

External

Data

Memory

(RD#,WR#)

48 KBytes

External

Code

Memory

(PSEN#)

16 KBytes RAM

Code and Data

(PSEN#,RD#,WR#)*

(Ok to populate

data memory

here—RD#/WR#

strobes are not

active)

(OK to populate

program

memory here—

PSEN# strobe

is not active)

3FFF

0000

Data

Code

*SUDPTR, USB upload/download, I2C interface boot access

Figure 3-3. Internal Code Memory, EA = 0

Inside FX2LP

Outside FX2LP

FFFF

E200

E1FF

E000

7.5 KBytes

USB regs and

4K FIFO buffers

(RD#,WR#)

0.5 KBytes RAM

Data (RD#,WR#)*

(OK to populate

data memory

here—RD#/WR#

strobes are not

active)

40 KBytes

External

Data

Memory

(RD#,WR#)

64 KBytes

External

Code

Memory

(PSEN#)

3FFF

0000

16 KBytes

RAM

Data

(RD#,WR#)*

(Ok to populate

data memory

here—RD#/WR#

strobes are not

active)

Data

Code

*SUDPTR, USB upload/download, I2C interface boot access

Figure 3-4. External Code Memory, EA = 1

Document #: 38-08032 Rev. *K

Page 8 of 60

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf TechnicalReference_Dem.pdf

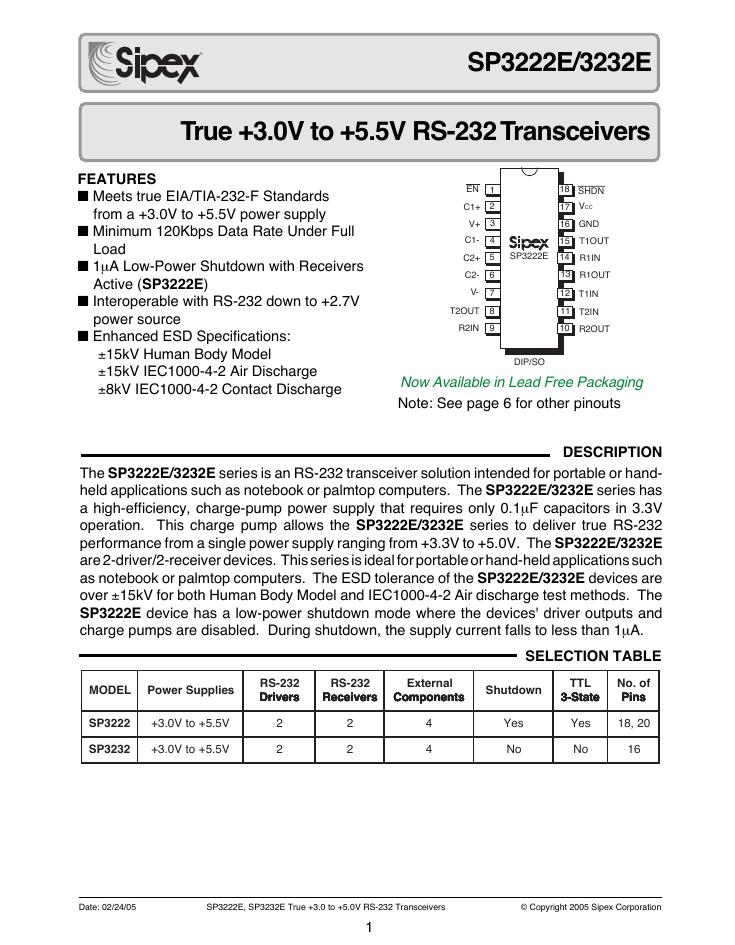

TechnicalReference_Dem.pdf SP3232EEN 手册(SP3232EEN).pdf

SP3232EEN 手册(SP3232EEN).pdf