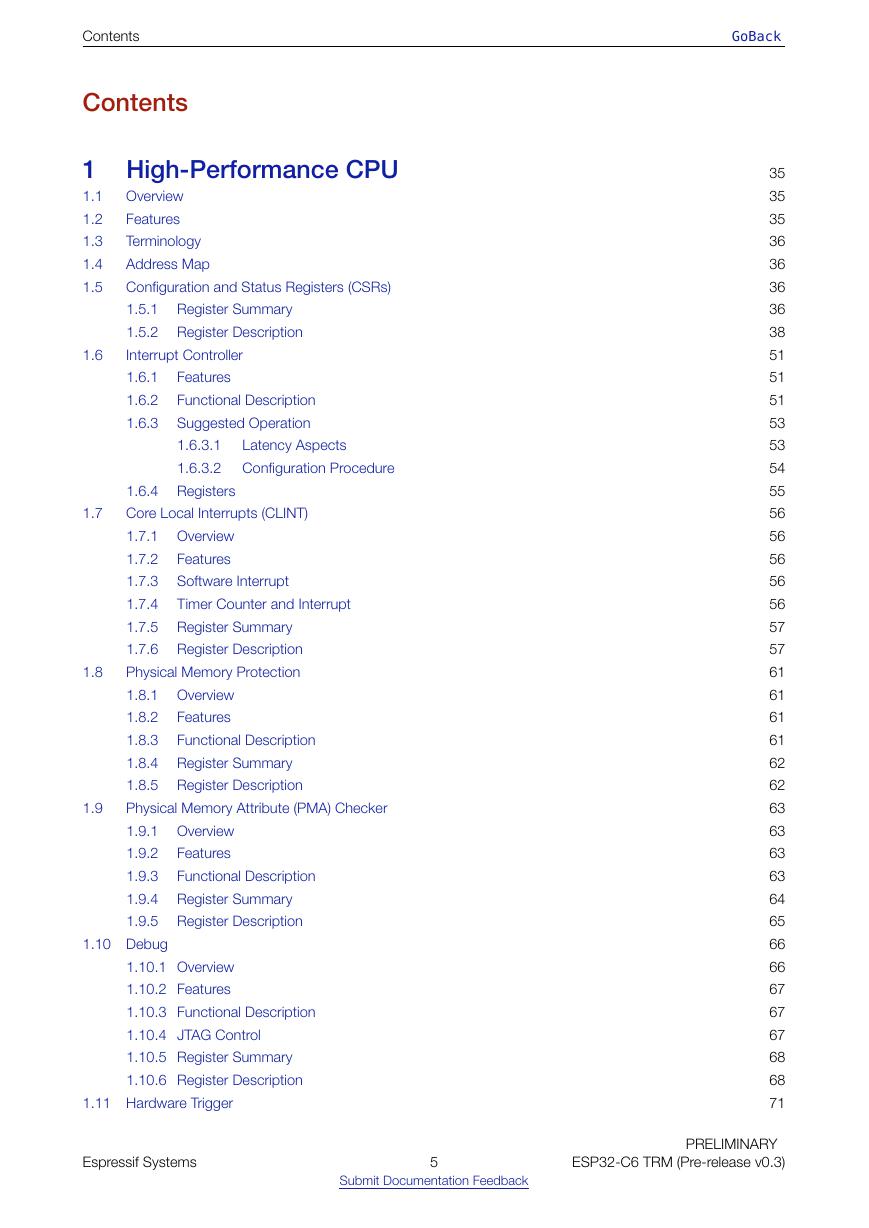

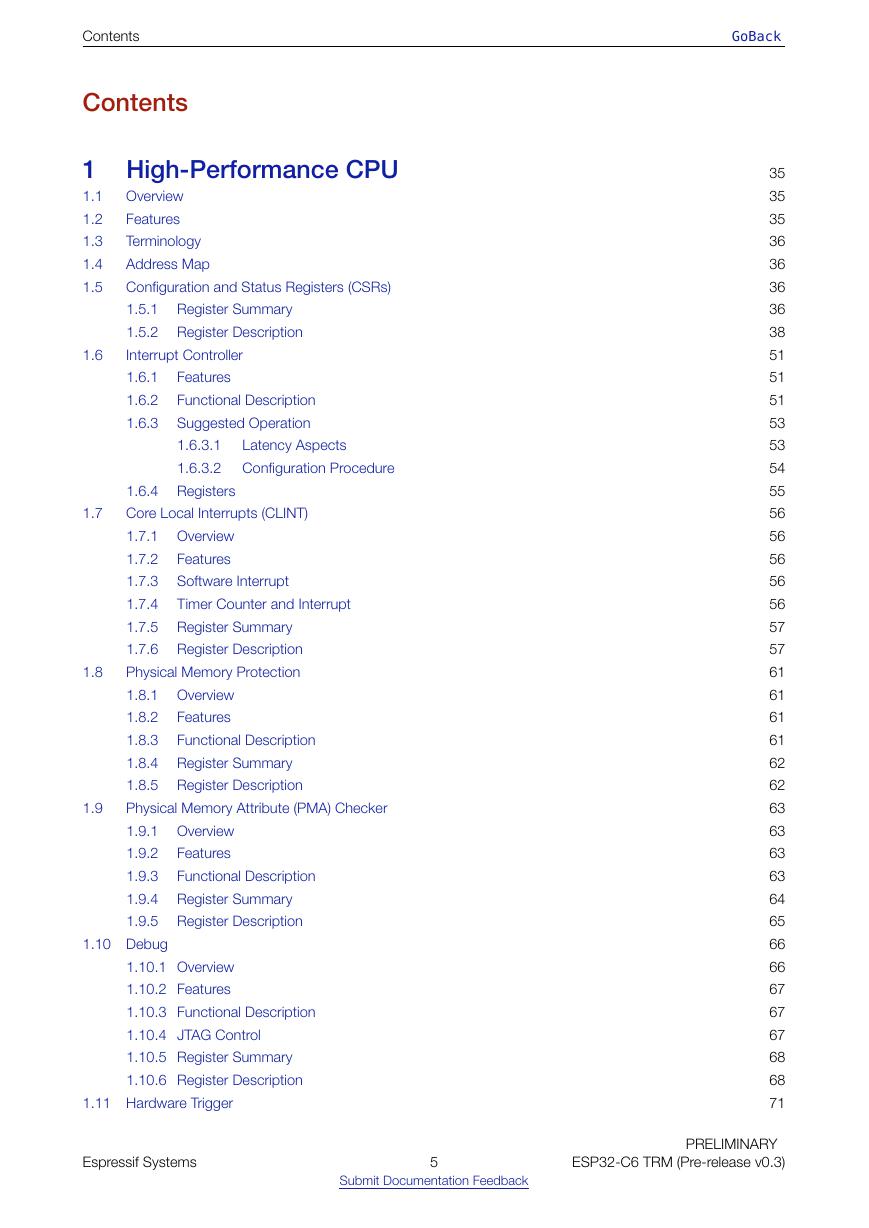

1 High-Performance CPU

1.1 Overview

1.2 Features

1.3 Terminology

1.4 Address Map

1.5 Configuration and Status Registers (CSRs)

1.5.1 Register Summary

1.5.2 Register Description

1.6 Interrupt Controller

1.6.1 Features

1.6.2 Functional Description

1.6.3 Suggested Operation

1.6.4 Registers

1.7 Core Local Interrupts (CLINT)

1.7.1 Overview

1.7.2 Features

1.7.3 Software Interrupt

1.7.4 Timer Counter and Interrupt

1.7.5 Register Summary

1.7.6 Register Description

1.8 Physical Memory Protection

1.8.1 Overview

1.8.2 Features

1.8.3 Functional Description

1.8.4 Register Summary

1.8.5 Register Description

1.9 Physical Memory Attribute (PMA) Checker

1.9.1 Overview

1.9.2 Features

1.9.3 Functional Description

1.9.4 Register Summary

1.9.5 Register Description

1.10 Debug

1.10.1 Overview

1.10.2 Features

1.10.3 Functional Description

1.10.4 JTAG Control

1.10.5 Register Summary

1.10.6 Register Description

1.11 Hardware Trigger

1.11.1 Features

1.11.2 Functional Description

1.11.3 Trigger Execution Flow

1.11.4 Register Summary

1.11.5 Register Description

1.12 Trace

1.12.1 Overview

1.12.2 Features

1.12.3 Functional Description

1.13 Debug Cross-Triggering

1.13.1 Overview

1.13.2 Features

1.13.3 Functional Description

1.13.4 Register Summary

1.13.5 Register Description

1.14 Dedicated IO

1.14.1 Overview

1.14.2 Features

1.14.3 Functional Description

1.14.4 Register Summary

1.14.5 Register Description

1.15 Atomic (A) Extension

1.15.1 Overview

1.15.2 Functional Description

2 RISC-V Trace Encoder (TRACE)

2.1 Terminology

2.2 Introduction

2.3 Features

2.4 Architectural Overview

2.5 Functional Description

2.5.1 Synchronization

2.5.2 Anchor Tag

2.5.3 Memory Writing Mode

2.5.4 Automatic Restart

2.6 Encoder Output Packets

2.6.1 Header

2.6.2 Index

2.6.3 Payload

2.7 Interrupt

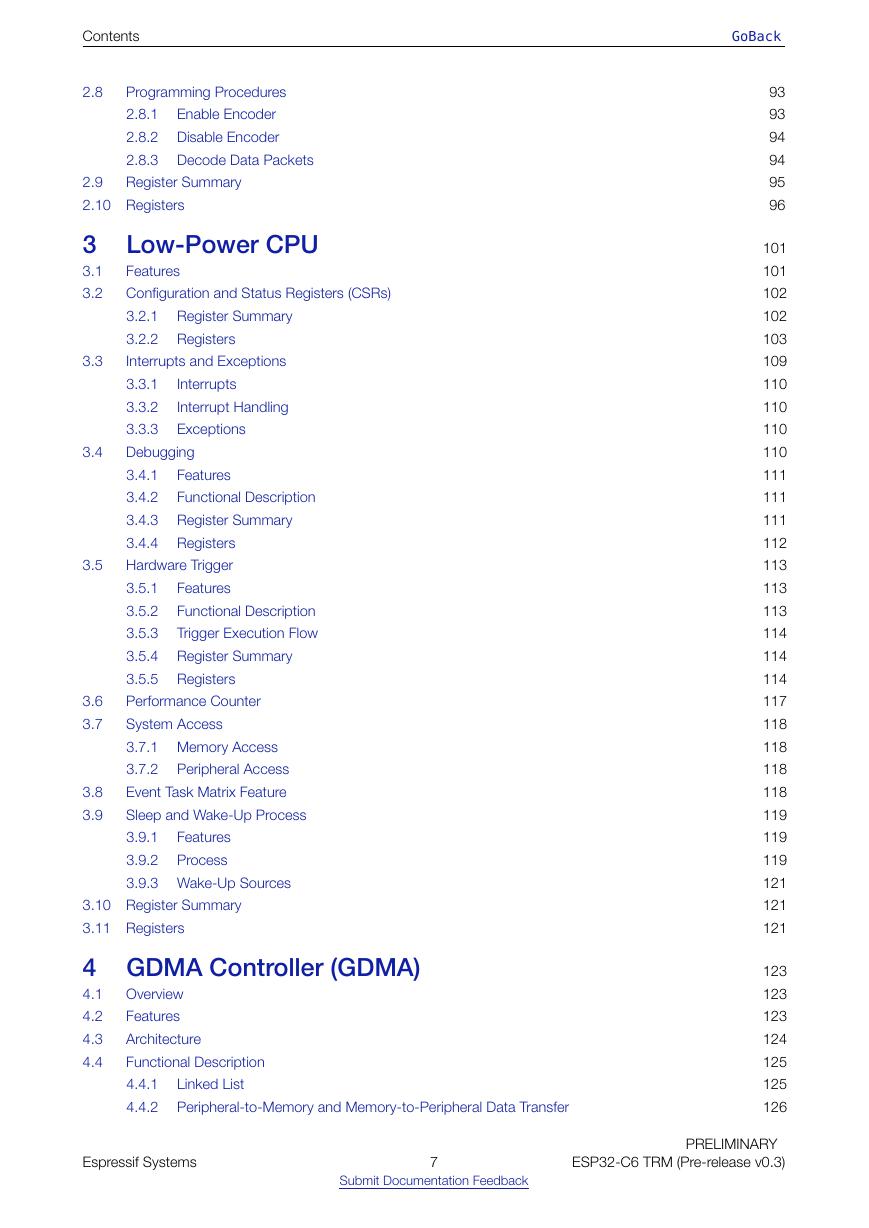

2.8 Programming Procedures

2.8.1 Enable Encoder

2.8.2 Disable Encoder

2.8.3 Decode Data Packets

2.9 Register Summary

2.10 Registers

3 Low-Power CPU

3.1 Features

3.2 Configuration and Status Registers (CSRs)

3.2.1 Register Summary

3.2.2 Registers

3.3 Interrupts and Exceptions

3.3.1 Interrupts

3.3.2 Interrupt Handling

3.3.3 Exceptions

3.4 Debugging

3.4.1 Features

3.4.2 Functional Description

3.4.3 Register Summary

3.4.4 Registers

3.5 Hardware Trigger

3.5.1 Features

3.5.2 Functional Description

3.5.3 Trigger Execution Flow

3.5.4 Register Summary

3.5.5 Registers

3.6 Performance Counter

3.7 System Access

3.7.1 Memory Access

3.7.2 Peripheral Access

3.8 Event Task Matrix Feature

3.9 Sleep and Wake-Up Process

3.9.1 Features

3.9.2 Process

3.9.3 Wake-Up Sources

3.10 Register Summary

3.11 Registers

4 GDMA Controller (GDMA)

4.1 Overview

4.2 Features

4.3 Architecture

4.4 Functional Description

4.4.1 Linked List

4.4.2 Peripheral-to-Memory and Memory-to-Peripheral Data Transfer

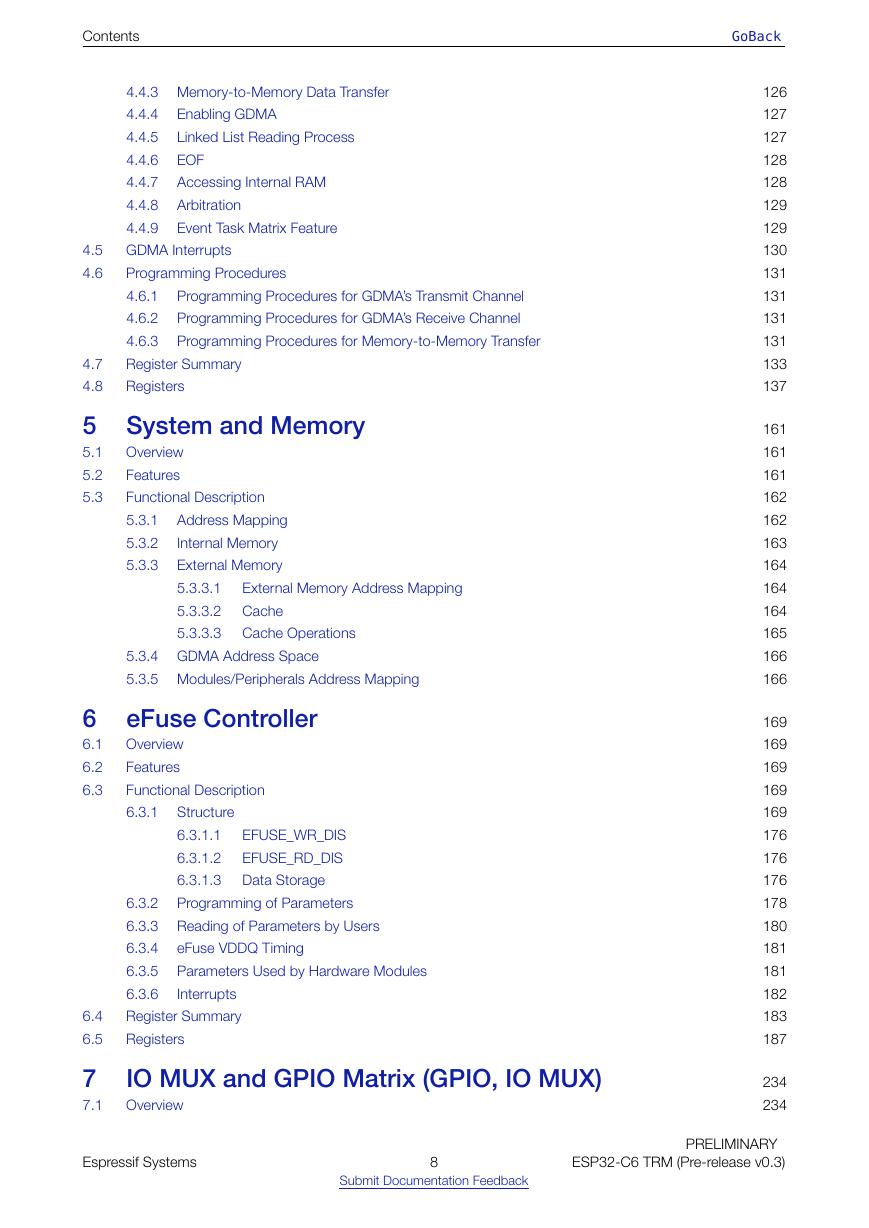

4.4.3 Memory-to-Memory Data Transfer

4.4.4 Enabling GDMA

4.4.5 Linked List Reading Process

4.4.6 EOF

4.4.7 Accessing Internal RAM

4.4.8 Arbitration

4.4.9 Event Task Matrix Feature

4.5 GDMA Interrupts

4.6 Programming Procedures

4.6.1 Programming Procedures for GDMA's Transmit Channel

4.6.2 Programming Procedures for GDMA's Receive Channel

4.6.3 Programming Procedures for Memory-to-Memory Transfer

4.7 Register Summary

4.8 Registers

5 System and Memory

5.1 Overview

5.2 Features

5.3 Functional Description

5.3.1 Address Mapping

5.3.2 Internal Memory

5.3.3 External Memory

5.3.4 GDMA Address Space

5.3.5 Modules/Peripherals Address Mapping

6 eFuse Controller

6.1 Overview

6.2 Features

6.3 Functional Description

6.3.1 Structure

6.3.2 Programming of Parameters

6.3.3 Reading of Parameters by Users

6.3.4 eFuse VDDQ Timing

6.3.5 Parameters Used by Hardware Modules

6.3.6 Interrupts

6.4 Register Summary

6.5 Registers

7 IO MUX and GPIO Matrix (GPIO, IO MUX)

7.1 Overview

7.2 Features

7.3 Architectural Overview

7.4 Peripheral Input via GPIO Matrix

7.4.1 Overview

7.4.2 Signal Synchronization

7.4.3 Functional Description

7.4.4 Simple GPIO Input

7.5 Peripheral Output via GPIO Matrix

7.5.1 Overview

7.5.2 Functional Description

7.5.3 Simple GPIO Output

7.5.4 Sigma Delta Modulated Output (SDM)

7.6 Direct Input and Output via IO MUX

7.6.1 Overview

7.6.2 Functional Description

7.7 LP IO MUX for Low Power and Analog Input/Output

7.7.1 Overview

7.7.2 Low Power Capabilities

7.7.3 Analog Functions

7.8 Pin Functions in Light-sleep

7.9 Pin Hold Feature

7.10 Power Supplies and Management of GPIO Pins

7.10.1 Power Supplies of GPIO Pins

7.10.2 Power Supply Management

7.11 Peripheral Signal List

7.12 IO MUX Functions List

7.13 LP IO MUX Functions List

7.14 ETM Event and Task

7.14.1 ETM Event

7.14.2 ETM Task

7.15 Register Summary

7.15.1 GPIO Matrix Register Summary

7.15.2 IO MUX Register Summary

7.15.3 Sub Design Register Summary

7.15.4 LP IO MUX Register Summary

7.16 Registers

7.16.1 GPIO Matrix Registers

7.16.2 IO MUX Registers

7.16.3 Sub Design Registers

7.16.4 LP IO MUX Registers

8 Reset and Clock

8.1 Reset

8.1.1 Overview

8.1.2 Architectural Overview

8.1.3 Features

8.1.4 Functional Description

8.1.5 Peripheral Reset

8.2 Clock

8.2.1 Overview

8.2.2 Architectural Overview

8.2.3 Features

8.2.4 Functional Description

8.3 Programming Procedures

8.3.1 HP System Clock Configuration

8.3.2 LP System Clock Configuration

8.3.3 Peripheral Clock Reset and Configuration

8.4 Register Summary

8.4.1 PCR Registers

8.4.2 LP System Clock Registers

8.5 Registers

8.5.1 PCR Registers

8.5.2 LP Registers

9 Chip Boot Control

9.1 Overview

9.2 Functional Description

9.2.1 Default Configuration

9.2.2 Boot Mode Control

9.2.3 ROM Messages Printing Control

9.2.4 JTAG Signal Source Control

9.2.5 SDIO Sampling Input Edge and Output Driving Edge Control

10 Interrupt Matrix (INTMTX)

10.1 Overview

10.2 Features

10.3 Functional Description

10.3.1 Peripheral Interrupt Sources

10.3.2 CPU Interrupts

10.3.3 Assign Peripheral Interrupt Source to CPU Interrupt

10.3.4 Query Current Interrupt Status of Peripheral Interrupt Source

10.4 Register Summary

10.4.1 Interrupt Matrix Register Summary

10.4.2 Interrupt Priority Register Summary

10.5 Registers

10.5.1 Interrupt Matrix Registers

10.5.2 Interrupt Priority Registers

11 Event Task Matrix (SOC_ETM)

11.1 Overview

11.2 Features

11.3 Functional Description

11.3.1 Architecture

11.3.2 Events

11.3.3 Tasks

11.3.4 Timing Considerations

11.3.5 Channel Control

11.4 Register Summary

11.5 Registers

12 System Timer (SYSTIMER)

12.1 Overview

12.2 Features

12.3 Clock Source Selection

12.4 Functional Description

12.4.1 Counter

12.4.2 Comparator and Alarm

12.4.3 Event Task Matrix

12.4.4 Synchronization Operation

12.4.5 Interrupt

12.5 Programming Procedure

12.5.1 Read Current Count Value

12.5.2 Configure One-Time Alarm in Target Mode

12.5.3 Configure Periodic Alarms in Period Mode

12.5.4 Update After Deep-sleep and Light-sleep

12.6 Register Summary

12.7 Registers

13 Timer Group (TIMG)

13.1 Overview

13.2 Features

13.3 Functional Description

13.3.1 16-bit Prescaler and Clock Selection

13.3.2 54-bit Time-base Counter

13.3.3 Alarm Generation

13.3.4 Timer Reload

13.3.5 Event Task Matrix Function

13.3.6 RTC_SLOW_CLK Frequency Calculation

13.3.7 Interrupts

13.4 Configuration and Usage

13.4.1 Timer as a Simple Clock

13.4.2 Timer as One-shot Alarm

13.4.3 Timer as Periodic Alarm by APB

13.4.4 Timer as Periodic Alarm by ETM

13.4.5 RTC_SLOW_CLK Frequency Calculation

13.5 Register Summary

13.6 Registers

14 Watchdog Timers (WDT)

14.1 Overview

14.2 Digital Watchdog Timers

14.2.1 Features

14.2.2 Functional Description

14.3 Super Watchdog

14.3.1 Features

14.3.2 Super Watchdog Controller

14.4 Interrupts

14.5 Register Summary

14.6 Registers

15 Permission Control (PMS)

15.1 Overview

15.2 Features

15.3 Functional Description

15.3.1 TEE Controller Functional Description

15.3.2 APM Controller Functional Description

15.4 Programming Procedure

15.5 Illegal access and interrupts

15.6 Register Summary

15.6.1 High Performance APM Registers (HP_APM_REG)

15.6.2 Low Power APM Registers (LP_APM_REG)

15.6.3 Low Power APM0 Registers (LP_APM0_REG)

15.6.4 High Performance TEE Registers

15.6.5 Low Power TEE Registers

15.7 Registers

15.7.1 High Performance APM Registers (HP_APM_REG)

15.7.2 Low Power APM Registers (LP_APM_REG)

15.7.3 Low Power APM0 Registers (LP_APM0_REG)

15.7.4 High Performance TEE Registers

15.7.5 Low Power TEE Registers

16 System Registers (HP_SYSTEM)

16.1 Overview

16.2 Features

16.3 Function Description

16.3.1 External Memory Encryption/Decryption Configuration

16.3.2 Anti-DPA Attack Security Control

16.3.3 Software ROM Table Register

16.3.4 HP Core/LP Core Debug Control

16.3.5 Bus Timeout Protection

16.4 Register Summary

16.5 Registers

17 Debug Assistant (ASSIST_DEBUG)

17.1 Overview

17.2 Features

17.3 Functional Description

17.3.1 Region Read/Write Monitoring

17.3.2 SP Monitoring

17.3.3 PC Logging

17.3.4 CPU/DMA Bus Access Logging

17.4 Recommended Operation

17.4.1 Region Monitoring and SP Monitoring Configuration

17.4.2 PC Logging Configuration

17.4.3 CPU/DMA Bus Access Logging Configuration

17.5 Register Summary

17.5.1 Summary of Bus Logging Configuration Registers

17.5.2 Summary of Other Registers

17.6 Registers

17.6.1 Bus Logging Configuration Registers

17.6.2 Other Registers

18 AES Accelerator (AES)

18.1 Introduction

18.2 Features

18.3 AES Working Modes

18.4 Typical AES Working Mode

18.4.1 Key, Plaintext, and Ciphertext

18.4.2 Endianness

18.4.3 Operation Process

18.5 DMA-AES Working Mode

18.5.1 Key, Plaintext, and Ciphertext

18.5.2 Endianness

18.5.3 Standard Incrementing Function

18.5.4 Block Number

18.5.5 Initialization Vector

18.5.6 Block Operation Process

18.6 Memory Summary

18.7 Register Summary

18.8 Registers

19 ECC Accelerator (ECC)

19.1 Introduction

19.2 Features

19.3 Terminology

19.3.1 ECC Basics

19.3.2 Definitions of ESP32-C6's ECC

19.4 Function Description

19.4.1 Key Size

19.4.2 Working Modes

19.5 Clocks and Resets

19.6 Interrupts

19.7 Programming Procedures

19.8 Register Summary

19.9 Registers

20 HMAC Accelerator (HMAC)

20.1 Main Features

20.2 Functional Description

20.2.1 Upstream Mode

20.2.2 Downstream JTAG Enable Mode

20.2.3 Downstream Digital Signature Mode

20.2.4 HMAC eFuse Configuration

20.2.5 HMAC Process (Detailed)

20.3 HMAC Algorithm Details

20.3.1 Padding Bits

20.3.2 HMAC Algorithm Structure

20.4 Register Summary

20.5 Registers

21 RSA Accelerator (RSA)

21.1 Introduction

21.2 Features

21.3 Functional Description

21.3.1 Large-number Modular Exponentiation

21.3.2 Large-number Modular Multiplication

21.3.3 Large-number Multiplication

21.3.4 Options for Additional Acceleration

21.4 Memory Summary

21.5 Register Summary

21.6 Registers

22 SHA Accelerator (SHA)

22.1 Introduction

22.2 Features

22.3 Working Modes

22.4 Function Description

22.4.1 Preprocessing

22.4.2 Hash Operation

22.4.3 Message Digest

22.4.4 Interrupt

22.5 Register Summary

22.6 Registers

23 Digital Signature (DS)

23.1 Overview

23.2 Features

23.3 Functional Description

23.3.1 Overview

23.3.2 Private Key Operands

23.3.3 Software Prerequisites

23.3.4 DS Operation at the Hardware Level

23.3.5 DS Operation at the Software Level

23.4 Memory Summary

23.5 Register Summary

23.6 Registers

24 External Memory Encryption and Decryption (XTS_AES)

24.1 Overview

24.2 Features

24.3 Module Structure

24.4 Functional Description

24.4.1 XTS Algorithm

24.4.2 Key

24.4.3 Target Memory Space

24.4.4 Data Writing

24.4.5 Manual Encryption Block

24.4.6 Auto Decryption Block

24.5 Software Process

24.6 Anti-DPA

24.7 Register Summary

24.8 Registers

25 Random Number Generator (RNG)

25.1 Introduction

25.2 Features

25.3 Functional Description

25.4 Programming Procedure

25.5 Register Summary

25.6 Register

26 UART Controller (UART, LP_UART, UHCI)

26.1 Overview

26.2 Features

26.3 UART Structure

26.4 Functional Description

26.4.1 Clock and Reset

26.4.2 UART FIFO

26.4.3 Baud Rate Generation and Detection

26.4.4 UART Data Frame

26.4.5 AT_CMD Character Structure

26.4.6 RS485

26.4.7 IrDA

26.4.8 Wake-up

26.4.9 Flow Control

26.4.10 GDMA Mode

26.4.11 UART Interrupts

26.4.12 UHCI Interrupts

26.5 Programming Procedures

26.5.1 Register Type

26.5.2 Detailed Steps

26.6 Register Summary

26.6.1 UART Register Summary

26.6.2 LP UART Register Summary

26.6.3 UHCI Register Summary

26.7 Registers

26.7.1 UART Registers

26.7.2 LP UART Registers

26.7.3 UHCI Registers

27 SPI Controller (SPI)

27.1 Overview

27.2 Glossary

27.3 Features

27.4 Architectural Overview

27.5 Functional Description

27.5.1 Data Modes

27.5.2 Introduction to FSPI Bus Signals

27.5.3 Bit Read/Write Order Control

27.5.4 Transfer Types

27.5.5 CPU-Controlled Data Transfer

27.5.6 DMA-Controlled Data Transfer

27.5.7 Data Flow Control

27.5.8 GP-SPI2 as a Master

27.5.9 GP-SPI2 Works as a Slave

27.6 CS Setup Time and Hold Time Control

27.7 GP-SPI2 Clock Control

27.7.1 Clock Phase and Polarity

27.7.2 Clock Control as Master

27.7.3 Clock Control as Slave

27.8 GP-SPI2 Timing Compensation

27.9 Interrupts

27.10 Register Summary

27.11 Registers

28 I2C Controller (I2C)

28.1 Overview

28.2 Features

28.3 I2C Architecture

28.4 Functional Description

28.4.1 Clock Configuration

28.4.2 SCL and SDA Noise Filtering

28.4.3 SCL Clock Stretching

28.4.4 Generating SCL Pulses in Idle State

28.4.5 Synchronization

28.4.6 Open-Drain Output

28.4.7 Timing Parameter Configuration

28.4.8 Timeout Control

28.4.9 Command Configuration

28.4.10 TX/RX RAM Data Storage

28.4.11 Data Conversion

28.4.12 Addressing Mode

28.4.13 R/W Bit Check in 10-bit Addressing Mode

28.4.14 To Start the I2C Controller

28.5 Functional differences between LP_I2C and I2C

28.6 Programming Example

28.6.1 I2C master Writes to I2C slave with a 7-bit Address in One Command Sequence

28.6.2 I2C master Writes to I2C slave with a 10-bit Address in One Command Sequence

28.6.3 I2C master Writes to I2C slave with Two 7-bit Addresses in One Command Sequence

28.6.4 I2C master Writes to I2C slave with a 7-bit Address in Multiple Command Sequences

28.6.5 I2C master Reads I2C slave with a 7-bit Address in One Command Sequence

28.6.6 I2C master Reads I2C slave with a 10-bit Address in One Command Sequence

28.6.7 I2C master Reads I2C slave with Two 7-bit Addresses in One Command Sequence

28.6.8 I2C master Reads I2C slave with a 7-bit Address in Multiple Command Sequences

28.7 Interrupts

28.8 Register Summary

28.9 I2C Register Summary

28.10 LP_I2C Register Summary

28.11 I2C Registers

28.11.1 LP_I2C 寄存器

29 I2S Controller (I2S)

29.1 Overview

29.2 Terminology

29.3 Features

29.4 System Architecture

29.5 Supported Audio Standards

29.5.1 TDM Philips Standard

29.5.2 TDM MSB Alignment Standard

29.5.3 TDM PCM Standard

29.5.4 PDM Standard

29.6 I2S TX/RX Clock

29.7 I2S Reset

29.8 I2S Master/Slave Mode

29.8.1 Master/Slave TX Mode

29.8.2 Master/Slave RX Mode

29.9 Transmitting Data

29.9.1 Data Format Control

29.9.2 Channel Mode Control

29.10 Receiving Data

29.10.1 Channel Mode Control

29.10.2 Data Format Control

29.11 Software Configuration Process

29.11.1 Configure I2S as TX Mode

29.11.2 Configure I2S as RX Mode

29.12 I2S Interrupts

29.12.1 Event Task Matrix Feature

29.13 Register Summary

29.14 Registers

30 Pulse Count Controller (PCNT)

30.1 Features

30.2 Functional Description

30.3 Applications

30.3.1 Channel 0 Incrementing Independently

30.3.2 Channel 0 Decrementing Independently

30.3.3 Channel 0 and Channel 1 Incrementing Together

30.4 Register Summary

30.5 Registers

31 USB Serial/JTAG Controller (USB_SERIAL_JTAG)

31.1 Overview

31.2 Features

31.3 Functional Description

31.3.1 CDC-ACM USB Interface Functional Description

31.3.2 CDC-ACM Firmware Interface Functional Description

31.3.3 USB-to-JTAG Interface: JTAG Command Processor

31.3.4 USB-to-JTAG Interface: CMD_REP Usage Example

31.3.5 USB-to-JTAG Interface: Response Capture Unit

31.3.6 USB-to-JTAG Interface: Control Transfer Requests

31.4 Recommended Operation

31.5 Interrupts

31.6 Register Summary

31.7 Registers

32 Two-wire Automotive Interface (TWAI)

32.1 Features

32.2 Protocol Overview

32.2.1 TWAI Properties

32.2.2 TWAI Messages

32.2.3 TWAI Errors

32.2.4 TWAI Bit Timing

32.3 Architectural Overview

32.3.1 Registers Block

32.3.2 Bit Stream Processor

32.3.3 Error Management Logic

32.3.4 Bit Timing Logic

32.3.5 Acceptance Filter

32.3.6 Receive FIFO

32.4 Functional Description

32.4.1 Modes

32.4.2 Bit Timing

32.4.3 Interrupt Management

32.4.4 Transmit and Receive Buffers

32.4.5 Receive FIFO and Data Overruns

32.4.6 Acceptance Filter

32.4.7 Error Management

32.4.8 Error Code Capture

32.4.9 Arbitration Lost Capture

32.4.10 Transceiver Auto-Standby

32.5 Register Summary

32.6 Registers

33 SDIO 2.0 Slave Controller (SDIO)

33.1 Overview

33.2 Features

33.3 Architecture Overview

33.4 Standards Compliance

33.5 Functional Description

33.5.1 Physical Bus

33.5.2 Supported Commands

33.5.3 I/O Function 0 Address Space

33.5.4 I/O Function 1/2 Address Space Map

33.5.5 DMA

33.5.6 SDIO Bus Timing

33.6 Interrupt

33.6.1 Host Interrupt

33.6.2 Slave Interrupt

33.7 Packet Sending and Receiving Procedure

33.7.1 Sending Packets to SDIO Host

33.7.2 Receiving Packets from SDIO Host

33.8 Register Summary

33.8.1 HINF Register Summary

33.8.2 SLC Register Summary

33.8.3 SLC Host Register Summary

33.9 Registers

33.9.1 HINF Registers

33.9.2 SLC Registers

33.9.3 SLC Host Registers

34 LED PWM Controller (LEDC)

34.1 Overview

34.2 Features

34.3 Functional Description

34.3.1 Architecture

34.3.2 Timers

34.3.3 PWM Generators

34.3.4 Duty Cycle Fading

34.3.5 Event Task Matrix Feature

34.3.6 Interrupts

34.4 Register Summary

34.5 Registers

35 Motor Control PWM (MCPWM)

35.1 Overview

35.2 Features

35.3 Modules

35.3.1 Overview

35.3.2 PWM Timer Module

35.3.3 PWM Operator Module

35.3.4 Capture Module

35.3.5 ETM Module

35.4 Register Summary

35.5 Registers

36 Remote Control Peripheral (RMT)

36.1 Overview

36.2 Features

36.3 Functional Description

36.3.1 RMT Architecture

36.3.2 RMT RAM

36.3.3 Clock

36.3.4 Transmitter

36.3.5 Receiver

36.3.6 Configuration Update

36.3.7 Interrupts

36.4 Register Summary

36.5 Registers

37 Parallel IO Controller (PARL_IO)

37.1 Introduction

37.2 Glossary

37.3 Features

37.4 Architectural Overview

37.5 Functional Description

37.5.1 Clock Generator

37.5.2 Clock & Reset Restriction

37.5.3 Master-Slave Mode

37.5.4 Receive Modes of the RX Unit

37.5.5 RX Unit GDMA SUC EOF Generation

37.5.6 RX Unit Timeout

37.5.7 Valid Signal Output of TX Unit

37.5.8 Bus Idle Value of TX Unit

37.5.9 Data Transfer in a Single Frame

37.5.10 Bit Reordering in One Byte

37.6 Programming Procedures

37.6.1 Data Receiving Operation Process

37.6.2 Data Transmitting Operation Process

37.7 Application Examples

37.7.1 Co-working with SPI

37.7.2 Co-working with I2S

37.7.3 Co-working with Camera

37.8 Interrupts

37.9 Register Summary

37.10 Registers

38 On-Chip Sensor and Analog Signal Processing

38.1 Overview

38.2 SAR ADC

38.2.1 Overview

38.2.2 Features

38.2.3 Functional Description

38.3 Temperature Sensor

38.3.1 Overview

38.3.2 Features

38.3.3 Functional Description

38.4 Event Task Matrix Feature

38.4.1 SAR ADC's ETM Feature

38.4.2 Temperature Sensor's ETM Feature

38.5 Interrupts

38.6 Register Summary

38.7 Registers

39 Related Documentation and Resources

Glossary

Abbreviations for Peripherals

Abbreviations Related to Registers

Access Types for Registers

Programming Reserved Register Field

Introduction

Programming Reserved Register Field

Revision History

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf