38 Year Data Retention

Preliminary

FM24CL04B

4Kb Serial 3V F-RAM Memory

Features

4K bit Ferroelectric Nonvolatile RAM

• Organized as 512 x 8 bits

• High Endurance 1014 Read/Writes

•

• NoDelay™ Writes

• Advanced High-Reliability Ferroelectric Process

Fast Two-wire Serial Interface

• Up to 1 MHz maximum bus frequency

• Direct hardware replacement for EEPROM

• Supports legacy timing for 100 kHz & 400 kHz

Description

The FM24CL04B is a 4-kilobit nonvolatile memory

employing an advanced ferroelectric process. A

ferroelectric random access memory or FRAM is

nonvolatile and performs reads and writes like a

RAM. It provides reliable data retention for 38 years

while eliminating the complexities, overhead, and

system level reliability problems caused by EEPROM

and other nonvolatile memories.

The FM24CL04B performs write operations at bus

speed. No write delays are incurred. Data is written to

the memory array in the cycle after it has been

successfully transferred to the device. The next bus

cycle may commence immediately without the need

for data polling. The FM24CL04B is capable of

supporting 1014 read/write cycles, or a million times

more write cycles than EEPROM.

These capabilities make the FM24CL04B ideal for

nonvolatile memory applications requiring frequent

or rapid writes. Examples range from data collection

where the number of write cycles may be critical, to

demanding industrial controls where the long write

time of EEPROM can cause data

loss. The

combination of features allows more frequent data

writing with less overhead for the system.

The FM24CL04B provides substantial benefits to

users of serial EEPROM, yet these benefits are

available in a hardware drop-in replacement. The

FM24CL04B is available in an industry standard 8-

pin SOIC package and uses a familiar two-wire

protocol. The specifications are guaranteed over an

industrial temperature range of -40°C to +85°C.

2.7V to 3.65V operation

100 µA Active Current (100 kHz)

3 µA (typ.) Standby Current

Low Power Operation

•

•

•

Industry Standard Configuration

•

•

Industrial Temperature -40° C to +85° C

8-pin “Green”/RoHS SOIC (-G)

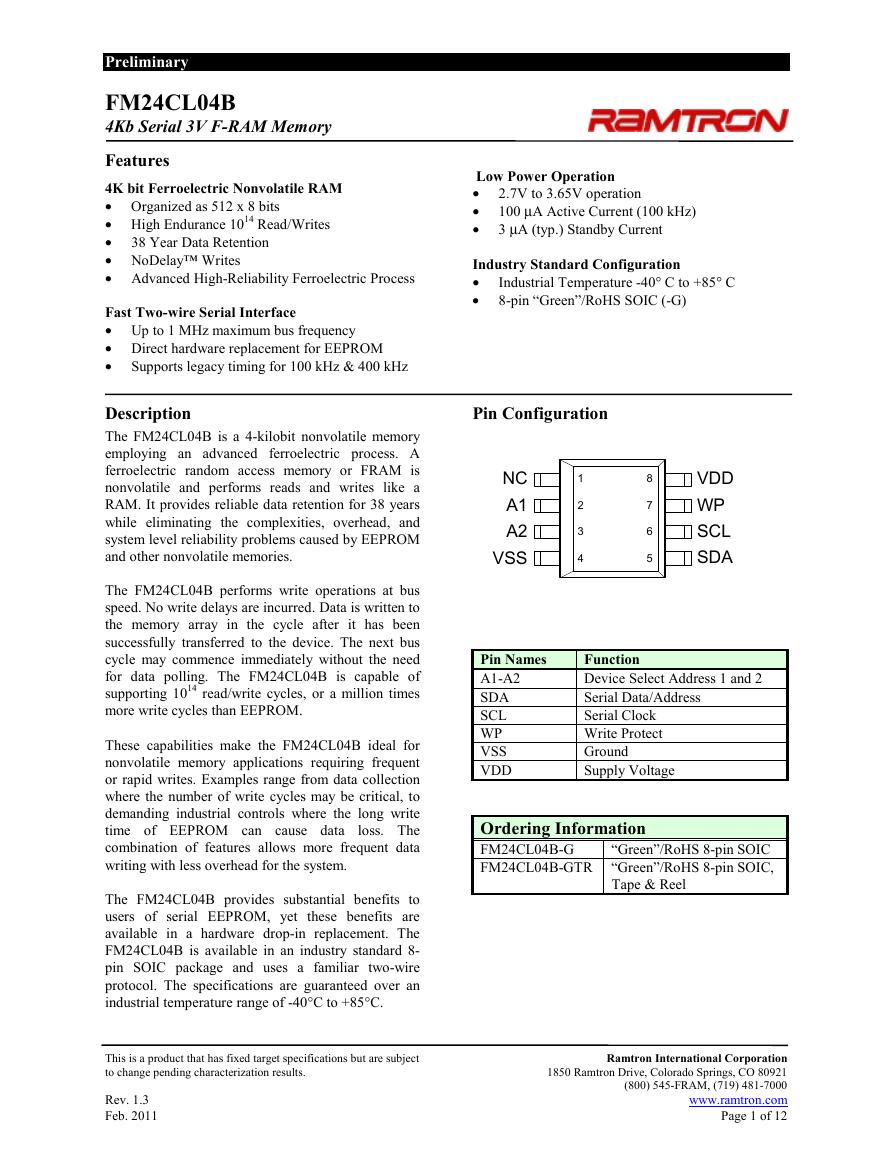

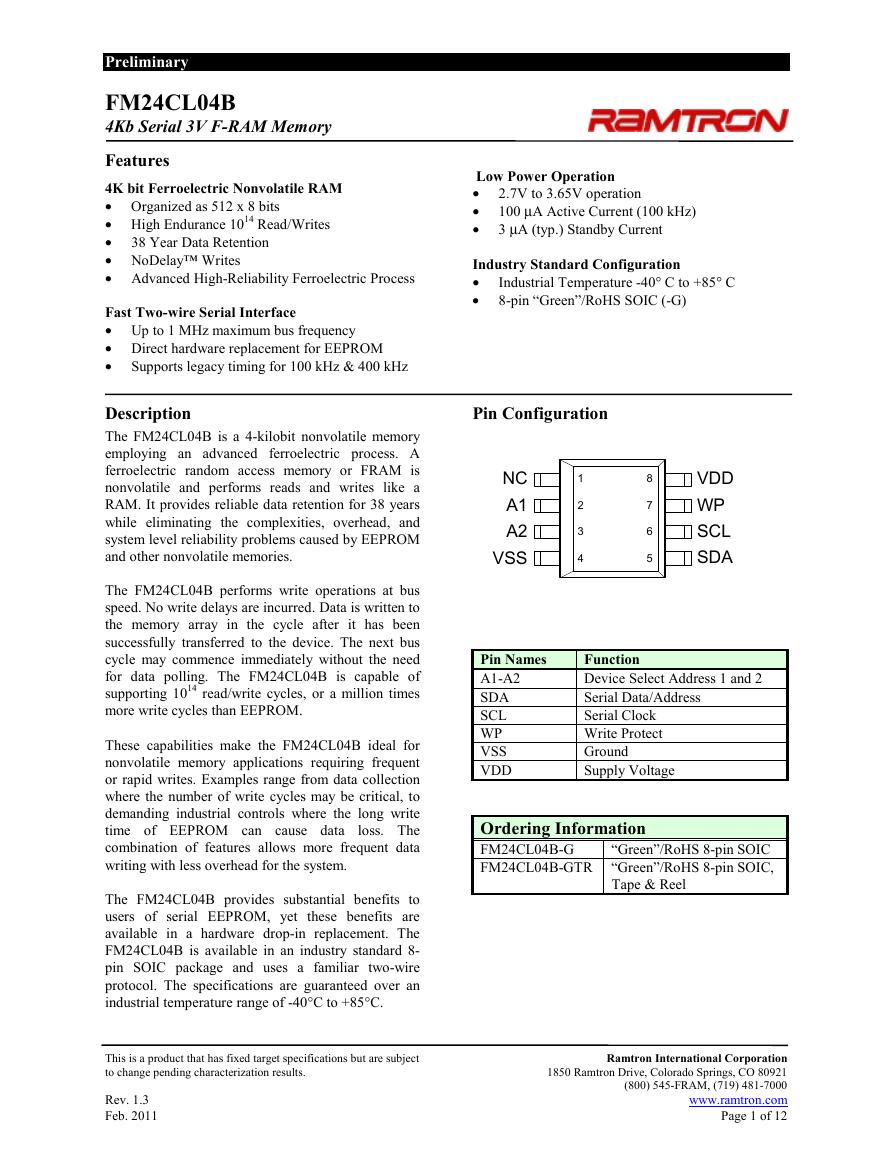

Pin Configuration

NC

A1

A2

VSS

1

2

3

4

VDD

WP

SCL

SDA

8

7

6

5

Pin Names

A1-A2

SDA

SCL

WP

VSS

VDD

Function

Device Select Address 1 and 2

Serial Data/Address

Serial Clock

Write Protect

Ground

Supply Voltage

Ordering Information

FM24CL04B-G

FM24CL04B-GTR

“Green”/RoHS 8-pin SOIC

“Green”/RoHS 8-pin SOIC,

Tape & Reel

This is a product that has fixed target specifications but are subject

to change pending characterization results.

Rev. 1.3

Feb. 2011

Ramtron International Corporation

1850 Ramtron Drive, Colorado Springs, CO 80921

(800) 545-FRAM, (719) 481-7000

www.ramtron.com

Page 1 of 12

�

FM24CL04B

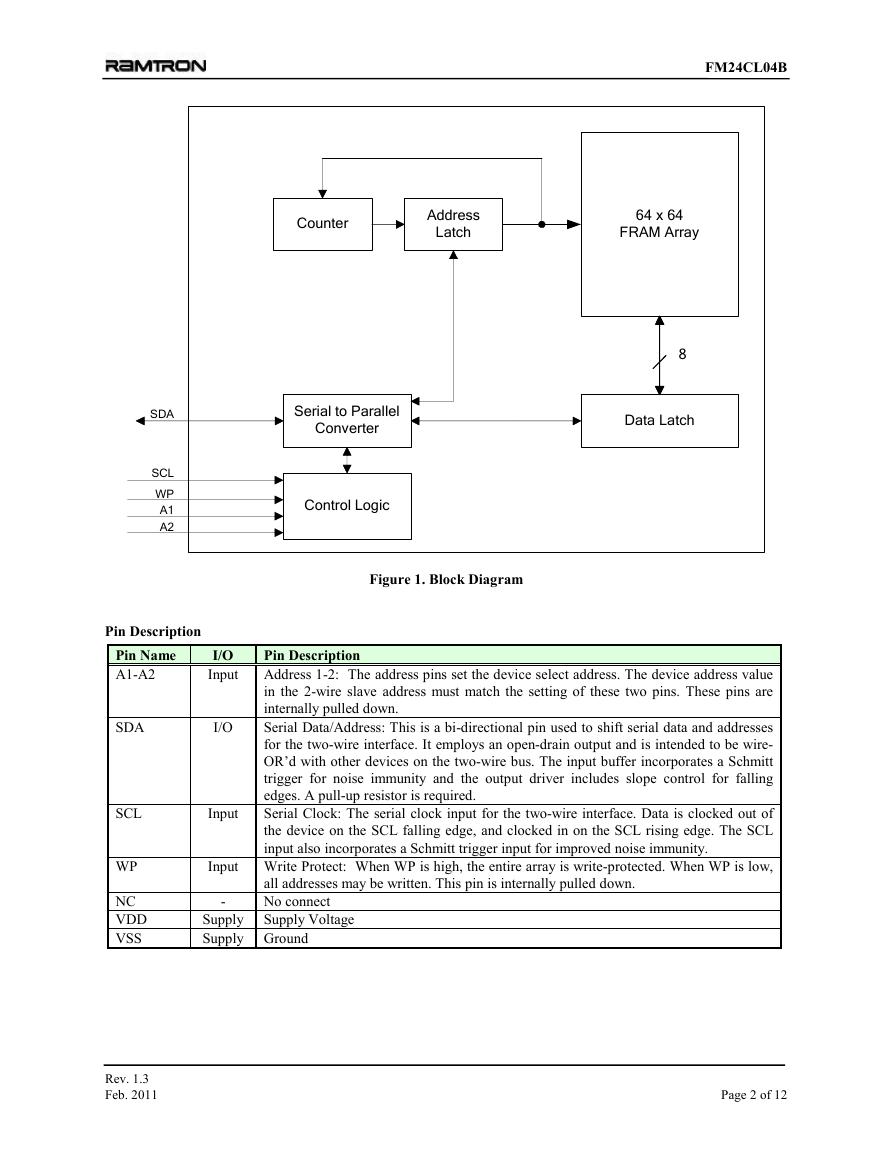

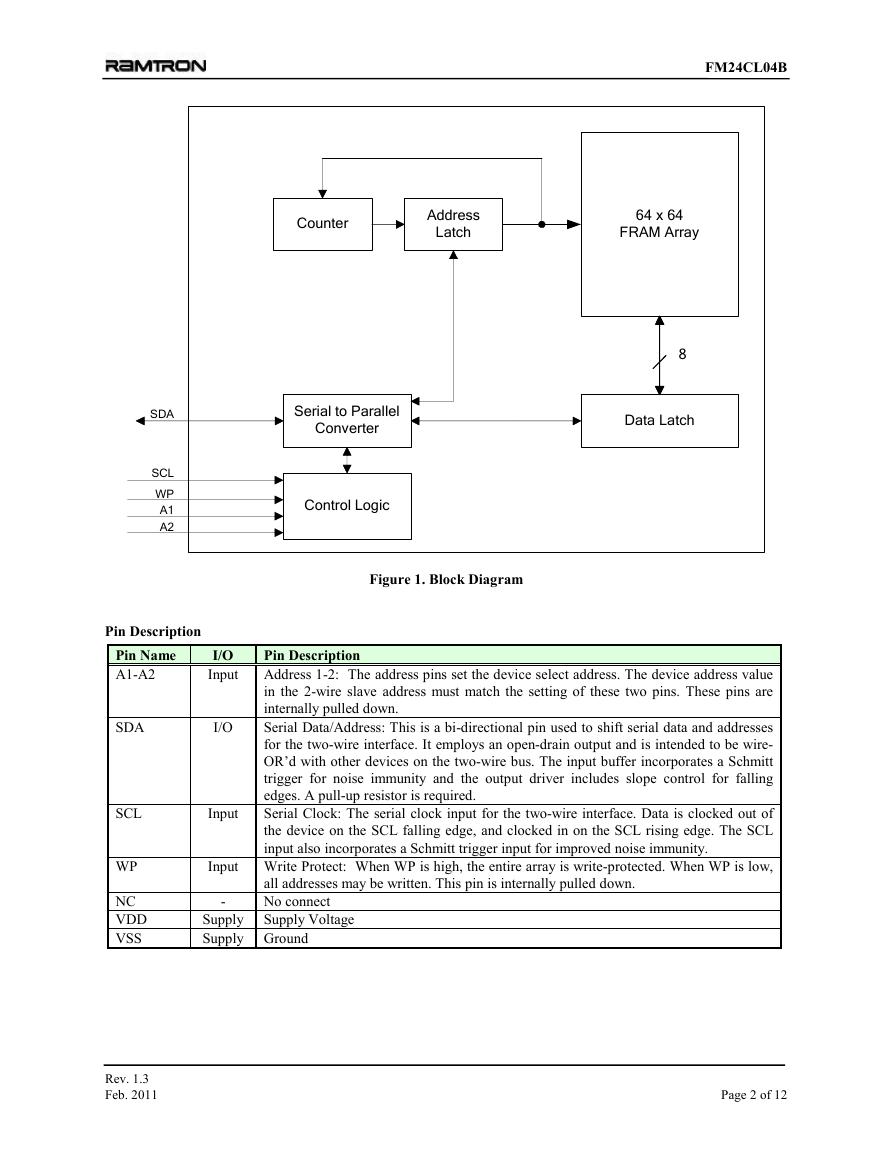

Counter

Address

Latch

64 x 64

FRAM Array

8

Data Latch

SDA

SCL

WP

A1

A2

Serial to Parallel

Converter

Control Logic

Figure 1. Block Diagram

Pin Description

Pin Name

A1-A2

I/O

Input

SDA

I/O

SCL

Input

Pin Description

Address 1-2: The address pins set the device select address. The device address value

in the 2-wire slave address must match the setting of these two pins. These pins are

internally pulled down.

Serial Data/Address: This is a bi-directional pin used to shift serial data and addresses

for the two-wire interface. It employs an open-drain output and is intended to be wire-

OR’d with other devices on the two-wire bus. The input buffer incorporates a Schmitt

trigger for noise immunity and the output driver includes slope control for falling

edges. A pull-up resistor is required.

Serial Clock: The serial clock input for the two-wire interface. Data is clocked out of

the device on the SCL falling edge, and clocked in on the SCL rising edge. The SCL

input also incorporates a Schmitt trigger input for improved noise immunity.

WP

NC

VDD

VSS

Rev. 1.3

Feb. 2011

Input Write Protect: When WP is high, the entire array is write-protected. When WP is low,

all addresses may be written. This pin is internally pulled down.

No connect

Supply Voltage

-

Supply

Supply Ground

Page 2 of 12

�

FM24CL04B

two-wire bus

industry standard

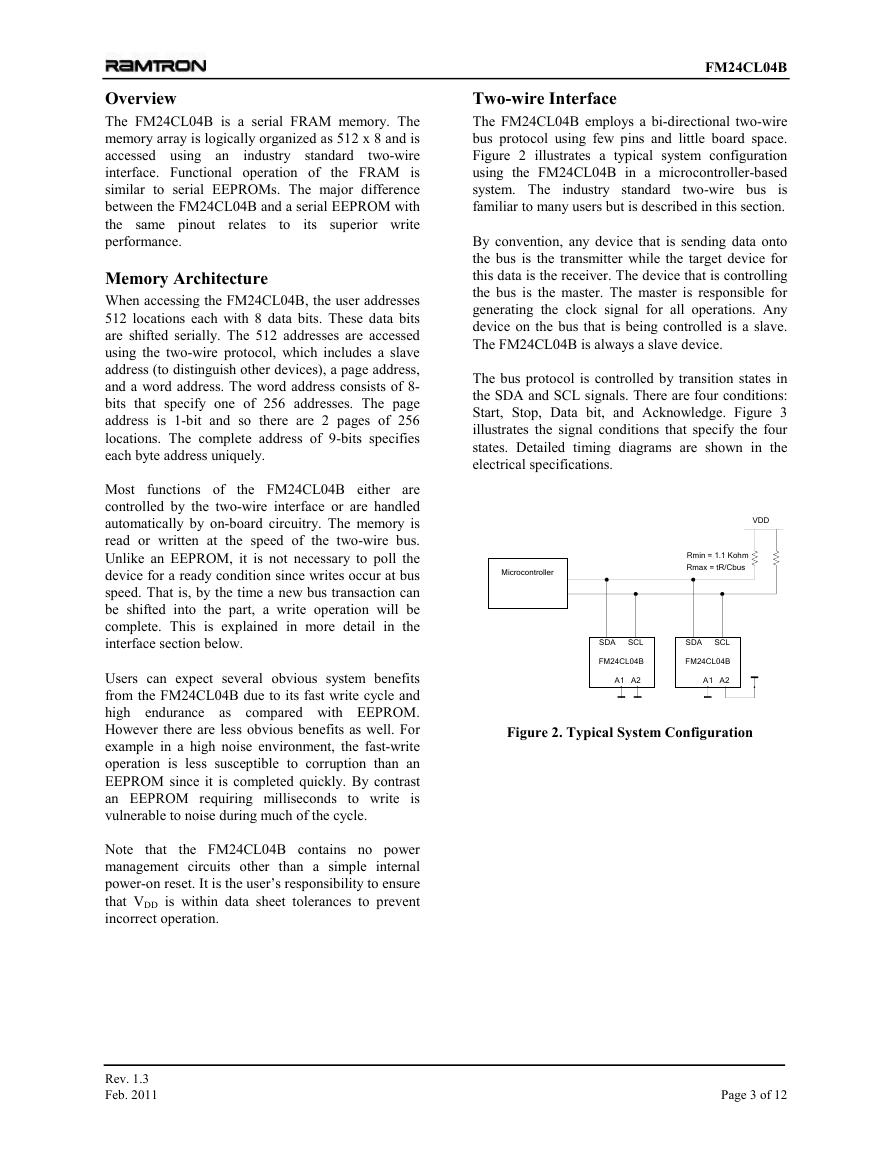

Two-wire Interface

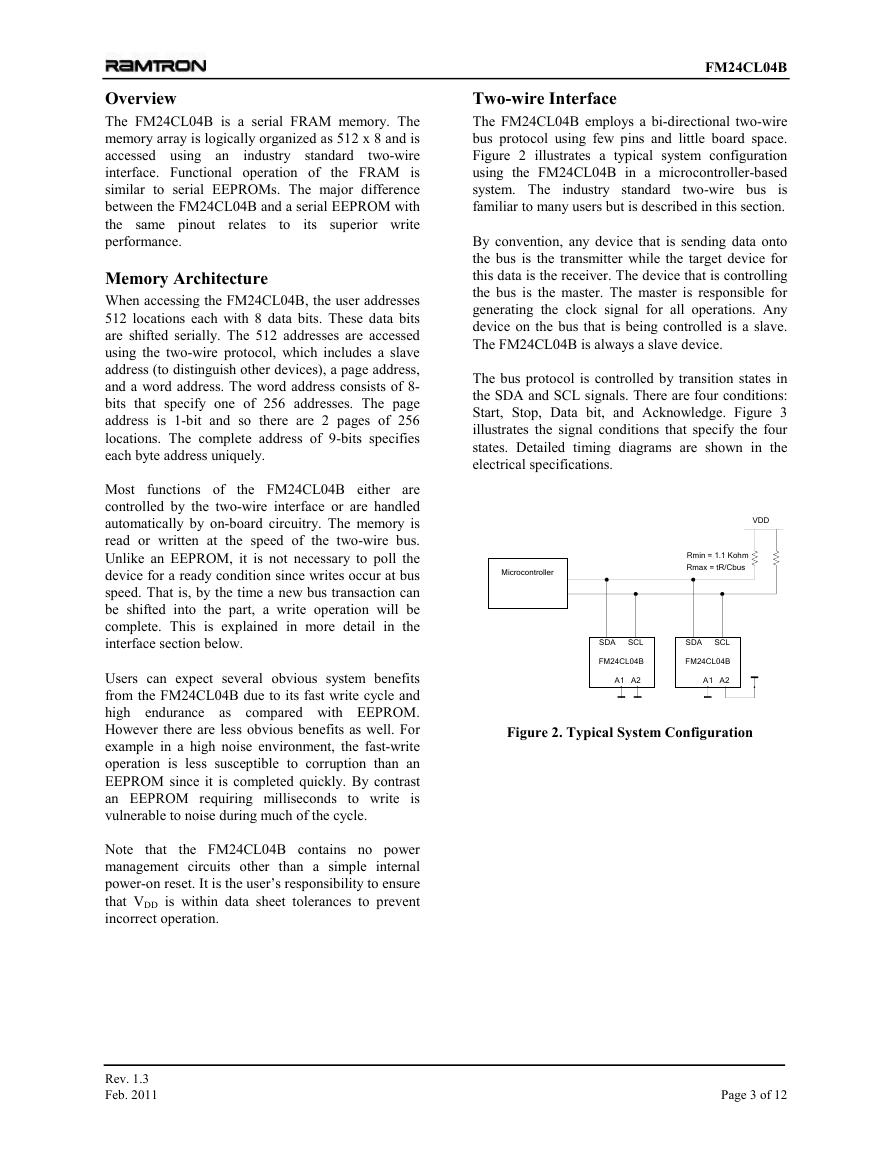

The FM24CL04B employs a bi-directional two-wire

bus protocol using few pins and little board space.

Figure 2 illustrates a typical system configuration

using the FM24CL04B in a microcontroller-based

system. The

is

familiar to many users but is described in this section.

By convention, any device that is sending data onto

the bus is the transmitter while the target device for

this data is the receiver. The device that is controlling

the bus is the master. The master is responsible for

generating the clock signal for all operations. Any

device on the bus that is being controlled is a slave.

The FM24CL04B is always a slave device.

The bus protocol is controlled by transition states in

the SDA and SCL signals. There are four conditions:

Start, Stop, Data bit, and Acknowledge. Figure 3

illustrates the signal conditions that specify the four

states. Detailed timing diagrams are shown in the

electrical specifications.

Microcontroller

VDD

Rmin = 1.1 Kohm

Rmax = tR/Cbus

SDA

SCL

SDA

SCL

FM24CL04B

FM24CL04B

A1 A2

A1 A2

Figure 2. Typical System Configuration

Overview

The FM24CL04B is a serial FRAM memory. The

memory array is logically organized as 512 x 8 and is

accessed using an

two-wire

interface. Functional operation of the FRAM is

similar to serial EEPROMs. The major difference

between the FM24CL04B and a serial EEPROM with

the same pinout relates

its superior write

performance.

industry standard

to

Memory Architecture

When accessing the FM24CL04B, the user addresses

512 locations each with 8 data bits. These data bits

are shifted serially. The 512 addresses are accessed

using the two-wire protocol, which includes a slave

address (to distinguish other devices), a page address,

and a word address. The word address consists of 8-

bits that specify one of 256 addresses. The page

address is 1-bit and so there are 2 pages of 256

locations. The complete address of 9-bits specifies

each byte address uniquely.

Most functions of

the FM24CL04B either are

controlled by the two-wire interface or are handled

automatically by on-board circuitry. The memory is

read or written at the speed of the two-wire bus.

Unlike an EEPROM, it is not necessary to poll the

device for a ready condition since writes occur at bus

speed. That is, by the time a new bus transaction can

be shifted into the part, a write operation will be

complete. This is explained in more detail in the

interface section below.

Users can expect several obvious system benefits

from the FM24CL04B due to its fast write cycle and

high endurance as compared with EEPROM.

However there are less obvious benefits as well. For

example in a high noise environment, the fast-write

operation is less susceptible to corruption than an

EEPROM since it is completed quickly. By contrast

an EEPROM requiring milliseconds to write is

vulnerable to noise during much of the cycle.

Note

the FM24CL04B contains no power

management circuits other than a simple internal

power-on reset. It is the user’s responsibility to ensure

that VDD is within data sheet tolerances to prevent

incorrect operation.

that

Rev. 1.3

Feb. 2011

Page 3 of 12

�

FM24CL04B

Figure 3. Data Transfer Protocol

Stop Condition

A Stop condition is indicated when the bus master

drives SDA from low to high while the SCL signal is

high. All operations must end with a Stop condition. If

an operation is pending when a stop is asserted, the

operation will be aborted. The master must have

control of SDA (not a memory read) in order to assert

a Stop condition.

Start Condition

A Start condition is indicated when the bus master

drives SDA from high to low while the SCL signal is

high. All read and write transactions begin with a Start

condition. An operation in progress can be aborted by

asserting a Start condition at any time. Aborting an

operation using the Start condition will ready the

FM24CL04B for a new operation.

If during operation the power supply drops below the

specified VDD minimum, the system should issue a

Start condition prior to performing another operation.

Data/Address Transfer

All data transfers (including addresses) take place

while the SCL signal is high. Except under the two

conditions described above, the SDA signal should not

change while SCL is high.

Acknowledge

The Acknowledge takes place after the 8th data bit has

been transferred in any transaction. During this state

the transmitter should release the SDA bus to allow the

receiver to drive it. The receiver drives the SDA signal

low to acknowledge receipt of the byte. If the receiver

does not drive SDA low, the condition is a No-

Acknowledge and the operation is aborted.

The receiver could fail to acknowledge for two distinct

reasons. First, if a byte transfer fails, the No-

Acknowledge ends the current operation so that the

device can be addressed again. This allows the last

byte to be recovered in the event of a communication

error. Second and most common, the receiver does not

Rev. 1.3

Feb. 2011

the

the

If

the

the data

last byte.

is needed,

acknowledge

to deliberately end an

operation. For example, during a read operation, the

FM24CL04B will continue to place data onto the bus

as long as the receiver sends acknowledges (and

clocks). When a read operation is complete and no

receiver must not

more data

acknowledge

receiver

acknowledges the last byte, this will cause the

FM24CL04B to attempt to drive the bus on the next

clock while the master is sending a new command

such as a Stop command.

Slave Address

The first byte that the FM24CL04B expects after a

start condition is the slave address. As shown in

Figure 4, the slave address contains the device type,

the device select, the page of memory to be

accessed, and a bit that specifies if the transaction is

a read or a write.

Bits 7-4 are the device type and should be set to

1010b for the FM24CL04B. The device type allows

other types of functions to reside on the 2-wire bus

within an identical address range. Bits 3-2 are the

device address. If bit 3 matches the A2 pin and bit 2

matches the A1 pin the device will be selected. Bit 1

is the page select. It specifies the 256-byte block of

memory that is targeted for the current operation. Bit

0 is the read/write bit. A 0 indicates a write

operation.

Word Address

After the FM24CL04B (as receiver) acknowledges

the slave ID, the master will place the word address

on the bus for a write operation. The word address is

the lower 8-bits of the address to be combined with

the 1-bit page select to specify exactly the byte to be

written. The complete 9-bit address is latched

internally.

Page 4 of 12

�

FM24CL04B

Figure 4. Slave Address

the FM24CL04B

increments

No word address occurs for a read operation. Reads

always use the lower 8-bits that are held internally in

the address latch and the 9th address bit is part of the

slave address. Reads always begin at the address

following the previous access. A random read address

can be loaded by doing a write operation as explained

below.

After transmission of each data byte, just prior to the

acknowledge,

the

internal address latch. This allows the next sequential

byte to be accessed with no additional addressing.

After the last address (1FFh) is reached, the address

latch will roll over to 000h. There is no limit to the

number of bytes that can be accessed with a single

read or write operation.

Data Transfer

After all address information has been transmitted,

data

the

FM24CL04B can begin. For a read operation the

FM24CL04B will place 8 data bits on the bus then

wait for an acknowledge. If the acknowledge occurs,

the next sequential byte will be transferred. If the

acknowledge is not sent, the read operation is

concluded. For a write operation, the FM24CL04B

will accept 8 data bits from the master then send an

acknowledge. All data transfer occurs MSB (most

significant bit) first.

the bus master and

transfer between

Memory Operation

The FM24CL04B is designed to operate in a manner

very similar to other 2-wire interface memory

products. The major differences result from the

higher performance write capability of FRAM

technology. These improvements result in some

differences between the FM24CL04B and a similar

configuration EEPROM during writes. The complete

operation for both writes and reads is explained

below.

Write Operation

All writes begin with a slave address then a word

address. The bus master indicates a write operation

by setting the LSB of the Slave address to a 0. After

addressing, the bus master sends each byte of data to

the memory and

the memory generates an

acknowledge condition. Any number of sequential

bytes may be written. If the end of the address range

is reached internally, the address counter will wrap

from 1FFh to 000h.

Unlike other nonvolatile memory technologies, there

is no write delay with FRAM. The entire memory

cycle occurs in less time than a single bus clock.

Therefore any operation including read or write can

occur immediately following a write. Acknowledge

polling, a

to

determine if a write is complete is unnecessary and

will always return a done condition.

An actual memory array write occurs after the 8th

data bit is transferred. It will be complete before the

acknowledge is sent. Therefore if the user desires to

abort a write without altering the memory contents,

this should be done using a start or stop condition

prior to the 8th data bit. The FM24CL04B needs no

page buffering.

Pulling write protect high will disable writes to the

entire array. The FM24CL04B will not acknowledge

data bytes that are written when write protect is

asserted. In addition, the address counter will not

increment if writes are attempted. Pulling WP low

(VSS) will deactivate this feature.

Figure 5 below illustrates both a single- and

multiple- byte write.

technique used with EEPROMs

Rev. 1.3

Feb. 2011

Page 5 of 12

�

By Master

Start

Address & Data

Stop

S

Slave Address

0

A

Word Address

A

Data Byte

A P

By FM24CL04B

Acknowledge

By Master

Start

Figure 5. Byte Write

Address & Data

FM24CL04B

Stop

S

Slave Address

0

A

Word Address

A

Data Byte

A

Data Byte

A P

By FM24CL04B

Acknowledge

Figure 6. Multiple Byte Write

Read Operation

There are two basic types of read operations. They are

current address read and selective address read. In a

current address read, the FM24CL04B uses the

internal address latch to supply the lower 8 address

bits. In a selective read, the user performs a procedure

to set these lower address bits to a specific value.

Current Address & Sequential Read

The FM24CL04B uses an internal latch to supply the

lower 8 address bits for a read operation. A current

address read uses the existing value in the address

latch as a starting place for the read operation. This is

the address immediately following that of the last

operation.

To perform a current address read, the bus master

supplies a slave address with the LSB set to 1. This

indicates that a read operation is requested. The page

select bit in the slave address specifies the block of

memory that is used for the read operation. After the

acknowledge, the FM24CL04B will begin shifting out

data from the current address. The current address is

the bit from the slave address combined with the 8 bits

that were in the internal address latch.

Beginning with the current address, the bus master can

read any number of bytes. Thus a sequential read is

simply a current address read with multiple byte

transfers. After each byte the internal address counter

will be incremented. Each time the bus master

acknowledges a byte,

the

FM24CL04B should read out the next sequential byte.

There are four ways to properly terminate a read

operation. Failing to properly terminate the read will

most likely create a bus contention as the FM24CL04B

indicates

that

this

attempts to read out additional data onto the bus. The

four valid methods are as follows.

1. The bus master issues a no-acknowledge in the

9th clock cycle and a stop in the 10th clock cycle.

This is illustrated in the diagrams below. This is

the preferred method.

2. The bus master issues a no-acknowledge in the

9th clock cycle and a start in the 10th.

3. The bus master issues a stop in the 9th clock

cycle. Bus contention may result.

4. The bus master issues a start in the 9th clock

cycle. Bus contention may result.

If the internal address reaches 1FFh it will wrap

around to 000h on the next read cycle. Figures 7 and

8 show the proper operation for current address reads.

Selective (Random) Read

A simple technique allows a user to select a random

address location as the starting point for a read

operation. This involves using the first two bytes of a

write operation to set the internal address byte

followed by subsequent read operations.

To perform a selective read, the bus master sends out

the slave address with the LSB set to 0. This specifies

a write operation. According to the write protocol, the

bus master then sends the word address byte that is

loaded into the internal address latch. After the

FM24CL04B acknowledges the word address, the bus

master issues a start condition. This simultaneously

aborts the write operation and allows the read

command to be issued with the slave address LSB set

to a 1. The operation is now a current address read.

See Figure 9.

Rev. 1.3

Feb. 2011

Page 6 of 12

�

FM24CL04B

Figure 7. Current Address Read

Figure 8. Sequential Read

Figure 9. Selective (Random) Read

Rev. 1.3

Feb. 2011

Page 7 of 12

�

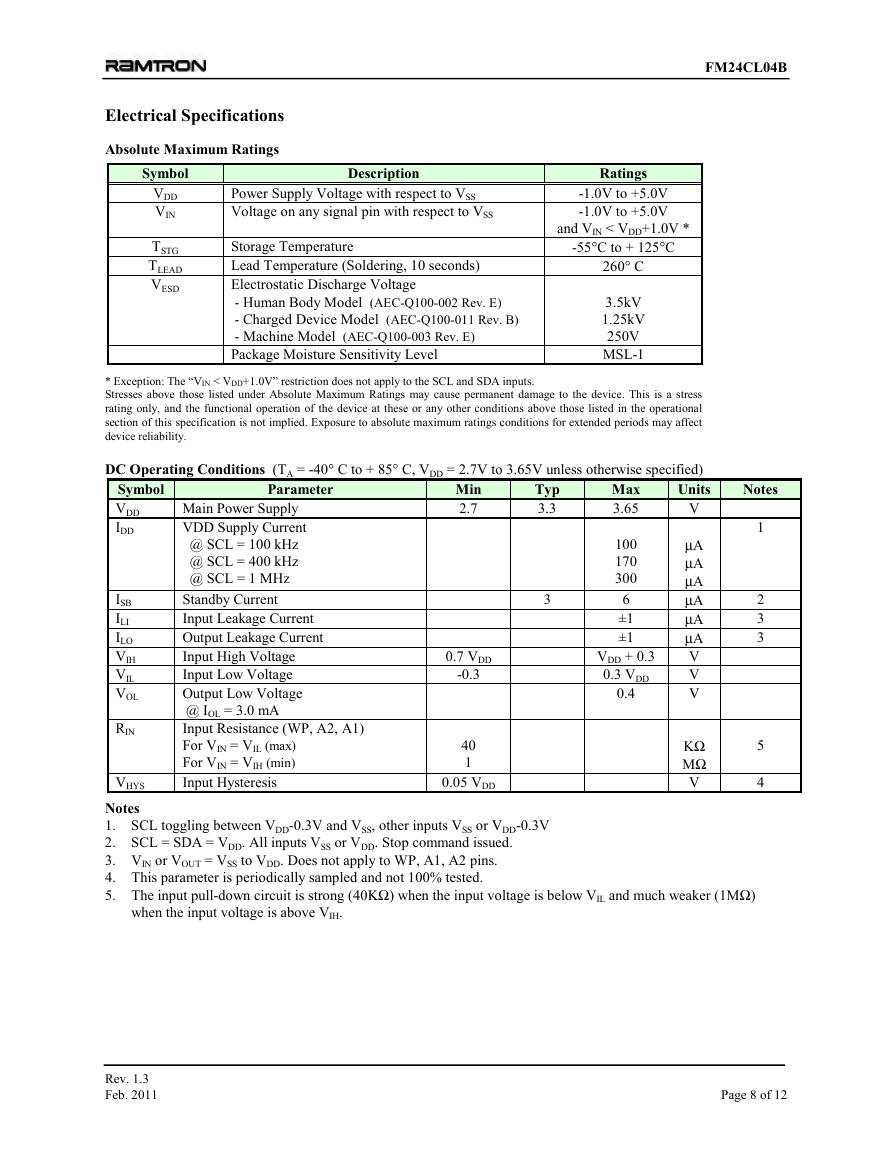

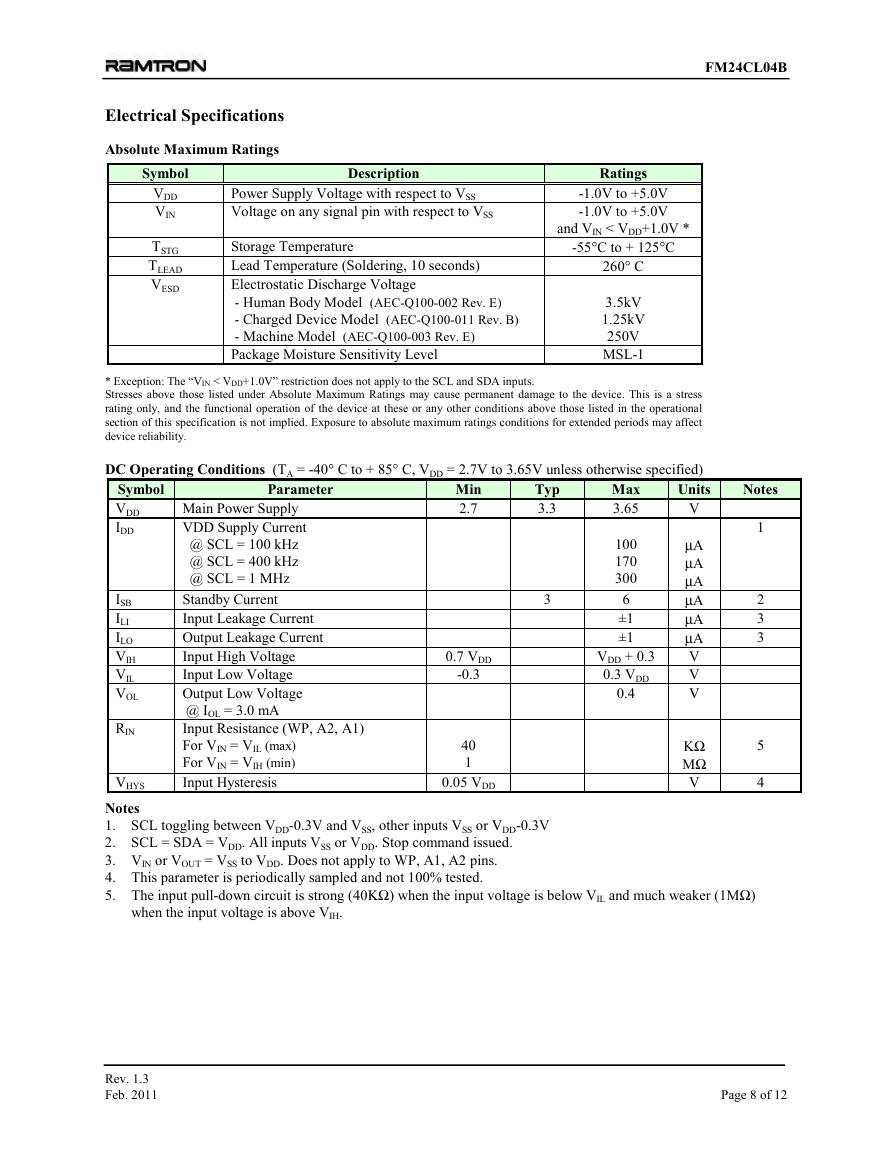

Electrical Specifications

FM24CL04B

Absolute Maximum Ratings

Symbol

VDD

VIN

TSTG

TLEAD

VESD

Description

Ratings

Power Supply Voltage with respect to VSS

Voltage on any signal pin with respect to VSS

Storage Temperature

Lead Temperature (Soldering, 10 seconds)

Electrostatic Discharge Voltage

- Human Body Model (AEC-Q100-002 Rev. E)

- Charged Device Model (AEC-Q100-011 Rev. B)

- Machine Model (AEC-Q100-003 Rev. E)

Package Moisture Sensitivity Level

-1.0V to +5.0V

-1.0V to +5.0V

and VIN < VDD+1.0V *

-55°C to + 125°C

260° C

3.5kV

1.25kV

250V

MSL-1

* Exception: The “VIN < VDD+1.0V” restriction does not apply to the SCL and SDA inputs.

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress

rating only, and the functional operation of the device at these or any other conditions above those listed in the operational

section of this specification is not implied. Exposure to absolute maximum ratings conditions for extended periods may affect

device reliability.

DC Operating Conditions (TA = -40° C to + 85° C, VDD = 2.7V to 3.65V unless otherwise specified)

Units

Parameter

0.05 VDD

VHYS

Notes

1. SCL toggling between VDD-0.3V and VSS, other inputs VSS or VDD-0.3V

2. SCL = SDA = VDD. All inputs VSS or VDD. Stop command issued.

3. VIN or VOUT = VSS to VDD. Does not apply to WP, A1, A2 pins.

4. This parameter is periodically sampled and not 100% tested.

5. The input pull-down circuit is strong (40KΩ) when the input voltage is below VIL and much weaker (1MΩ)

4

when the input voltage is above VIH.

Rev. 1.3

Feb. 2011

Page 8 of 12

Symbol

VDD

IDD

ISB

ILI

ILO

VIH

VIL

VOL

RIN

Main Power Supply

VDD Supply Current

@ SCL = 100 kHz

@ SCL = 400 kHz

@ SCL = 1 MHz

Standby Current

Input Leakage Current

Output Leakage Current

Input High Voltage

Input Low Voltage

Output Low Voltage

@ IOL = 3.0 mA

Input Resistance (WP, A2, A1)

For VIN = VIL (max)

For VIN = VIH (min)

Input Hysteresis

Min

2.7

Typ

3.3

3

0.7 VDD

-0.3

40

1

Max

3.65

100

170

300

6

±1

±1

VDD + 0.3

0.3 VDD

0.4

V

µA

µA

µA

µA

µA

µA

V

V

V

KΩ

MΩ

V

Notes

1

2

3

3

5

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf