November 2011

CYIV-51003-1.1

CYIV-51003-1.1

概述

3. Cyclone IV 器件中的存储器模块

Cyclone® IV 器件具有嵌入式存储器结构,满足了 Altera® Cyclone IV 器件设计对片上

存储器的需求。嵌入式存储器结构由一列列 M9K 存储器模块组成,通过对这些 M9K 存

储器模块进行配置,可以实现各种存储器功能,例如:RAM、移位寄存器、 ROM 以及

FIFO 缓冲器。

本应用笔记包含以下几部分内容:

■ “ 存储器模式 ”( 第 3-7 页 )

■ “ 时钟模式 ”( 第 3-14 页 )

■ “ 设计考量 ”( 第 3-15 页 )

M9K 存储器模块支持以下特性:

■ 每模块 8,192 个存储器位 ( 包括奇偶校验位,每模块共 9,216 位 )

■ 用于每一个端口的独立读使能 (rden) 与写使能 (wren) 信号

■ Packed 模式,该模式下 M9K 存储器模块被分成两个 4.5 K 单端口 RAM

■ 可变端口配置

■ 单端口与简单双端口模式,支持所有端口宽度

■ 真双端口 ( 一个读和一个写,两个读,或者两个写 ) 操作

■ 字节使能,实现写入期间的数据输入屏蔽

■ 用于每一个端口 ( 端口 A 和 B) 的时钟使能控制信号

■ 初始化文件,在 RAM 和 ROM 模式下预加载存储器中的数据

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 1

2011 年 11 月

Subscribe

�

3–2

第 3 章 :Cyclone IV 器件中的存储器模块

概述

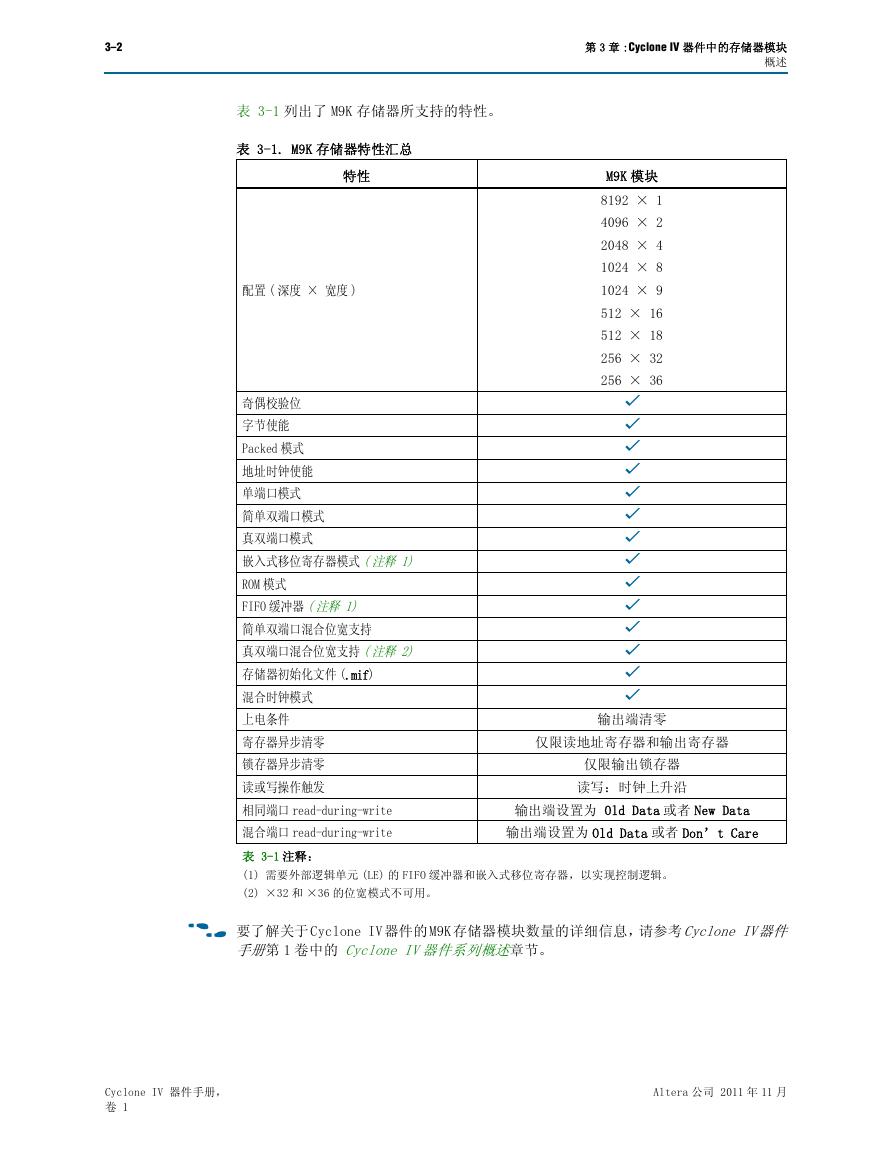

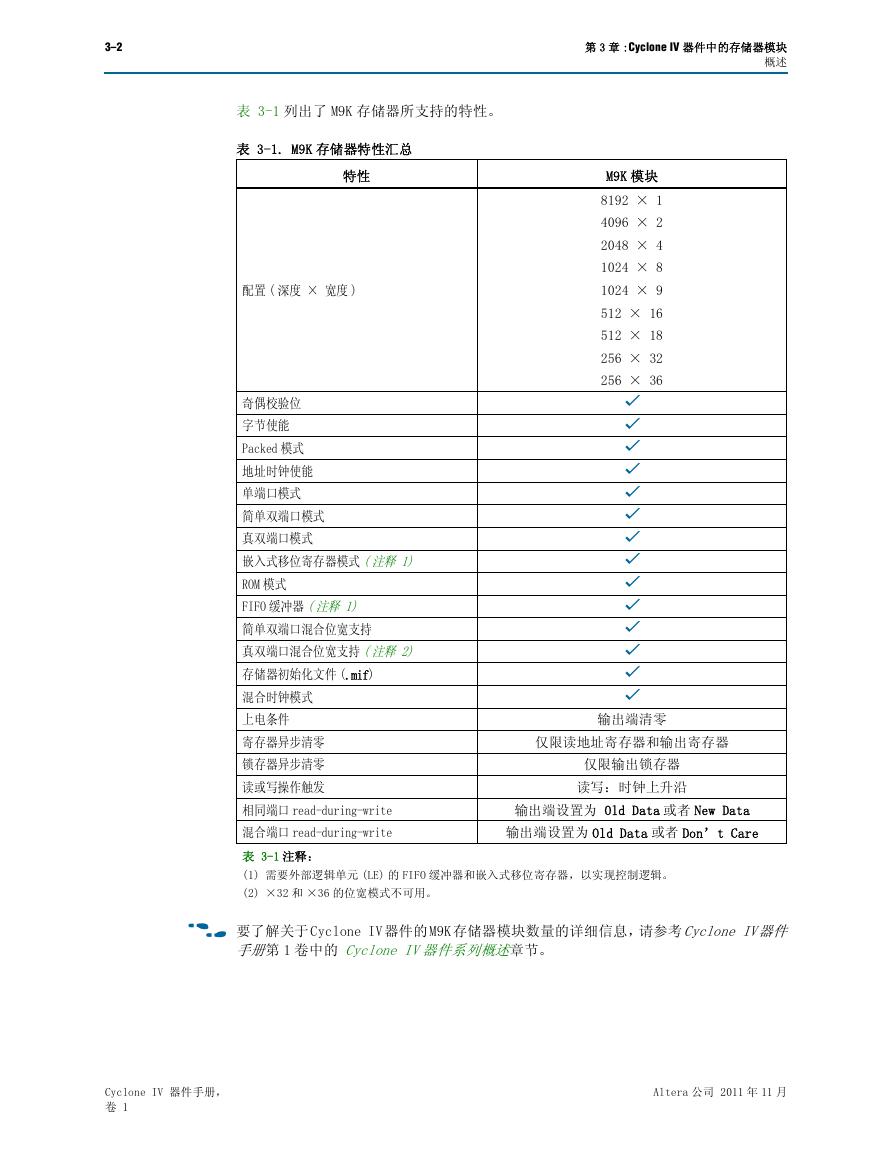

表 3-1 列出了 M9K 存储器所支持的特性。

表 3-1. M9K 存储器特性汇总

特性

配置 ( 深度 × 宽度 )

奇偶校验位

字节使能

Packed 模式

地址时钟使能

单端口模式

简单双端口模式

真双端口模式

嵌入式移位寄存器模式 (注释 1)

ROM 模式

FIFO 缓冲器 (注释 1)

简单双端口混合位宽支持

真双端口混合位宽支持 (注释 2)

存储器初始化文件 (.mif)

混合时钟模式

上电条件

寄存器异步清零

锁存器异步清零

读或写操作触发

相同端口 read-during-write

混合端口 read-during-write

表 3-1 注释:

M9K 模块

8192 × 1

4096 × 2

2048 × 4

1024 × 8

1024 × 9

512 × 16

512 × 18

256 × 32

256 × 36

v

v

v

v

v

v

v

v

v

v

v

v

v

v

输出端清零

仅限读地址寄存器和输出寄存器

仅限输出锁存器

读写:时钟上升沿

输出端设置为 Old Data 或者 New Data

输出端设置为 Old Data 或者 Don’t Care

(1) 需要外部逻辑单元 (LE) 的 FIFO 缓冲器和嵌入式移位寄存器,以实现控制逻辑。

(2) ×32 和 ×36 的位宽模式不可用。

f 要了解关于 Cyclone IV 器件的 M9K 存储器模块数量的详细信息,请参考Cyclone IV器件

手册第 1 卷中的 Cyclone IV器件系列概述章节。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 3 章 :Cyclone IV 器件中的存储器模块

概述

控制信号

3–3

时钟使能控制信号对进入输入与输出寄存器的时钟以及整个 M9K 存储器模块进行控制。

该信号将时钟禁用,使 M9K 存储器模块侦测不到任何的时钟边沿,从而不会执行任何

操作。

rden 与 wren 控制信号控制 M9K 存储器模块的每一个端口上的读写操作。当不需要操作

时,您可以分别将 rden 或者 wren 信号禁用,从而降低功耗。

奇偶校验位支持

通过奇偶校验位以及内部逻辑资源,用于错误检测的奇偶校验检查是可以实现的。

Cyclone IV 器件 M9K 存储器模块支持每一个存储字节含有一个奇偶校验位,您可以将

该位用作奇偶校验位或者额外的数据位。实际上,该位不执行奇偶校验功能。

字节使能支持

Cyclone IV 器件 M9K 存储器模块支持字节使能,该功能屏蔽了输入数据,这样仅写入

数据中的指定字节。未被写入的字节保留之前写入的值。 wren 信号以及字节使能

(byteena) 信号一起控制 RAM 模块的写操作。 byteena 信号默认为高电平 ( 使能的 ),

这种情况下写操作仅由 wren 信号来控制。 byteena 寄存器的清零端口是不存在的。当

写端口具有 ×16, ×18, ×32, 或者 ×36 位数据位宽时,M9K 模块将支持字节使能。

字节使能以独热码的形式运行,并且 byteena 的最低位对应于数据总线的最低字节。

例如,若 byteena = 01,并且在 ×18 模式下使用一个 RAM 模块,则 data[8..0] 被使

能,而 data[17..9] 被禁用。同样地,若 byteena = 11, 则 data[8..0] 以及

data[17..9] 均被使能。字节使能为高电平有效。

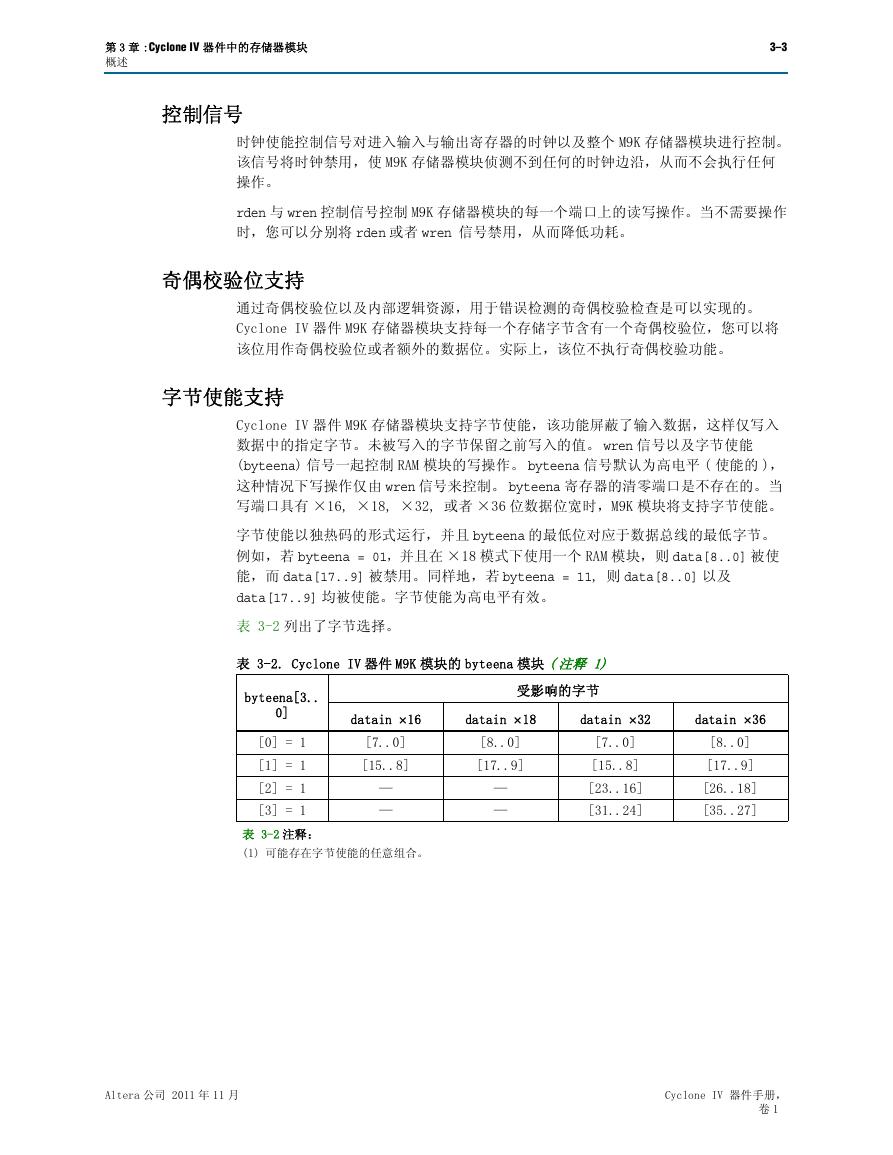

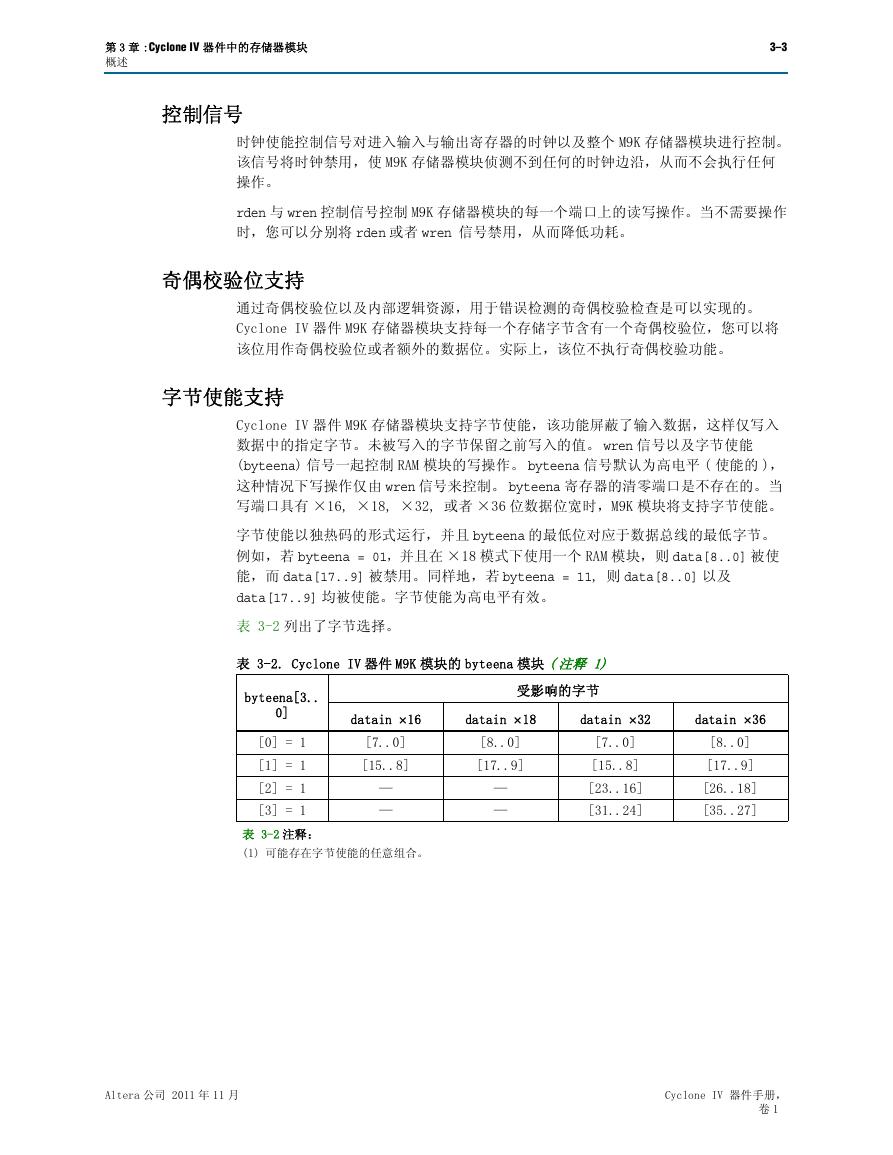

表 3-2 列出了字节选择。

表 3-2. Cyclone IV 器件 M9K 模块的 byteena 模块 (注释 1)

byteena[3..

0]

[0] = 1

[1] = 1

[2] = 1

[3] = 1

受影响的字节

datain ×16

datain ×18

datain ×32

datain ×36

[7..0]

[15..8]

—

—

[8..0]

[17..9]

—

—

[7..0]

[15..8]

[23..16]

[31..24]

[8..0]

[17..9]

[26..18]

[35..27]

表 3-2 注释:

(1) 可能存在字节使能的任意组合。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

3–4

第 3 章 :Cyclone IV 器件中的存储器模块

概述

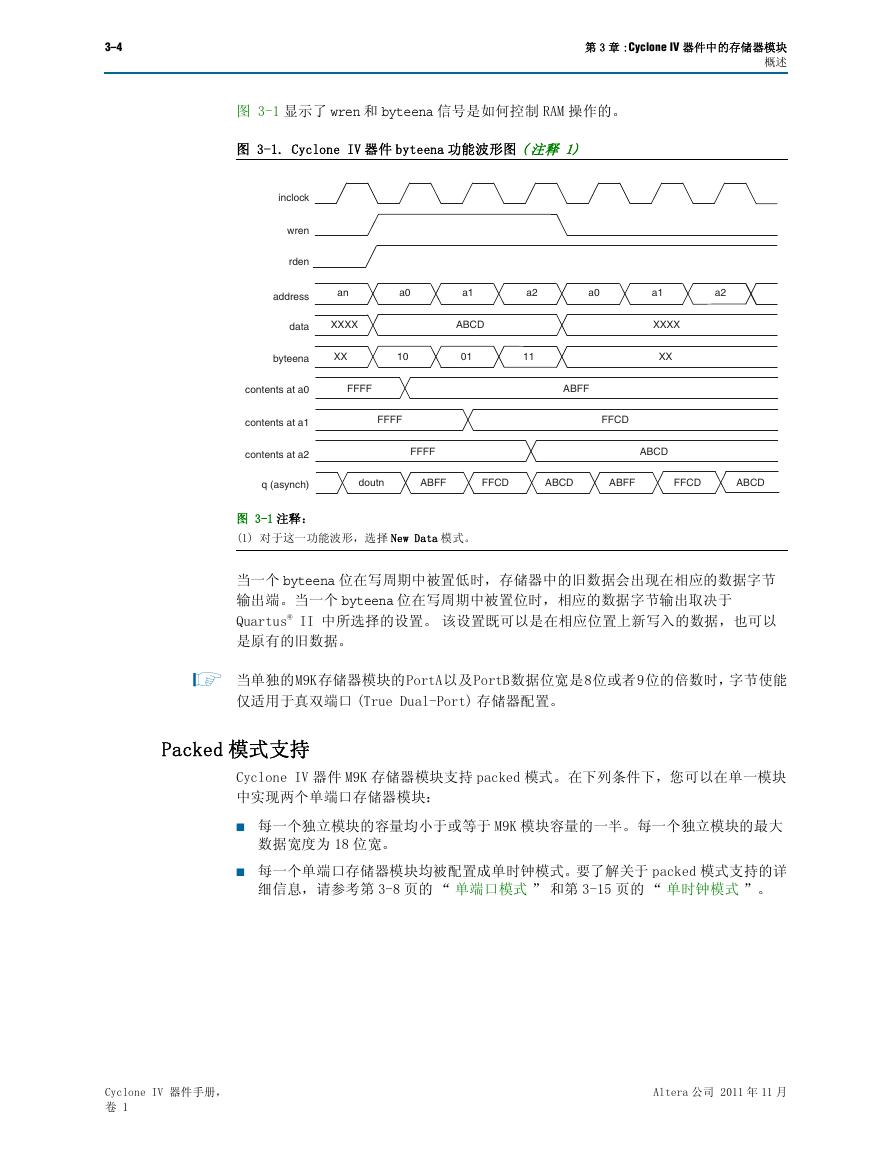

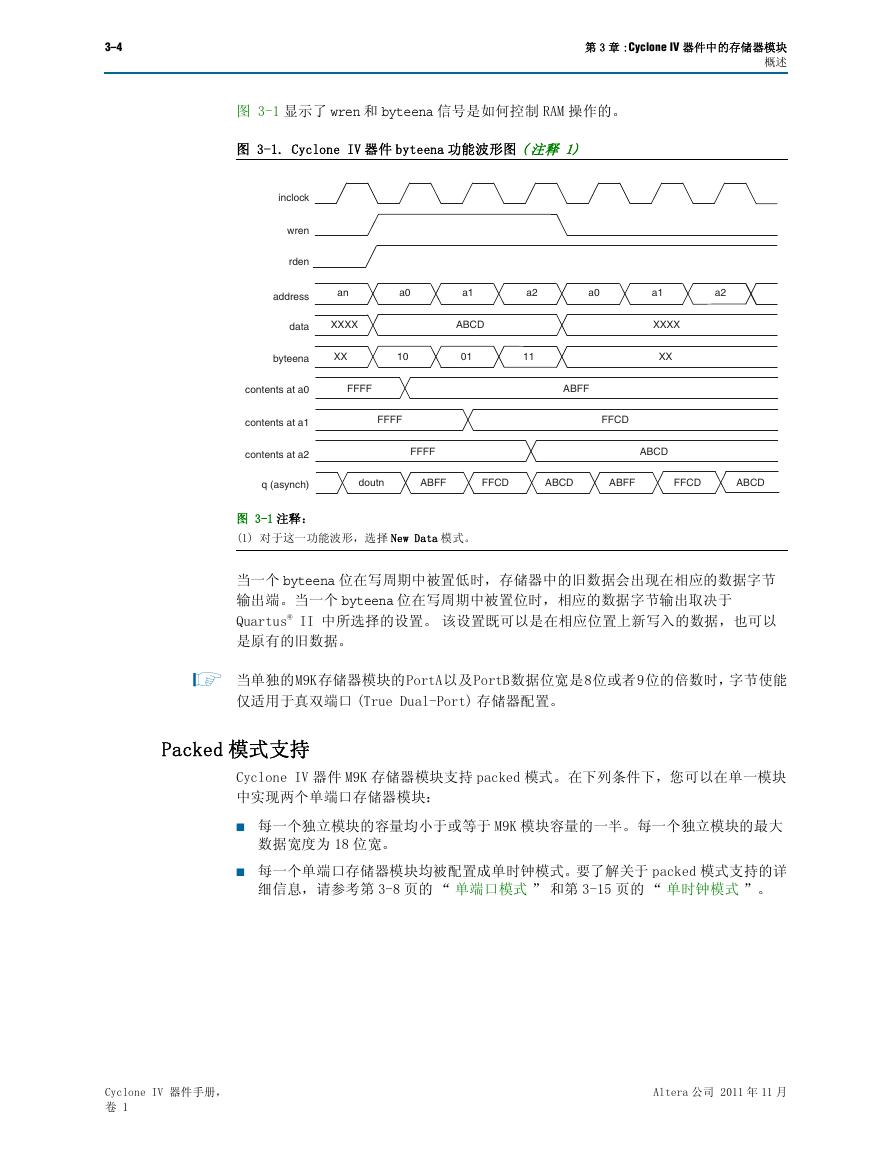

图 3-1 显示了 wren 和 byteena 信号是如何控制 RAM 操作的。

图 3-1. Cyclone IV 器件 byteena 功能波形图 (注释 1)

inclock

wren

rden

address

an

a0

a1

a2

a0

a1

a2

data

XXXX

ABCD

byteena

XX

10

01

11

XXXX

XX

contents at a0

FFFF

contents at a1

FFFF

ABFF

FFCD

contents at a2

q (asynch)

图 3-1 注释:

FFFF

ABCD

doutn

ABFF

FFCD

ABCD

ABFF

FFCD

ABCD

(1) 对于这一功能波形,选择 New Data 模式。

当一个 byteena 位在写周期中被置低时,存储器中的旧数据会出现在相应的数据字节

输出端。当一个 byteena 位在写周期中被置位时,相应的数据字节输出取决于

Quartus® II 中所选择的设置。 该设置既可以是在相应位置上新写入的数据,也可以

是原有的旧数据。

1 当单独的M9K存储器模块的PortA以及PortB数据位宽是8位或者9位的倍数时,字节使能

仅适用于真双端口 (True Dual-Port) 存储器配置。

Packed 模式支持

Cyclone IV 器件 M9K 存储器模块支持 packed 模式。在下列条件下,您可以在单一模块

中实现两个单端口存储器模块:

■ 每一个独立模块的容量均小于或等于 M9K 模块容量的一半。每一个独立模块的最大

数据宽度为 18 位宽。

■ 每一个单端口存储器模块均被配置成单时钟模式。要了解关于 packed 模式支持的详

细信息,请参考第 3-8 页的 “ 单端口模式 ” 和第 3-15 页的 “ 单时钟模式 ”。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 3 章 :Cyclone IV 器件中的存储器模块

概述

地址时钟使能支持

3–5

Cyclone IV 器件 M9K 存储器模块支持低电平有效地址时钟使能,只要 addressstall

信号为高电平 (addressstall = '1'),低电平有效地址时钟使能就会保持之前的地址

值。 当在双端口模式下配置 M9K 存储器模块时,每个端口都有各自独立的地址时钟使

能。

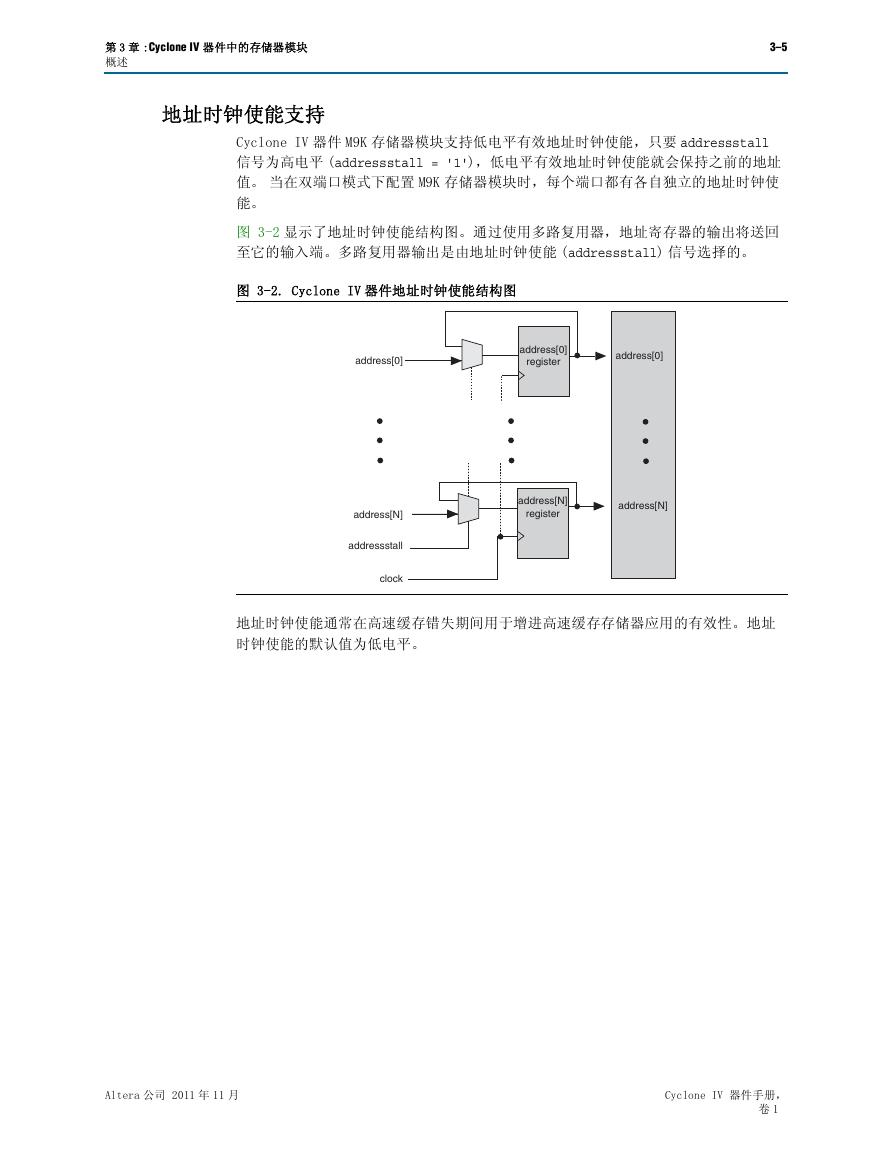

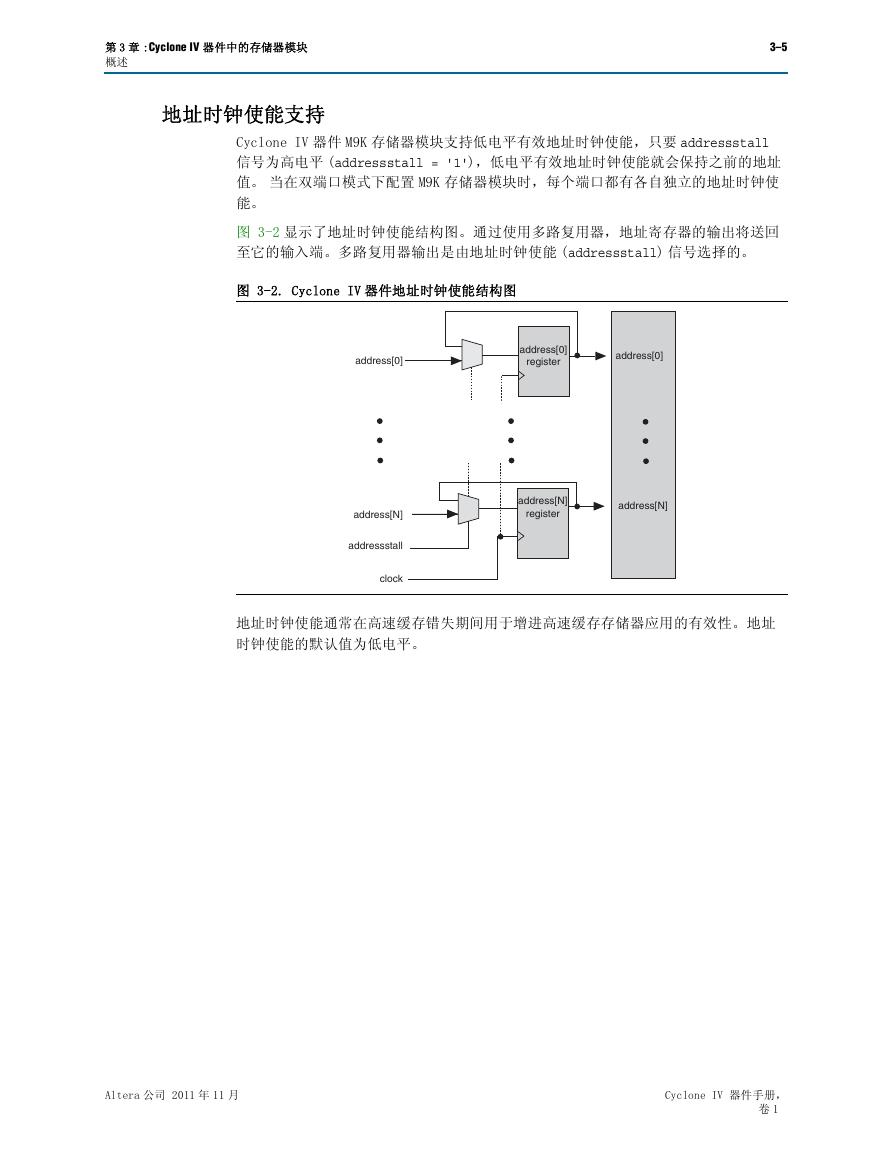

图 3-2 显示了地址时钟使能结构图。通过使用多路复用器,地址寄存器的输出将送回

至它的输入端。多路复用器输出是由地址时钟使能 (addressstall) 信号选择的。

图 3-2. Cyclone IV 器件地址时钟使能结构图

address[0]

address[0]

register

address[0]

address[N]

register

address[N]

address[N]

addressstall

clock

地址时钟使能通常在高速缓存错失期间用于增进高速缓存存储器应用的有效性。地址

时钟使能的默认值为低电平。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

3–6

第 3 章 :Cyclone IV 器件中的存储器模块

概述

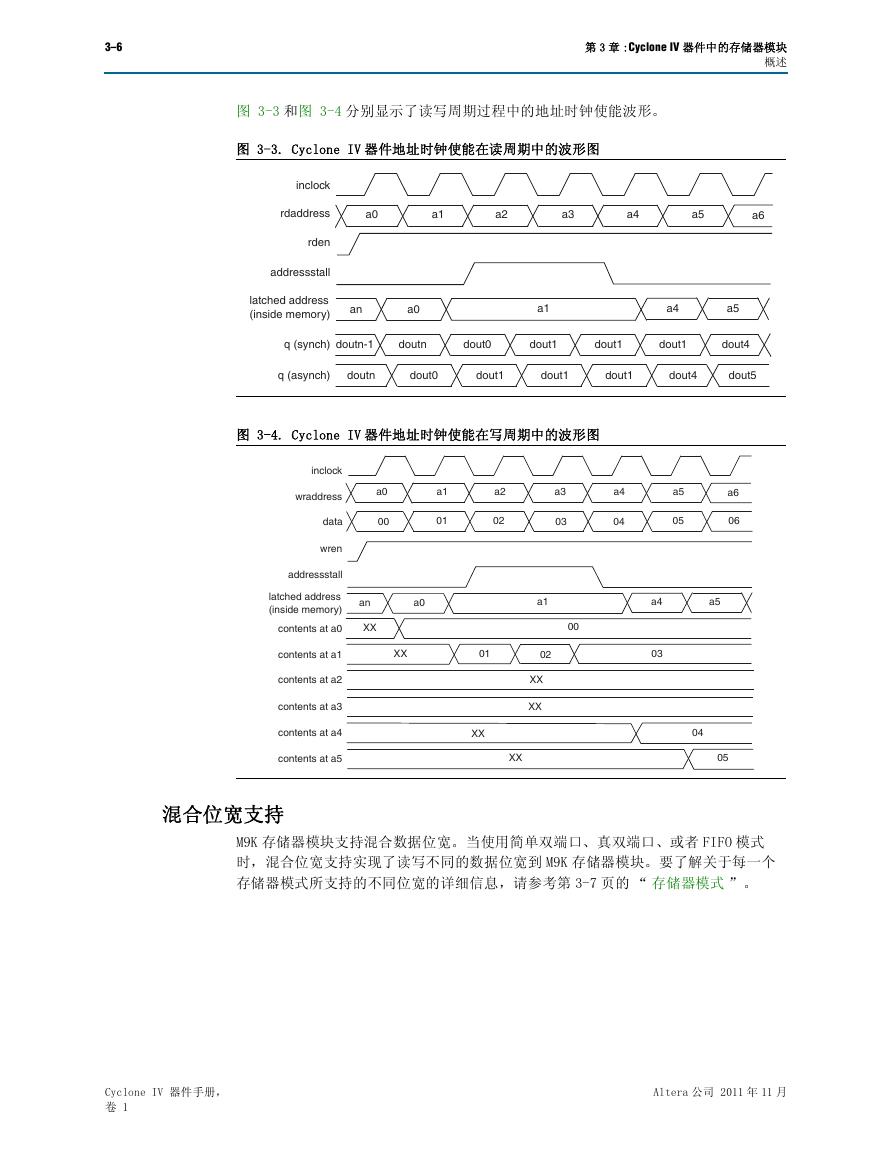

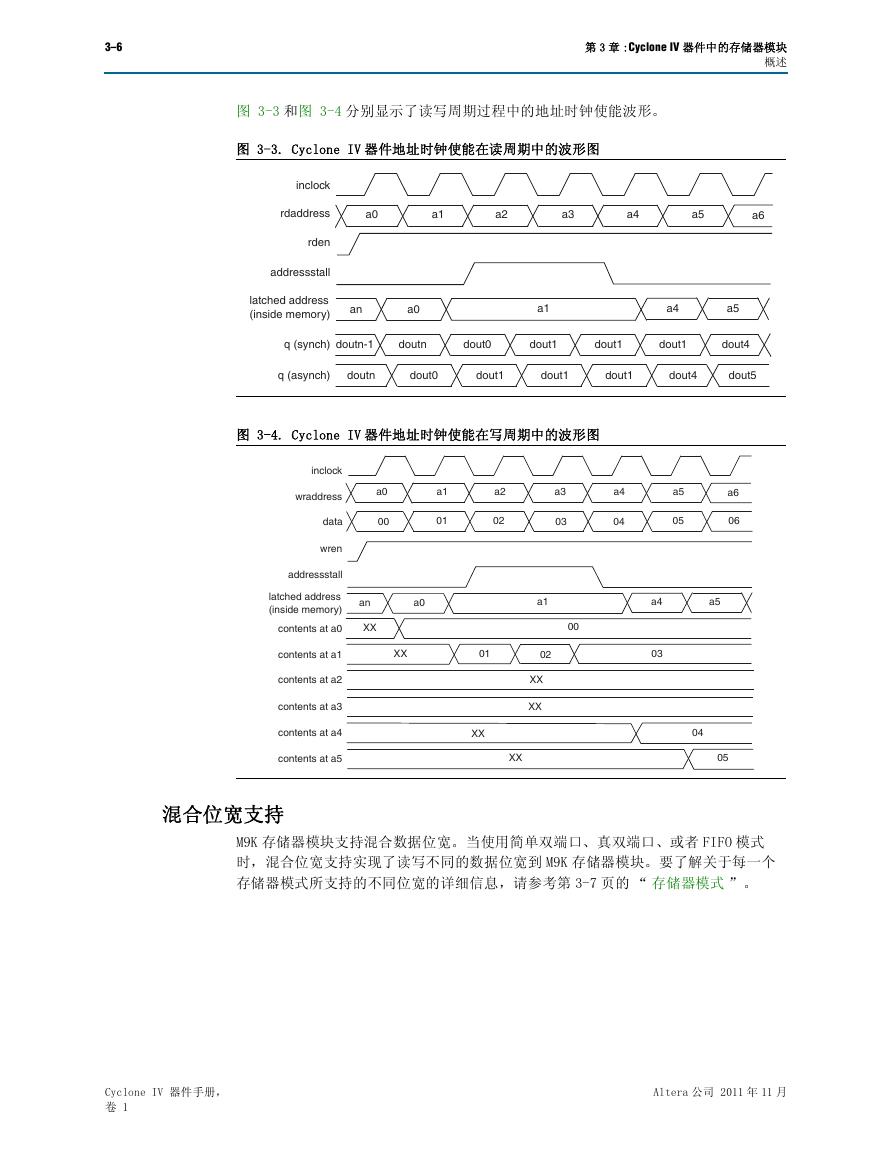

图 3-3 和图 3-4 分别显示了读写周期过程中的地址时钟使能波形。

图 3-3. Cyclone IV 器件地址时钟使能在读周期中的波形图

inclock

rdaddress

a0

a1

a2

a3

a4

a5

a6

rden

addressstall

latched address

(inside memory)

an

a0

a1

a4

a5

q (synch)

doutn-1

doutn

dout0

dout1

dout1

dout1

dout4

q (asynch)

doutn

dout0

dout1

dout1

dout1

dout4

dout5

图 3-4. Cyclone IV 器件地址时钟使能在写周期中的波形图

inclock

wraddress

data

wren

a0

00

a1

01

a2

02

a3

03

a4

04

a5

05

a6

06

addressstall

latched address

(inside memory)

an

a0

contents at a0

XX

a1

00

contents at a1

XX

01

02

contents at a2

contents at a3

contents at a4

contents at a5

XX

XX

XX

XX

a5

a4

03

04

05

混合位宽支持

M9K 存储器模块支持混合数据位宽。当使用简单双端口、真双端口、或者 FIFO 模式

时,混合位宽支持实现了读写不同的数据位宽到 M9K 存储器模块。要了解关于每一个

存储器模式所支持的不同位宽的详细信息,请参考第 3-7 页的 “ 存储器模式 ”。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 3 章 :Cyclone IV 器件中的存储器模块

存储器模式

异步清零

3–7

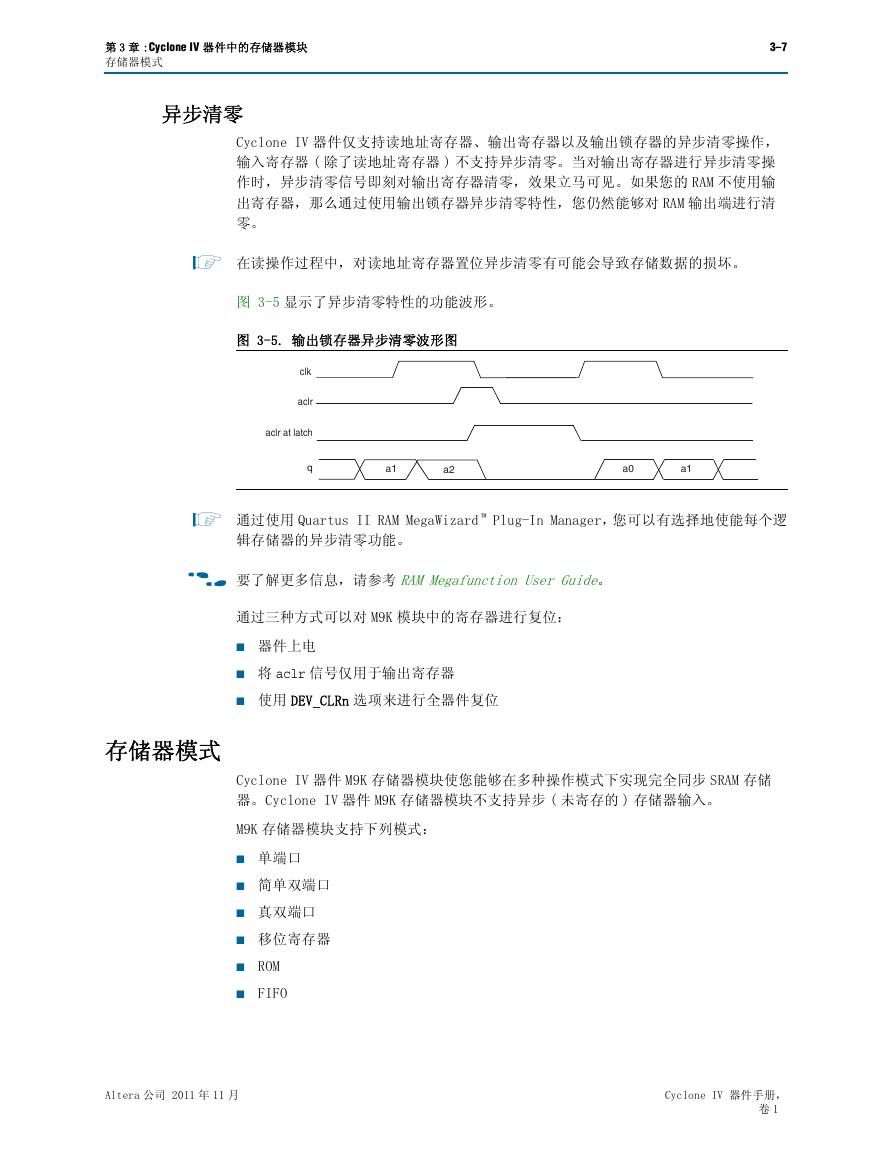

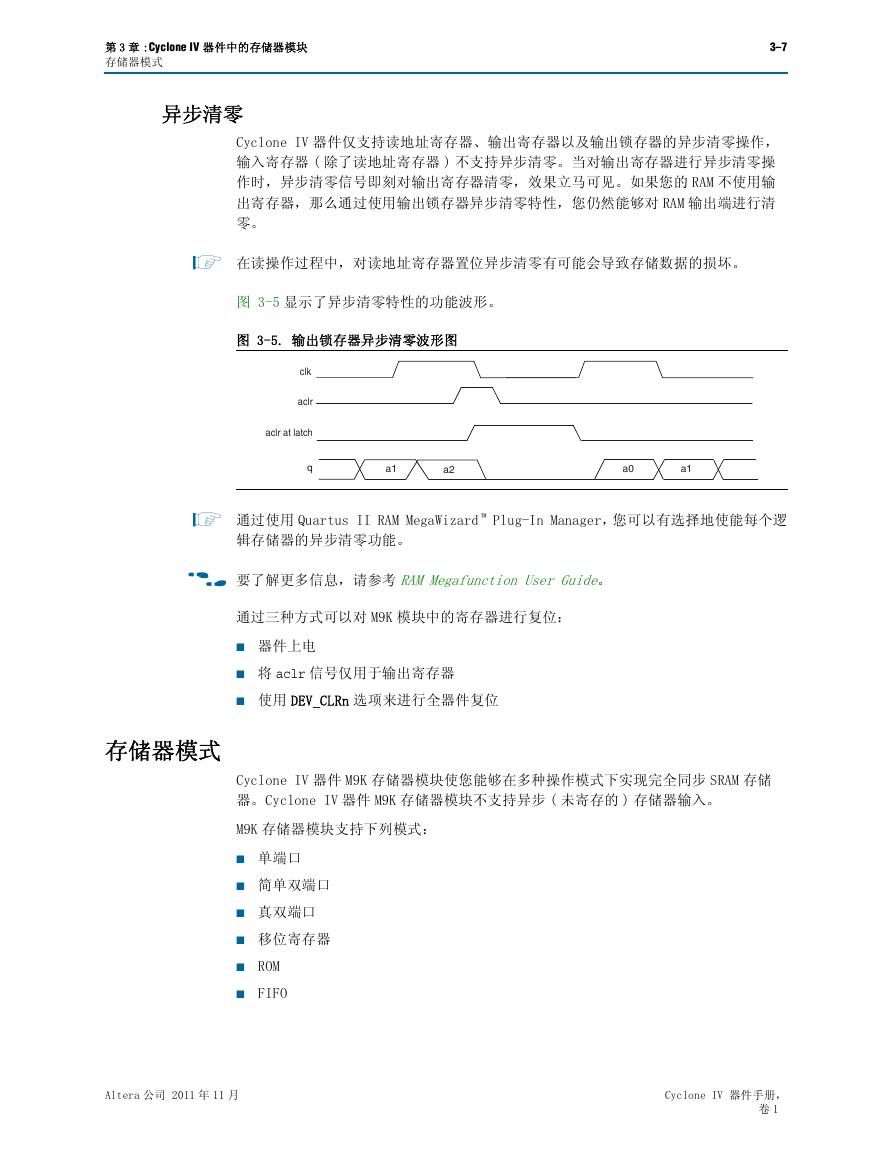

Cyclone IV 器件仅支持读地址寄存器、输出寄存器以及输出锁存器的异步清零操作,

输入寄存器 ( 除了读地址寄存器 ) 不支持异步清零。当对输出寄存器进行异步清零操

作时,异步清零信号即刻对输出寄存器清零,效果立马可见。如果您的 RAM 不使用输

出寄存器,那么通过使用输出锁存器异步清零特性,您仍然能够对 RAM 输出端进行清

零。

1 在读操作过程中,对读地址寄存器置位异步清零有可能会导致存储数据的损坏。

图 3-5 显示了异步清零特性的功能波形。

图 3-5. 输出锁存器异步清零波形图

clk

aclr

aclr at latch

q

a1

a2

a0

a1

1 通过使用 Quartus II RAM MegaWizard ™ Plug-In Manager,您可以有选择地使能每个逻

辑存储器的异步清零功能。

f 要了解更多信息,请参考 RAM Megafunction User Guide。

通过三种方式可以对 M9K 模块中的寄存器进行复位:

■ 器件上电

■ 将 aclr 信号仅用于输出寄存器

■ 使用 DEV_CLRn 选项来进行全器件复位

存储器模式

Cyclone IV 器件 M9K 存储器模块使您能够在多种操作模式下实现完全同步 SRAM 存储

器。Cyclone IV 器件 M9K 存储器模块不支持异步 ( 未寄存的 ) 存储器输入。

M9K 存储器模块支持下列模式:

■ 单端口

■ 简单双端口

■ 真双端口

■ 移位寄存器

■ ROM

■ FIFO

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

3–8

第 3 章 :Cyclone IV 器件中的存储器模块

存储器模式

1 M9K 存储器模块输入寄存器上建立及保持时间的违规将可能导致存储器数据的损坏,这

种情况会发生在读写操作期间。

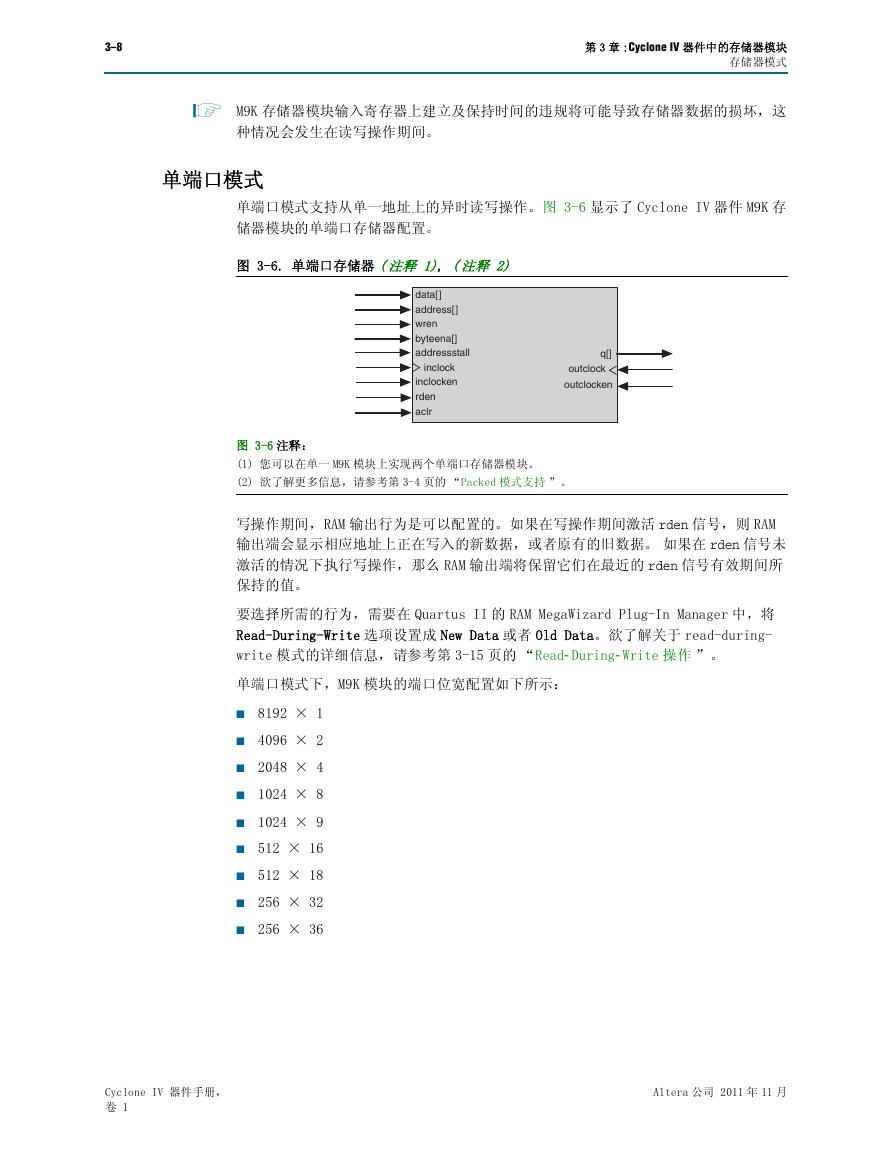

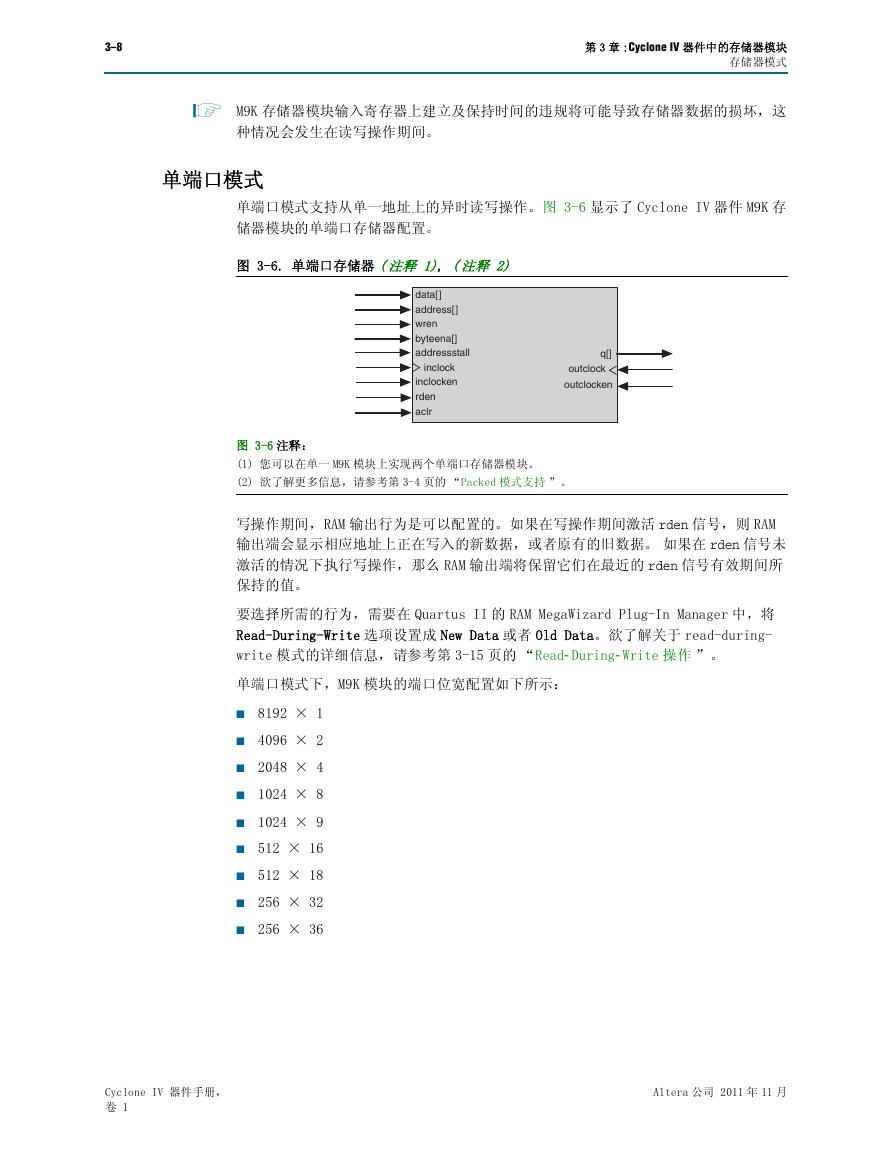

单端口模式

单端口模式支持从单一地址上的异时读写操作。图 3-6 显示了 Cyclone IV 器件 M9K 存

储器模块的单端口存储器配置。

图 3-6. 单端口存储器 (注释 1), (注释 2)

data[ ]

address[ ]

wren

byteena[]

addressstall

inclock

inclocken

rden

aclr

q[]

outclock

outclocken

图 3-6 注释:

(1) 您可以在单一 M9K 模块上实现两个单端口存储器模块。

(2) 欲了解更多信息,请参考第 3-4 页的 “Packed 模式支持 ”。

写操作期间,RAM 输出行为是可以配置的。如果在写操作期间激活 rden 信号,则 RAM

输出端会显示相应地址上正在写入的新数据,或者原有的旧数据。 如果在 rden 信号未

激活的情况下执行写操作,那么 RAM 输出端将保留它们在最近的 rden 信号有效期间所

保持的值。

要选择所需的行为,需要在 Quartus II 的 RAM MegaWizard Plug-In Manager 中,将

Read-During-Write 选项设置成 New Data 或者 Old Data。欲了解关于 read-during-

write 模式的详细信息,请参考第 3-15 页的 “Read- During- Write 操作 ”。

单端口模式下,M9K 模块的端口位宽配置如下所示:

■ 8192 × 1

■ 4096 × 2

■ 2048 × 4

■ 1024 × 8

■ 1024 × 9

■ 512 × 16

■ 512 × 18

■ 256 × 32

■ 256 × 36

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf