1. Cyclone IV FPGA 器件系列概述

November 2011

CYIV-51001-1.5

CYIV-51001-1.5

Altera 新的 Cyclone® IV 系列 FPGA 器件巩固了 Cyclone 系列在低成本、低功耗 FPGA

市场的领导地位,并且目前提供集成收发器功能的型号。Cyclone IV 器件旨在用于大

批量,成本敏感的应用,使系统设计师在降低成本的同时又能够满足不断增长的带宽

要求。

Cyclone IV 器件系列是建立在一个优化的低功耗工艺基础之上,并提供以下两种型

号:

■ Cyclone IV E— 最低的功耗,通过最低的成本实现较高的功能性

■ Cyclone IV GX— 最低的功耗,集成了 3.125 Gbps 收发器的最低成本的 FPGA

1 Cyclone IV E 器件可以在 1.0 V 和 1.2 V 核电压下使用。

f 欲了解详细信息,请参考 Power Requirements for Cyclone IV Devices章

节。

Cyclone IV 器件集成了一个可选择的低成本收发器,在未影响性能的情况下,节省了

功耗及成本。针对无线、有线、广播、工业,用户以及通信等行业中的低成本的小型

应用,Cyclone IV 器件无疑是最理想的选择。

Cyclone IV 器件系列特性

Cyclone IV 器件系列具有以下特性:

■ 低成本、低功耗的 FPGA 架构:

■

6 K 到 150 K 的逻辑单元

■ 高达 6.3 Mb 的嵌入式存储器

■ 高达 360 个 18 × 18 乘法器,实现 DSP 处理密集型应用

■ 协议桥接应用,实现小于 1.5 W 的总功耗

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 1

2011 年 11 月

Subscribe

�

1–2

第 1 章 :Cyclone IV FPGA 器件系列概述

Cyclone IV 器件系列特性

■ Cyclone IV GX 器件提供高达八个高速收发器以支持:

■ 高达 3.125 Gbps 的数据速率

■

■

8B/10B 编码器 / 解码器

8-bit 或者 10-bit 位物理介质附加子层 (PMA) 到物理编码子层 (PCS) 接口

■ 字节串化器 / 解串器 (SERDES)

■ 字对齐器

■ 速率匹配 FIFO

■ 公共无线电接口 (CPRI) 的 TX 位滑块

■ 电路空闲

■ 动态通道重配置以实现数据速率及协议的即时修改

■ 静态均衡及预加重以实现最佳的信号完整性

■ 每通道 150 mW 的功耗

■ 灵活的时钟结构以支持单一收发器模块中的多种协议

■ Cyclone IV GX 器件对 PCI Express (PIPE)(PCIe)Gen 1 提供了专用的硬核 IP:

■ ×1,×2, 和 ×4 通道配置

■ 终点和根端口配置

■ 高达 256-byte 的有效负载

■ 一个虚拟通道

■

■

2 KB 重试缓存

4 KB 接收 (Rx) 缓存

■ Cyclone IV GX 器件提供多种协议支持:

■

PCIe (PIPE) Gen 1×1,×2, 和 ×4 (2.5 Gbps)

■ 千兆以太网 (1.25 Gbps)

■

■

CPRI ( 高达 3.072 Gbps)

XAUI (3.125 Gbps)

■ 三倍速率串行数字接口 (SDI)( 高达 2.97 Gbps)

■ 串行 RapidIO(3.125 Gbps)

■

■

■

Basic 模式 ( 高达 3.125 Gbps)

V-by-One( 高达 3.0 Gbps)

DisplayPort(2.7 Gbps)

■ 串行高级技术附件 (Serial Advanced Technology Attachment (SATA))( 高达

3.0 Gbps)

■

OBSAI( 高达 3.072 Gbps)

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 1 章 :Cyclone IV FPGA 器件系列概述

器件资源

1–3

■ 高达 532 个用户 I/O

■ 高达 840 Mbps 发送器 (Tx), 875 Mbps Rx 的 LVDS 接口

■ 支持高达 200 MHz 的 DDR2 SDRAM 接口

■ 支持高达 167 MHz 的 QDRII SRAM 和 DDR SDRAM

■ 每器件中高达 8 个锁相环 (PLLs)

■ 支持商业与工业温度等级

器件资源

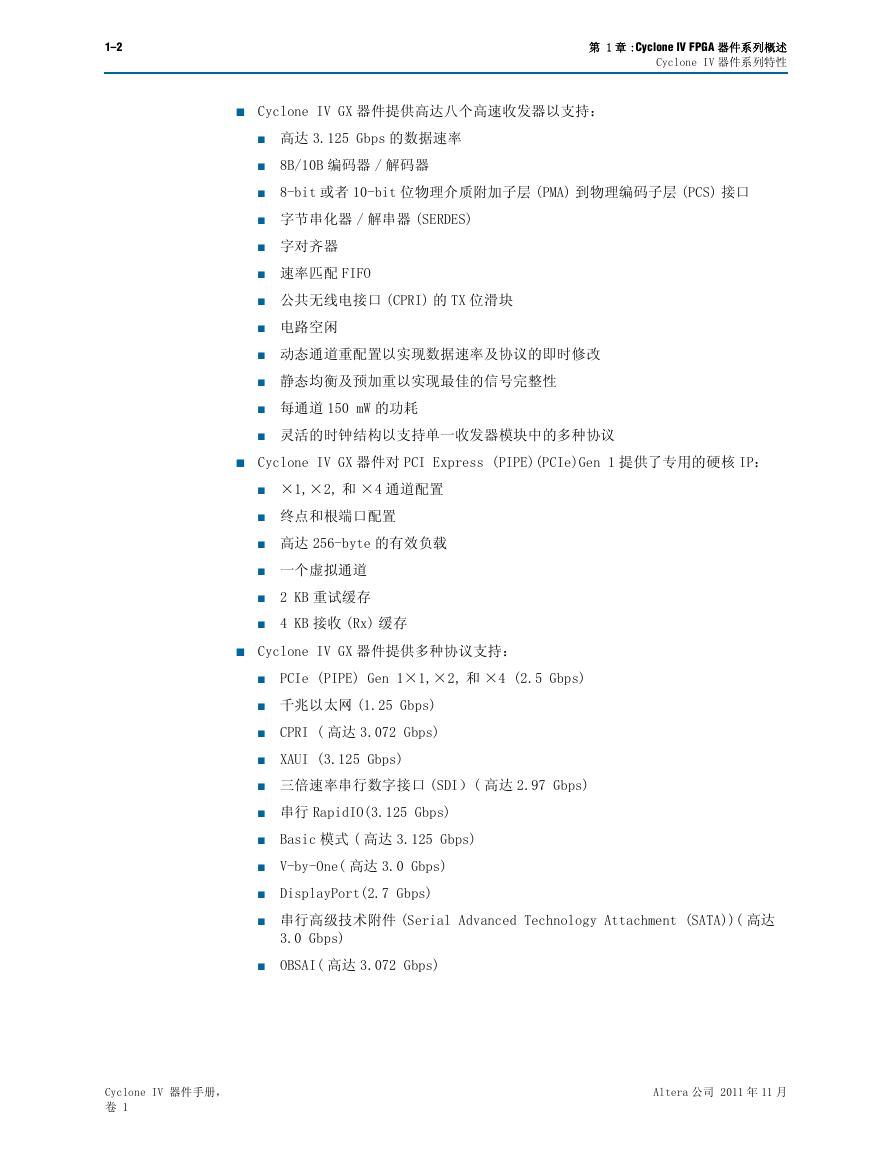

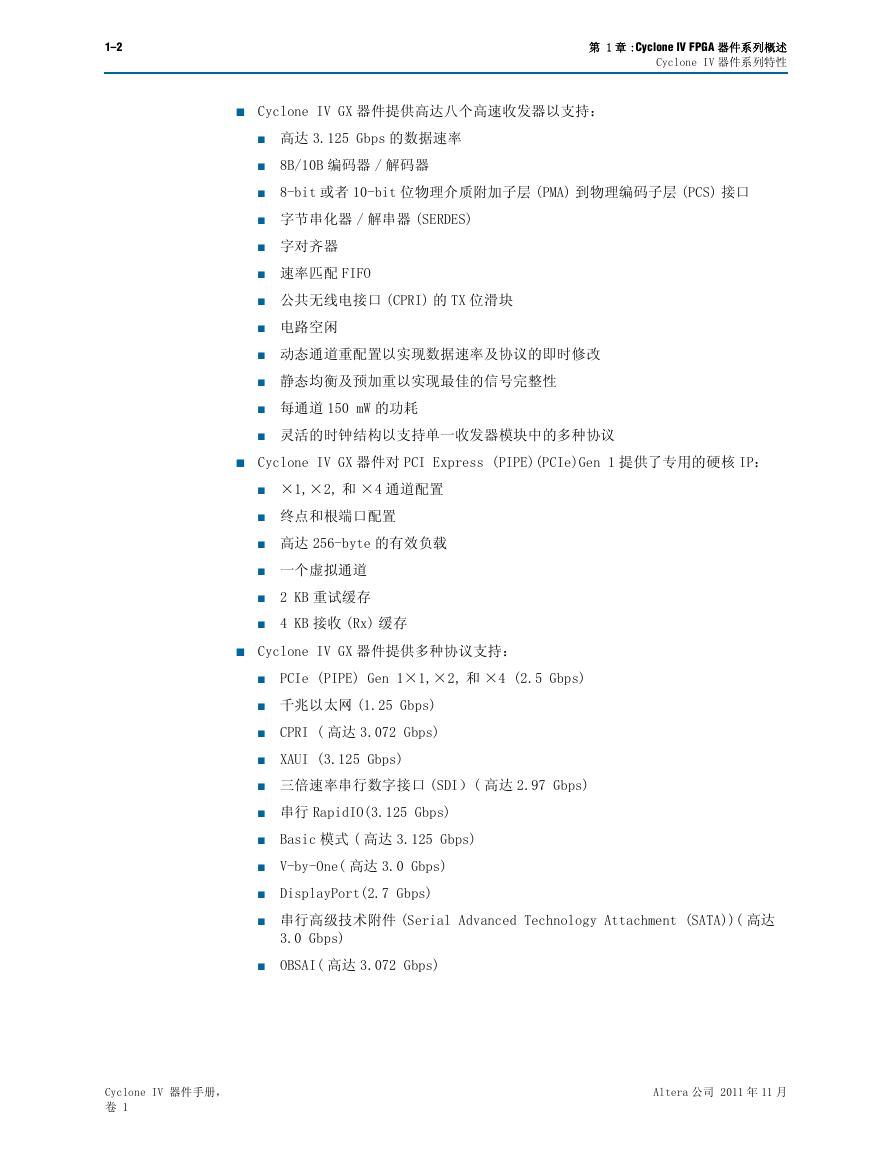

表 1-1 列出了 Cyclone IV E 器件资源。

表 1-1. Cyclone IV E 器件系列资源

资源

6

E

C

4

P

E

0

1

E

C

4

P

E

5

1

E

C

4

P

E

2

2

E

C

4

P

E

0

3

E

C

4

P

E

0

4

E

C

4

P

E

5

5

E

C

4

P

E

5

7

E

C

4

P

E

5

1

1

E

C

4

P

E

逻辑单元 (LE)

6,272

10,320

15,408

22,320

28,848

39,600

55,856

75,408

114,480

嵌入式存储器 (Kbits)

270

414

504

594

594

1,134

2,340

2,745

3,888

嵌入式 18 × 18 乘法器

通用 PLL

全局时钟网络

用户 I/O 块

最大用户 I/O

(注释 1)

表 1-1 注释:

15

2

10

8

23

2

10

8

56

4

20

8

66

4

20

8

66

4

20

8

116

154

200

4

20

8

4

20

8

4

20

8

179

179

343

153

532

532

374

426

266

4

20

8

528

(1) 管脚列表文件中的用户 I/O 管脚包括所有的通用 I/O 管脚、专用时钟管脚以及两用配置管脚。收发器管脚和专用配置管脚不包

括在这一管脚列表中。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

1–4

第 1 章 :Cyclone IV FPGA 器件系列概述

器件资源

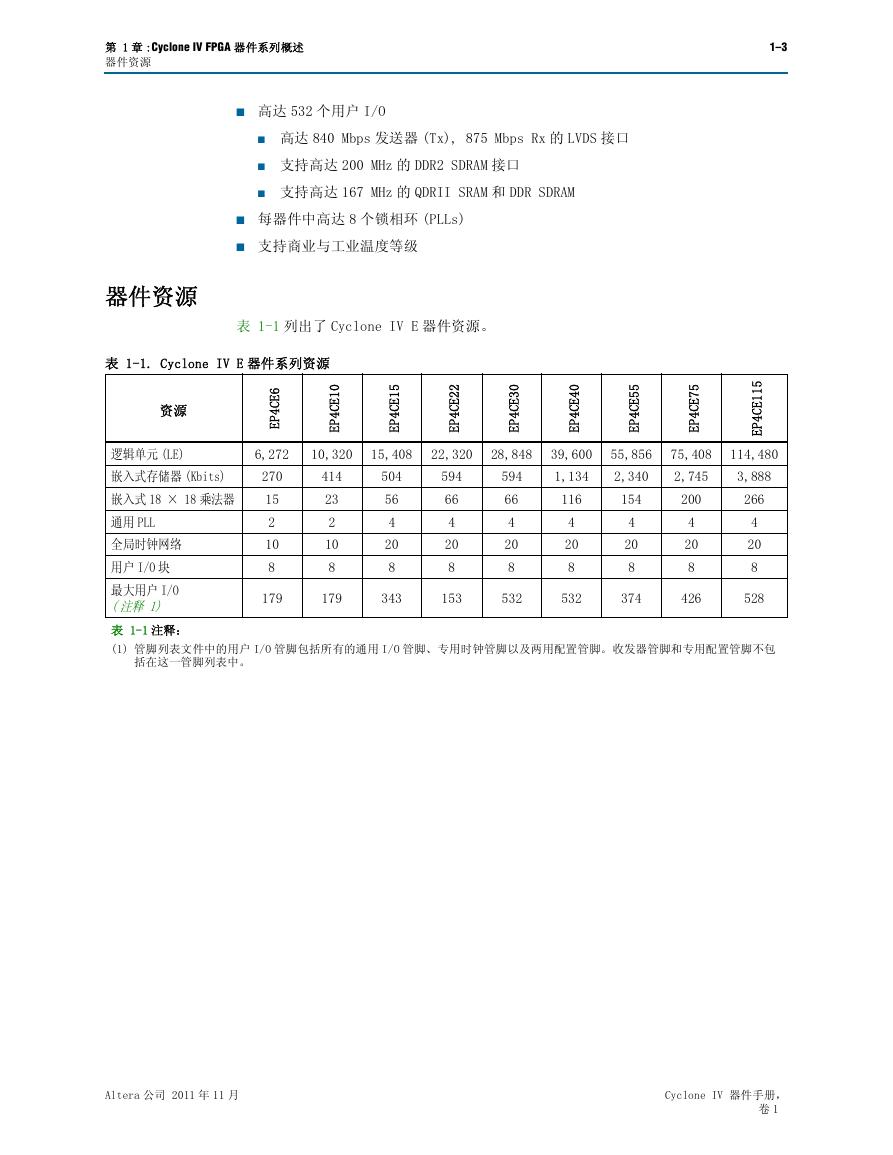

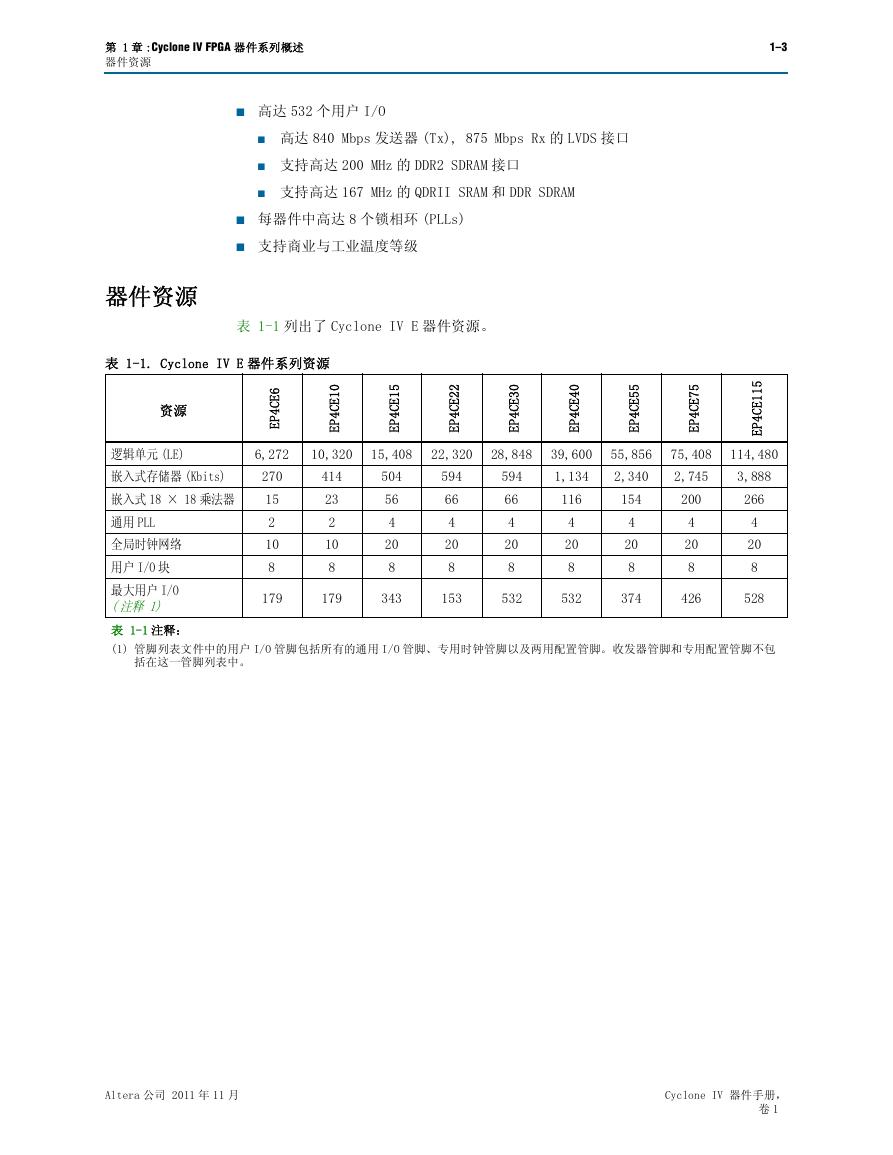

表 1-2 列出了 Cyclone IV GX 器件资源

表 1-2. Cyclone IV GX 器件系列的资源

5

1

X

G

C

4

P

E

2

2

X

G

C

4

P

E

0

3

X

G

C

4

P

E

)

1

释

注

(

0

3

X

G

C

4

P

E

)

2

释

注

(

0

5

X

G

C

4

P

E

)

3

释

注

(

5

7

X

G

C

4

P

E

)

3

释

注

(

0

1

1

X

G

C

4

P

E

)

3

释

注

(

0

5

1

X

G

C

4

P

E

)

3

释

注

(

14,400

21,280

29,440

29,440

49,888

73,920

109,424

149,760

540

0

1

2

756

40

2

2

1,080

1,080

2,502

4,158

5,490

6,480

80

2

2

80

4

140

4

198

4

280

4

360

4

(注释 4)

(注释 4)

(注释 4)

(注释 4)

(注释 4)

2

4

4

4

4

(注释 5)

(注释 5)

(注释 5)

(注释 5)

(注释 5)

(注释 5)

(注释 5)

(注释 5)

20

2

2.5

1

9

20

4

20

4

30

4

30

8

30

8

30

8

30

8

2.5

2.5

3.125

3.125

3.125

3.125

3.125

1

9

1

9

1

11

1

11

1

11

1

11

1

11

(注释 7)

(注释 7)

(注释 7)

(注释 8)

(注释 8)

(注释 8)

(注释 8)

(注释 8)

72

150

150

290

310

310

475

475

资源

逻辑单元 (LE)

嵌入式存储器 (Kbit)

嵌入式 18 × 18 乘法器

通用 PLL

多用 PLL

全局时钟网络

高速收发器 (注释 6)

收发器最大数据速率

(Gbps)

PCIe(PIPE) 硬核 IP 模

块

用户 I/O 块

最大用户 I/O

(注释 9)

表 1-2 注释:

(1) 应用于 F169 和 F324 封装。

(2) 应用于 F484 封装。

(3) 仅有两个多用途 PLL 可应用于 F484 封装。

(4) 其中两个通用 PLL 可以支持收发器时钟。欲了解详细信息,请参阅 Clock Networks and PLLs in Cyclone IV Devices

章节。

(5) 当多用 PLL 未用于同步收发器时,可将它们用于通用时钟。有关详细信息,请参阅 Clock Networks and PLLs in

Cyclone IV Devices章节。

(6) 如果 PCIe ×1, 您可以将该象限中其它收发器用于相同或者不同的数据速率下的其他协议。

(7) 包括用于 HSSI 参考时钟输入的一个配置 I/O 块和两个专用的时钟输入 I/O 块。

(8) 包括用于 HSSI 参考时钟输入的一个配置 I/O 块和四个专用的时钟输入 I/O 块。

(9) 管脚列表文件中的用户 I/O 管脚包括所有的通用 I/O 管脚、专用时钟管脚以及两用配置管脚。收发器管脚和专用配置

管脚不包括在这一管脚列表中。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

A

l

t

e

r

a

公

司

2

0

1

1

年

1

1

月

C

y

c

l

o

n

e

I

V

器

件

手

册

,

卷

1

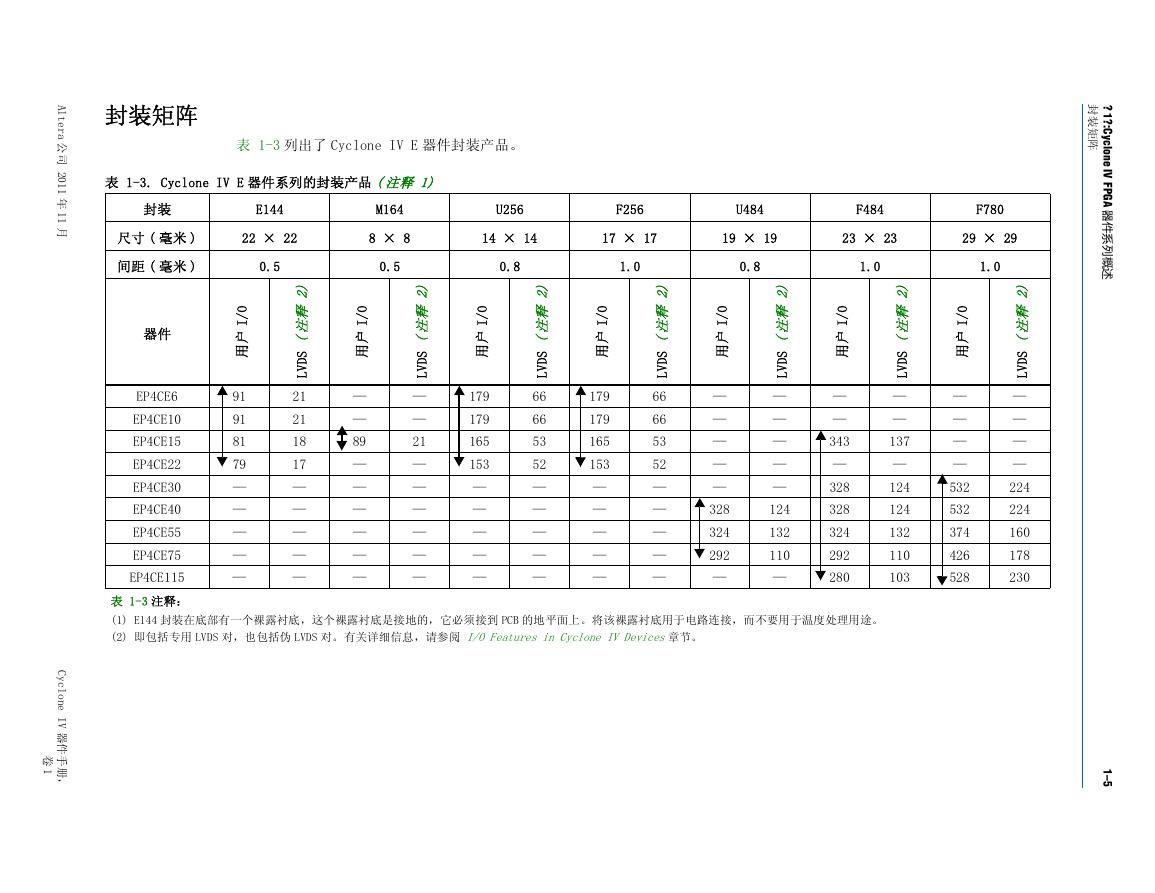

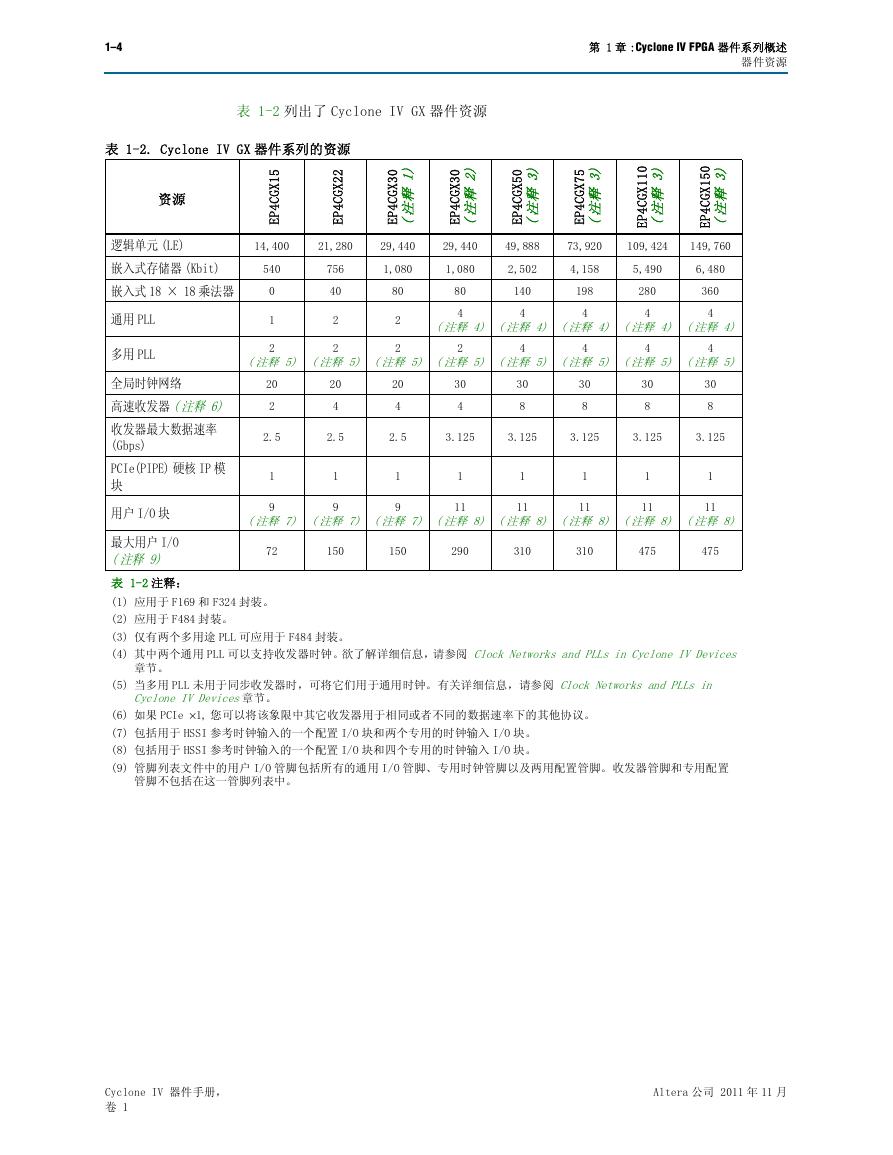

封装矩阵

表 1-3 列出了 Cyclone IV E 器件封装产品。

封

装

矩

阵

?

1

?

:

C

y

c

l

o

n

e

表 1-3. Cyclone IV E 器件系列的封装产品 (注释 1)

封装

E144

尺寸 ( 毫米 )

22 × 22

间距 ( 毫米 )

0.5

M164

8 × 8

0.5

U256

F256

U484

F484

F780

14 × 14

17 × 17

19 × 19

23 × 23

29 × 29

0.8

1.0

0.8

1.0

1.0

)

2

释

注

(

S

D

V

L

21

21

18

17

—

—

—

—

—

)

2

释

注

(

S

D

V

L

—

—

21

—

—

—

—

—

—

O

/

I

户

用

179

179

165

153

—

—

—

—

—

)

2

释

注

(

S

D

V

L

66

66

53

52

—

—

—

—

—

O

/

I

户

用

179

179

165

153

—

—

—

—

—

)

2

释

注

(

S

D

V

L

66

66

53

52

—

—

—

—

—

)

2

释

注

(

S

D

V

L

—

—

—

—

—

124

132

110

—

)

2

释

注

(

S

D

V

L

—

—

137

—

124

124

132

110

103

O

/

I

户

用

—

—

343

—

328

328

324

292

280

)

2

释

注

(

S

D

V

L

—

—

—

—

224

224

160

178

230

O

/

I

户

用

—

—

—

—

532

532

374

426

528

O

/

I

户

用

—

—

—

—

—

328

324

292

—

O

/

I

户

用

—

—

89

—

—

—

—

—

—

O

/

I

户

用

91

91

81

79

—

—

—

—

—

器件

EP4CE6

EP4CE10

EP4CE15

EP4CE22

EP4CE30

EP4CE40

EP4CE55

EP4CE75

EP4CE115

表 1-3 注释:

(1) E144 封装在底部有一个裸露衬底,这个裸露衬底是接地的,它必须接到 PCB 的地平面上。将该裸露衬底用于电路连接,而不要用于温度处理用途。

(2) 即包括专用 LVDS 对,也包括伪 LVDS 对。有关详细信息,请参阅 I/O Features in Cyclone IV Devices章节。

I

V

F

P

G

A

器

件

系

列

概

述

1

–

5

�

卷

1

l

C

y

c

o

n

e

I

V

器

件

手

册

,

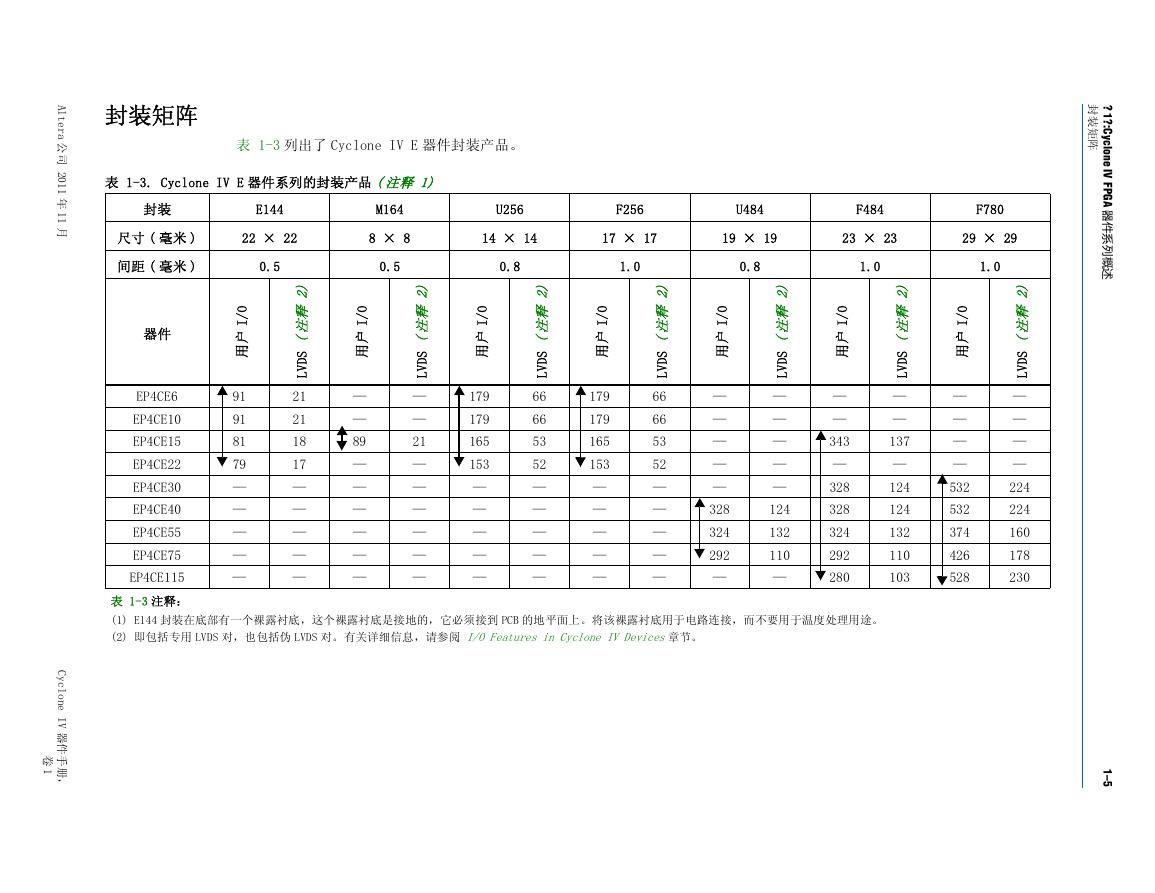

表 1-4 列出了 Cyclone IV GX 器件封装产品,包括 I/O 和收发器数量

表 1-4. Cyclone IV GX 器件系列的封装产品

封装

N148

F169

F324

F484

F672

F896

11 × 11

14 × 14

19 × 19

23 × 23

27 × 27

31 × 31

尺寸 ( 毫

米 )

间距 ( 毫

米 )

器件

0.5

)

1

释

注

(

S

D

V

L

O

/

I

户

用

EP4CGX15

72

25

EP4CGX22

— —

EP4CGX30

— —

EP4CGX50

— —

EP4CGX75

— —

EP4CGX110

EP4CGX150

—

—

—

—

表 1-4 注释:

1.0

)

1

释

注

(

S

D

V

L

25

25

25

O

/

I

户

用

72

72

72

— —

— —

—

—

—

—

s

R

V

C

X

2

2

2

—

—

—

—

1.0

)

1

释

注

(

S

D

V

L

—

64

64

O

/

I

户

用

—

150

150

— —

— —

—

—

—

—

s

R

V

C

X

—

4

4

—

—

—

—

1.0

)

1

释

注

(

S

D

V

L

—

—

130

130

130

120

120

O

/

I

户

用

—

—

290

290

290

270

270

s

R

V

C

X

—

—

4

4

4

4

4

1.0

)

1

释

注

(

S

D

V

L

—

—

—

140

140

181

181

O

/

I

户

用

—

—

—

310

310

393

393

s

R

V

C

X

—

—

—

8

8

8

8

1.0

)

1

释

注

(

S

D

V

L

—

—

—

—

—

220

220

O

/

I

户

用

—

—

—

—

—

475

475

s

R

V

C

X

—

—

—

—

—

8

8

s

R

V

C

X

2

—

—

—

—

—

—

(1) 即包括专用 LVDS 对,也包括伪 LVDS 对。有关详细信息,请参阅 I/O Features in Cyclone IV Devices章节。

N

o

v

e

m

b

e

r

2

0

1

1

A

l

t

e

r

a

C

o

r

p

o

r

a

t

i

o

n

封

装

矩

阵

1

–

6

?

1

?

:

C

y

c

l

o

n

e

I

V

F

P

G

A

器

件

系

列

概

述

�

第 1 章 :Cyclone IV FPGA 器件系列概述

Cyclone IV 器件系列的速度等级

1–7

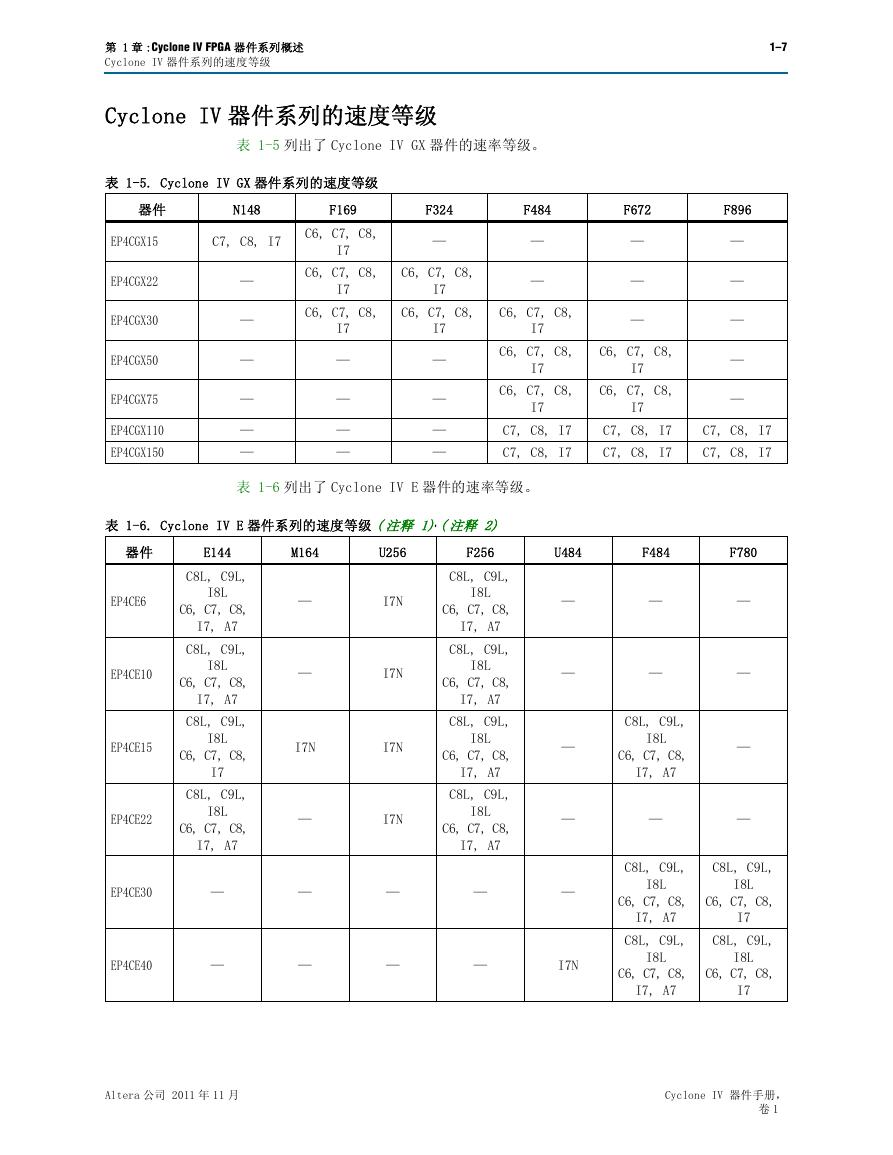

Cyclone IV 器件系列的速度等级

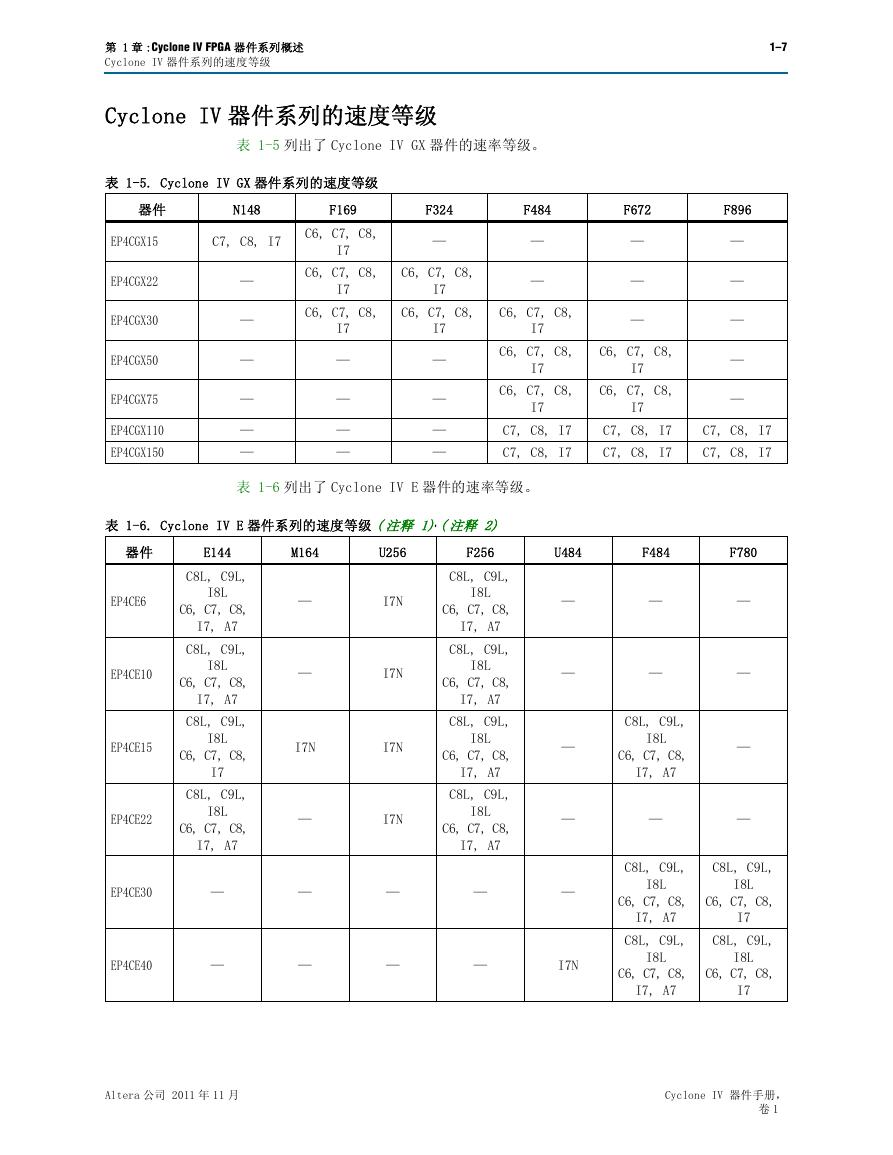

表 1-5 列出了 Cyclone IV GX 器件的速率等级。

表 1-5. Cyclone IV GX 器件系列的速度等级

器件

N148

F169

EP4CGX15

C7, C8, I7

C6, C7, C8,

I7

F324

—

F484

F672

F896

EP4CGX22

EP4CGX30

EP4CGX50

EP4CGX75

EP4CGX110

EP4CGX150

—

—

—

—

—

—

C6, C7, C8,

C6, C7, C8,

I7

I7

C6, C7, C8,

C6, C7, C8,

C6, C7, C8,

—

—

I7

—

—

—

I7

—

—

—

—

I7

—

—

—

—

C6, C7, C8,

C6, C7, C8,

I7

I7

C6, C7, C8,

C6, C7, C8,

I7

I7

C7, C8, I7

C7, C8, I7

C7, C8, I7

C7, C8, I7

C7, C8, I7

C7, C8, I7

—

—

—

—

—

表 1-6 列出了 Cyclone IV E 器件的速率等级。

表 1-6. Cyclone IV E 器件系列的速度等级 (注释 1),(注释 2)

器件

E144

M164

U256

F256

U484

F484

F780

EP4CE6

EP4CE10

EP4CE15

EP4CE22

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

C8L, C9L,

I8L

C6, C7, C8,

I7

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

EP4CE30

—

EP4CE40

—

—

—

I7N

I7N

I7N

I7N

—

—

—

I7N

—

—

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

—

—

—

—

—

—

—

I7N

—

—

C8L, C9L,

I8L

C6, C7, C8,

I7, A7

—

—

—

—

—

C8L, C9L,

C8L, C9L,

I8L

I8L

C6, C7, C8,

C6, C7, C8,

I7, A7

I7

C8L, C9L,

C8L, C9L,

I8L

I8L

C6, C7, C8,

C6, C7, C8,

I7, A7

I7

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

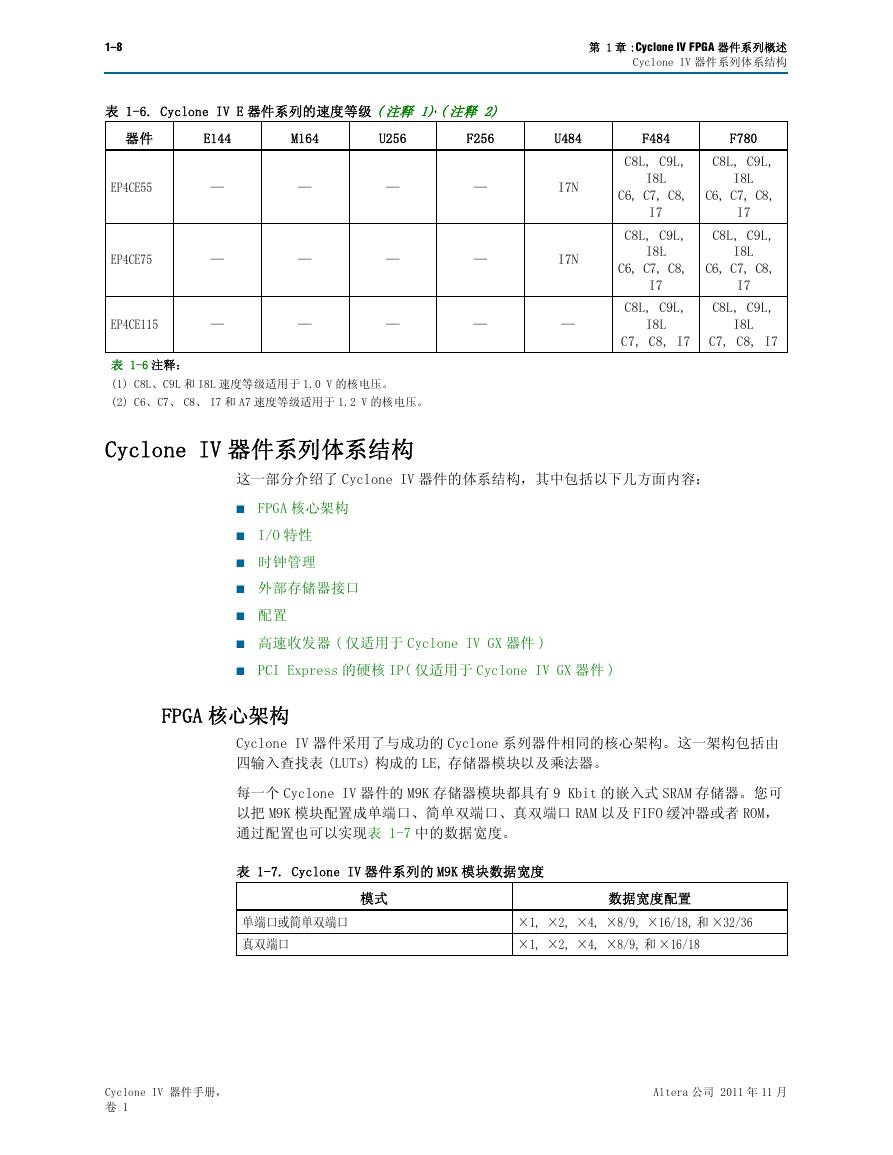

1–8

第 1 章 :Cyclone IV FPGA 器件系列概述

Cyclone IV 器件系列体系结构

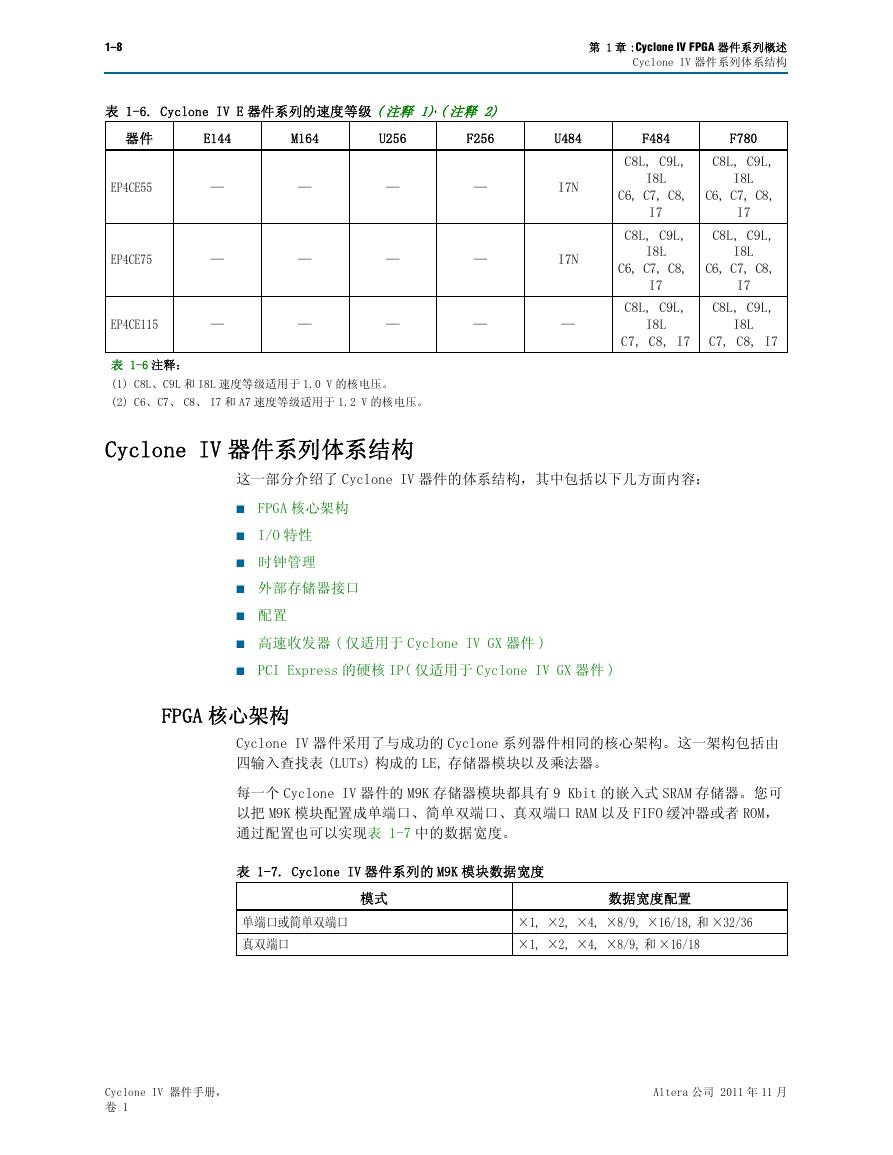

表 1-6. Cyclone IV E 器件系列的速度等级 (注释 1),(注释 2)

器件

E144

M164

U256

F256

U484

F484

F780

EP4CE55

—

—

—

EP4CE75

EP4CE115

表 1-6 注释:

—

—

—

—

—

—

—

—

—

(1) C8L、C9L 和 I8L 速度等级适用于 1.0 V 的核电压。

(2) C6、C7、 C8、 I7 和 A7 速度等级适用于 1.2 V 的核电压。

Cyclone IV 器件系列体系结构

I7N

I7N

C8L, C9L,

C8L, C9L,

I8L

I8L

C6, C7, C8,

C6, C7, C8,

I7

I7

C8L, C9L,

C8L, C9L,

I8L

I8L

C6, C7, C8,

C6, C7, C8,

I7

I7

C8L, C9L,

C8L, C9L,

—

I8L

I8L

C7, C8, I7

C7, C8, I7

这一部分介绍了 Cyclone IV 器件的体系结构,其中包括以下几方面内容:

■ FPGA 核心架构

■ I/O 特性

■ 时钟管理

■ 外部存储器接口

■ 配置

■ 高速收发器 ( 仅适用于 Cyclone IV GX 器件 )

■ PCI Express 的硬核 IP( 仅适用于 Cyclone IV GX 器件 )

FPGA 核心架构

Cyclone IV 器件采用了与成功的 Cyclone 系列器件相同的核心架构。这一架构包括由

四输入查找表 (LUTs) 构成的 LE, 存储器模块以及乘法器。

每一个 Cyclone IV 器件的 M9K 存储器模块都具有 9 Kbit 的嵌入式 SRAM 存储器。您可

以把 M9K 模块配置成单端口、简单双端口、真双端口 RAM 以及 FIFO 缓冲器或者 ROM,

通过配置也可以实现表 1-7 中的数据宽度。

表 1-7. Cyclone IV 器件系列的 M9K 模块数据宽度

模式

数据宽度配置

单端口或简单双端口

真双端口

×1, ×2, ×4, ×8/9, ×16/18, 和 ×32/36

×1, ×2, ×4, ×8/9, 和 ×16/18

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf