7. Cyclone IV 器件中的外部存储器接口

December 2010

CYIV-51007-2.2

CYIV-51007-2.2

本章节介绍了 Cyclone® IV 器件的存储器接口管脚的支持以及外部存储器接口的特性。

除了大量供应的片上存储器,Cyclone IV 器件可以很容易地与各种外部存储器件建立

连接,其中包括 DDR2 SDRAM、DDR SDRAM 和 QDR II SRAM。外部存储器件是各种图像处

理、存储、通信以及通用嵌入式应用的一个重要的系统组件。

1 Altera 建议使用 Altera® ALTMEMPHY 宏功能来构建所有的 DDR2 或者 DDR SDRAM 外部存储

器。通过将 Altera DDR2 或者 DDR SDRAM 存储控制器、第三方控制器或者定制控制器

用于特定的应用需要,可以实现控制器功能。Cyclone IV 器件在电气方面提供了对

QDR II 接口的支持,但是对于 QDR II 接口,Altera 没有提供控制器或者物理层 (PHY)

宏功能。

本章节含盖以下两部分内容:

■ Cyclone IV 器件的存储器接口管脚支持 ( 第 7-2 页 )

■ Cyclone IV 器件存储器接口特性 ( 第 7-12 页 )

f 欲了解所支持的最大时钟速率、器件与管脚规划、IP 实现以及器件端接的详细信息,

请参阅 External Memory Interface Handbook。

© 2010 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 1

2010 年 12 月

Subscribe

�

7–2

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

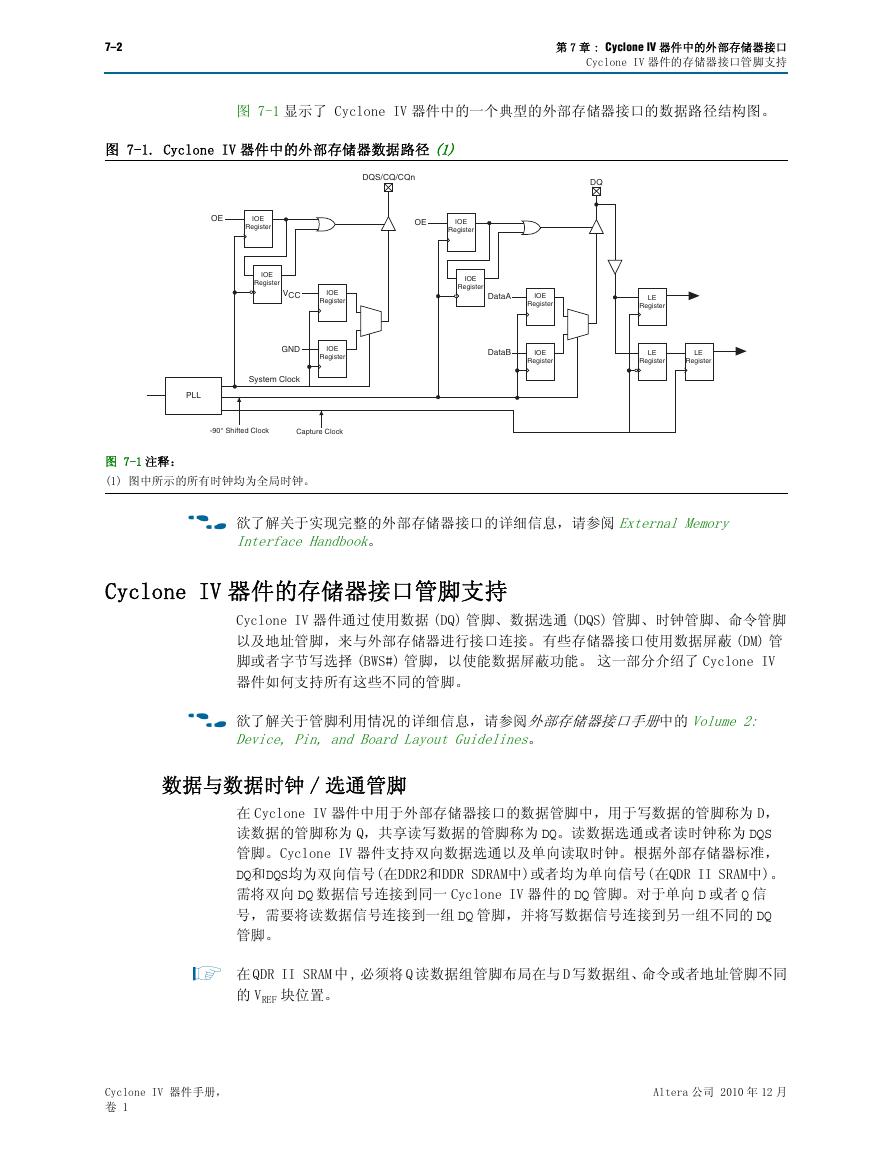

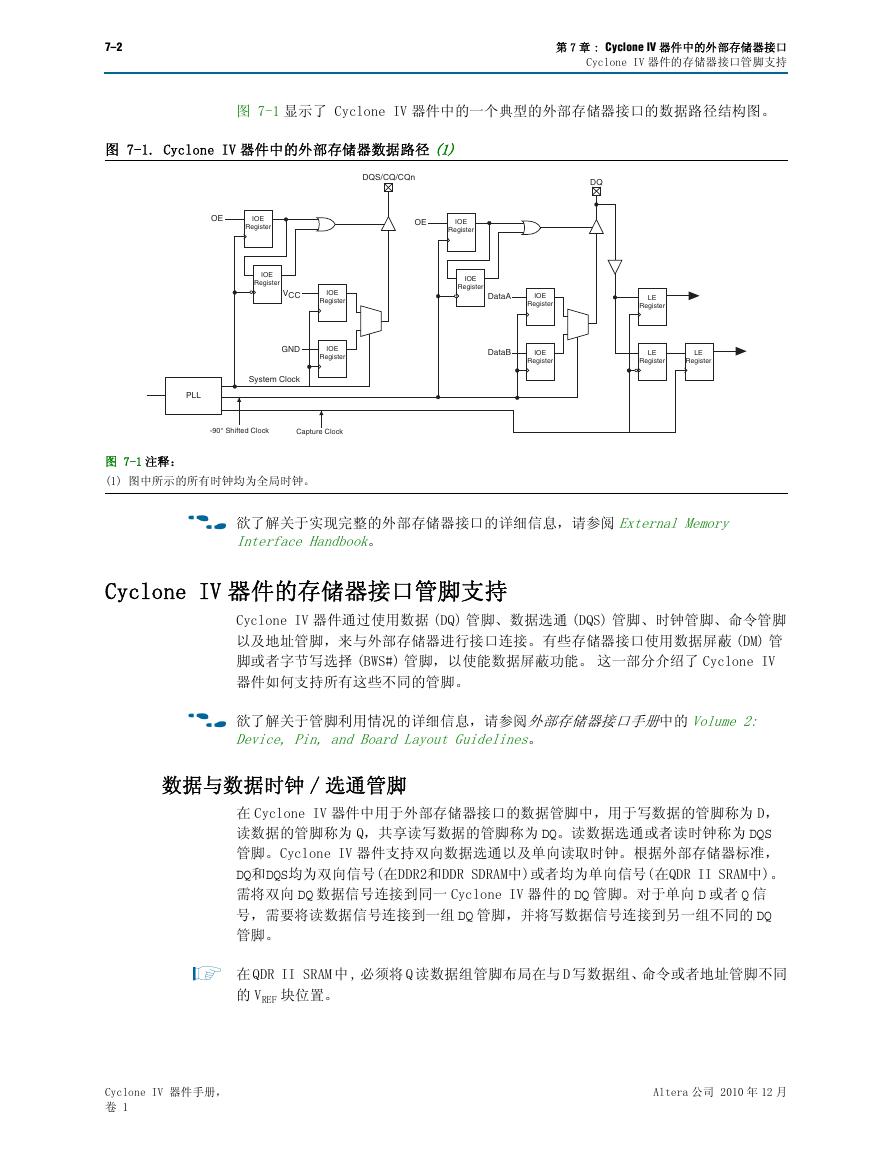

图 7-1 显示了 Cyclone IV 器件中的一个典型的外部存储器接口的数据路径结构图。

图 7-1. Cyclone IV 器件中的外部存储器数据路径 (1)

DQS/CQ/CQn

DQ

OE

IOE

Register

OE

IOE

Register

IOE

Register

DataA

IOE

Register

LE

Register

DataB

IOE

Register

LE

Register

LE

Register

IOE

Register

VCC

IOE

Register

GND

IOE

Register

System Clock

PLL

-90° Shifted Clock

Capture Clock

图 7-1 注释:

(1) 图中所示的所有时钟均为全局时钟。

f 欲了解关于实现完整的外部存储器接口的详细信息,请参阅 External Memory

Interface Handbook。

Cyclone IV 器件的存储器接口管脚支持

Cyclone IV 器件通过使用数据 (DQ) 管脚、数据选通 (DQS) 管脚、时钟管脚、命令管脚

以及地址管脚,来与外部存储器进行接口连接。有些存储器接口使用数据屏蔽 (DM) 管

脚或者字节写选择 (BWS#) 管脚,以使能数据屏蔽功能。 这一部分介绍了 Cyclone IV

器件如何支持所有这些不同的管脚。

f 欲了解关于管脚利用情况的详细信息,请参阅外部存储器接口手册中的 Volume 2:

Device, Pin, and Board Layout Guidelines。

数据与数据时钟 / 选通管脚

在 Cyclone IV 器件中用于外部存储器接口的数据管脚中,用于写数据的管脚称为 D,

读数据的管脚称为 Q,共享读写数据的管脚称为 DQ。读数据选通或者读时钟称为 DQS

管脚。Cyclone IV 器件支持双向数据选通以及单向读取时钟。根据外部存储器标准,

DQ和DQS均为双向信号(在DDR2和DDR SDRAM中)或者均为单向信号(在QDR II SRAM中)。

需将双向 DQ 数据信号连接到同一 Cyclone IV 器件的 DQ 管脚。对于单向 D 或者 Q 信

号,需要将读数据信号连接到一组 DQ 管脚,并将写数据信号连接到另一组不同的 DQ

管脚。

1 在 QDR II SRAM 中 , 必须将 Q 读数据组管脚布局在与 D 写数据组、命令或者地址管脚不同

的 VREF 块位置。

Cyclone IV 器件手册,

卷 1

Altera 公司 2010 年 12 月

�

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

7–3

在 Cyclone IV 器件中, DQS 管脚仅在写模式期间用于 DDR2 和 DDR SDRAM 接口中。

Cyclone IV 器件将忽略作为读数据选通信号的 DQS,因为 PHY 内部生成了用于读模式

的读取捕捉时钟。然而,您必须将 DQS 管脚连接到 DDR2 和 DDR SDRAM 接口中的 DQS 信

号,或者连接到 QDR II SRAM 接口中的 CQ 信号。

1 Cyclone IV 器件不支持差分选通管脚,这是 DDR2 SDRAM 器件中的一个可选功能。

f 当使用 Altera Memory Controller MegaCore® 功能时,PHY 将被例化。欲了解关于存储

器接口数据路径的详细信息,请参阅 External Memory Interface Handbook。

1 ALTMEMPHY 是一个自校准的宏功能,这个模块得到了增强使其简化了不同存储器接口中

读数据路径的实现。ALTMEMPHY 的自校准功能在工艺、电压和温度 (PVT) 变化范围内对

时钟相位及频率进行优化, 从而实现了易于使用的特性。通过使用 ALTMEMPHY 宏功

能,可以节省 Cyclone IV 器件中的全局时钟资源 ( 因为 DQS 被忽略来实现读捕捉 )。

重同步的问题不会出现,因为不会发生从存储器域时钟 (DQS) 到系统域的数据传输 (

该数据传输用于捕捉数据 DQ)。

Cyclone IV 器件中所有的 I/O 块均对 DQ 和 DQS 信号提供了 ×8、 ×9、 ×16、 ×18、

×32 和 ×36 的 DQ-bus 模式,但不包括 Cyclone IV GX 器件 ( 其不支持左侧的 I/O 块

接口 )。 DDR2 和 DDR SDRAM 接口使用 ×8 模式的 DQS 组,无需考虑接口带宽。 对于一

个更宽的接口,通过使用多个 ×8 的 DQ 组来达到所需的宽度要求。

在 ×9、 ×18 和 ×36 模式中,一对互补的 DQS 管脚 (CQ 和 CQ#) 分别驱动组中 9、 18

或者 36 个 DQ 管脚,以支持一个、两个或者四个奇偶校验位以及相应的数据位。×9、

×18 和 ×36 模式支持 QDR II 存储器接口。 CQ# 是一个反向的读时钟信号,连接到补

充数据选通 (DQS 或 CQ#) 管脚。 如果 DQ 管脚未用作存储器接口信号,则可用作普通的

用户 I/O 管脚。

f 欲了解运行在≥2.97 Gbps数据速率上的Cyclone IV收发器中的未支持的DQS和DQ组的详

细信息,请参阅 Cyclone IV Device Family Pin Connection Guidelines。

Altera 公司 2010 年 12 月 Cyclone IV 器件手册,

卷 1

�

7–4

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

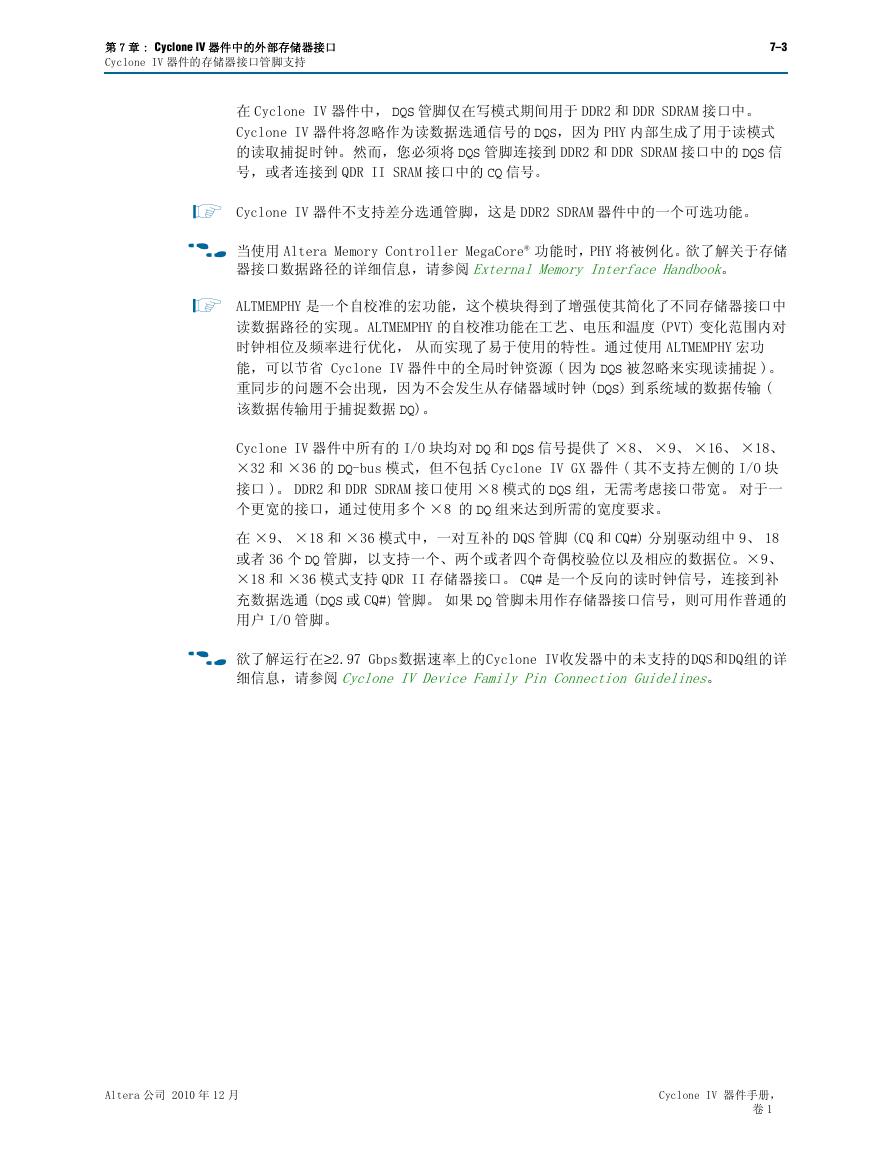

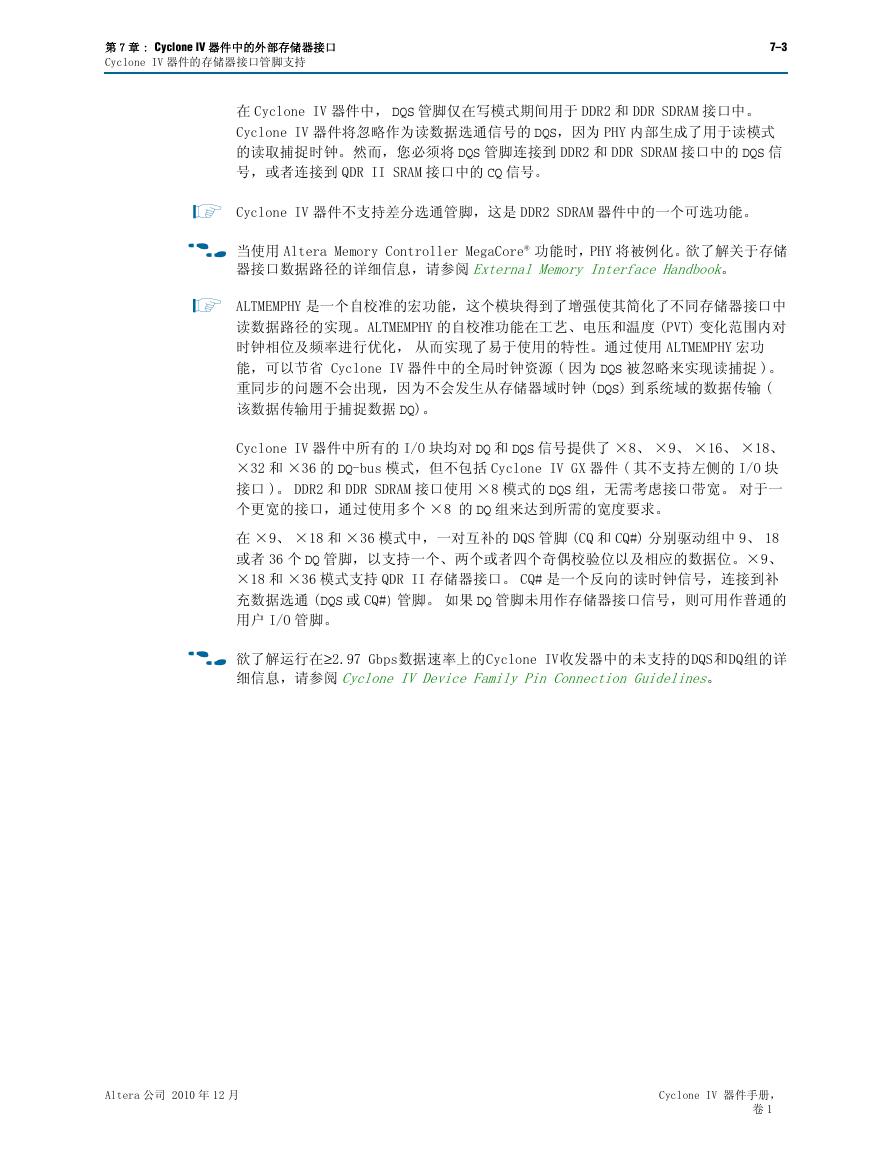

表 7-1 列出了 Cyclone IV GX 器件的每一侧上所支持的 DQS 或 DQ 组的数量。

表 7-1. Cyclone IV GX 器件每侧上所支持的 DQS 和 DQ 总线模式 (1)

器件

封装

EP4CGX15

148-pin QFN

169-pin FBGA

169-pin FBGA

EP4CGX22

EP4CGX30

324-pin FBGA

EP4CGX50

EP4CGX75

484-pin FBGA (4)

484-pin FBGA

672-pin FBGA

484-pin FBGA

EP4CGX110

EP4CGX150

672-pin FBGA

896-pin FBGA

表 7-1 注释:

(1) 仍然是初步的 DQS/DQ 组数。

在器件中的位

×8 组

×9 组

×16 组

×18 组

×32 组

×36 组

置

数

数

数

数

右侧

顶端 (2)

底部 (3)

右侧

顶端 (2)

底部 (3)

右侧

顶端 (2)

底部 (3)

右侧

顶端

底部

右侧

顶端

底部

右侧

顶端

底部

右侧

顶端

底部

右侧

顶端

底部

右侧

顶端

底部

右侧

顶端

底部

1

1

1

1

1

1

1

1

1

2

2

2

4

4

4

4

4

4

4

4

4

4

4

4

4

4

4

6

6

6

0

0

0

0

0

0

0

0

0

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

0

0

0

0

0

0

0

0

0

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

3

3

0

0

0

0

0

0

0

0

0

1

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

3

3

数

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

数

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

(2) 有些 DQ 管脚可用作 RUP 和 RDN 管脚。如果使用这些管脚作为 OCT 校准的 RUP 和 RDN 管脚,则不能使用这些组。

(3) 有些 DQ 管脚可用作 RUP 管脚,而有些 DM 管脚可用作 RDN 管脚。如果使用这些管脚作为 OCT 校准的 RUP 和 RDN 管脚,则不能使

用这些组。

(4) 仅适用于 EP4CGX30 器件。

Cyclone IV 器件手册,

卷 1

Altera 公司 2010 年 12 月

�

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

7–5

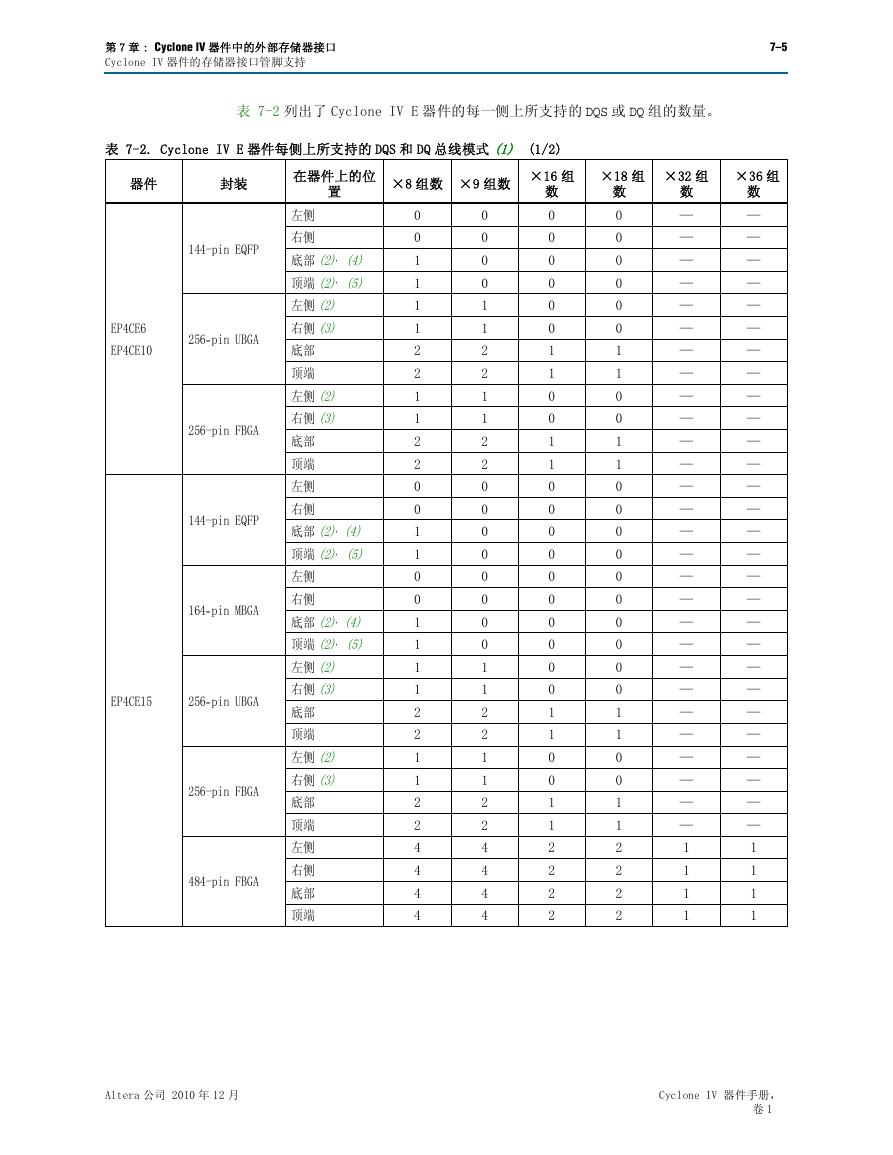

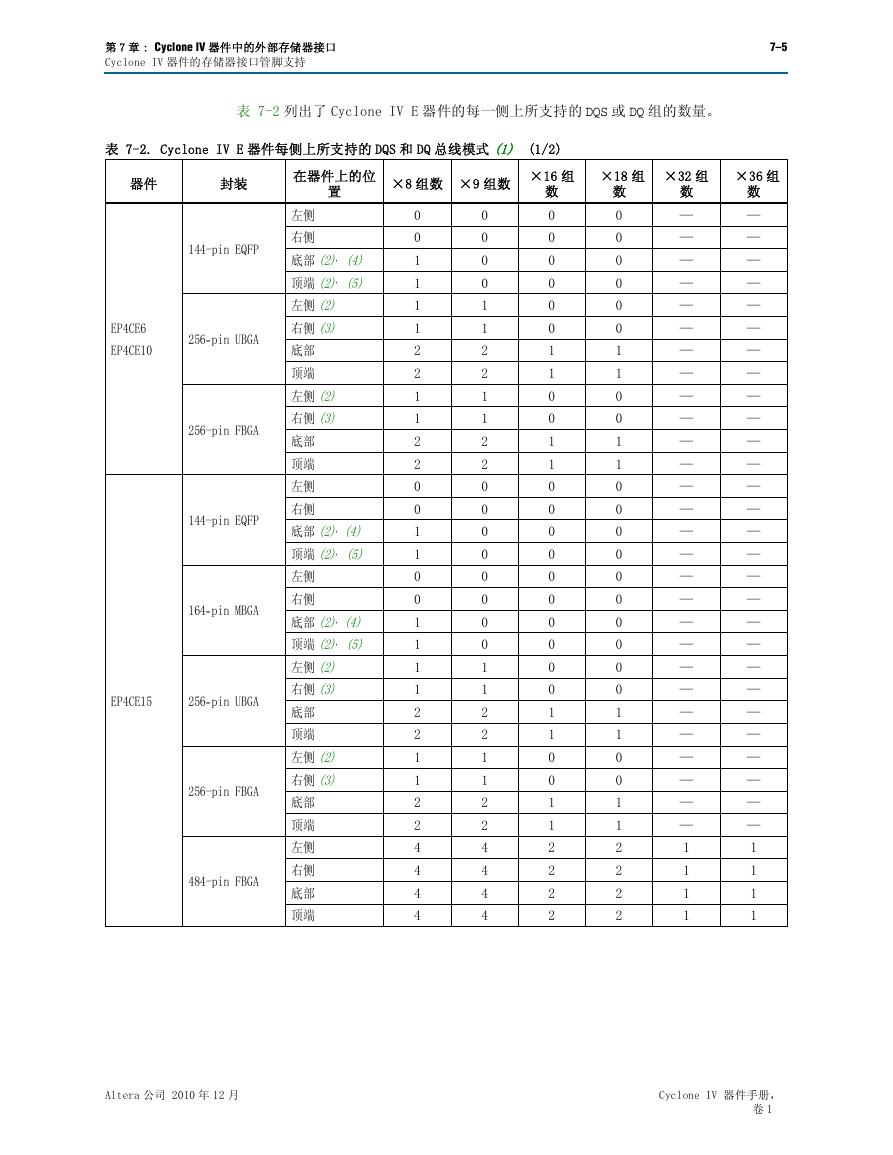

表 7-2 列出了 Cyclone IV E 器件的每一侧上所支持的 DQS 或 DQ 组的数量。

表 7-2. Cyclone IV E 器件每侧上所支持的 DQS 和 DQ 总线模式 (1) (1/2)

×16 组

×18 组

×32 组

×36 组

数

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

数

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

器件

封装

在器件上的位

置

×8 组数 ×9 组数

数

数

144-pin EQFP

EP4CE6

EP4CE10

256- pin UBGA

256-pin FBGA

144-pin EQFP

164- pin MBGA

EP4CE15

256- pin UBGA

256-pin FBGA

484-pin FBGA

左侧

右侧

底部 (2), (4)

顶端 (2), (5)

左侧 (2)

右侧 (3)

底部

顶端

左侧 (2)

右侧 (3)

底部

顶端

左侧

右侧

底部 (2), (4)

顶端 (2), (5)

左侧

右侧

底部 (2), (4)

顶端 (2), (5)

左侧 (2)

右侧 (3)

底部

顶端

左侧 (2)

右侧 (3)

底部

顶端

左侧

右侧

底部

顶端

0

0

1

1

1

1

2

2

1

1

2

2

0

0

1

1

0

0

1

1

1

1

2

2

1

1

2

2

4

4

4

4

0

0

0

0

1

1

2

2

1

1

2

2

0

0

0

0

0

0

0

0

1

1

2

2

1

1

2

2

4

4

4

4

0

0

0

0

0

0

1

1

0

0

1

1

0

0

0

0

0

0

0

0

0

0

1

1

0

0

1

1

2

2

2

2

0

0

0

0

0

0

1

1

0

0

1

1

0

0

0

0

0

0

0

0

0

0

1

1

0

0

1

1

2

2

2

2

Altera 公司 2010 年 12 月 Cyclone IV 器件手册,

卷 1

�

7–6

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

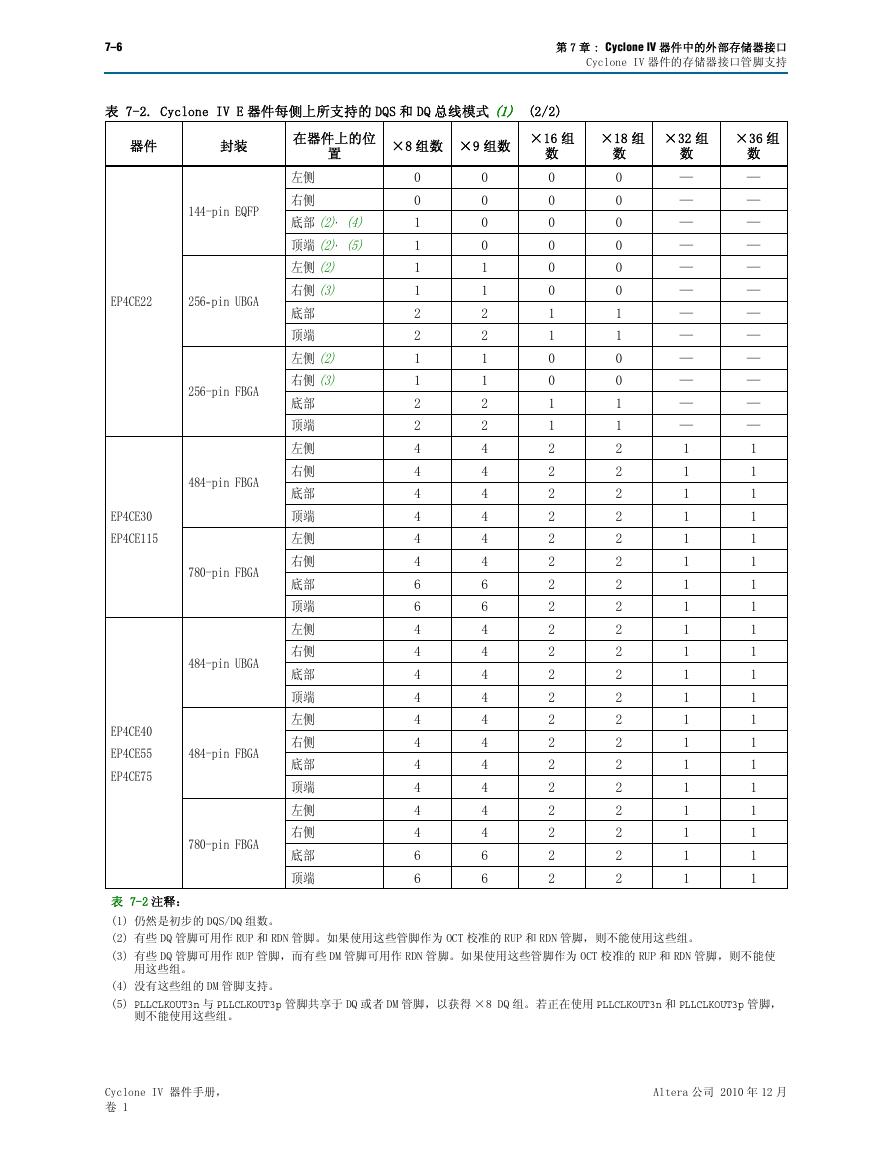

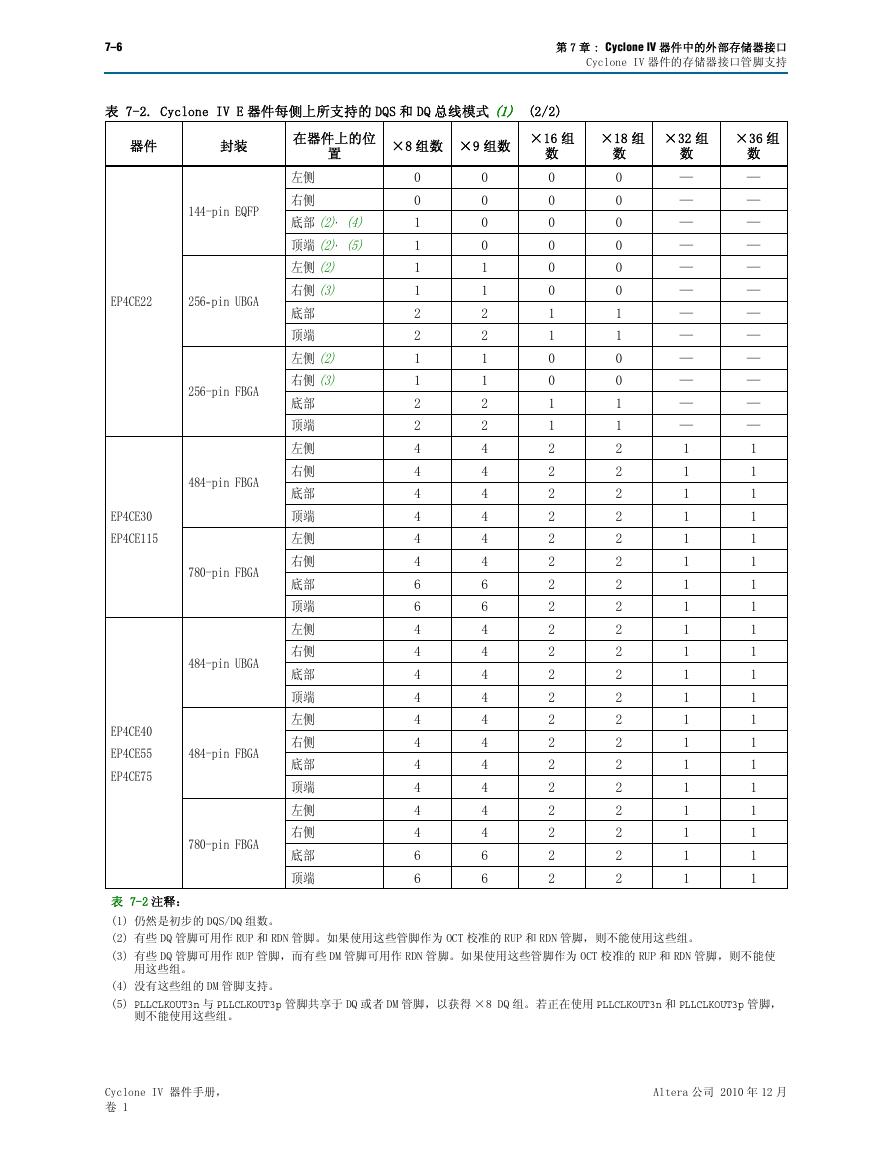

表 7-2. Cyclone IV E 器件每侧上所支持的 DQS 和 DQ 总线模式 (1) (2/2)

×16 组

×18 组

×32 组

×36 组

数

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

数

—

—

—

—

—

—

—

—

—

—

—

—

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

器件

封装

在器件上的位

置

×8 组数 ×9 组数

数

数

左侧

右侧

底部 (2), (4)

顶端 (2), (5)

左侧 (2)

右侧 (3)

底部

顶端

左侧 (2)

右侧 (3)

底部

顶端

左侧

右侧

底部

顶端

左侧

右侧

底部

顶端

左侧

右侧

底部

顶端

左侧

右侧

底部

顶端

左侧

右侧

底部

顶端

144-pin EQFP

EP4CE22

256- pin UBGA

EP4CE30

EP4CE115

256-pin FBGA

484-pin FBGA

780-pin FBGA

484-pin UBGA

EP4CE40

EP4CE55

EP4CE75

484-pin FBGA

780-pin FBGA

表 7-2 注释:

(1) 仍然是初步的 DQS/DQ 组数。

0

0

1

1

1

1

2

2

1

1

2

2

4

4

4

4

4

4

6

6

4

4

4

4

4

4

4

4

4

4

6

6

0

0

0

0

1

1

2

2

1

1

2

2

4

4

4

4

4

4

6

6

4

4

4

4

4

4

4

4

4

4

6

6

0

0

0

0

0

0

1

1

0

0

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

0

0

0

0

0

0

1

1

0

0

1

1

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

2

(2) 有些 DQ 管脚可用作 RUP 和 RDN 管脚。如果使用这些管脚作为 OCT 校准的 RUP 和 RDN 管脚,则不能使用这些组。

(3) 有些 DQ 管脚可用作 RUP 管脚,而有些 DM 管脚可用作 RDN 管脚。如果使用这些管脚作为 OCT 校准的 RUP 和 RDN 管脚,则不能使

用这些组。

(4) 没有这些组的 DM 管脚支持。

(5) PLLCLKOUT3n 与 PLLCLKOUT3p 管脚共享于 DQ 或者 DM 管脚,以获得 ×8 DQ 组。若正在使用 PLLCLKOUT3n 和 PLLCLKOUT3p 管脚,

则不能使用这些组。

Cyclone IV 器件手册,

卷 1

Altera 公司 2010 年 12 月

�

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

7–7

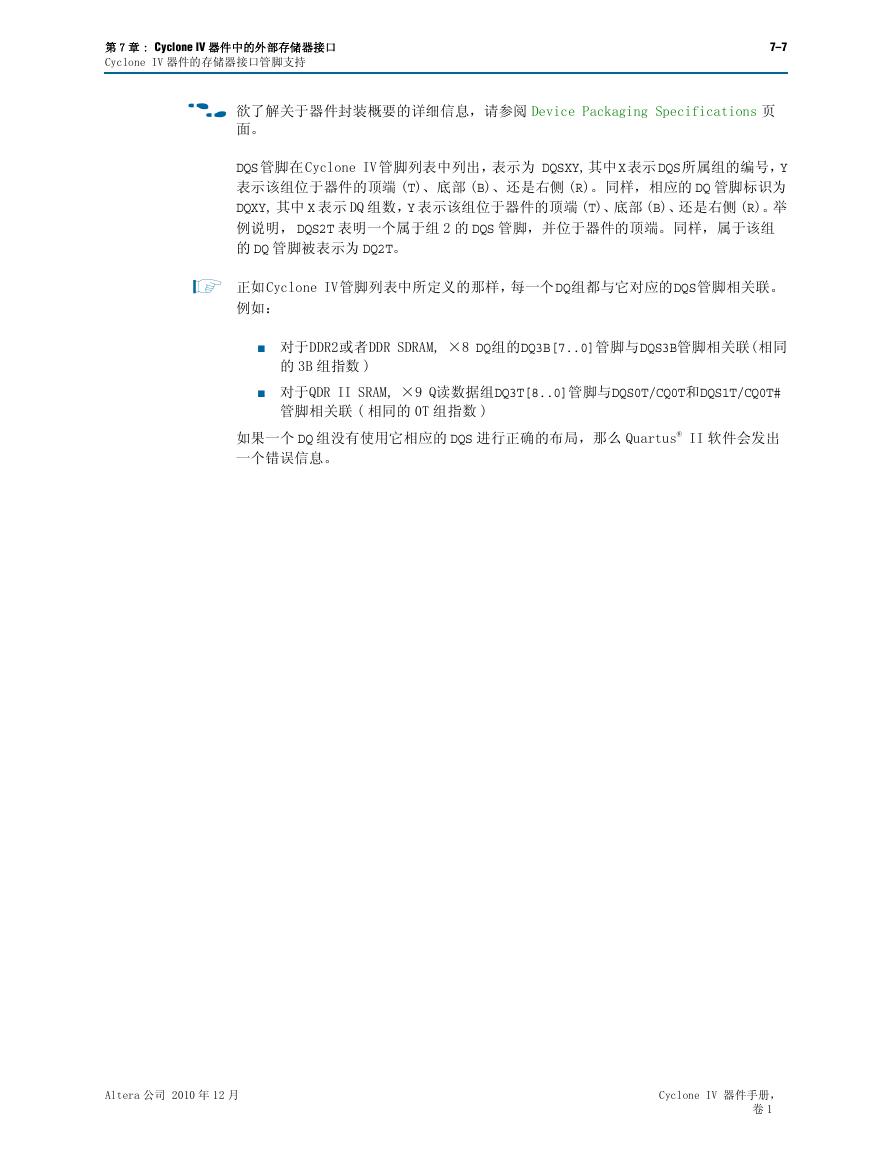

f 欲了解关于器件封装概要的详细信息,请参阅 Device Packaging Specifications 页

面。

DQS管脚在 Cyclone IV 管脚列表中列出,表示为 DQSXY, 其中X表示 DQS所属组的编号,Y

表示该组位于器件的顶端 (T)、底部 (B)、还是右侧 (R)。同样,相应的 DQ 管脚标识为

DQXY, 其中 X 表示 DQ 组数,Y 表示该组位于器件的顶端 (T)、底部 (B)、还是右侧 (R)。举

例说明, DQS2T 表明一个属于组 2 的 DQS 管脚,并位于器件的顶端。同样,属于该组

的 DQ 管脚被表示为 DQ2T。

1 正如Cyclone IV管脚列表中所定义的那样,每一个DQ组都与它对应的DQS管脚相关联。

例如:

■ 对于DDR2或者DDR SDRAM, ×8 DQ组的DQ3B[7..0]管脚与DQS3B管脚相关联(相同

的 3B 组指数 )

■ 对于QDR II SRAM, ×9 Q读数据组DQ3T[8..0]管脚与DQS0T/CQ0T和DQS1T/CQ0T#

管脚相关联 ( 相同的 0T 组指数 )

如果一个 DQ 组没有使用它相应的 DQS 进行正确的布局,那么 Quartus® II 软件会发出

一个错误信息。

Altera 公司 2010 年 12 月 Cyclone IV 器件手册,

卷 1

�

7–8

第 7 章 : Cyclone IV 器件中的外部存储器接口

Cyclone IV 器件的存储器接口管脚支持

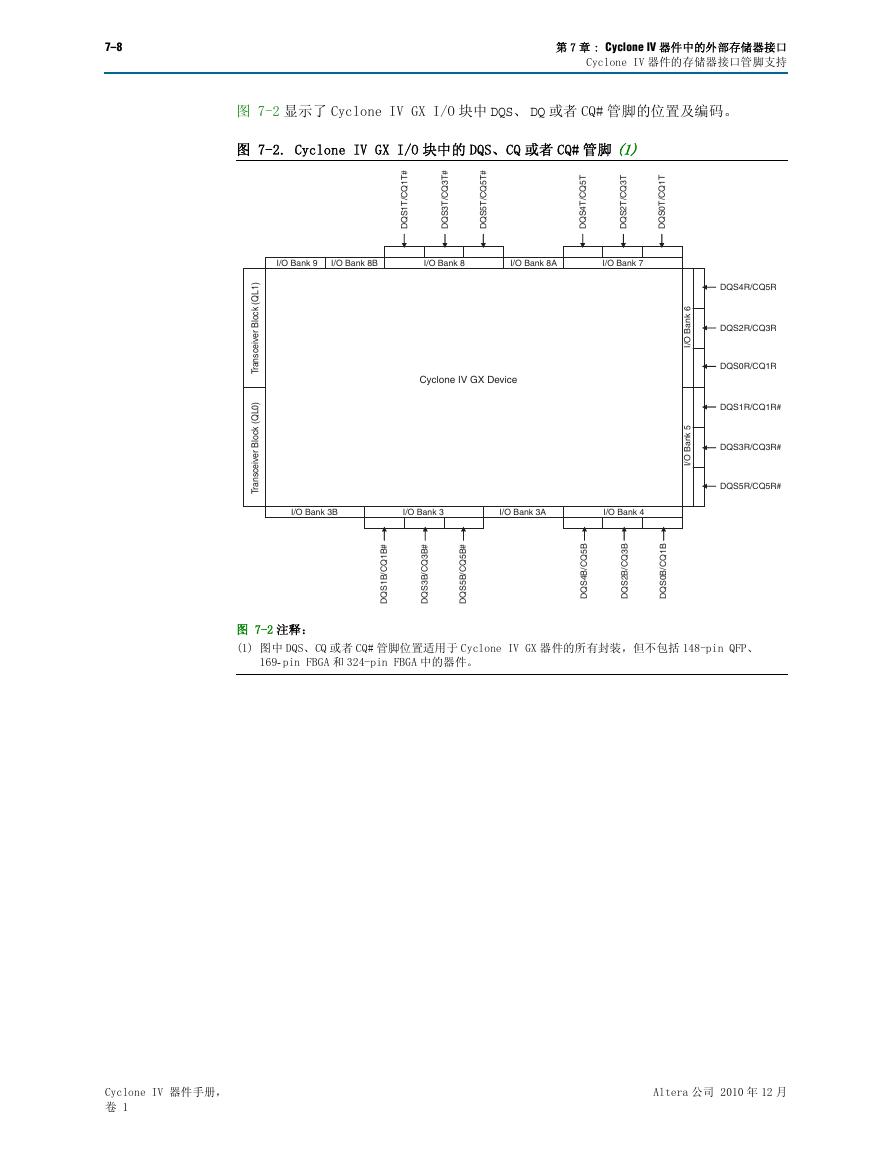

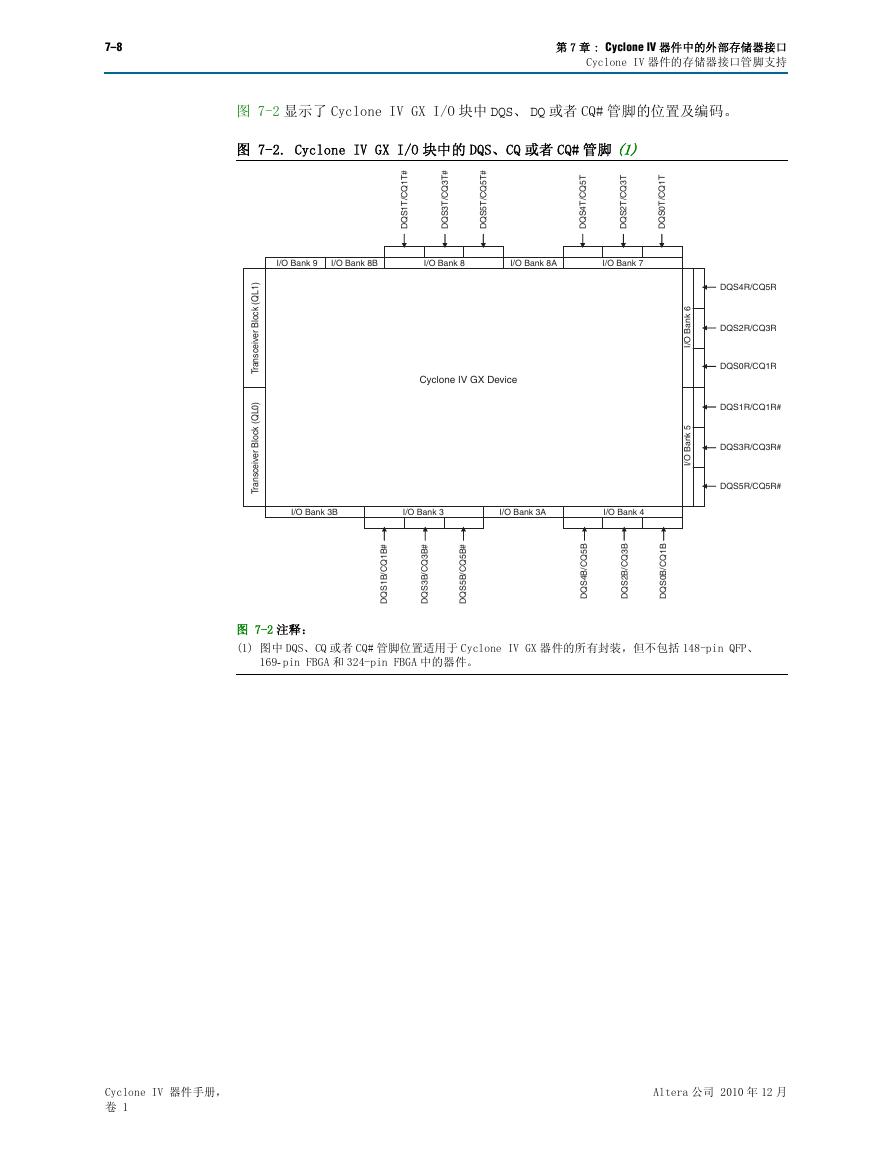

图 7-2 显示了 Cyclone IV GX I/O 块中 DQS、 DQ 或者 CQ# 管脚的位置及编码。

图 7-2. Cyclone IV GX I/O 块中的 DQS、CQ 或者 CQ# 管脚 (1)

/

#

T

1

Q

C

T

1

S

Q

D

/

#

T

3

Q

C

T

3

S

Q

D

/

#

T

5

Q

C

T

5

S

Q

D

/

T

5

Q

C

T

4

S

Q

D

/

T

3

Q

C

T

2

S

Q

D

/

T

1

Q

C

T

0

S

Q

D

I/O Bank 9

I/O Bank 8B

I/O Bank 8

I/O Bank 8A

I/O Bank 7

)

1

L

Q

(

k

c

o

B

l

i

r

e

v

e

c

s

n

a

r

T

)

0

L

Q

(

k

c

o

B

l

i

r

e

v

e

c

s

n

a

r

T

6

k

n

a

B

O

/

I

Cyclone IV GX Device

5

k

n

a

B

O

/

I

DQS4R/CQ5R

DQS2R/CQ3R

DQS0R/CQ1R

DQS1R/CQ1R#

DQS3R/CQ3R#

DQS5R/CQ5R#

I/O Bank 3B

I/O Bank 3

I/O Bank 3A

I/O Bank 4

/

#

B

1

Q

C

B

1

S

Q

D

/

#

B

3

Q

C

B

3

S

Q

D

/

#

B

5

Q

C

B

5

S

Q

D

/

B

5

Q

C

B

4

S

Q

D

/

B

3

Q

C

B

2

S

Q

D

/

B

1

Q

C

B

0

S

Q

D

图 7-2 注释:

(1) 图中 DQS、CQ 或者 CQ# 管脚位置适用于 Cyclone IV GX 器件的所有封装,但不包括 148-pin QFP、

169- pin FBGA 和 324-pin FBGA 中的器件。

Cyclone IV 器件手册,

卷 1

Altera 公司 2010 年 12 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf