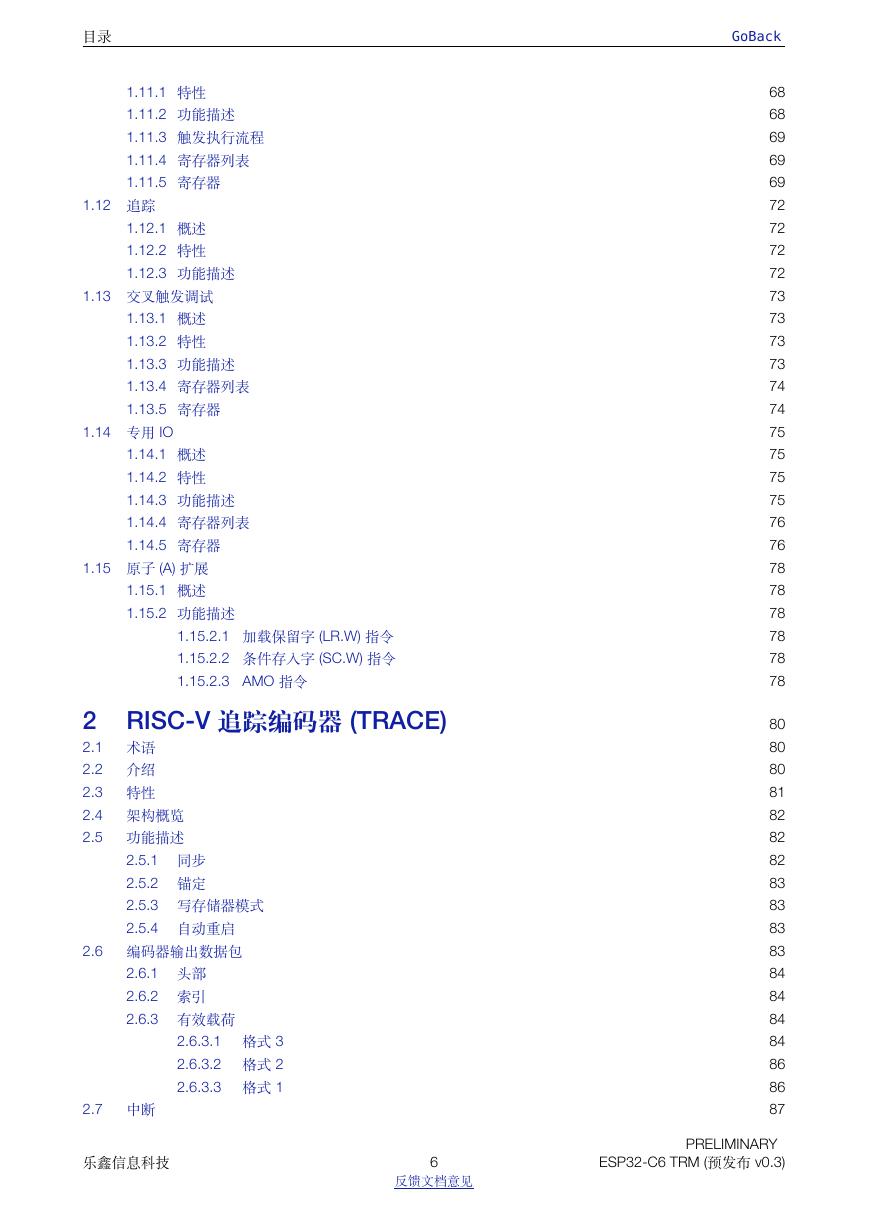

1 高性能处理器

1.1 概述

1.2 特性

1.3 术语

1.4 地址分布

1.5 配置与状态寄存器 (CSR)

1.5.1 寄存器列表

1.5.2 寄存器

1.6 中断控制器

1.6.1 特性

1.6.2 功能描述

1.6.3 建议操作

1.6.4 寄存器

1.7 核心本地中断 (CLINT)

1.7.1 概述

1.7.2 特性

1.7.3 软件中断

1.7.4 定时器计数器与中断

1.7.5 寄存器列表

1.7.6 寄存器

1.8 存储器保护

1.8.1 概述

1.8.2 特性

1.8.3 功能描述

1.8.4 寄存器列表

1.8.5 寄存器

1.9 物理存储器属性 (PMA) 检查器

1.9.1 概述

1.9.2 特性

1.9.3 功能描述

1.9.4 寄存器列表

1.9.5 寄存器

1.10 调试

1.10.1 概述

1.10.2 特性

1.10.3 功能描述

1.10.4 JTAG 控制

1.10.5 寄存器列表

1.10.6 寄存器

1.11 硬件触发器

1.11.1 特性

1.11.2 功能描述

1.11.3 触发执行流程

1.11.4 寄存器列表

1.11.5 寄存器

1.12 追踪

1.12.1 概述

1.12.2 特性

1.12.3 功能描述

1.13 交叉触发调试

1.13.1 概述

1.13.2 特性

1.13.3 功能描述

1.13.4 寄存器列表

1.13.5 寄存器

1.14 专用 IO

1.14.1 概述

1.14.2 特性

1.14.3 功能描述

1.14.4 寄存器列表

1.14.5 寄存器

1.15 原子 (A) 扩展

1.15.1 概述

1.15.2 功能描述

2 RISC-V 追踪编码器 (TRACE)

2.1 术语

2.2 介绍

2.3 特性

2.4 架构概览

2.5 功能描述

2.5.1 同步

2.5.2 锚定

2.5.3 写存储器模式

2.5.4 自动重启

2.6 编码器输出数据包

2.6.1 头部

2.6.2 索引

2.6.3 有效载荷

2.7 中断

2.8 编程流程

2.8.1 使能编码器

2.8.2 关闭编码器

2.8.3 解码数据包

2.9 寄存器列表

2.10 寄存器

3 低功耗处理器

3.1 特性

3.2 配置与状态寄存器 (CSR)

3.2.1 寄存器列表

3.2.2 寄存器

3.3 中断和异常

3.3.1 中断

3.3.2 中断处理

3.3.3 异常

3.4 调试

3.4.1 特性

3.4.2 功能描述

3.4.3 寄存器列表

3.4.4 寄存器

3.5 硬件触发器

3.5.1 特性

3.5.2 功能描述

3.5.3 触发执行流程

3.5.4 寄存器列表

3.5.5 寄存器

3.6 性能计数器

3.7 系统访问

3.7.1 存储器

3.7.2 外设

3.8 事件任务矩阵功能

3.9 睡眠和唤醒流程

3.9.1 特性

3.9.2 流程

3.9.3 唤醒源

3.10 寄存器列表

3.11 寄存器

4 通用 DMA 控制器 (GDMA)

4.1 概述

4.2 特性

4.3 架构

4.4 功能描述

4.4.1 链表

4.4.2 外设到存储及存储到外设的数据传输

4.4.3 存储到存储数据传输

4.4.4 启动 GDMA

4.4.5 读链表

4.4.6 数据传输结束标志

4.4.7 访问片内 RAM

4.4.8 仲裁

4.4.9 事件任务矩阵功能

4.5 GDMA 中断

4.6 编程流程

4.6.1 GDMA TX 通道配置流程

4.6.2 GDMA RX 通道配置流程

4.6.3 GDMA 存储器到存储器配置流程

4.7 寄存器列表

4.8 寄存器

5 系统和存储器

5.1 概述

5.2 主要特性

5.3 功能描述

5.3.1 地址映射

5.3.2 内部存储器

5.3.3 外部存储器

5.3.4 GDMA 地址空间

5.3.5 模块/外设地址空间映射

6 eFuse 控制器 (eFuse)

6.1 概述

6.2 主要特性

6.3 功能描述

6.3.1 结构

6.3.2 烧写参数

6.3.3 用户读取参数

6.3.4 eFuse VDDQ 时序

6.3.5 硬件模块使用参数

6.3.6 中断

6.4 寄存器列表

6.5 寄存器

7 IO MUX 和 GPIO 交换矩阵 (GPIO, IO MUX)

7.1 概述

7.2 主要特性

7.3 结构概览

7.4 通过 GPIO 交换矩阵的外设输入

7.4.1 概述

7.4.2 信号同步

7.4.3 功能描述

7.4.4 简单 GPIO 输入

7.5 通过 GPIO 交换矩阵的外设输出

7.5.1 概述

7.5.2 功能描述

7.5.3 简单 GPIO 输出

7.5.4 Sigma Delta 调制输出 (SDM)

7.6 IO MUX 的直接输入输出功能

7.6.1 概述

7.6.2 功能描述

7.7 LP IO MUX 的低功耗性能和模拟输入输出功能

7.7.1 概述

7.7.2 低功耗性能描述

7.7.3 模拟功能描述

7.8 Light-sleep 模式管脚功能

7.9 GPIO 管脚的 Hold 特性

7.10 GPIO 管脚供电和电源管理

7.10.1 GPIO 管脚供电

7.10.2 电源管理

7.11 外设信号列表

7.12 IO MUX 管脚功能列表

7.13 LP IO MUX 管脚功能列表

7.14 ETM 相关事件和任务

7.14.1 ETM 相关事件

7.14.2 ETM 相关任务

7.15 寄存器列表

7.15.1 GPIO 交换矩阵寄存器列表

7.15.2 IO MUX 寄存器列表

7.15.3 子模块寄存器列表

7.15.4 LP IO MUX 寄存器列表

7.16 寄存器

7.16.1 GPIO 交换矩阵寄存器

7.16.2 IO MUX 寄存器

7.16.3 子模块寄存器

7.16.4 LP IO MUX 寄存器

8 复位和时钟

8.1 复位

8.1.1 概述

8.1.2 结构图

8.1.3 特性

8.1.4 功能描述

8.1.5 外设复位

8.2 时钟

8.2.1 概述

8.2.2 结构图

8.2.3 特性

8.2.4 功能描述

8.3 配置流程

8.3.1 高性能系统时钟配置

8.3.2 低功耗系统时钟配置

8.3.3 外设时钟复位配置

8.4 寄存器列表

8.4.1 PCR 模块寄存器列表

8.4.2 低功耗系统时钟寄存器列表

8.5 寄存器

8.5.1 PCR 模块寄存器

8.5.2 低功耗系统时钟寄存器

9 芯片 Boot 控制

9.1 概述

9.2 功能描述

9.2.1 默认配置

9.2.2 Boot 模式控制

9.2.3 ROM 代码日志打印控制

9.2.4 JTAG 信号源控制

9.2.5 SDIO 输入采样沿和输出驱动沿控制

10 中断矩阵 (INTMTX)

10.1 概述

10.2 特性

10.3 功能描述

10.3.1 外部中断源

10.3.2 CPU 中断

10.3.3 分配外部中断源至 CPU 外部中断

10.3.4 查询外部中断源当前的中断状态

10.4 寄存器列表

10.4.1 中断矩阵寄存器列表

10.4.2 中断优先级寄存器列表

10.5 寄存器

10.5.1 中断矩阵寄存器

10.5.2 中断优先级寄存器

11 事件任务矩阵 (SOC_ETM)

11.1 概述

11.2 特性

11.3 功能描述

11.3.1 架构

11.3.2 事件

11.3.3 任务

11.3.4 时序考虑因素

11.3.5 通道控制

11.4 寄存器列表

11.5 寄存器

12 系统定时器 (SYSTIMER)

12.1 概述

12.2 主要特性

12.3 时钟源选择

12.4 功能描述

12.4.1 计数器

12.4.2 比较器和报警

12.4.3 事件任务矩阵

12.4.4 同步操作

12.4.5 中断

12.5 编程示例

12.5.1 读取当前计数器的值

12.5.2 在单次报警模式下配置一次性报警

12.5.3 在周期报警模式下配置周期性报警

12.5.4 唤醒后时间补偿

12.6 寄存器列表

12.7 寄存器

13 定时器组 (TIMG)

13.1 概述

13.2 主要特性

13.3 功能描述

13.3.1 16 位预分频器与时钟选择器

13.3.2 54 位时基计数器

13.3.3 报警产生

13.3.4 定时器重新加载

13.3.5 事件任务矩阵功能

13.3.6 RTC 慢速时钟 (RTC_SLOW_CLK) 频率计算

13.3.7 中断

13.4 配置与使用

13.4.1 定时器用作简单时钟

13.4.2 定时器用于单次报警

13.4.3 通过 APB 设置定时器用于周期性报警

13.4.4 通过 ETM 设置定时器用于周期性报警

13.4.5 RTC_SLOW_CLK 频率计算

13.5 寄存器列表

13.6 寄存器

14 看门狗定时器 (WDT)

14.1 概述

14.2 数字看门狗定时器

14.2.1 主要特性

14.2.2 功能描述

14.3 超级看门狗定时器

14.3.1 主要特性

14.3.2 SWD 控制器

14.4 中断

14.5 寄存器列表

14.6 寄存器

15 权限控制

15.1 概述

15.2 主要特性

15.3 功能描述

15.3.1 TEE 控制器功能描述

15.3.2 APM 控制器功能描述

15.4 配置流程

15.5 非法访问与中断

15.6 寄存器列表

15.6.1 高性能 APM 寄存器 (HP_APM_REG)

15.6.2 低功耗 APM 寄存器 (LP_APM_REG)

15.6.3 低功耗 APM0 寄存器 (LP_APM0_REG)

15.6.4 高性能 TEE 寄存器

15.6.5 低功耗 TEE 寄存器

15.7 寄存器

15.7.1 高性能 APM 寄存器描述 (HP_APM_REG)

15.7.2 低功耗 APM 寄存器描述 (LP_APM_REG)

15.7.3 低功耗 APM0 寄存器描述 (LP_APM0_REG)

15.7.4 高性能 TEE 寄存器描述

15.7.5 低功耗 TEE 寄存器描述

16 系统寄存器 (HP_SYSTEM)

16.1 概述

16.2 主要特性

16.3 功能描述

16.3.1 外部存储器加密/解密配置

16.3.2 防 DPA 攻击安全控制

16.3.3 软件 ROM 表寄存器

16.3.4 HP/LP 核心调试控制

16.3.5 总线超时保护

16.4 寄存器列表

16.5 寄存器

17 辅助调试 (ASSIST_DEBUG)

17.1 概述

17.2 主要特性

17.3 功能描述

17.3.1 区域读写监测

17.3.2 栈指针监测

17.3.3 PC 记录

17.3.4 CPU/DMA 总线访问记录

17.4 工作流程

17.4.1 区域监测和栈监测配置

17.4.2 PC 记录配置

17.4.3 CPU/DMA 总线访问记录配置

17.5 寄存器列表

17.5.1 总线记录配置寄存器列表

17.5.2 其它寄存器列表

17.6 寄存器

17.6.1 总线记录配置寄存器

17.6.2 其它寄存器

18 AES 加速器 (AES)

18.1 概述

18.2 主要特性

18.3 工作模式简介

18.4 Typical AES 工作模式

18.4.1 密钥、明文、密文

18.4.2 字节序

18.4.3 Typical AES 工作模式的流程

18.5 DMA-AES 工作模式

18.5.1 密钥、明文、密文

18.5.2 字节序

18.5.3 标准增量函数

18.5.4 块个数

18.5.5 初始向量

18.5.6 DMA-AES 工作模式的流程

18.6 存储器列表

18.7 寄存器列表

18.8 寄存器

19 ECC 加速器 (ECC)

19.1 概述

19.2 主要特性

19.3 专业名词定义

19.3.1 ECC 背景知识

19.3.2 ESP32-C6 ECC 相关定义

19.4 功能描述

19.4.1 密钥长度模式

19.4.2 工作模式

19.5 时钟与复位

19.6 中断

19.7 软件配置流程

19.8 寄存器列表

19.9 寄存器

20 HMAC 加速器 (HMAC)

20.1 主要特性

20.2 功能描述

20.2.1 上行模式

20.2.2 下行 JTAG 启动模式

20.2.3 下行数字签名模式

20.2.4 HMAC eFuse 配置

20.2.5 调用 HMAC 流程(详细说明)

20.3 HMAC 算法细节

20.3.1 附加填充位

20.3.2 HMAC 算法结构

20.4 寄存器列表

20.5 寄存器

21 RSA 加速器 (RSA)

21.1 概述

21.2 主要特性

21.3 功能描述

21.3.1 大数模幂运算

21.3.2 大数模乘运算

21.3.3 大数乘法运算

21.3.4 控制加速

21.4 存储器列表

21.5 寄存器列表

21.6 寄存器

22 SHA 加速器 (SHA)

22.1 概述

22.2 主要特性

22.3 工作模式简介

22.4 功能描述

22.4.1 信息预处理

22.4.2 哈希运算流程

22.4.3 信息摘要存储

22.4.4 中断

22.5 寄存器列表

22.6 寄存器

23 数字签名 (DS)

23.1 概述

23.2 主要特性

23.3 功能描述

23.3.1 概述

23.3.2 私钥运算子

23.3.3 软件准备工作

23.3.4 硬件工作流程

23.3.5 软件工作流程

23.4 存储器列表

23.5 寄存器列表

23.6 寄存器

24 片外存储器加密与解密 (XTS_AES)

24.1 概述

24.2 主要特性

24.3 模块结构

24.4 功能描述

24.4.1 XTS 算法

24.4.2 密钥

24.4.3 目标空间

24.4.4 数据写入

24.4.5 手动加密模块

24.4.6 自动解密模块

24.5 软件流程

24.6 抗 DPA 攻击

24.7 寄存器列表

24.8 寄存器

25 随机数发生器 (RNG)

25.1 概述

25.2 主要特性

25.3 功能描述

25.4 编程指南

25.5 寄存器列表

25.6 寄存器

26 UART 控制器 (UART, LP_UART, UHCI)

26.1 概述

26.2 主要特性

26.3 UART 架构

26.4 功能描述

26.4.1 时钟与复位

26.4.2 UART FIFO

26.4.3 波特率产生与检测

26.4.4 UART 数据帧

26.4.5 AT_CMD字符格式

26.4.6 RS485

26.4.7 IrDA

26.4.8 唤醒

26.4.9 流控

26.4.10 GDMA 模式

26.4.11 UART 中断

26.4.12 UCHI 中断

26.5 编程流程

26.5.1 寄存器类型

26.5.2 具体步骤

26.6 寄存器列表

26.6.1 UART寄存器列表

26.6.2 LP UART寄存器列表

26.6.3 UHCI寄存器列表

26.7 寄存器

26.7.1 UART寄存器

26.7.2 LP UART寄存器

26.7.3 UHCI寄存器

27 SPI 控制器 (SPI)

27.1 概述

27.2 术语

27.3 特性

27.4 架构概览

27.5 功能描述

27.5.1 数据模式

27.5.2 FSPI 总线信号描述

27.5.3 数据位读/写顺序控制

27.5.4 传输类型

27.5.5 CPU 控制的数据传输

27.5.6 DMA 控制的数据传输

27.5.7 GP-SPI2 用作主机和从机时的数据流控制

27.5.8 GP-SPI2 用作主机

27.5.9 GP-SPI2 用作从机

27.6 CS 建立时间和保持时间控制

27.7 GP-SPI2 时钟控制

27.7.1 时钟相位和极性

27.7.2 主机时钟控制

27.7.3 从机时钟控制

27.8 GP-SPI2 时序补偿

27.9 中断

27.10 寄存器列表

27.11 寄存器

28 I2C 控制器 (I2C)

28.1 概述

28.2 主要特性

28.3 I2C 架构

28.4 功能描述

28.4.1 时钟配置

28.4.2 滤除 SCL 和 SDA 噪声

28.4.3 SCL 时钟拉伸

28.4.4 SCL 空闲时产生 SCL 脉冲

28.4.5 同步

28.4.6 漏级开路输出

28.4.7 时序参数配置

28.4.8 超时控制

28.4.9 指令配置

28.4.10 TX/RX RAM数据存储

28.4.11 数据转换

28.4.12 寻址模式

28.4.13 10 位寻址的读写标志位检查

28.4.14 启动控制器

28.5 LP_I2C 和 I2C 的功能差异

28.6 编程示例

28.6.1 I2C 主机写入从机,7 位寻址,单次命令序列

28.6.2 I2C 主机写入从机,10 位寻址,单次命令序列

28.6.3 I2C 主机写入从机,7 位双地址寻址,单次命令序列

28.6.4 I2C 主机写入从机,7 位寻址,多次命令序列

28.6.5 I2C 主机读取从机,7 位寻址,单次命令序列

28.6.6 I2C 主机读取从机,10 位寻址,单次命令序列

28.6.7 I2C 主机读取从机,7 位双寻址,单次命令序列

28.6.8 I2C 主机读取从机,7 位寻址,多次命令序列

28.7 中断

28.8 寄存器列表

28.8.1 I2C 寄存器列表

28.8.2 LP_I2C 寄存器列表

28.9 寄存器

28.9.1 I2C 寄存器

28.9.2 LP_I2C 寄存器

29 I2S 控制器 (I2S)

29.1 概述

29.2 术语

29.3 特性

29.4 系统架构

29.5 I2S 模块支持的音频协议

29.5.1 TDM Philips 标准模式

29.5.2 TDM MSB 对齐标准模式

29.5.3 TDM PCM 标准模式

29.5.4 PDM 标准模式

29.6 I2S TX/RX 模块时钟

29.7 I2S 模块复位

29.8 I2S 主/从机模式

29.8.1 主/从机发送模式

29.8.2 主/从机接收模式

29.9 发送数据

29.9.1 数据格式控制

29.9.2 通道模式控制

29.10 接收数据

29.10.1 通道模式控制

29.10.2 数据格式控制

29.11 软件配置流程

29.11.1 软件配置 I2S 发送流程

29.11.2 软件配置 I2S 接收流程

29.12 I2S 中断

29.12.1 事件任务矩阵功能

29.13 寄存器列表

29.14 寄存器

30 脉冲计数控制器 (PCNT)

30.1 主要特性

30.2 功能描述

30.3 应用实例

30.3.1 通道 0 独自递增计数

30.3.2 通道 0 独自递减计数

30.3.3 通道 0 和通道 1 同时递增计数

30.4 寄存器列表

30.5 寄存器

31 USB 串口/JTAG 控制器 (USB_SERIAL_JTAG)

31.1 概述

31.2 特性

31.3 功能描述

31.3.1 CDC-ACM USB 接口描述

31.3.2 CDC-ACM 固件接口描述

31.3.3 USB-JTAG 接口:JTAG 命令处理器

31.3.4 USB-JTAG 接口:CMD_REP 使用示例

31.3.5 USB-JTAG 接口:响应捕捉单元

31.3.6 USB-JTAG 接口:控制传输请求

31.4 操作建议

31.5 中断

31.6 寄存器列表

31.7 寄存器

32 双线汽车接口 (TWAI)

32.1 主要特性

32.2 协议概述

32.2.1 TWAI 性能

32.2.2 TWAI 报文

32.2.3 TWAI 错误

32.2.4 TWAI 位时序

32.3 结构概述

32.3.1 寄存器模块

32.3.2 位流处理器

32.3.3 错误管理逻辑

32.3.4 位时序逻辑

32.3.5 接收滤波器

32.3.6 接收 FIFO

32.4 功能描述

32.4.1 模式

32.4.2 位时序

32.4.3 中断管理

32.4.4 发送缓冲器与接收缓冲器

32.4.5 接收 FIFO 和数据溢出

32.4.6 接收滤波器

32.4.7 错误管理

32.4.8 错误捕捉

32.4.9 仲裁丢失捕捉

32.4.10 收发器自动待机

32.5 寄存器列表

32.6 寄存器

33 SDIO 2.0 从机控制器 (SDIO)

33.1 概述

33.2 主要特性

33.3 结构描述

33.4 协议标准

33.5 功能描述

33.5.1 物理总线

33.5.2 支持命令

33.5.3 I/O function 0 地址空间

33.5.4 I/O function 1/2 地址空间

33.5.5 DMA

33.5.6 SDIO 总线时序

33.6 中断

33.6.1 主机侧中断

33.6.2 从机侧中断

33.7 包的发送和接收流程

33.7.1 从机向主机发送包

33.7.2 从机从主机接收包

33.8 寄存器列表

33.8.1 HINF 寄存器列表

33.8.2 SLC 寄存器列表

33.8.3 SLC Host 寄存器列表

33.9 寄存器

33.9.1 HINF 寄存器

33.9.2 SLC 寄存器

33.9.3 SLC Host 寄存器

34 LED PWM 控制器 (LEDC)

34.1 概述

34.2 特性

34.3 功能描述

34.3.1 架构

34.3.2 定时器

34.3.3 PWM 生成器

34.3.4 占空比渐变

34.3.5 事件任务矩阵功能

34.3.6 中断

34.4 寄存器列表

34.5 寄存器

35 电机控制脉宽调制器 (MCPWM)

35.1 概述

35.2 主要特性

35.3 模块

35.3.1 概述

35.3.2 PWM 定时器模块

35.3.3 PWM 操作器模块

35.3.4 捕获模块

35.3.5 ETM 模块

35.4 寄存器列表

35.5 寄存器

36 红外遥控 (RMT)

36.1 概述

36.2 主要特性

36.3 功能描述

36.3.1 RMT 架构

36.3.2 RMT RAM

36.3.3 时钟

36.3.4 发射器

36.3.5 接收器

36.3.6 配置参数更新

36.3.7 中断

36.4 寄存器列表

36.5 寄存器

37 并行 IO 控制器 (PARL_IO)

37.1 概况

37.2 术语

37.3 特性

37.4 系统架构

37.5 功能描述

37.5.1 时钟生成器

37.5.2 时钟复位使用限制

37.5.3 主从机模式

37.5.4 RX 模块接收模式

37.5.5 RX 模块 GDMA SUC EOF 信号生成

37.5.6 RX 模块超时

37.5.7 TX 模块有效信号输出

37.5.8 TX 模块总线空闲值

37.5.9 单帧数据传输

37.5.10 字节范围内数据重排

37.6 配置流程

37.6.1 数据接收操作流程

37.6.2 数据发送操作流程

37.7 应用示例

37.7.1 与 SPI 进行数据传输

37.7.2 与 I2S 进行数据传输

37.7.3 与 Camera 进行数据传输

37.8 中断

37.9 寄存器列表

37.10 寄存器

38 片上传感器与模拟信号处理

38.1 概述

38.2 SAR ADC

38.2.1 概述

38.2.2 特性

38.2.3 功能描述

38.3 温度传感器

38.3.1 概述

38.3.2 特性

38.3.3 功能描述

38.4 事件任务矩阵功能

38.4.1 SAR ADC 的 ETM 功能

38.4.2 温度传感器 的 ETM 功能

38.5 中断

38.6 寄存器列表

38.7 寄存器

39 相关文档和资源

词汇列表

外设相关词汇

寄存器相关缩写

寄存器的访问类型

如何配置寄存器的保留域

概述

如何配置保留域

修订历史

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf