Table of Contents

List of Figures

List of Tables

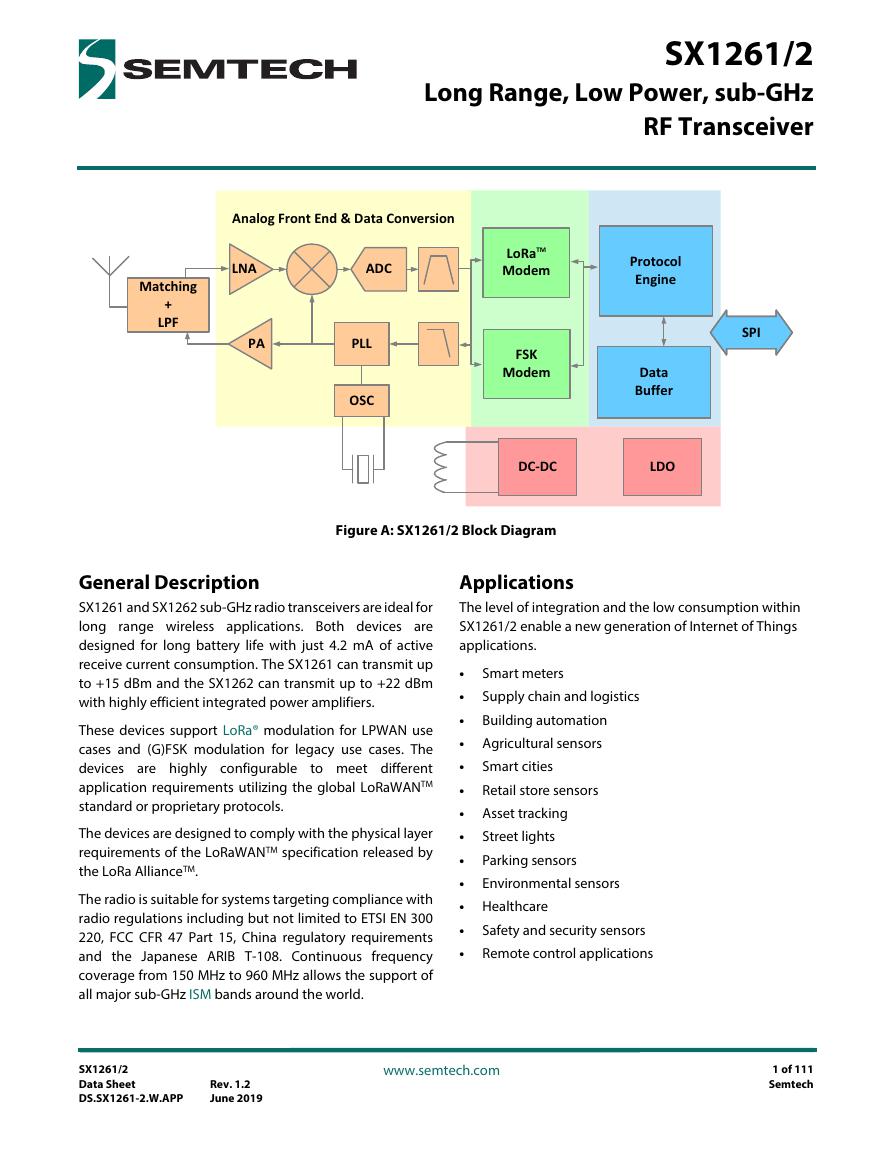

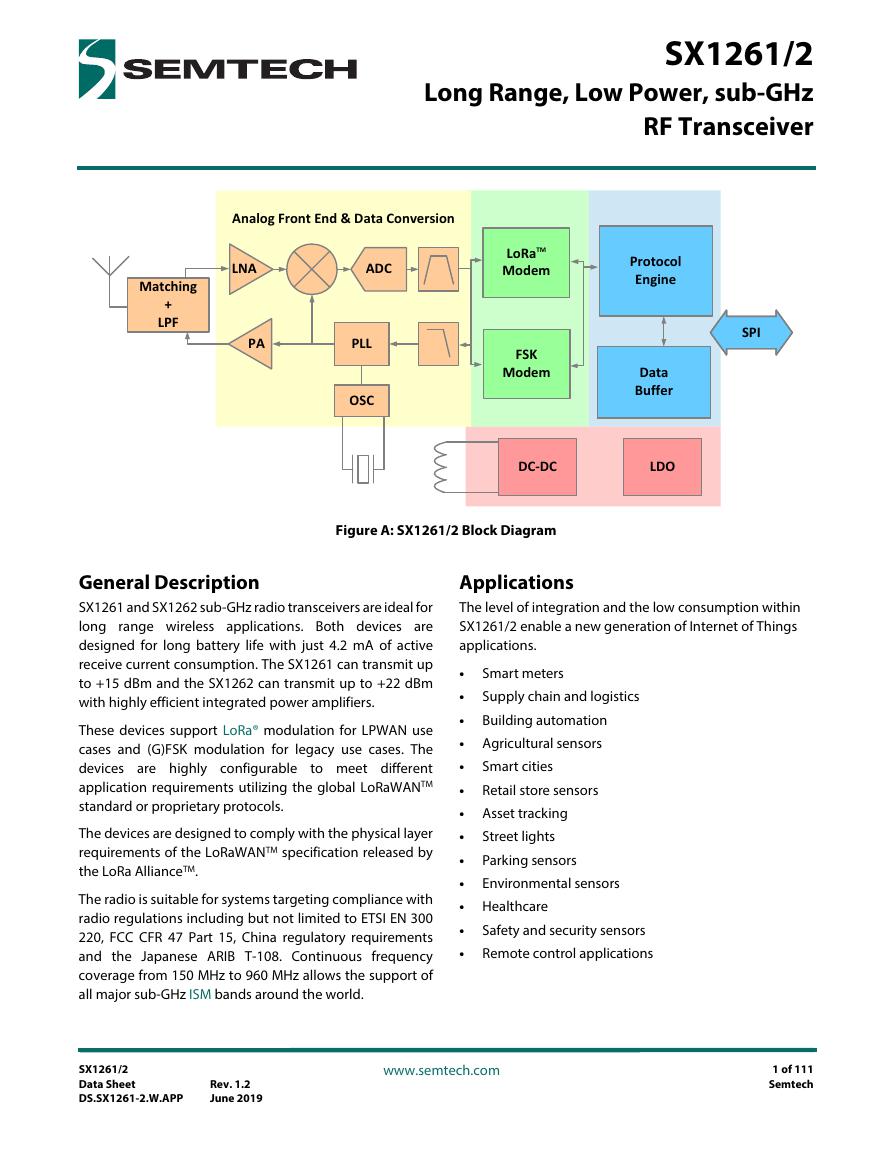

1. Architecture

2. Pin Connection

2.1 I/O Description

2.2 Package View

3. Specifications

3.1 ESD Notice

3.2 Absolute Maximum Ratings

3.3 Operating Range

3.4 Crystal Specifications

3.5 Electrical Specifications

3.5.1 Power Consumption

3.5.2 General Specifications

3.5.3 Receive Mode Specifications

3.5.4 Transmit Mode Specifications

3.5.5 Digital I/O Specifications

4. Circuit Description

4.1 Clock References

4.1.1 RC Frequency References

4.1.2 High-Precision Frequency Reference

4.1.3 XTAL Control Block

4.1.4 TCXO Control Block

4.2 Phase-Locked Loop (PLL)

4.3 Receiver

4.3.1 Intermediate Frequencies

4.4 Transmitter

4.4.1 SX1261 Power Amplifier Specifics

4.4.2 SX1262 Power Amplifier Specifics

4.4.3 Power Amplifier Summary

5. Power Distribution

5.1 Selecting DC-DC Converter or LDO Regulation

5.1.1 Option A: SX1261 with DC-DC Regulator

5.1.2 Option B: SX1261 with LDO Regulator

5.1.3 Option C: SX1262 with DC-DC Regulator

5.1.4 Option D: SX1262 with LDO Regulator

5.1.5 Consideration on the DC-DC Inductor Selection

5.2 Flexible DIO Supply

6. Modems

6.1 LoRa® Modem

6.1.1 Modulation Parameter

6.1.2 LoRa® Packet Engine

6.1.3 LoRa® Frame

6.1.4 LoRa® Time-on-Air

6.1.5 LoRa® Channel Activity Detection (CAD)

6.2 FSK Modem

6.2.1 Modulation Parameter

6.2.2 FSK Packet Engine

6.2.3 FSK Packet Format

7. Data Buffer

7.1 Principle of Operation

7.2 Data Buffer in Receive Mode

7.3 Data Buffer in Transmit Mode

7.4 Using the Data Buffer

8. Digital Interface and Control

8.1 Reset

8.2 SPI Interface

8.2.1 SPI Timing When the Transceiver is in Active Mode

8.2.2 SPI Timing When the Transceiver Leaves Sleep Mode

8.3 Multi-Purpose Digital Input/Output (DIO)

8.3.1 BUSY Control Line

8.3.2 Digital Input/Output

8.4 Digital Interface Status versus Chip modes

8.5 IRQ Handling

9. Operational Modes

9.1 Startup

9.2 Calibration

9.2.1 Image Calibration for Specific Frequency Bands

9.3 Sleep Mode

9.4 Standby (STDBY) Mode

9.5 Frequency Synthesis (FS) Mode

9.6 Receive (RX) Mode

9.6.1 PA Ramping

9.7 Active Mode Switching Time

9.8 Transceiver Circuit Modes Graphical Illustration

10. Host Controller Interface

10.1 Command Structure

10.2 Transaction Termination

11. List of Commands

11.1 Operational Modes Commands

11.2 Register and Buffer Access Commands

11.3 DIO and IRQ Control

11.4 RF, Modulation and Packet Commands

11.5 Status Commands

12. Register Map

12.1 Register Table

13. Commands Interface

13.1 Operational Modes Functions

13.1.1 SetSleep

13.1.2 SetStandby

13.1.3 SetFs

13.1.4 SetTx

13.1.5 SetRx

13.1.6 StopTimerOnPreamble

13.1.7 SetRxDutyCycle

13.1.8 SetCAD

13.1.9 SetTxContinuousWave

13.1.10 SetTxInfinitePreamble

13.1.11 SetRegulatorMode

13.1.12 Calibrate Function

13.1.13 CalibrateImage

13.1.14 SetPaConfig

13.1.15 SetRxTxFallbackMode

13.2 Registers and Buffer Access

13.2.1 WriteRegister Function

13.2.2 ReadRegister Function

13.2.3 WriteBuffer Function

13.2.4 ReadBuffer Function

13.3 DIO and IRQ Control Functions

13.3.1 SetDioIrqParams

13.3.2 IrqMask

13.3.3 GetIrqStatus

13.3.4 ClearIrqStatus

13.3.5 SetDIO2AsRfSwitchCtrl

13.3.6 SetDIO3AsTCXOCtrl

13.4 RF Modulation and Packet-Related Functions

13.4.1 SetRfFrequency

13.4.2 SetPacketType

13.4.3 GetPacketType

13.4.4 SetTxParams

13.4.5 SetModulationParams

13.4.6 SetPacketParams

13.4.7 SetCadParams

13.4.8 SetBufferBaseAddress

13.4.9 SetLoRaSymbNumTimeout

13.5 Communication Status Information

13.5.1 GetStatus

13.5.2 GetRxBufferStatus

13.5.3 GetPacketStatus

13.5.4 GetRssiInst

13.5.5 GetStats

13.5.6 ResetStats

13.6 Miscellaneous

13.6.1 GetDeviceErrors

13.6.2 ClearDeviceErrors

14. Application

14.1 HOST API Basic Read Write Function

14.2 Circuit Configuration for Basic Tx Operation

14.3 Circuit Configuration for Basic Rx Operation

14.4 Issuing Commands in the Right Order

14.5 Application Schematics

14.5.1 Application Design of the SX1261 with RF Switch

14.5.2 Application Design of the SX1262 with RF Switch

15. Known Limitations

15.1 Modulation Quality with 500 kHz LoRa® Bandwidth

15.1.1 Description

15.1.2 Workaround

15.2 Better Resistance of the SX1262 Tx to Antenna Mismatch

15.2.1 Description

15.2.2 Workaround

15.3 Implicit Header Mode Timeout Behavior

15.3.1 Description

15.3.2 Workaround

15.4 Optimizing the Inverted IQ Operation

15.4.1 Description

15.4.2 Workaround

16. Packaging Information

16.1 Package Outline Drawing

16.2 Package Marking

16.3 Land Pattern

16.4 Reflow Profiles

Glossary

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf