6. Cyclone IV 器件中的 I/O 特性

November 2011

CYIV-51006-2.3

CYIV-51006-2.3

本章节介绍了 Cyclone® IV 器件所支持的 I/O 与高速 I/O 的性能和特性。

Cyclone IV 器件的 I/O 功能是由许多低成本应用中的多样化 I/O 标准所驱动的,大幅

度提高了 I/O 的性能要求。Altera 的目标是创建一个可以轻松而灵活地容纳您的主模

块设计要的器件。

自从在上一代低成本 FPGA 中实现了在所有的 I/O 块中可以选择所有的 I/O 标准,使得

Cyclone IV 器件的 I/O 灵活性相应增加。改进了片上端接 (OCT) 的支持,另外真差分

缓冲器也已消除了许多应用中所需的外部电阻,例如显示系统 接口。

高速差分 I/O 标准在高速接口中已经很普遍,这是由于它们在单端 I/O 标准中具有显

著的优势。Cyclone IV 器件支持 LVDS、BLVDS、RSDS、mini- LVDS 和 PPDS。收发器参

考时钟和现有的通用 I/O (GPIO)时钟输入功能也支持 LVDS I/O 标准。

Quartus® II 软件完成了具有强大的管脚计划功能的解决方案。实现在您得到设计文件

之前,对 I/O 系统设计的计划和优化。

这一章节包括以下几部分内容:

■ “Cyclone IV 的 I/O 单元 ” 第 6-2 页

■ “I/O 单元特性 ” 第 6-3 页

■ “OCT 支持 ” 第 6-6 页

■ “I/O 标准 ” 第 6-11 页

■ “I/O 标准的匹配方案 ” 第 6-13 页

■ “I/O 块 ” 第 6-16 页

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks

are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications

in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or

liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised

to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 1

2011 年 11 月

Subscribe

�

6–2

第 6 章 :Cyclone IV 器件中的 I/O 特性

Cyclone IV 的 I/O 单元

■ “ 垫布局和直流指南 ” 第 6-22 页

■ “ 时钟管脚功能 ” 第 6-23 页

■ “ 高速 I/O 接口 ” 第 6-23 页

■ “ 高速 I/O 标准支持 ” 第 6-27 页

■ “ 真差分输出缓冲器功能 ” 第 6-34 页

■ “ 高速 I/O 时序 ” 第 6-35 页

■ “ 设计指南 ” 第 6-36 页

■ “ 软件概述 ” 第 6-37 页

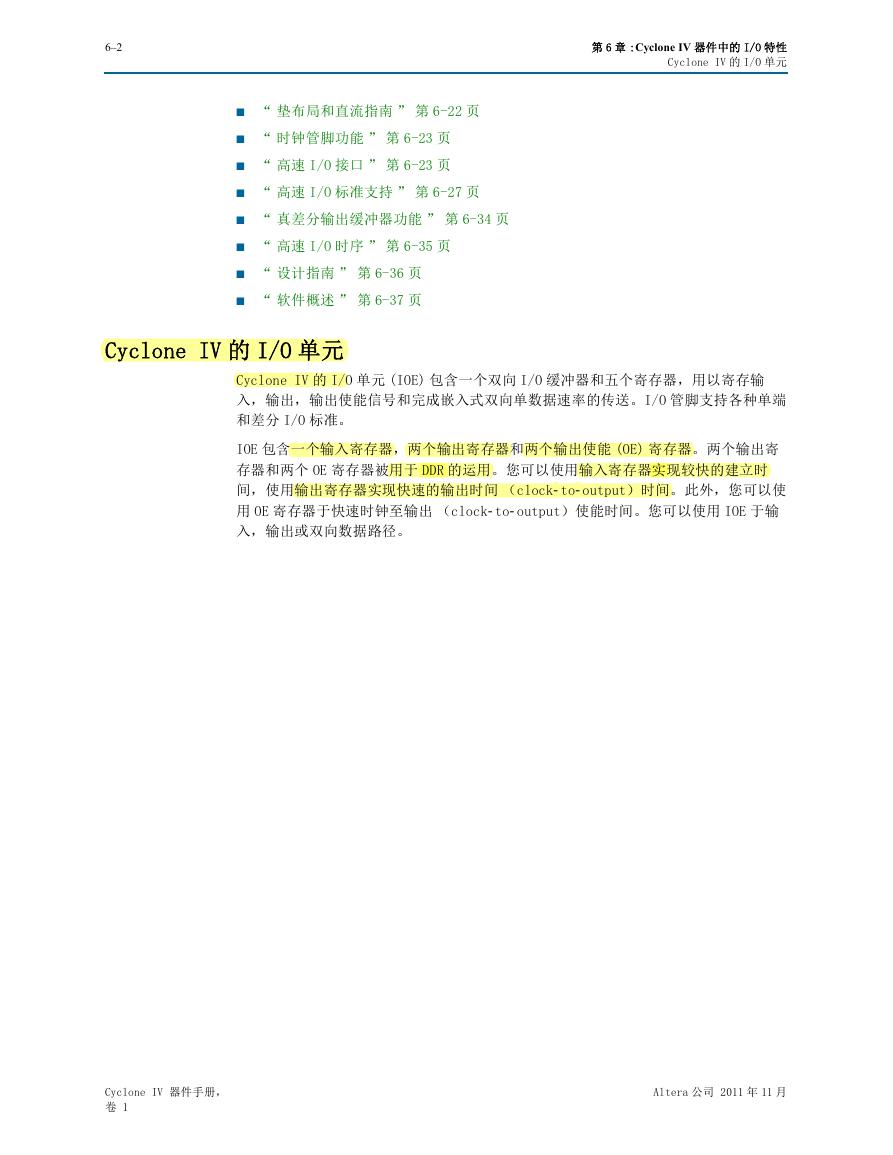

Cyclone IV 的 I/O 单元

Cyclone IV 的 I/O 单元 (IOE) 包含一个双向 I/O 缓冲器和五个寄存器,用以寄存输

入,输出,输出使能信号和完成嵌入式双向单数据速率的传送。I/O 管脚支持各种单端

和差分 I/O 标准。

IOE 包含一个输入寄存器,两个输出寄存器和两个输出使能 (OE) 寄存器。两个输出寄

存器和两个 OE 寄存器被用于 DDR 的运用。您可以使用输入寄存器实现较快的建立时

间,使用输出寄存器实现快速的输出时间 (clock- to- output)时间。此外,您可以使

用 OE 寄存器于快速时钟至输出 (clock- to- output)使能时间。您可以使用 IOE 于输

入,输出或双向数据路径。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 6 章 :Cyclone IV 器件中的 I/O 特性

I/O 单元特性

6–3

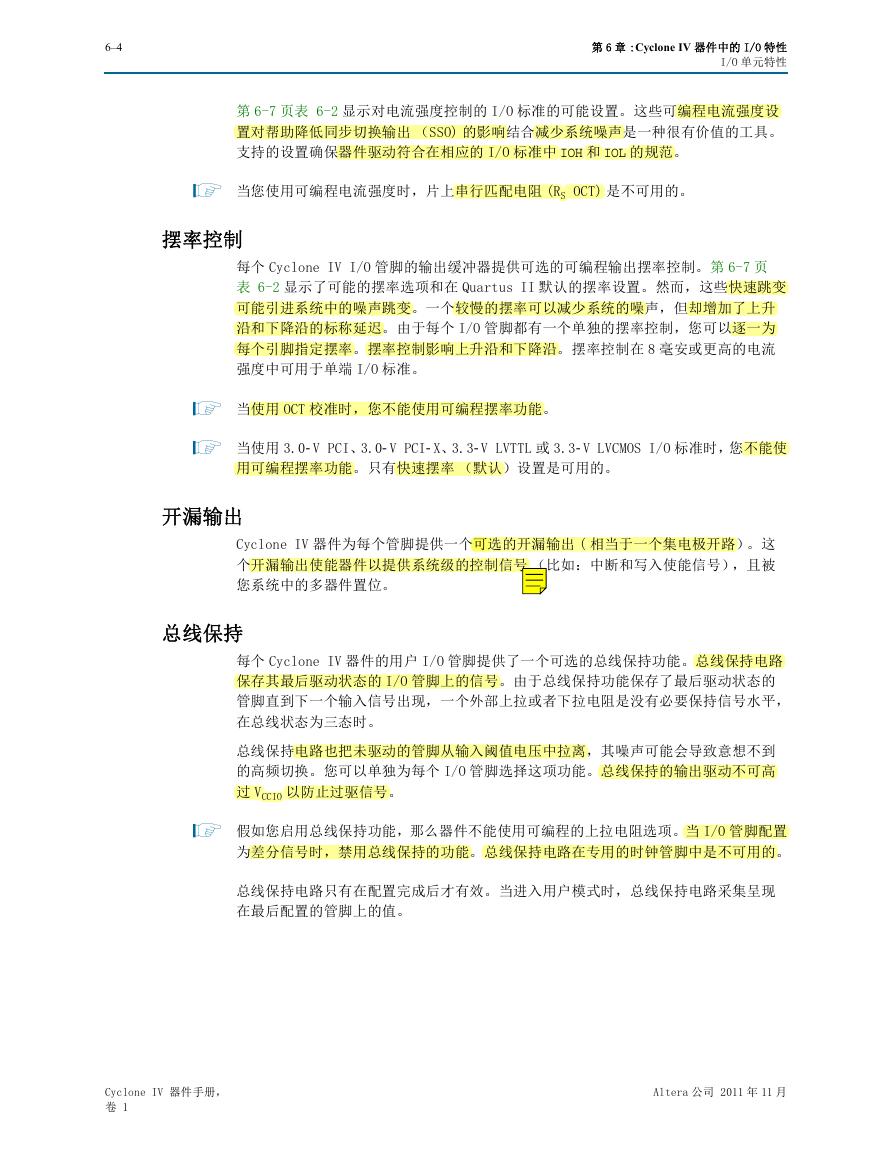

图 6-1 显示了 Cyclone IV 器件 IOE 结构为单数据速率 (SDR) 的操作。

图 6-1. 对于 SDR 模式的 Cyclone IV IOE 的一个双向 I/O 配置

io_clk[5..0]

Column

or Row

Interconnect

OE

clkout

oe_out

aclr/prn

Chip-Wide Reset

sclr/

preset

clkin

oe_in

data_in1

data_in0

OE Register

D

Q

ENA

ACLR

/PRN

VCCIO

Optional

PCI Clamp

VCCIO

Output Register

D

Q

ENA

ACLR

/PRN

Output

Pin Delay

(1)

Current Strength Control

Open-Drain Out

Slew Rate Control

Input Pin to

Input Register

Delay

or Input Pin to

Logic Array

Delay

D

Q

ENA

ACLR

/PRN

Input Register

Programmable

Pull-Up

Resistor

Bus Hold

图 6-1 注释 :

(1) 三态控制不可用于真差分 I/O 标准的输出配置。

I/O 单元特性

Cyclone IV IOE 提供了 I/O 管脚的一系列可编程的特性。这些特性增加了 I/O 利用率

的灵活性,并提供了一个方法以减少外部分立元器件的利用率,例如上拉电阻和二极

管。

可编程电流强度

每个 Cyclone IV I/O 管脚上的输出缓冲器对于某些 I/O 标准有一个可编程电流强度控

制。

LVTTL、LVCMOS、SSTL- 2 Class I 和 II、SSTL- 18 Class I 和 II、HSTL- 18 Class I 和

II、HSTL- 15 Class I 和 II 以及 HSTL- 12 Class I 和 II I/O 标准有几个层次的电流强

度您可以控制。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

6–4

第 6 章 :Cyclone IV 器件中的 I/O 特性

I/O 单元特性

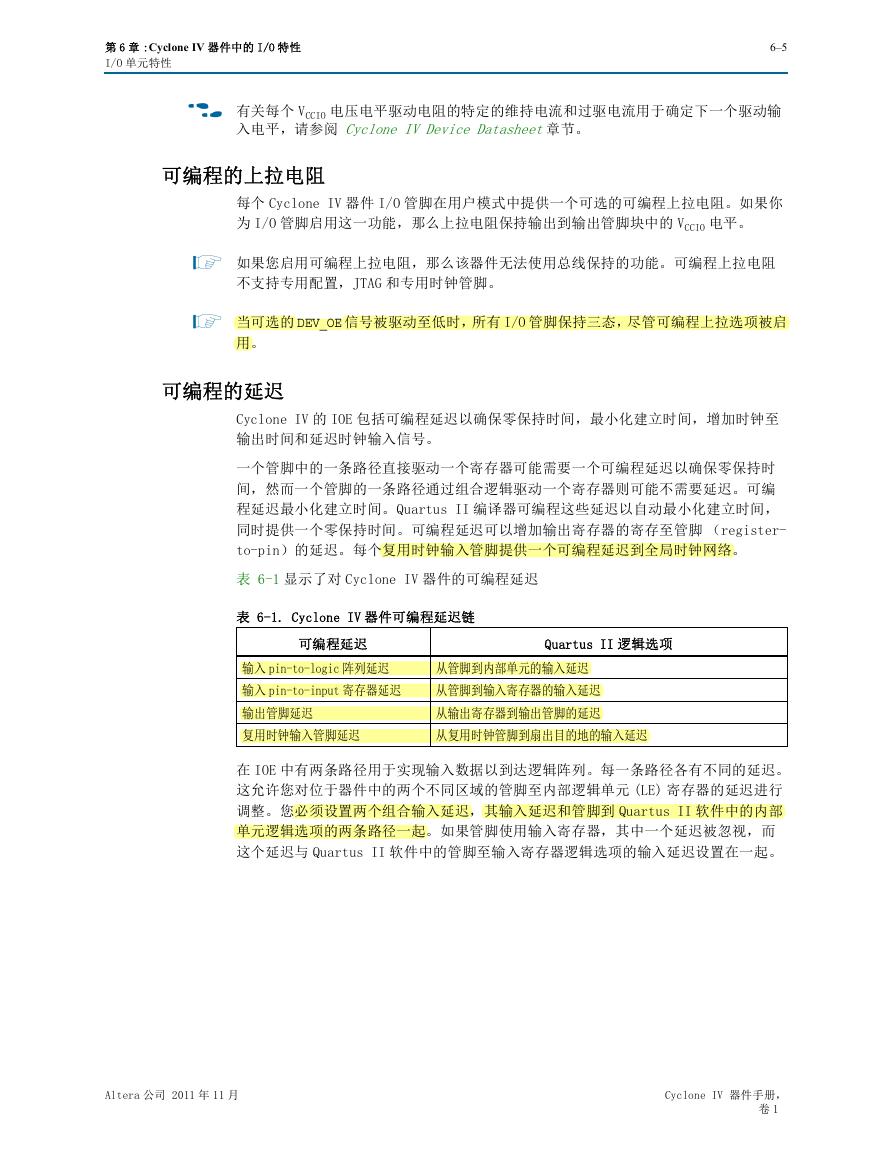

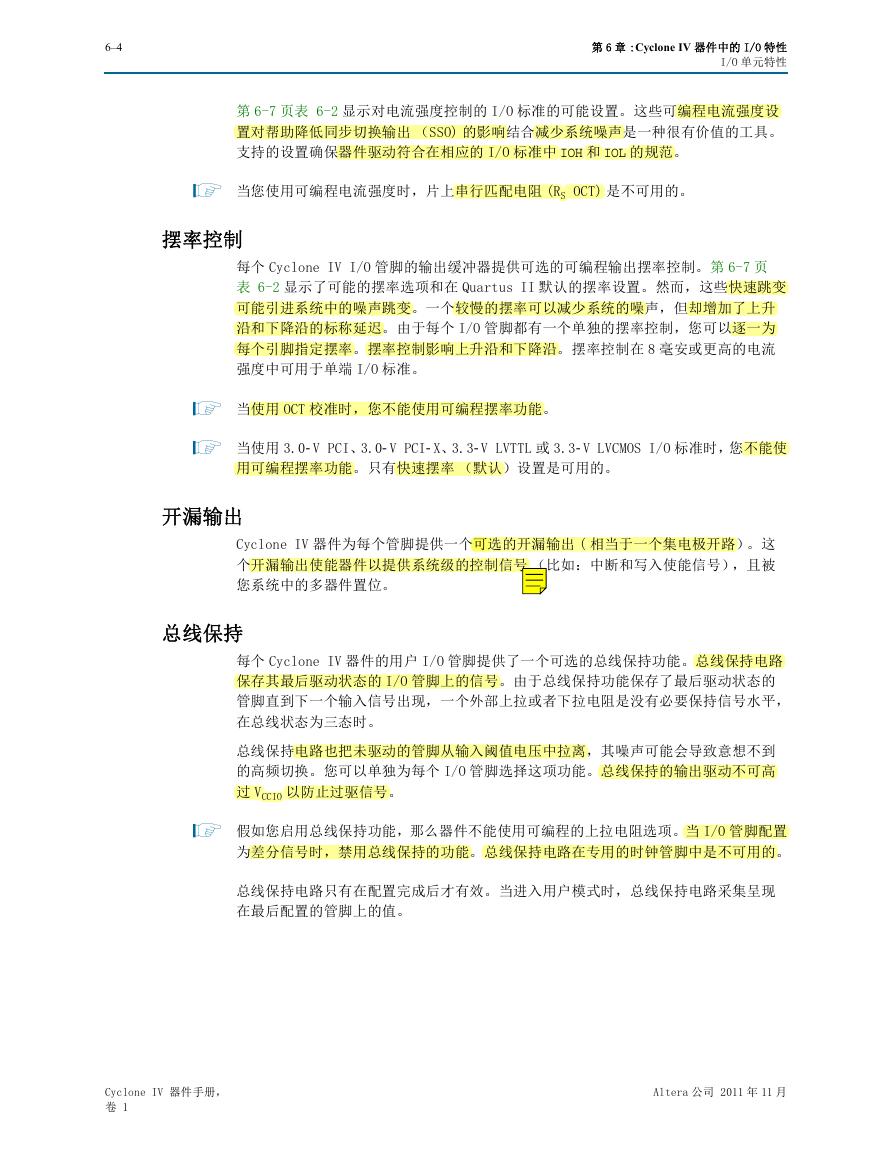

第 6-7 页表 6-2 显示对电流强度控制的 I/O 标准的可能设置。这些可编程电流强度设

置对帮助降低同步切换输出 (SSO) 的影响结合减少系统噪声是一种很有价值的工具。

支持的设置确保器件驱动符合在相应的 I/O 标准中 IOH 和 IOL 的规范。

1 当您使用可编程电流强度时,片上串行匹配电阻 (RS OCT) 是不可用的。

摆率控制

每个 Cyclone IV I/O 管脚的输出缓冲器提供可选的可编程输出摆率控制。第 6-7 页

表 6-2 显示了可能的摆率选项和在 Quartus II 默认的摆率设置。然而,这些快速跳变

可能引进系统中的噪声跳变。一个较慢的摆率可以减少系统的噪声,但却增加了上升

沿和下降沿的标称延迟。由于每个 I/O 管脚都有一个单独的摆率控制,您可以逐一为

每个引脚指定摆率。摆率控制影响上升沿和下降沿。摆率控制在 8 毫安或更高的电流

强度中可用于单端 I/O 标准。

1 当使用 OCT 校准时,您不能使用可编程摆率功能。

1 当使用 3.0- V PCI、3.0- V PCI- X、3.3- V LVTTL 或 3.3- V LVCMOS I/O 标准时,您不能使

用可编程摆率功能。只有快速摆率 (默认)设置是可用的。

开漏输出

Cyclone IV 器件为每个管脚提供一个可选的开漏输出 ( 相当于一个集电极开路)。这

个开漏输出使能器件以提供系统级的控制信号 (比如:中断和写入使能信号),且被

您系统中的多器件置位。

总线保持

每个 Cyclone IV 器件的用户 I/O 管脚提供了一个可选的总线保持功能。总线保持电路

保存其最后驱动状态的 I/O 管脚上的信号。由于总线保持功能保存了最后驱动状态的

管脚直到下一个输入信号出现,一个外部上拉或者下拉电阻是没有必要保持信号水平,

在总线状态为三态时。

总线保持电路也把未驱动的管脚从输入阈值电压中拉离,其噪声可能会导致意想不到

的高频切换。您可以单独为每个 I/O 管脚选择这项功能。总线保持的输出驱动不可高

过 VCCIO 以防止过驱信号。

1 假如您启用总线保持功能,那么器件不能使用可编程的上拉电阻选项。当 I/O 管脚配置

为差分信号时,禁用总线保持的功能。总线保持电路在专用的时钟管脚中是不可用的。

总线保持电路只有在配置完成后才有效。当进入用户模式时,总线保持电路采集呈现

在最后配置的管脚上的值。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 6 章 :Cyclone IV 器件中的 I/O 特性

I/O 单元特性

6–5

f 有关每个 VCCIO 电压电平驱动电阻的特定的维持电流和过驱电流用于确定下一个驱动输

入电平,请参阅 Cyclone IV Device Datasheet章节。

可编程的上拉电阻

每个 Cyclone IV 器件 I/O 管脚在用户模式中提供一个可选的可编程上拉电阻。如果你

为 I/O 管脚启用这一功能,那么上拉电阻保持输出到输出管脚块中的 VCCIO 电平。

1 如果您启用可编程上拉电阻,那么该器件无法使用总线保持的功能。可编程上拉电阻

不支持专用配置,JTAG 和专用时钟管脚。

1 当可选的 DEV_OE 信号被驱动至低时,所有 I/O 管脚保持三态,尽管可编程上拉选项被启

用。

可编程的延迟

Cyclone IV 的 IOE 包括可编程延迟以确保零保持时间,最小化建立时间,增加时钟至

输出时间和延迟时钟输入信号。

一个管脚中的一条路径直接驱动一个寄存器可能需要一个可编程延迟以确保零保持时

间,然而一个管脚的一条路径通过组合逻辑驱动一个寄存器则可能不需要延迟。可编

程延迟最小化建立时间。Quartus II 编译器可编程这些延迟以自动最小化建立时间,

同时提供一个零保持时间。可编程延迟可以增加输出寄存器的寄存至管脚 (register-

to-pin)的延迟。每个复用时钟输入管脚提供一个可编程延迟到全局时钟网络。

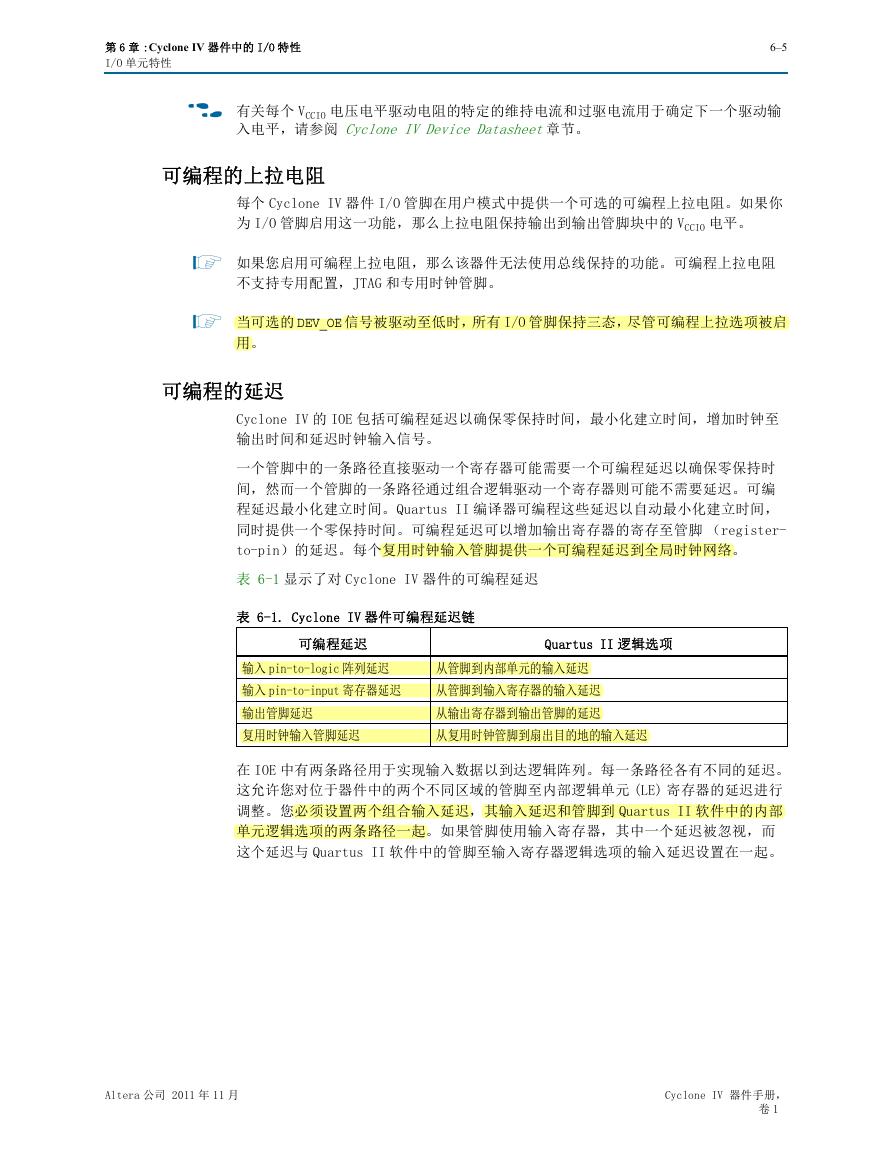

表 6-1 显示了对 Cyclone IV 器件的可编程延迟

表 6-1. Cyclone IV 器件可编程延迟链

可编程延迟

Quartus II 逻辑选项

输入 pin-to-logic 阵列延迟

从管脚到内部单元的输入延迟

输入 pin-to-input 寄存器延迟

从管脚到输入寄存器的输入延迟

输出管脚延迟

从输出寄存器到输出管脚的延迟

复用时钟输入管脚延迟

从复用时钟管脚到扇出目的地的输入延迟

在 IOE 中有两条路径用于实现输入数据以到达逻辑阵列。每一条路径各有不同的延迟。

这允许您对位于器件中的两个不同区域的管脚至内部逻辑单元 (LE) 寄存器的延迟进行

调整。您必须设置两个组合输入延迟,其输入延迟和管脚到 Quartus II 软件中的内部

单元逻辑选项的两条路径一起。如果管脚使用输入寄存器,其中一个延迟被忽视,而

这个延迟与 Quartus II 软件中的管脚至输入寄存器逻辑选项的输入延迟设置在一起。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

6–6

第 6 章 :Cyclone IV 器件中的 I/O 特性

OCT 支持

IOE 寄存器在每个 I/O 模块的预置或清零功能上共享相同的资源。您可以为每个独立的

IOE 编程预置或清零功能,但您不可以同时使用这两项功能。 您也可以在完成配置后,

编程寄存器上电到高电平或低电平。如果编程到低电平,异步清零可以控制寄存器。

如果编程到高电平,异步预置可以控制寄存器。此功能可以防止无意中激活另一个器

件上电后的低电平有效的输入。如果 IOE 中的一个寄存器使用预置或清零信号,那么

在 IOE 中的所有寄存器在他们需要预置或清零信号时必须使用这个相同的信号。此外,

一个同步复位信号在 IOE 寄存器中是可用的。

f 要了解关于输入和输出管脚延迟设置的详细信息,请参阅Quartus II Handbook 第2卷

Area and Timing Optimization 章节。

PCI 钳位二极管

Cyclone IV 器件为每个 I/O 管脚提供一个可选的 PCI-clamp 二极管使能输入和输出。

复用配置管脚在用户模式中支持二极管,如果在选定的配置方案中不使用特定的管脚

作为配置管脚。例如,如果您正使用主动串行 (AS) 模式配置方案,您不可以使用在

用户模式下的 ASDO 和 nCSO 管脚的钳位二极管。专用的配置管脚不支持片上二极管。

PCI-clamp 二极管在以下 I/O 标准中是可用的:

■ 3.3-V LVTTL

■ 3.3-V LVCMOS

■ 3.0-V LVTTL

■ 3.0-V LVCMOS

■ 2.5-V LVTTL/LVCMOS

■ PCI

■ PCI-X

如果输入 I/O 标准是列表标准中的其中一个,PCI-clamp 二极管在 Quartus II 软件中

默认为使能状态。

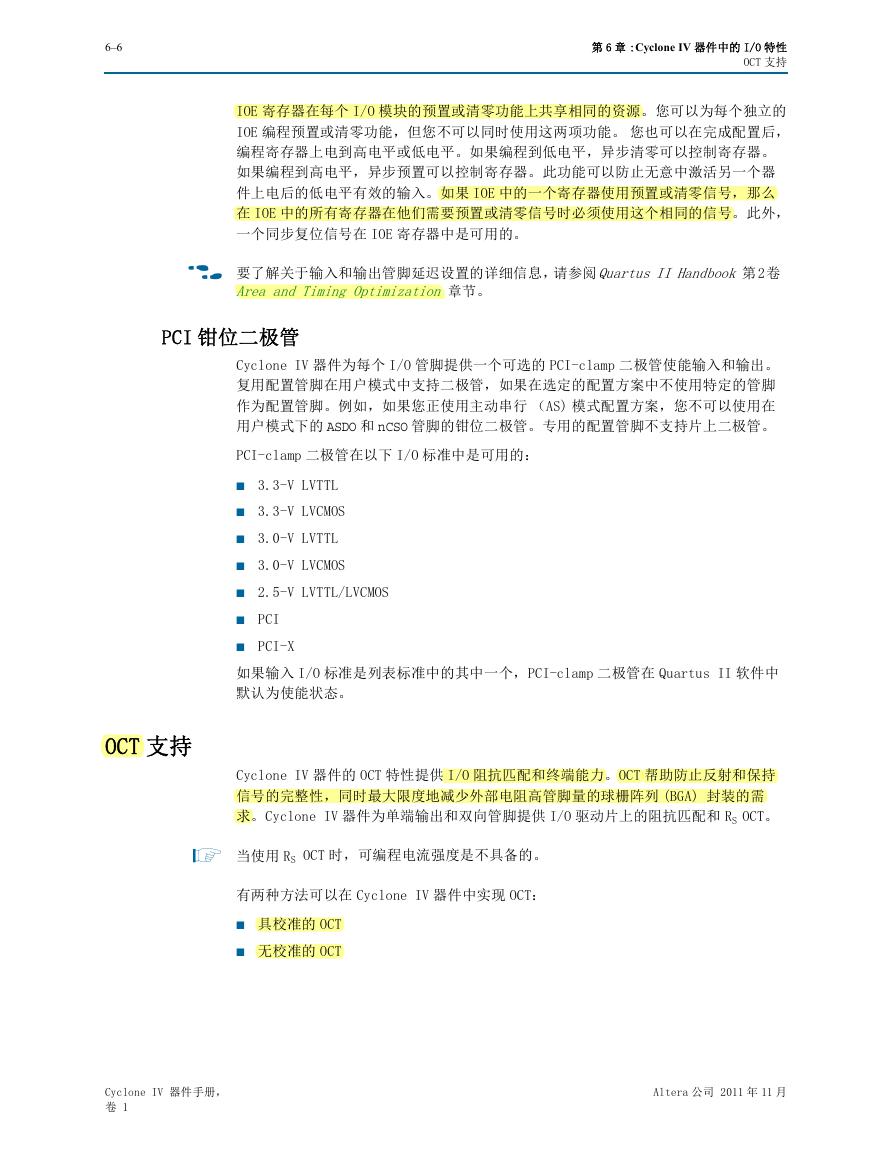

OCT 支持

Cyclone IV 器件的 OCT 特性提供 I/O 阻抗匹配和终端能力。OCT 帮助防止反射和保持

信号的完整性,同时最大限度地减少外部电阻高管脚量的球栅阵列 (BGA) 封装的需

求。Cyclone IV 器件为单端输出和双向管脚提供 I/O 驱动片上的阻抗匹配和 RS OCT。

1 当使用 RS OCT 时,可编程电流强度是不具备的。

有两种方法可以在 Cyclone IV 器件中实现 OCT:

■ 具校准的 OCT

■ 无校准的 OCT

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 6 章 :Cyclone IV 器件中的 I/O 特性

OCT 支持

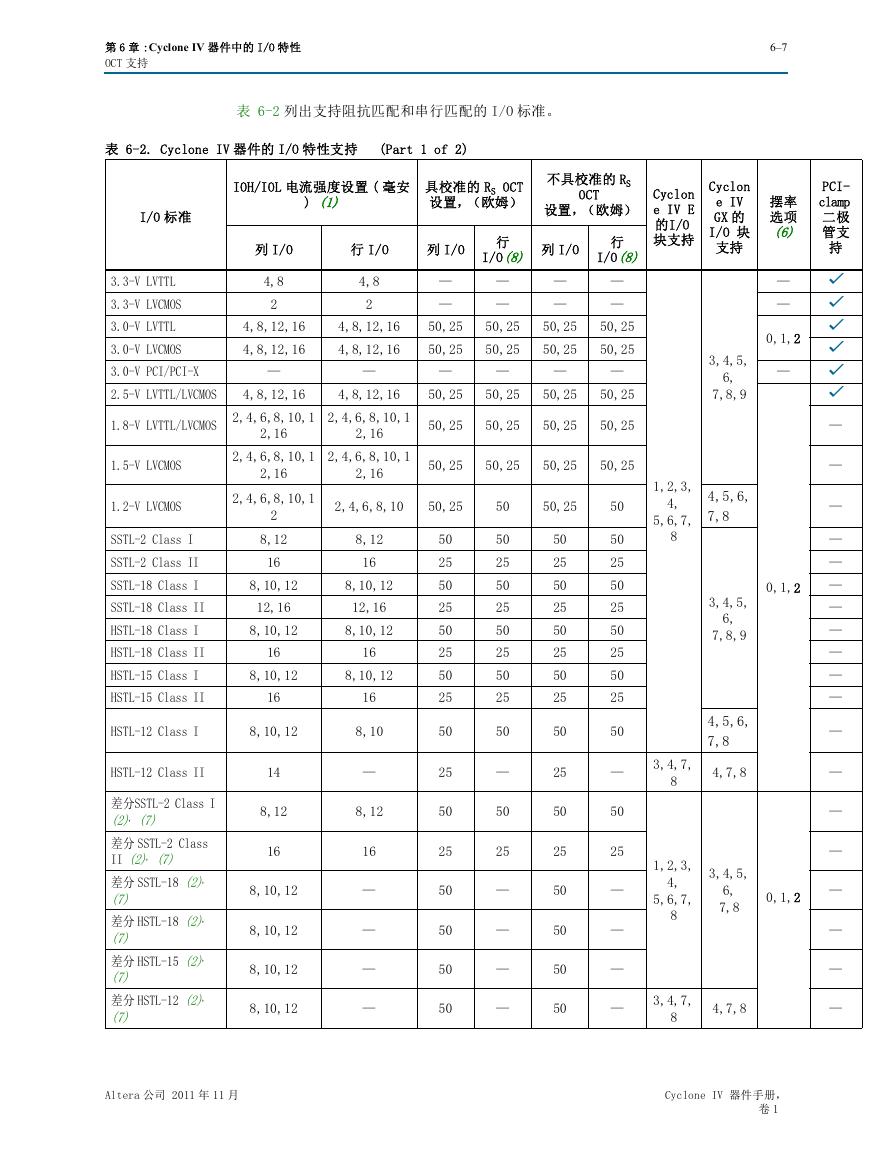

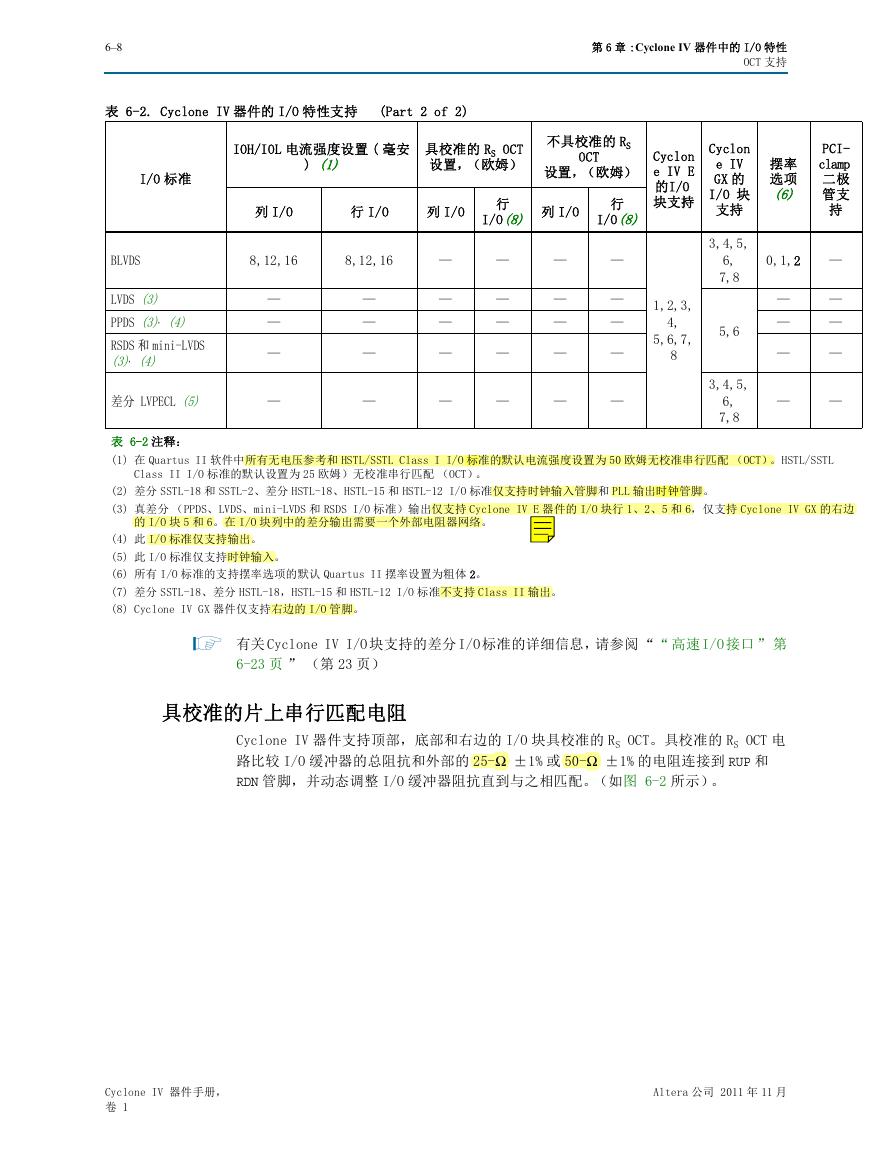

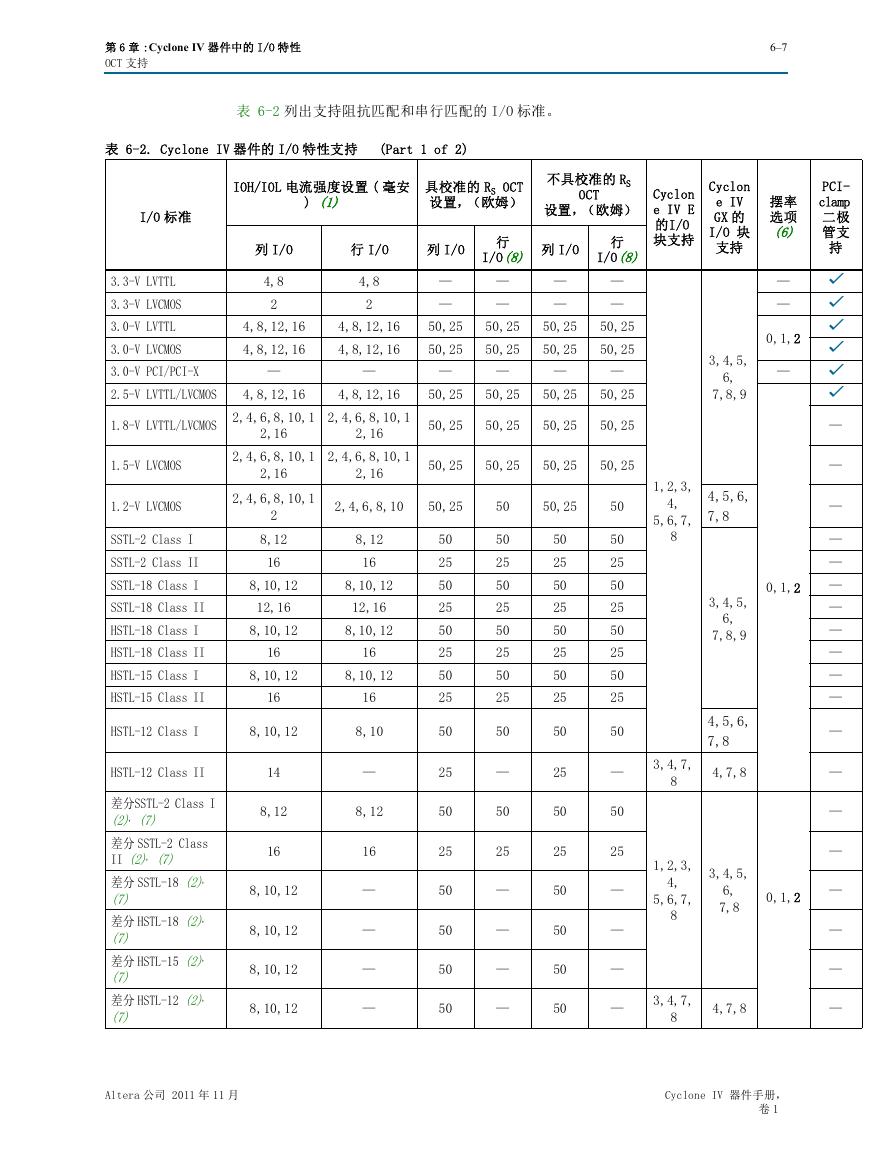

表 6-2 列出支持阻抗匹配和串行匹配的 I/O 标准。

表 6-2. Cyclone IV 器件的 I/O 特性支持

(Part 1 of 2)

IOH/IOL 电流强度设置 ( 毫安

) (1)

具校准的 RS OCT

设置,(欧姆)

不具校准的 RS

OCT

设置,(欧姆)

I/O 标准

列 I/O

行 I/O

列 I/O

行

I/O(8)

列 I/O

行

I/O(8)

Cyclon

e IV E

的I/O

块支持

Cyclon

e IV

GX 的

I/O 块

支持

3.3-V LVTTL

3.3-V LVCMOS

3.0-V LVTTL

3.0-V LVCMOS

4,8

2

4,8

2

—

—

—

—

4,8,12,16

4,8,12,16

50,25

50,25

4,8,12,16

4,8,12,16

50,25

50,25

3.0-V PCI/PCI-X

—

—

—

—

—

—

50,25

50,25

—

—

—

50,25

50,25

—

2.5-V LVTTL/LVCMOS

4,8,12,16

4,8,12,16

50,25

50,25

50,25

50,25

2,4,6,8,10,1

2,4,6,8,10,1

2,16

2,16

2,4,6,8,10,1

2,4,6,8,10,1

2,16

2,16

50,25

50,25

50,25

50,25

50,25

50,25

50,25

50,25

2,4,6,8,10

50,25

1.8-V LVTTL/LVCMOS

1.5-V LVCMOS

1.2-V LVCMOS

SSTL-2 Class I

SSTL-2 Class II

SSTL-18 Class I

SSTL-18 Class II

HSTL-18 Class I

2,4,6,8,10,1

2

8,12

16

8,10,12

12,16

8,10,12

8,12

16

8,10,12

12,16

8,10,12

16

HSTL-18 Class II

16

HSTL-15 Class I

8,10,12

8,10,12

HSTL-15 Class II

16

HSTL-12 Class I

8,10,12

HSTL-12 Class II

14

差分SSTL-2 Class I

(2), (7)

差分 SSTL-2 Class

II (2), (7)

差分 SSTL-18 (2),

(7)

差分 HSTL-18 (2),

(7)

差分 HSTL-15 (2),

(7)

差分 HSTL-12 (2),

(7)

8,12

16

8,10,12

8,10,12

8,10,12

8,10,12

16

8,10

—

8,12

16

—

—

—

—

50

50

25

50

25

50

25

50

25

50

—

50

25

—

—

—

—

50,25

50

25

50

25

50

25

50

25

50

25

50

25

50

50

50

50

50

50

25

50

25

50

25

50

25

50

—

50

25

—

—

—

—

50

25

50

25

50

25

50

25

50

25

50

25

50

50

50

50

6–7

摆率

选项

(6)

—

—

0,1,2

—

3,4,5,

6,

7,8,9

1,2,3,

4,

5,6,7,

8

4,5,6,

7,8

0,1,2

3,4,5,

6,

7,8,9

4,5,6,

7,8

4,7,8

3,4,7,

8

1,2,3,

4,

5,6,7,

8

3,4,5,

6,

7,8

0,1,2

3,4,7,

8

4,7,8

PCI-

clamp

二极

管支

持

v

v

v

v

v

v

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

6–8

第 6 章 :Cyclone IV 器件中的 I/O 特性

OCT 支持

表 6-2. Cyclone IV 器件的 I/O 特性支持

(Part 2 of 2)

IOH/IOL 电流强度设置 ( 毫安

) (1)

具校准的 RS OCT

设置,(欧姆)

不具校准的 RS

OCT

设置,(欧姆)

I/O 标准

列 I/O

行 I/O

列 I/O

行

I/O(8)

列 I/O

行

I/O(8)

BLVDS

8,12,16

8,12,16

LVDS (3)

PPDS (3), (4)

RSDS 和 mini-LVDS

(3), (4)

差分 LVPECL (5)

表 6-2 注释:

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

—

Cyclon

e IV E

的I/O

块支持

1,2,3,

4,

5,6,7,

8

Cyclon

e IV

GX 的

I/O 块

支持

3,4,5,

6,

7,8

5,6

3,4,5,

6,

7,8

摆率

选项

(6)

PCI-

clamp

二极

管支

持

0,1,2

—

—

—

—

—

—

—

—

—

(1) 在 Quartus II 软件中所有无电压参考和 HSTL/SSTL Class I I/O 标准的默认电流强度设置为 50 欧姆无校准串行匹配 (OCT)。HSTL/SSTL

Class II I/O 标准的默认设置为 25 欧姆)无校准串行匹配 (OCT)。

(2) 差分 SSTL-18 和 SSTL-2、差分 HSTL-18、HSTL-15 和 HSTL-12 I/O 标准仅支持时钟输入管脚和 PLL 输出时钟管脚。

(3) 真差分 (PPDS、LVDS、mini-LVDS 和 RSDS I/O 标准)输出仅支持 Cyclone IV E 器件的 I/O 块行 1、2、5 和 6,仅支持 Cyclone IV GX 的右边

的 I/O 块 5 和 6。在 I/O 块列中的差分输出需要一个外部电阻器网络。

(4) 此 I/O 标准仅支持输出。

(5) 此 I/O 标准仅支持时钟输入。

(6) 所有 I/O 标准的支持摆率选项的默认 Quartus II 摆率设置为粗体 2。

(7) 差分 SSTL-18、差分 HSTL-18,HSTL-15 和 HSTL-12 I/O 标准不支持 Class II 输出。

(8) Cyclone IV GX 器件仅支持右边的 I/O 管脚。

1 有关 Cyclone IV I/O 块支持的差分 I/O 标准的详细信息,请参阅 ““ 高速 I/O 接口 ” 第

6-23 页 ” (第 23 页)

具校准的片上串行匹配电阻

Cyclone IV 器件支持顶部,底部和右边的 I/O 块具校准的 RS OCT。具校准的 RS OCT 电

路比较 I/O 缓冲器的总阻抗和外部的 25-Ω ±1% 或 50-Ω ±1% 的电阻连接到 RUP 和

RDN 管脚,并动态调整 I/O 缓冲器阻抗直到与之相匹配。(如图 6-2 所示)。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf