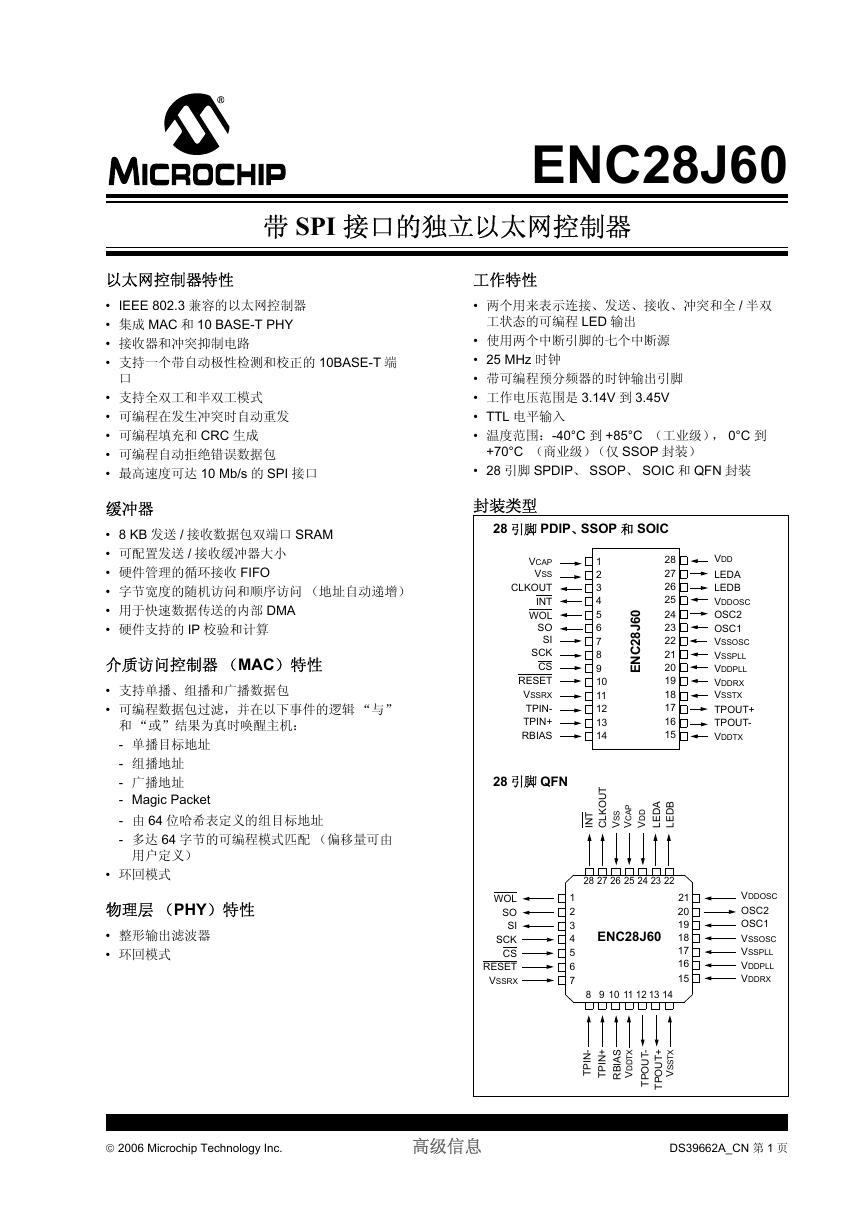

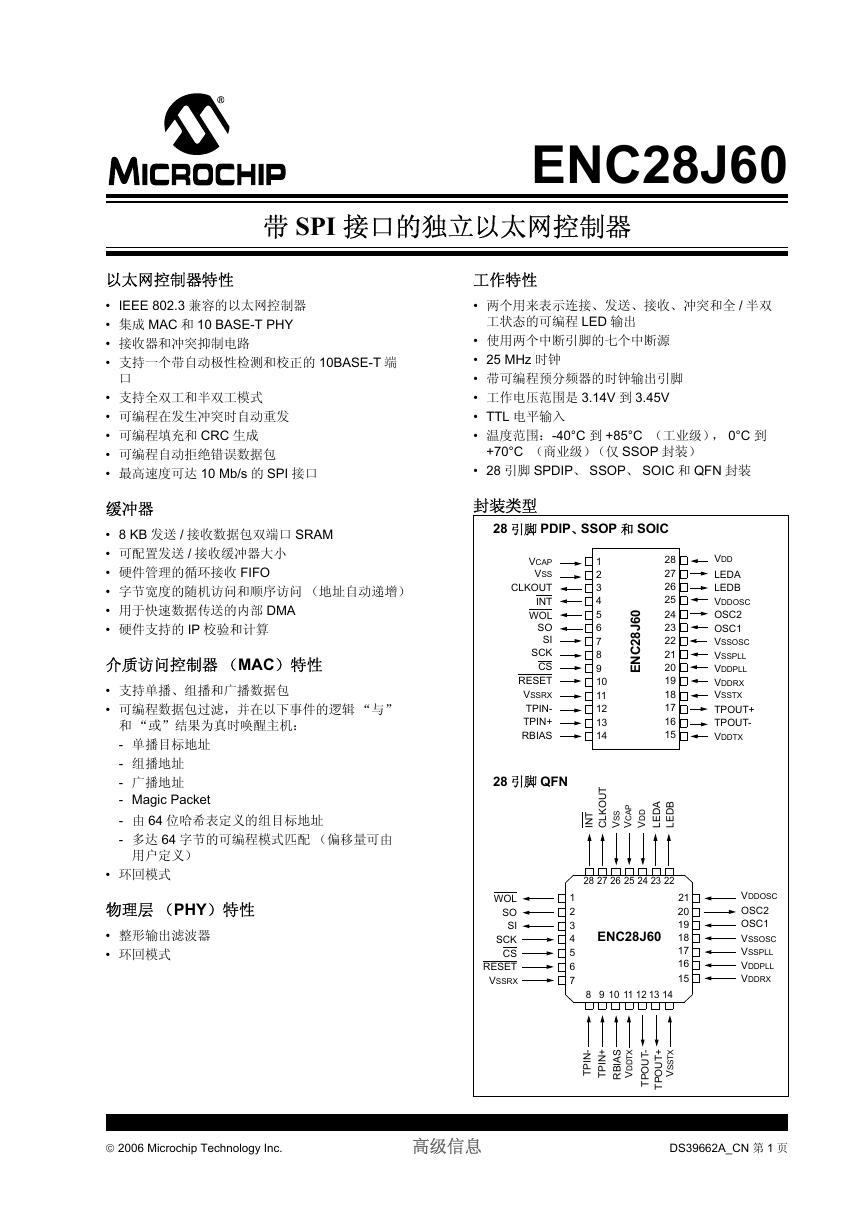

以太网控制器特性

缓冲器

介质访问控制器(MAC)特性

物理层(PHY)特性

工作特性

封装类型

目录

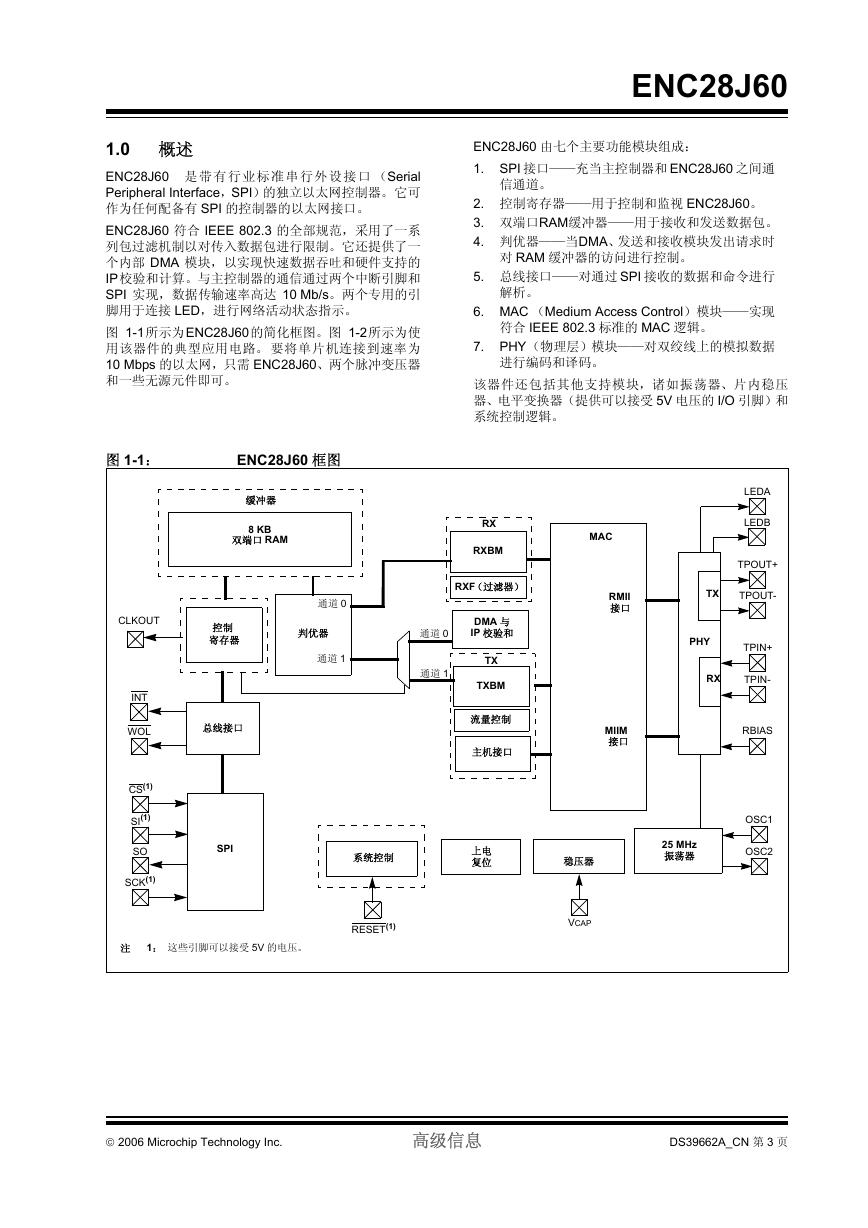

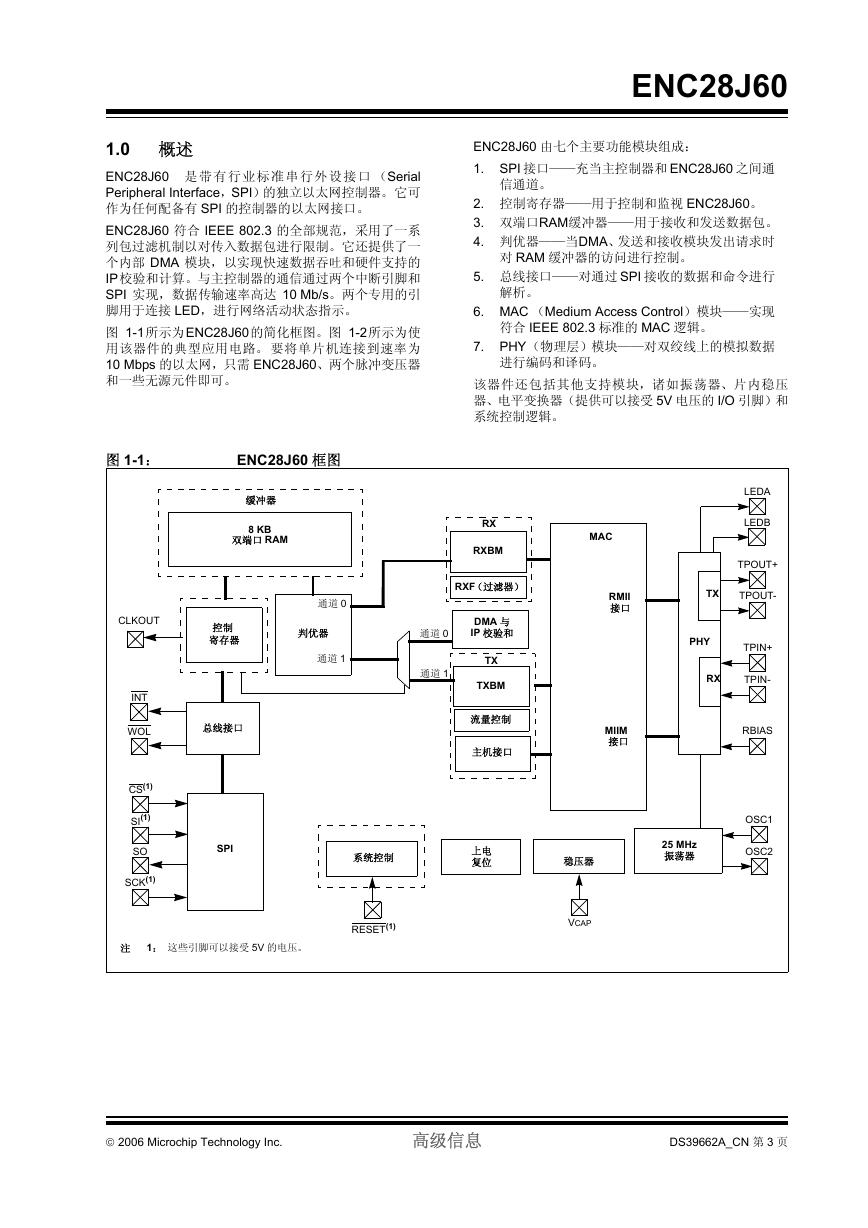

1.0 概述

图1-1: ENC28J60框图

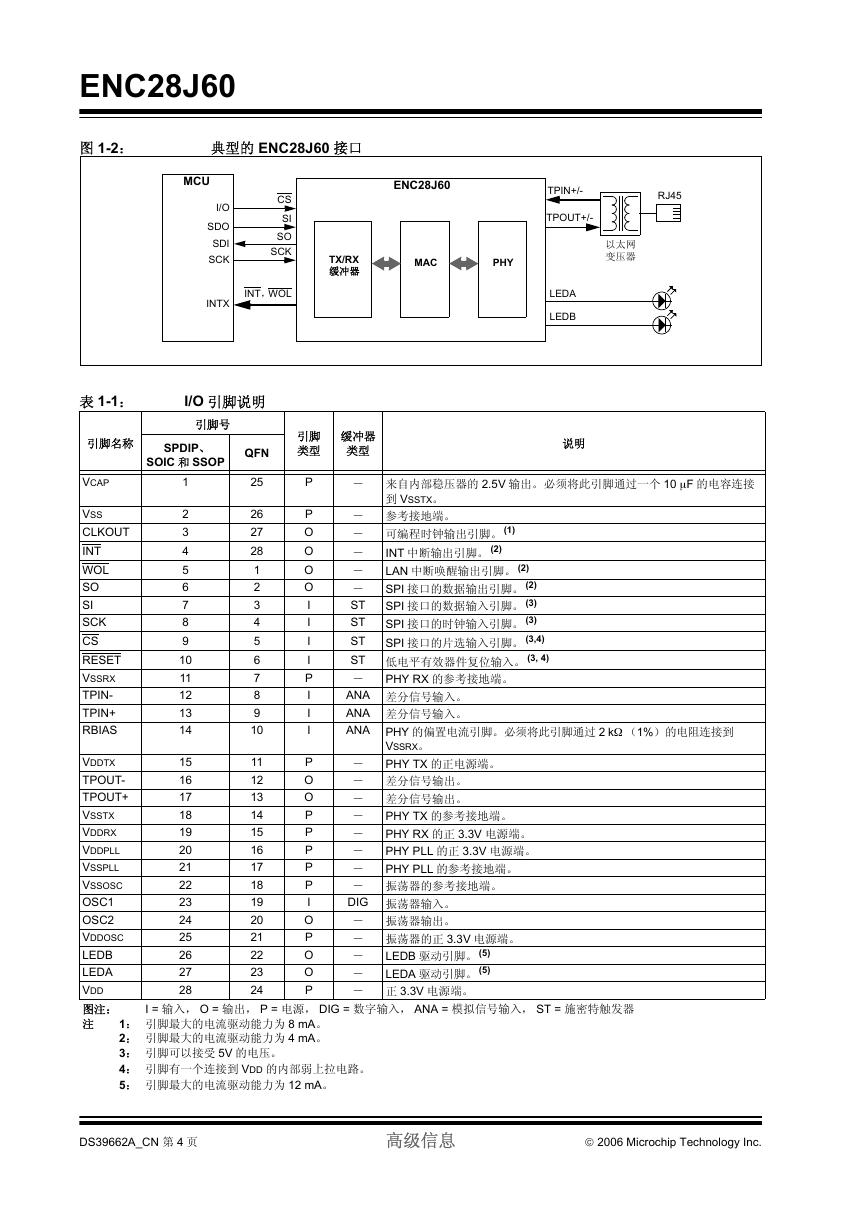

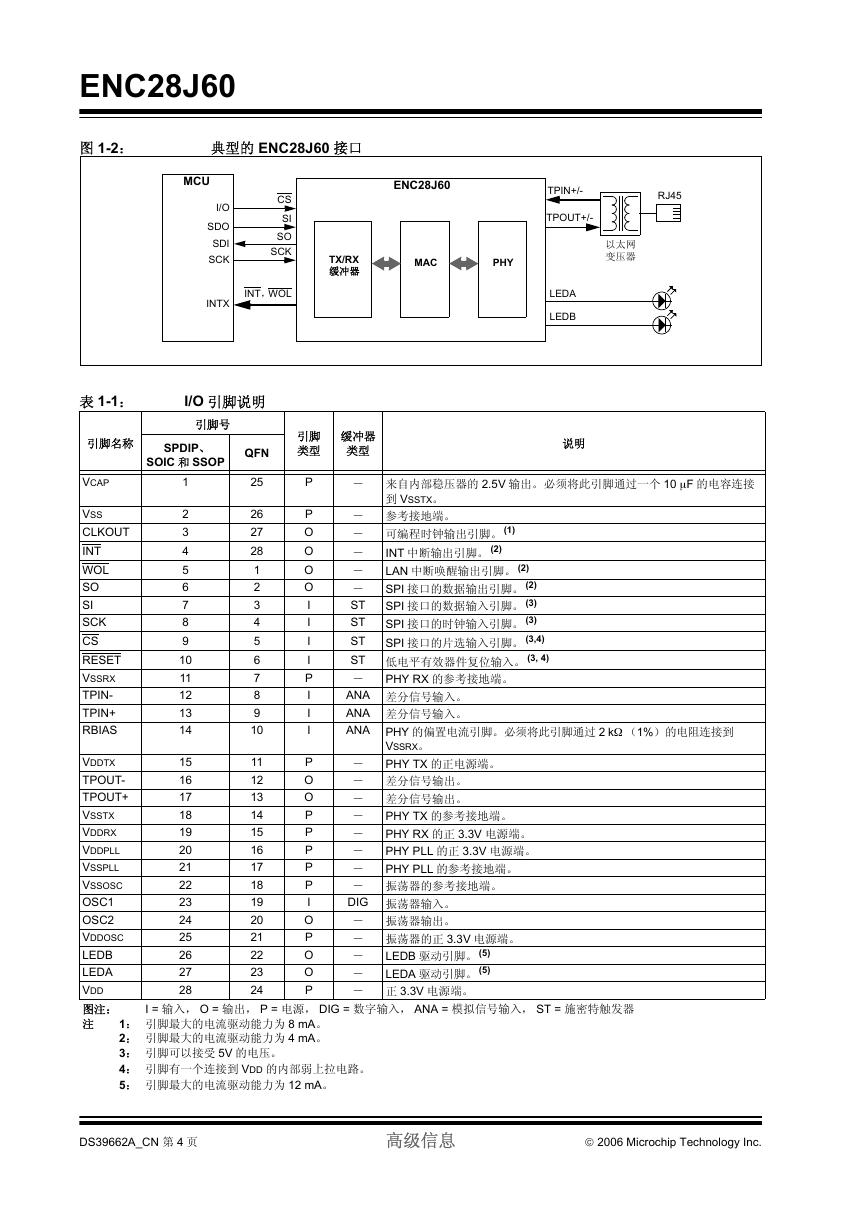

图1-2: 典型的ENC28J60接口

表1-1: I/O引脚说明

2.0 外部连接

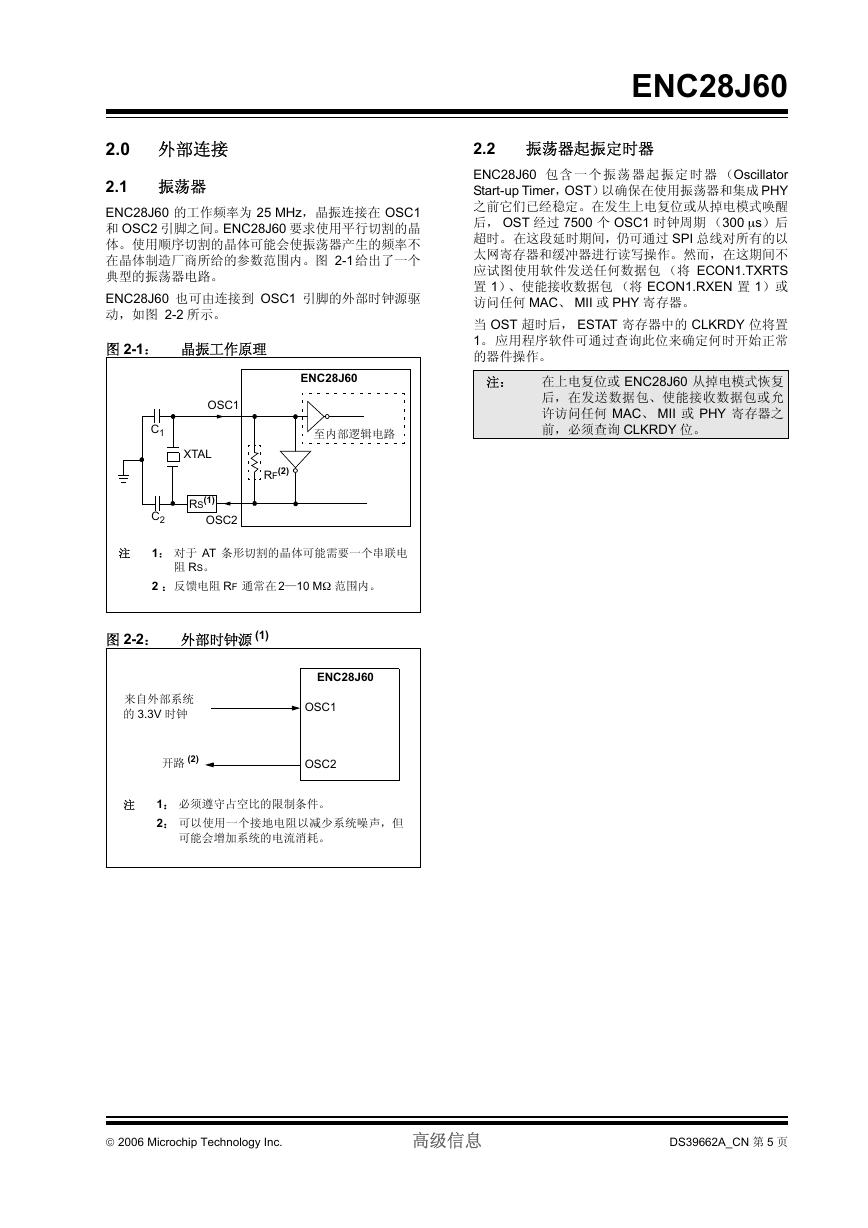

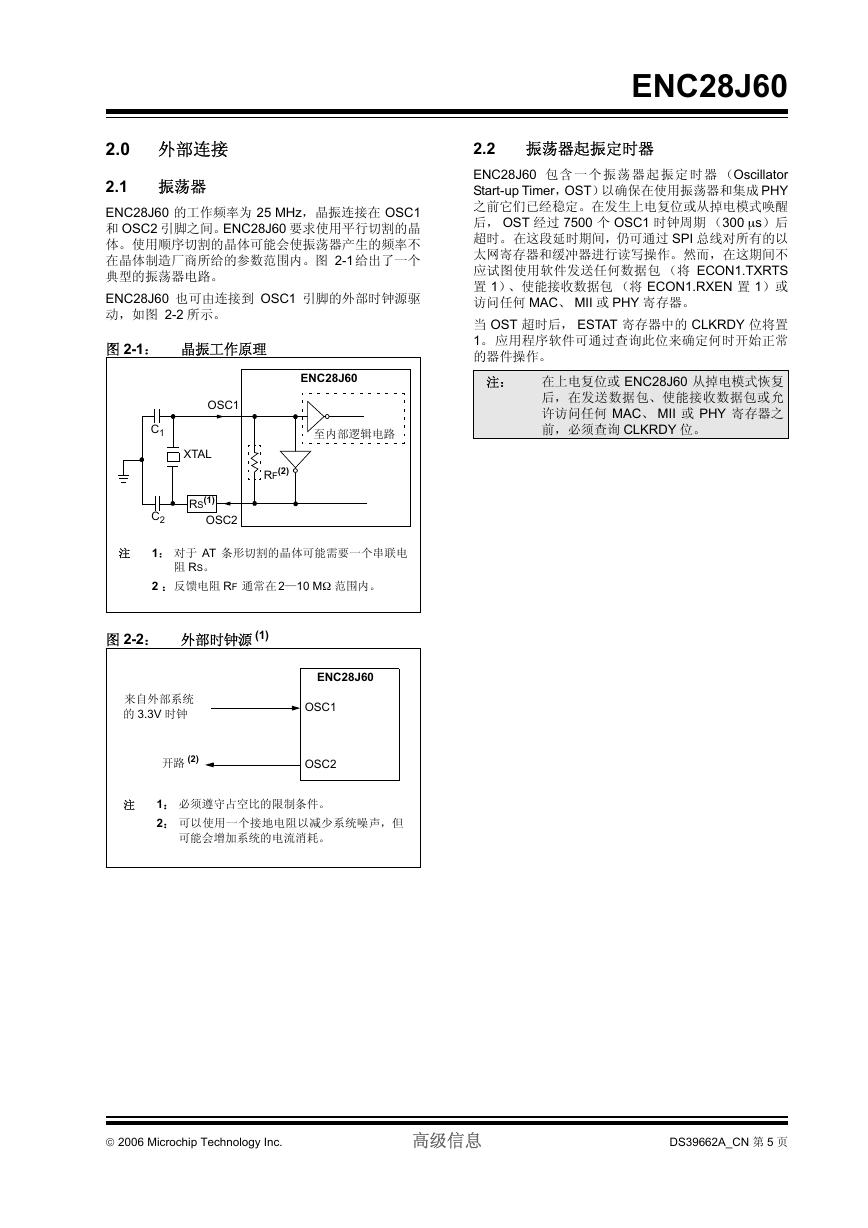

2.1 振荡器

图2-1: 晶振工作原理

图2-2: 外部时钟源

2.2 振荡器起振定时器

2.3 CLKOUT 引脚

图2-3: CLKOUT传输

寄存器 2-1: ECOCON: 时钟输出控制寄存器

2.4 磁性元件,端接元件和其他外部元件

图2-4: 外部连接

2.5 I/O电平

图2-5: 使用与门转换电平

图2-6: 使用三态缓冲器转换电平

2.6 LED配置

图2-7: LEDB 极性和复位配置选项

寄存器 2-2: PHLCON:PHY模块LED控制寄存器

3.0 存储器构成

图3-1: ENC28J60 存储器构成

3.1 控制寄存器

表3-1: ENC28J60控制寄存器映射

表3-2: ENC28J60 控制寄存器汇总 (续)

3.1.1 ECON1寄存器

寄存器3-1: ECON1:以太网控制寄存器1

3.1.2 ECON2寄存器

寄存器3-2: ECON2:以太网控制寄存器2

3.2 以太网缓冲器

3.2.1 接收缓冲器

3.2.2 发送缓冲器

3.2.3 读写缓冲器

3.2.4 DMA访问缓冲器

图3-2: 以太网缓冲器构成

3.3 PHY 寄存器

3.3.1 读PHY寄存器

3.3.2 写PHY寄存器

3.3.3 扫描PHY寄存器

表3-3: ENC28J60 PHY寄存器汇总

寄存器3-3: MICON:MII控制寄存器

寄存器3-4: MICMD:MII命令寄存器

寄存器3-5: MISTAT:MII状态寄存器

3.3.4 PHSTAT寄存器

3.3.5 PHID1和PHID2寄存器

寄存器3-6: PHSTAT1:物理层状态寄存器1

寄存器3-7: PHSTAT2:物理层状态寄存器2

4.0 串行外设接口(SPI)

4.1 概述

图4-1: SPI输入时序

图4-2: SPI输出时序

4.2 SPI指令集

表4-1: ENC28J60的SPI指令集

4.2.1 读控制寄存器的命令

图4-3: 读控制寄存器的命令序列 (ETH寄存器)

图4-4: 读控制寄存器的命令序列(MAC和MII寄存器)

4.2.2 读缓冲存储器命令

4.2.3 写控制寄存器的命令

图4-5: 写控制寄存器的命令序列

4.2.4 写缓冲器命令

4.2.5 位域置1命令

4.2.6 位域清零命令

图4-6: 写缓冲存储器的命令序列

4.2.7 系统命令

图4-7: 系统命令序列

5.0 以太网概述

5.1 数据包格式

5.1.1 前导字段/帧起始定界符

图5-1: 以太网数据包格式

5.1.2 目标地址

5.1.3 源地址

5.1.4 类型/长度

5.1.5 数据

5.1.6 填充

5.1.7 CRC

6.0 初始化

6.1 接收缓冲器

6.2 发送缓冲器

6.3 接收过滤器

6.4 等待OST

6.5 MAC 初始化设置

寄存器6-1: MACON1:MAC控制寄存器1

寄存器6-2: MACON3:MAC控制寄存器3

寄存器6-3: MACON4:MAC控制寄存器4

寄存器6-4: MABBIPG:MAC背对背包间间隔寄存器

6.6 PHY初始化设置

寄存器6-5: PHCON2:PHY控制寄存器2

7.0 发送和接收数据包

7.1 发送数据包

图7-1: 包控制字节格式

图7-2: 发送数据包结构示例

表7-1: 发送状态向量

表7-2: 与数据包发送相关的寄存器汇总

7.2 接收数据包

7.2.1 使能接收

7.2.2 接收数据包结构

图7-3: 接收数据包结构示例

表7-3: 接收状态向量

7.2.3 读接收的数据包

例7-1: 随机访问地址计算

7.2.4 释放接收缓冲空间

7.2.5 接收缓冲器剩余空间

例7-2: 接收缓冲器空余空间计算方法

表7-4: 数据包接收所使用的寄存器汇总

8.0 接收过滤器

寄存器8-1: ERXFCON:接收过滤器控制寄存器

图8-1: 使用逻辑或的过滤流程

图8-2: 使用逻辑与的过滤流程

8.1 单播过滤器

8.2 格式匹配过滤器

图8-3: 格式匹配示例

8.3 Magic Packet过滤器

图8-4: Magic Packet示例

8.4 哈希表过滤器

8.5 组播过滤器

8.6 广播过滤器

9.0 双工模式配置和协商

9.1 半双工工作方式

9.2 全双工工作方式

10.0 流量控制

10.1 半双工模式

10.2 全双工模式

图10-1: 全双工网络示例

寄存器10-1: EFLOCON:以太网流量控制寄存器

表10-1: 流量控制使用的寄存器汇总

11.0 复位

图11-1: 片上复位电路

11.1 上电复位(POR)

11.2 系统复位

11.3 仅发送复位

11.4 仅接收复位

11.5 MAC和PHY子系统复位

寄存器 11-1: MACON2: MAC控制寄存器2

寄存器 11-2: MAPHSUP: MAC-PHY支持寄存器

寄存器 11-3: PHCON1: PHY控制寄存器1

12.0 中断

图12-1: ENC28J60 中断逻辑

12.1 INT中断允许位(INTIE)

12.1.1 INT中断寄存器

寄存器 12-1: ESTAT: 以太网状态寄存器

寄存器 12-2: EIE: 以太网中断允许寄存器

寄存器 12-3: EIR: 以太网中断请求(标志)寄存器

寄存器 12-4: PHIE: PHY中断允许寄存器

寄存器 12-5: PHIR: PHY中断请求(标志)寄存器

12.1.2 接收错误中断标志位(RXERIF)

12.1.3 发送错误中断标志位(TXERIF)

12.1.4 发送中断标志位(TXIF)

12.1.5 连接状态改变中断标志位(LINKIF)

12.1.6 DMA中断标志位 (DMAIF)

12.1.7 接收数据包待处理中断标志位 (PKTIF)

12.2 LAN唤醒中断(WOLIE/WOLIF)

12.2.1 WOL中断寄存器

寄存器 12-6: EWOLIE: 以太网LAN唤醒中断允许寄存器

寄存器 12-7: EWOLIR: 以太网LAN唤醒中断请求(标志) 寄存器

13.0 直接存储器访问控制器

13.1 复制内存

13.2 校验和计算

表13-1: 与DMA控制器相关的寄存器汇总

14.0 掉电

表14-1: 掉电使用的寄存器汇总

15.0 内置自测试控制器

寄存器15-1: EBSTCON:自测试控制寄存器

15.1 使用BIST

15.2 随机数据填充模式

15.3 带竞争的随机数据填充模式

15.4 地址填充模式

15.5 模式移位填充模式

表15-1: 与自测试控制器相关的寄存器汇总

16.0 电气特性

绝对额定最大值

16.1 直流特性:ENC28J60(工业级和商业级)

表16-1: 交流特性:ENC28J60(工业级和商业级)

表16-2: 振荡器时序规范

表16-3: 复位交流特性

表16-4: CLKOUT 引脚交流特性

表16-5: 外部电磁要求

表16-6: SPI接口交流特性

图16-1: SPI输入时序

图16-2: SPI输出时序

17.0 封装信息

17.1 封装标识信息

17.2 封装详细信息

28引脚窄条塑封双列直插式封装(SP)――主体300mil(PDIP)

28引脚宽条塑封小外形封装(SO)――主体300mil(SOIC)

28引脚塑封缩小外形封装(SS)――主体209mil,5.30mm(SSOP)

28引脚塑封正方扁平无脚封装(ML)主体6x6 mm(QFN)――触点长度为0.55毫米 (Saw Singulated)

索引

Microchip网站

变更通知客户服务

客户支持

读者反馈表

产品标识体系

全球销售及服务网点

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf