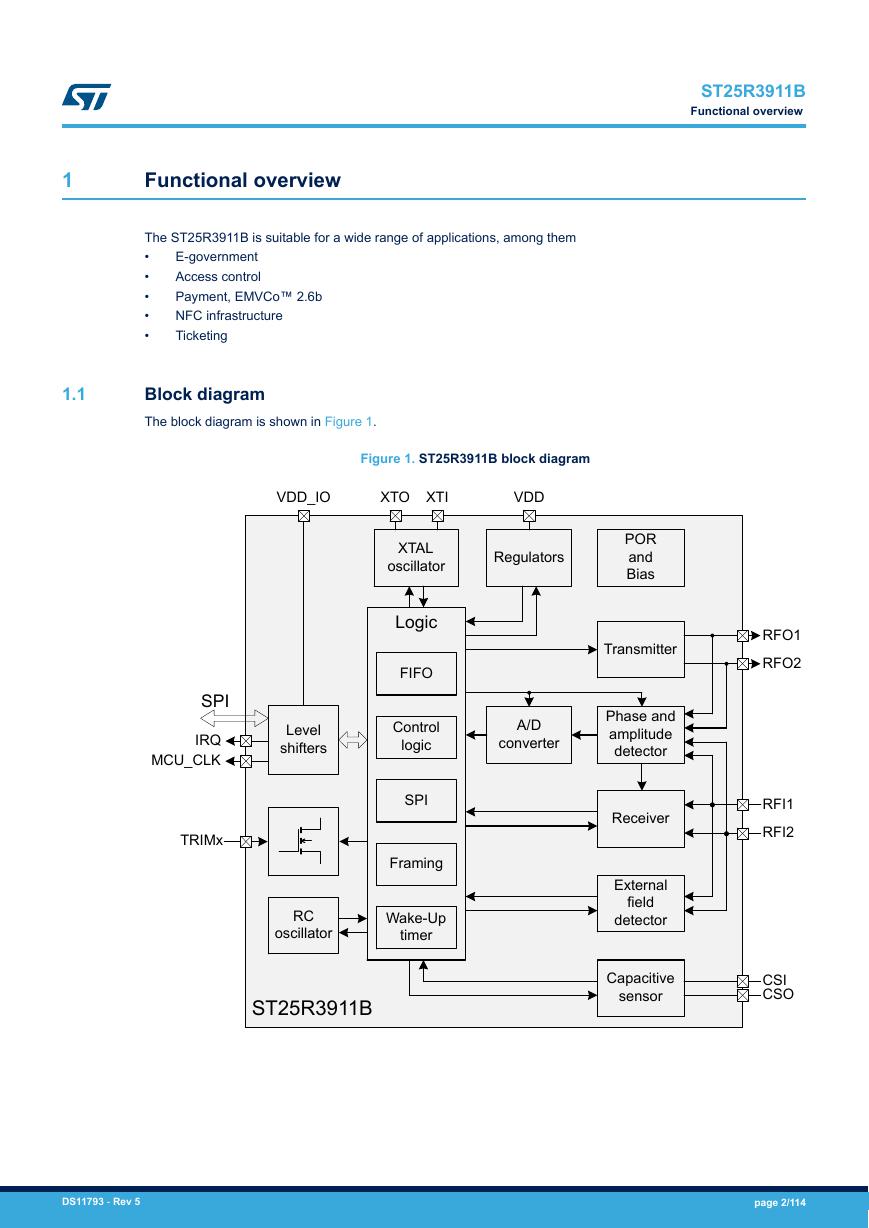

1 Functional overview

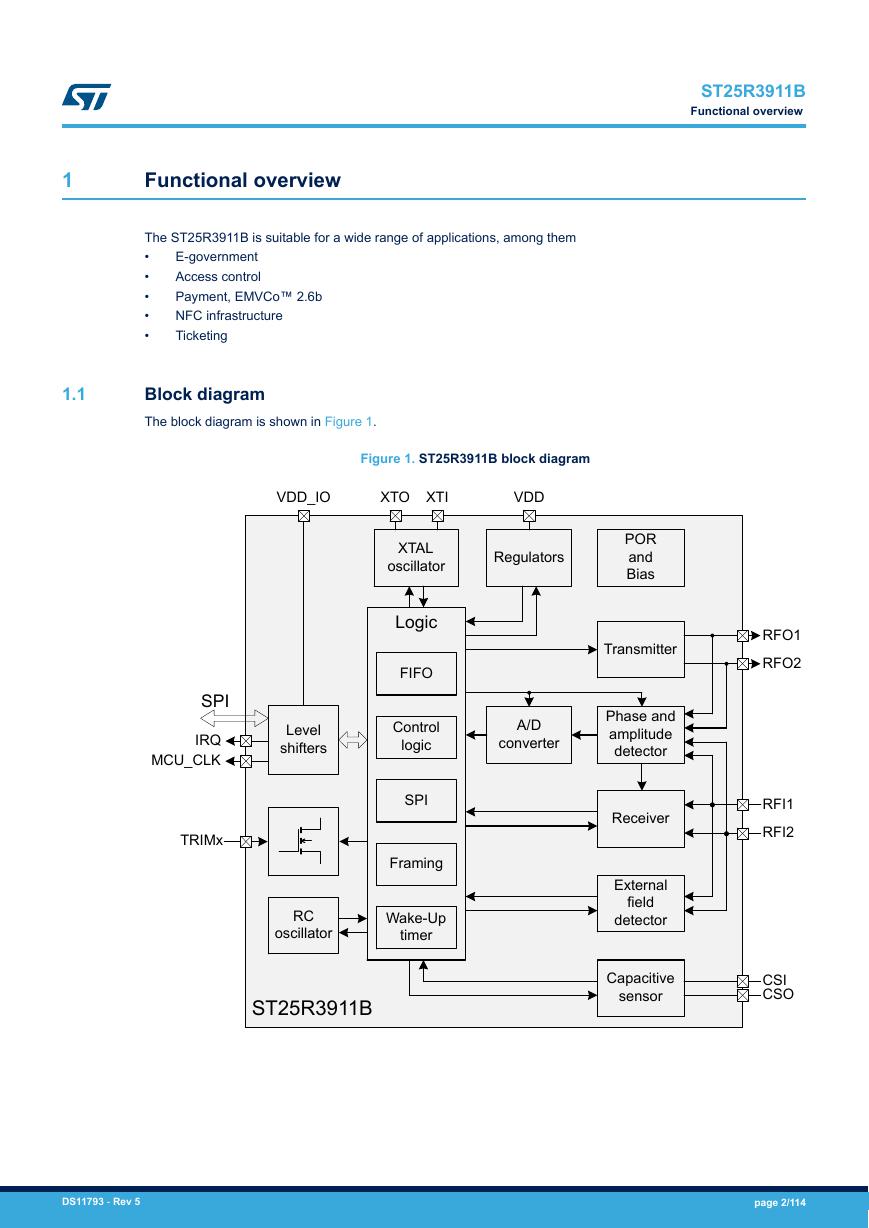

1.1 Block diagram

1.1.1 Transmitter

1.1.2 Receiver

1.1.3 Phase and amplitude detector

1.1.4 A/D converter

1.1.5 Capacitive sensor

1.1.6 External field detector

1.1.7 Quartz crystal oscillator

1.1.8 Power supply regulators

1.1.9 POR and Bias

1.1.10 RC oscillator and Wake-Up timer

1.1.11 ISO-14443 and NFCIP-1 framing

1.1.12 FIFO

1.1.13 Control logic

1.1.14 SPI

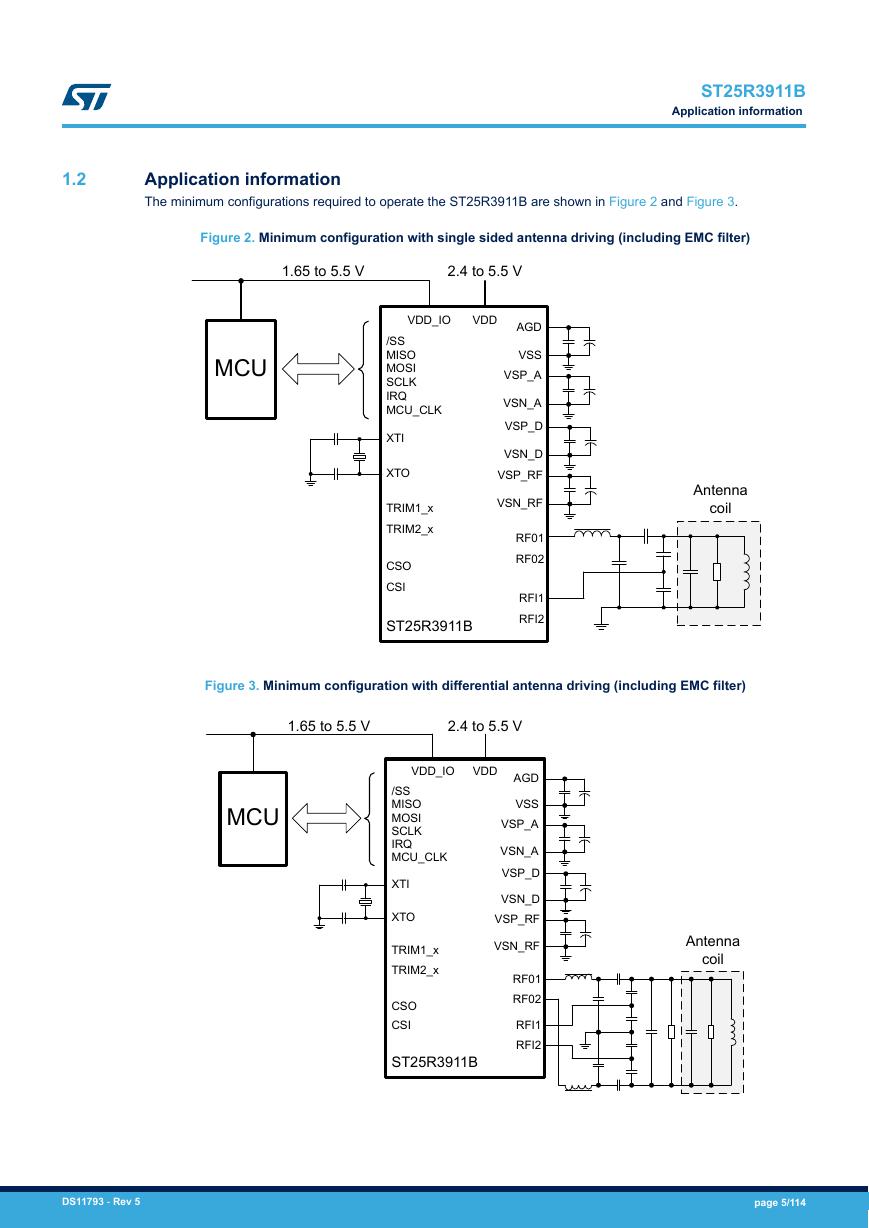

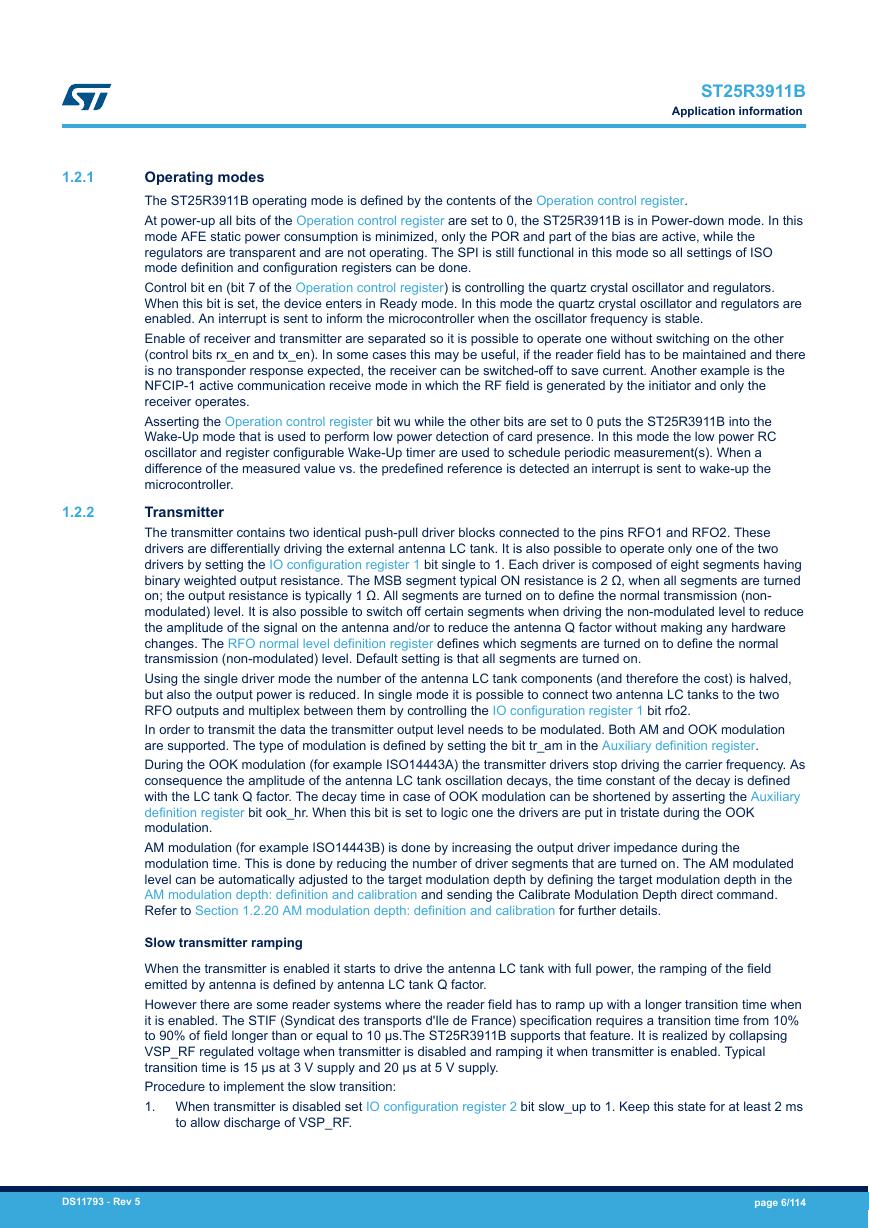

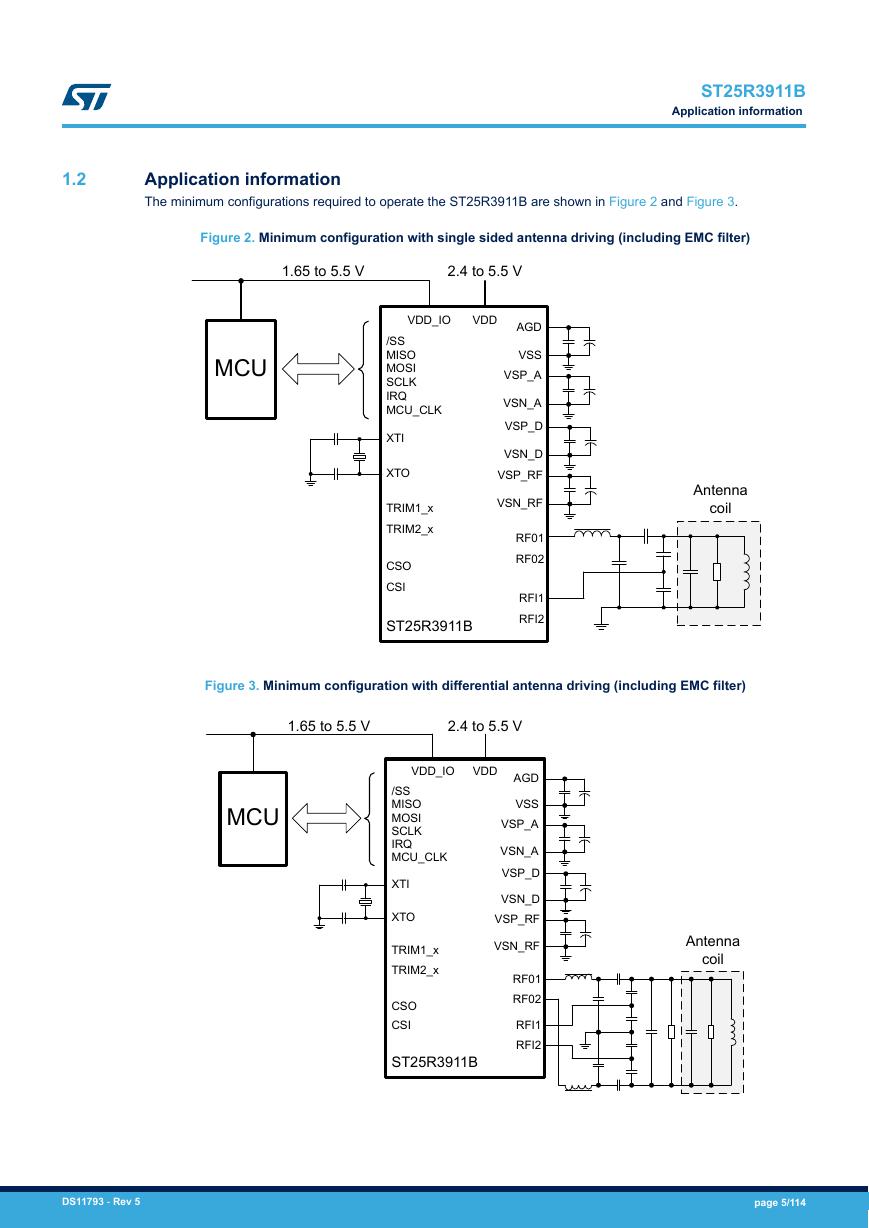

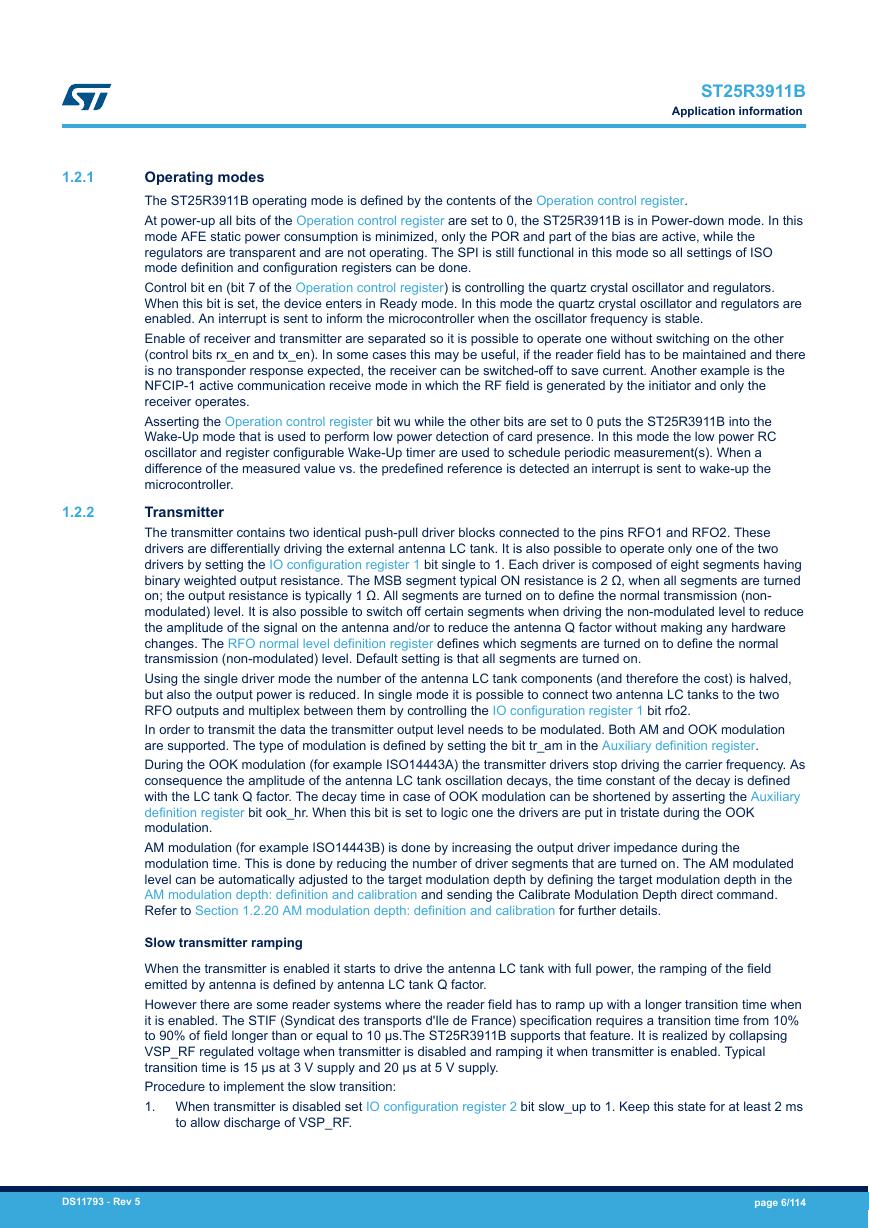

1.2 Application information

1.2.1 Operating modes

1.2.2 Transmitter

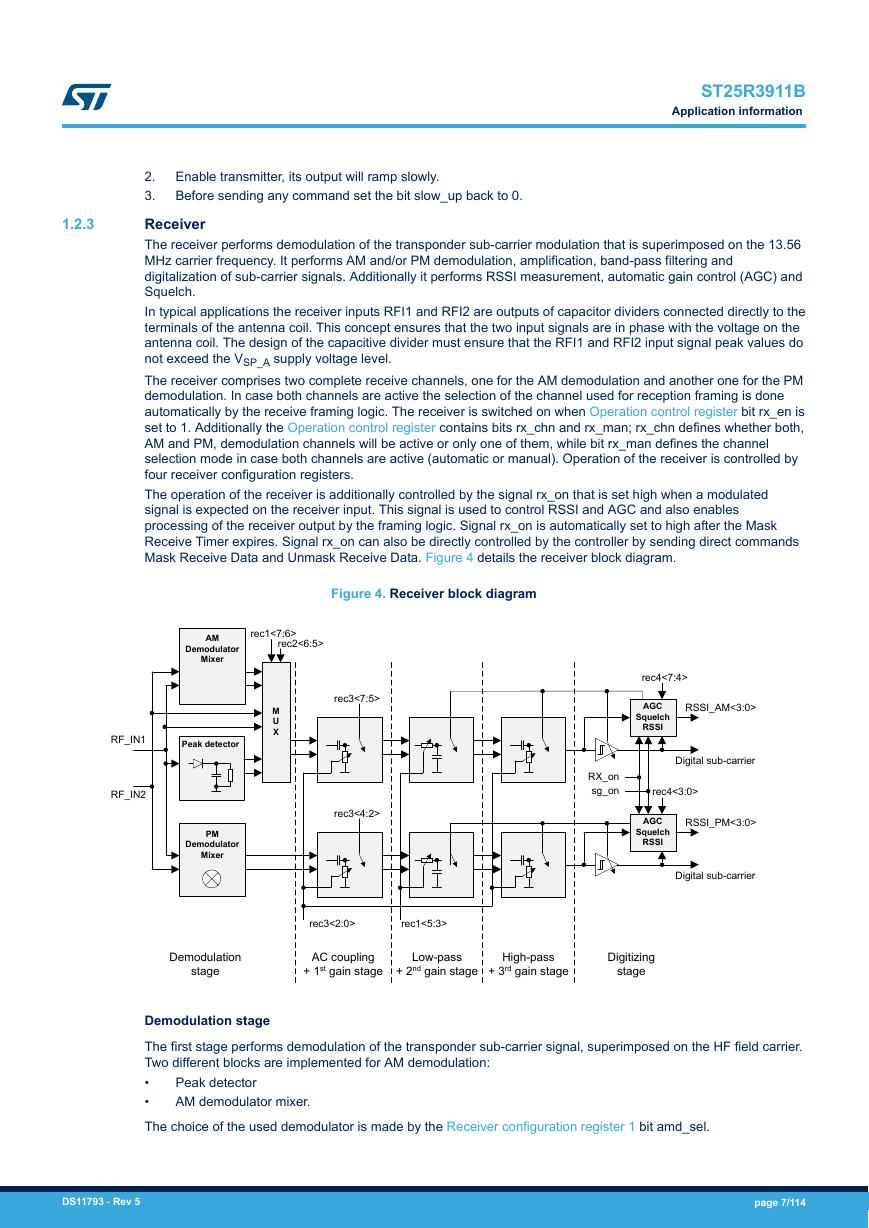

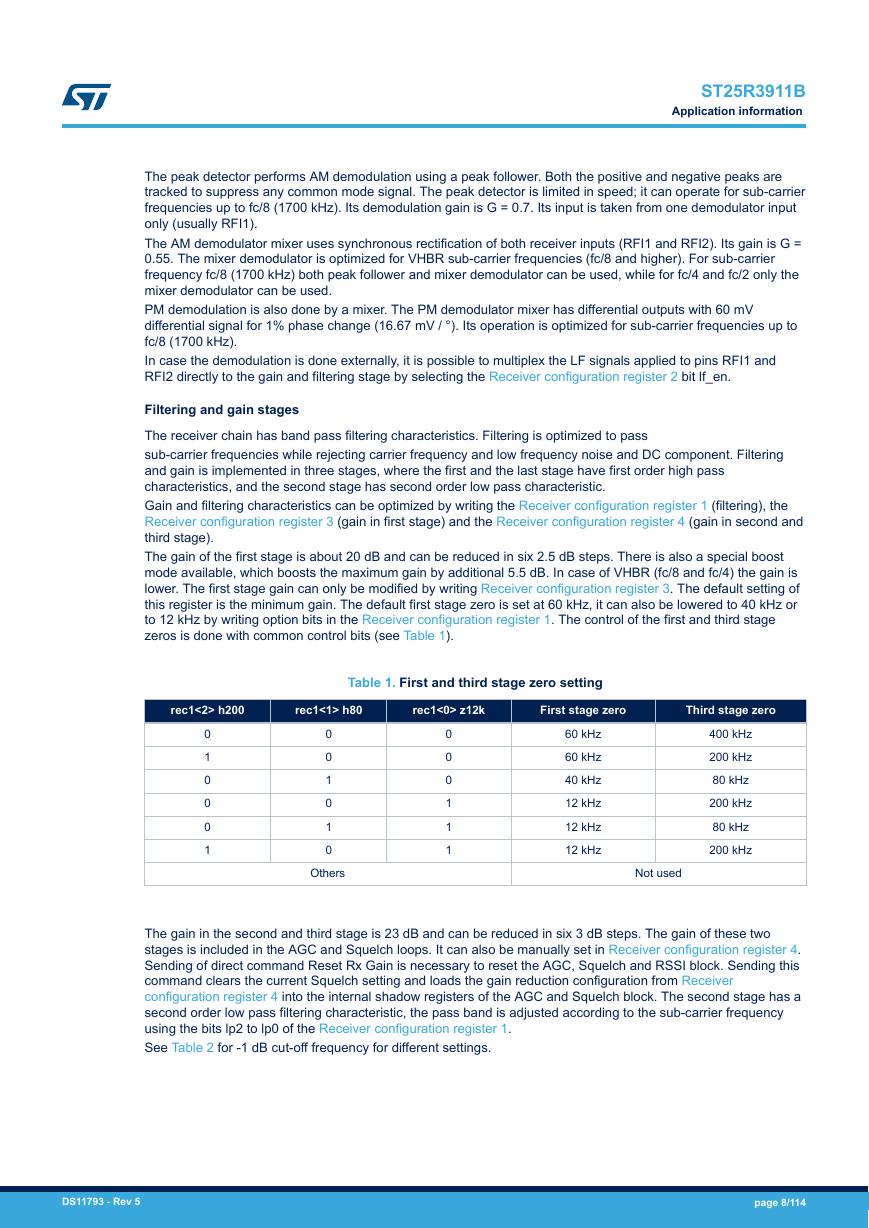

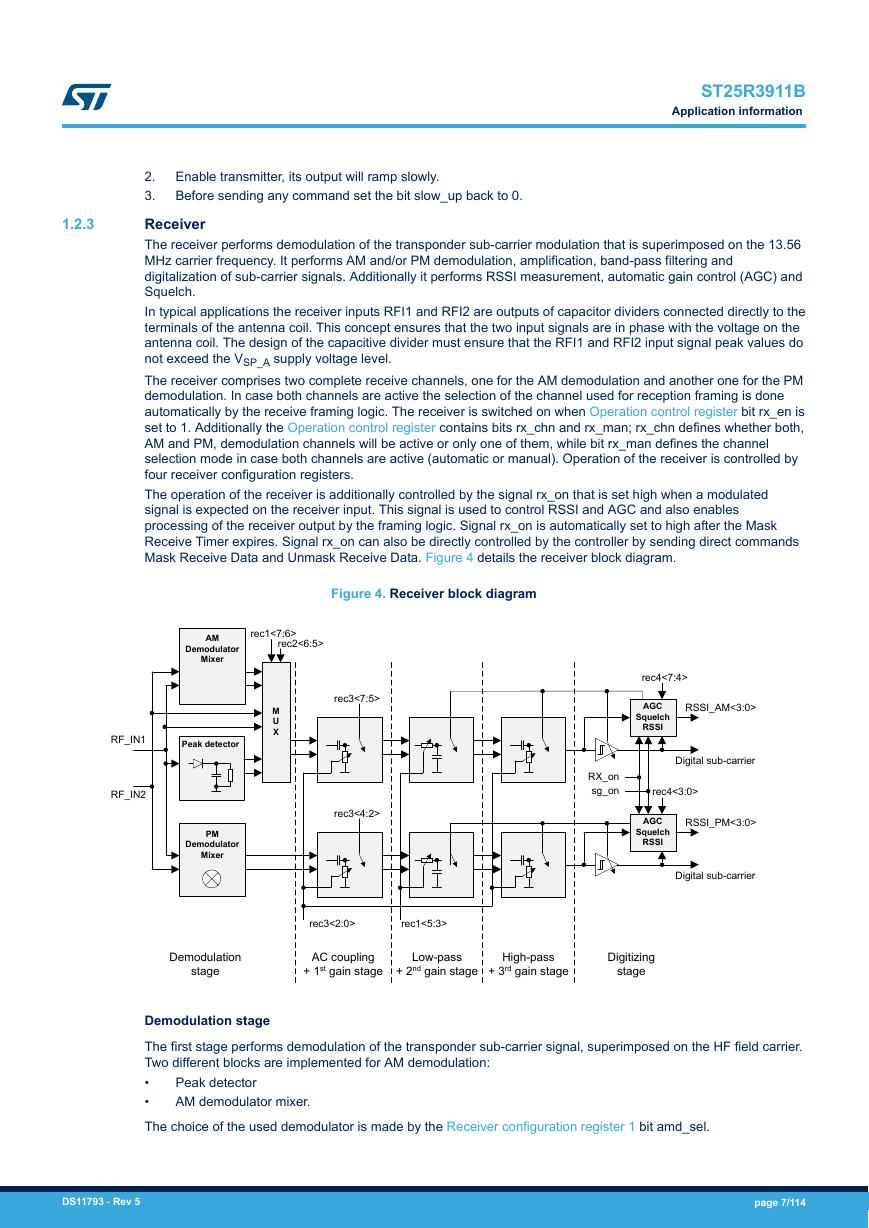

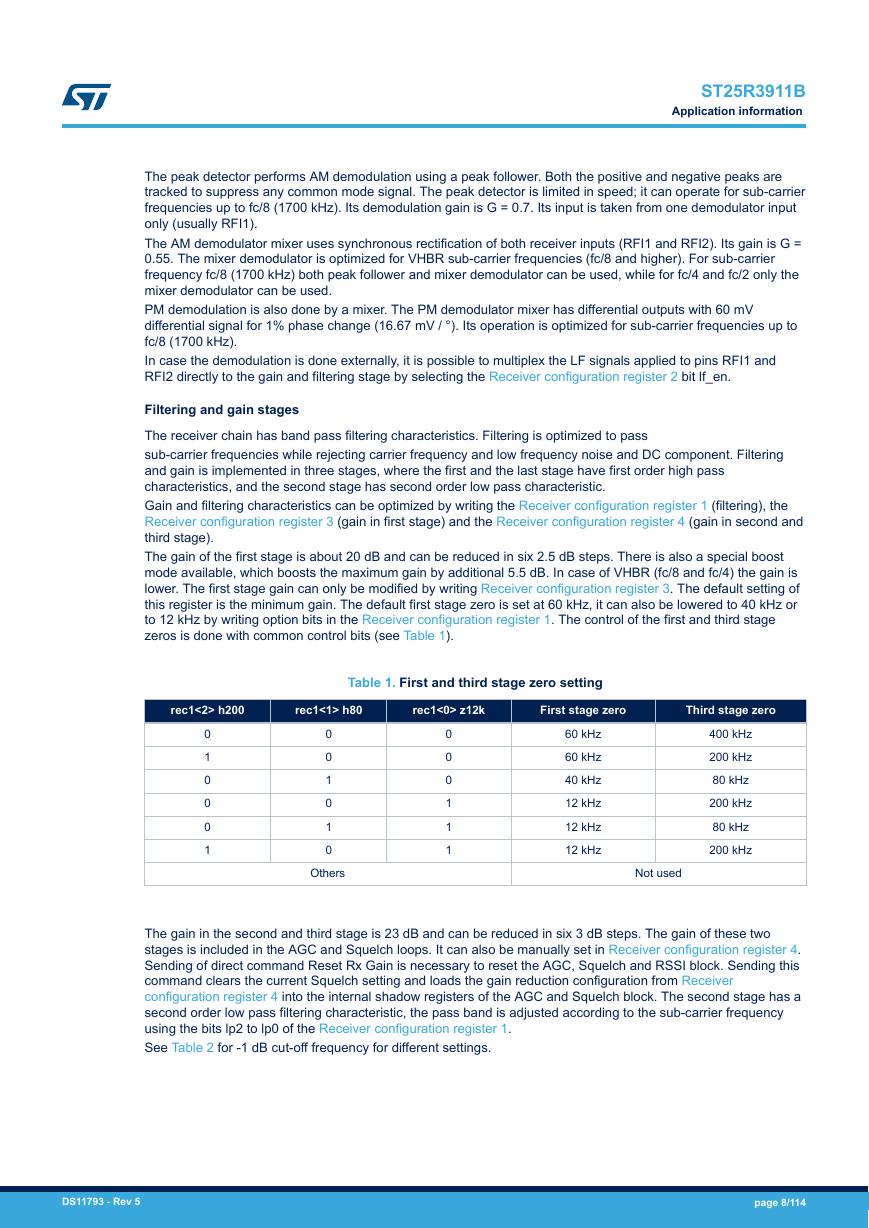

1.2.3 Receiver

1.2.4 Capacitive sensor

1.2.5 Wake-up mode

1.2.6 Quartz crystal oscillator

1.2.7 Timers

1.2.8 A/D converter

1.2.9 Phase and amplitude detector

1.2.10 External field detector

1.2.11 Power supply system

1.2.12 Communication with an external microcontroller

1.2.13 Direct commands

1.2.14 Start timers

1.2.15 Test access

1.2.16 Power-up sequence

1.2.17 Reader operation

1.2.18 FeliCa™ reader mode

1.2.19 NFCIP-1 operation

1.2.20 AM modulation depth: definition and calibration

1.2.21 Antenna tuning

1.2.22 Stream mode and transparent mode

1.3 Registers

1.3.1 IO configuration register 1

1.3.2 IO configuration register 2

1.3.3 Operation control register

1.3.4 Mode definition register

1.3.5 Bit rate definition register

1.3.6 ISO14443A and NFC 106kb/s settings register

1.3.7 ISO14443B settings register 1

1.3.8 ISO14443B and FeliCa settings register

1.3.9 Stream mode definition register

1.3.10 Auxiliary definition register

1.3.11 Receiver configuration register 1

1.3.12 Receiver configuration register 2

1.3.13 Receiver configuration register 3

1.3.14 Receiver configuration register 4

1.3.15 Mask receive timer register

1.3.16 No-response timer register 1

1.3.17 No-response timer register 2

1.3.18 General purpose and no-response timer control register

1.3.19 General purpose timer register 1

1.3.20 General purpose timer register 2

1.3.21 Mask main interrupt register

1.3.22 Mask timer and NFC interrupt register

1.3.23 Mask error and wake-up interrupt register

1.3.24 Main interrupt register

1.3.25 Timer and NFC interrupt register

1.3.26 Error and wake-up interrupt register

1.3.27 FIFO status register 1

1.3.28 FIFO status register 2

1.3.29 Collision display register

1.3.30 Number of transmitted bytes register 1

1.3.31 Number of transmitted bytes register 2

1.3.32 NFCIP bit rate detection display register

1.3.33 A/D converter output register

1.3.34 Antenna calibration control register

1.3.35 Antenna calibration target register

1.3.36 Antenna calibration display register

1.3.37 AM modulation depth control register

1.3.38 AM modulation depth display register

1.3.39 RFO AM modulated level definition register

1.3.40 RFO normal level definition register

1.3.41 External field detector threshold register

1.3.42 Regulator voltage control register

1.3.43 Regulator and timer display register

1.3.44 RSSI display register

1.3.45 Gain reduction state register

1.3.46 Capacitive sensor control register

1.3.47 Capacitive sensor display register

1.3.48 Auxiliary display register

1.3.49 Wake-up timer control register

1.3.50 Amplitude measurement configuration register

1.3.51 Amplitude measurement reference register

1.3.52 Amplitude measurement auto-averaging display register

1.3.53 Amplitude measurement display register

1.3.54 Phase measurement configuration register

1.3.55 Phase measurement reference register

1.3.56 Phase measurement auto-averaging display register

1.3.57 Phase measurement display register

1.3.58 Capacitance measurement configuration register

1.3.59 Capacitance measurement reference register

1.3.60 Capacitance measurement auto-averaging display register

1.3.61 Capacitance measurement display register

1.3.62 IC identity register

2 Pinouts and pin description

3 Electrical characteristics

3.1 Absolute maximum ratings

3.2 Operating conditions

3.3 DC/AC characteristics for digital inputs and outputs

3.3.1 CMOS inputs

3.3.2 CMOS outputs

3.4 Electrical specifications

3.5 Typical operating characteristics

3.5.1 Thermal resistance and maximum power dissipation

4 Package information

4.1 QFN32 package information

5 Ordering information

Revision history

Contents

List of tables

List of figures

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf