w

Stereo CODEC with 1W Stereo Class D Speaker Drivers and

Headphone Drivers for Portable Audio Applications

WM8960

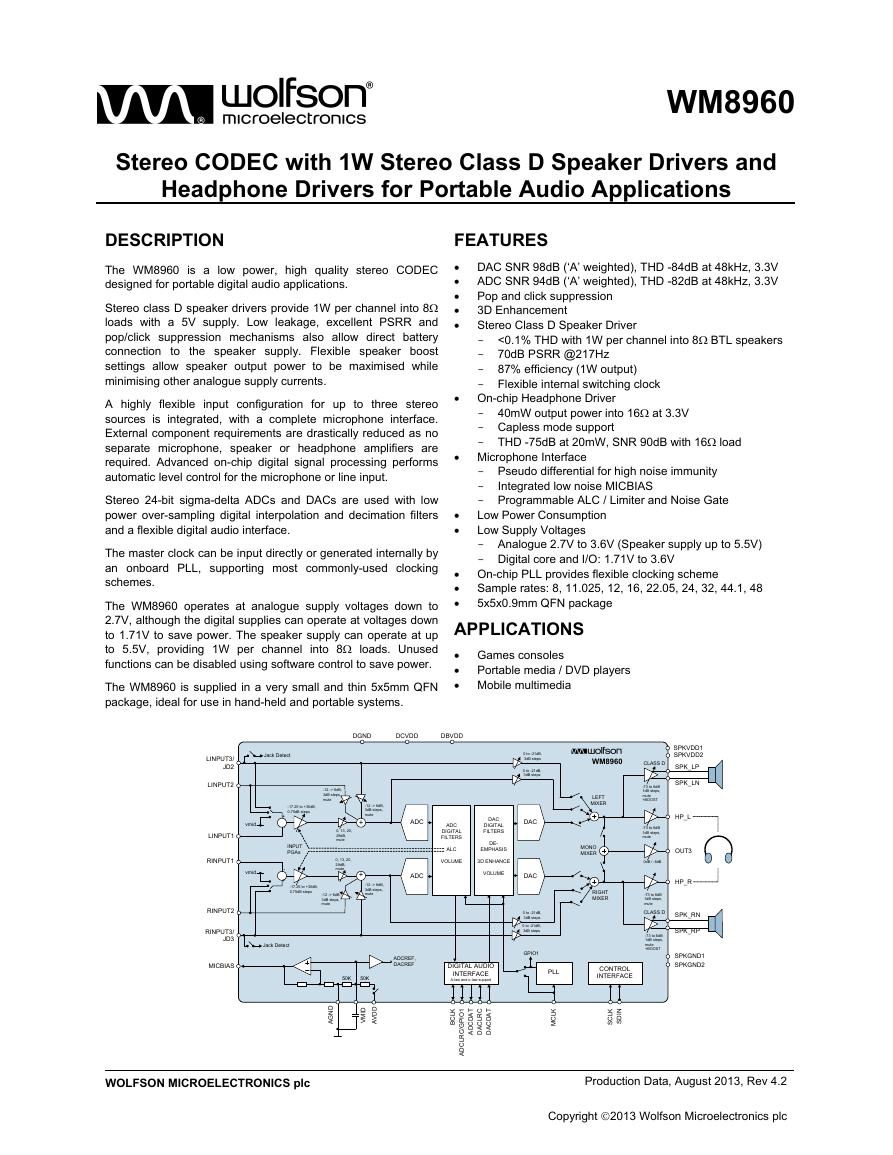

DESCRIPTION

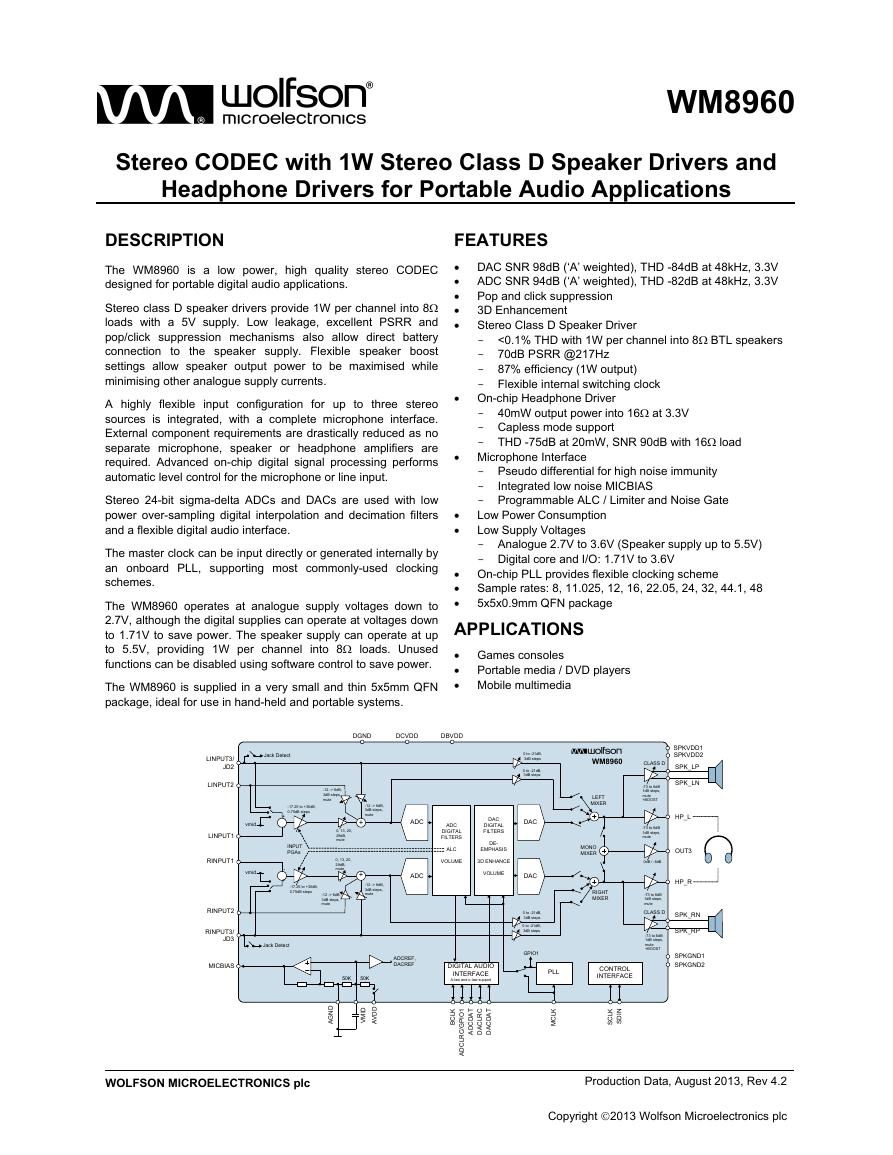

The WM8960 is a low power, high quality stereo CODEC

designed for portable digital audio applications.

Stereo class D speaker drivers provide 1W per channel into 8

loads with a 5V supply. Low leakage, excellent PSRR and

pop/click suppression mechanisms also allow direct battery

connection to the speaker supply. Flexible speaker boost

settings allow speaker output power to be maximised while

minimising other analogue supply currents.

A highly flexible input configuration for up to three stereo

sources is integrated, with a complete microphone interface.

External component requirements are drastically reduced as no

separate microphone, speaker or headphone amplifiers are

required. Advanced on-chip digital signal processing performs

automatic level control for the microphone or line input.

Stereo 24-bit sigma-delta ADCs and DACs are used with low

power over-sampling digital interpolation and decimation filters

and a flexible digital audio interface.

The master clock can be input directly or generated internally by

an onboard PLL, supporting most commonly-used clocking

schemes.

The WM8960 operates at analogue supply voltages down to

2.7V, although the digital supplies can operate at voltages down

to 1.71V to save power. The speaker supply can operate at up

to 5.5V, providing 1W per channel into 8 loads. Unused

functions can be disabled using software control to save power.

The WM8960 is supplied in a very small and thin 5x5mm QFN

package, ideal for use in hand-held and portable systems.

FEATURES

DAC SNR 98dB (‘A’ weighted), THD -84dB at 48kHz, 3.3V

ADC SNR 94dB (‘A’ weighted), THD -82dB at 48kHz, 3.3V

Pop and click suppression

Stereo Class D Speaker Driver

3D Enhancement

On-chip Headphone Driver

- <0.1% THD with 1W per channel into 8 BTL speakers

- 70dB PSRR @217Hz

- 87% efficiency (1W output)

- Flexible internal switching clock

- 40mW output power into 16 at 3.3V

- Capless mode support

- THD -75dB at 20mW, SNR 90dB with 16 load

- Pseudo differential for high noise immunity

-

- Programmable ALC / Limiter and Noise Gate

Low Power Consumption

Low Supply Voltages

- Analogue 2.7V to 3.6V (Speaker supply up to 5.5V)

- Digital core and I/O: 1.71V to 3.6V

Integrated low noise MICBIAS

Microphone Interface

5x5x0.9mm QFN package

On-chip PLL provides flexible clocking scheme

Sample rates: 8, 11.025, 12, 16, 22.05, 24, 32, 44.1, 48

APPLICATIONS

Games consoles

Portable media / DVD players

Mobile multimedia

LINPUT3/

JD2

LINPUT2

LINPUT1

RINPUT1

vmid

vmid

RINPUT2

RINPUT3/

JD3

MICBIAS

DGND

DCVDD

DBVDD

Jack Detect

SPKVDD1

SPKVDD2W

SPK_LP

WM8960

CLASS D

0 to -21dB,

3dB steps

0 to -21dB,

3dB steps

DAC

-12 -> 6dB,

3dB steps,

mute

-17.25 to +30dB,

0.75dB steps

INPUT

PGAs

0, 13, 20,

29dB,

mute

0, 13, 20,

29dB,

mute

+

+

+

-

-

+

-17.25 to +30dB,

0.75dB steps

-12 -> 6dB,

3dB steps,

mute

-12 -> 6dB,

3dB steps,

mute

-12 -> 6dB,

3dB steps,

mute

ADC

ADC

DIGITAL

FILTERS

ALC

DAC

DIGITAL

FILTERS

DE-

EMPHASIS

VOLUME

3D ENHANCE

ADC

VOLUME

DAC

LEFT

MIXER

MONO

MIXER

RIGHT

MIXER

Jack Detect

ADCREF,

DACREF

50K

50K

DIGITAL AUDIO

INTERFACE

A-law and u-law support

D

N

G

A

I

D

M

V

D

D

V

A

K

L

C

B

T

A

D

C

D

A

C

R

L

C

A

D

T

A

D

C

A

D

I

/

1

O

P

G

C

R

L

C

D

A

0 to -21dB,

3dB steps

0 to -21dB,

3dB steps

GPIO1

PLL

K

L

C

M

CONTROL

INTERFACE

K

L

C

S

I

N

D

S

-73 to 6dB

1dB steps,

mute

+BOOST

-73 to 6dB

1dB steps,

mute

0dB / -6dB

-73 to 6dB

1dB steps,

mute

CLASS D

-73 to 6dB

1dB steps,

mute

+BOOST

SPK_LN

HP_L

OUT3

HP_R

SPK_RN

SPK_RP

SPKGND1

SPKGND2

WOLFSON MICROELECTRONICS plc

Production Data, August 2013, Rev 4.2

Copyright 2013 Wolfson Microelectronics plc

�

WM8960

Production Data

TABLE OF CONTENTS

DESCRIPTION ....................................................................................................... 1

FEATURES ............................................................................................................ 1

APPLICATIONS ..................................................................................................... 1

TABLE OF CONTENTS ......................................................................................... 2

PIN CONFIGURATION .......................................................................................... 3

ORDERING INFORMATION .................................................................................. 3

PIN DESCRIPTION ................................................................................................ 4

ABSOLUTE MAXIMUM RATINGS ........................................................................ 5

RECOMMENDED OPERATING CONDITIONS ..................................................... 5

ELECTRICAL CHARACTERISTICS ..................................................................... 6

OUTPUT PGA GAIN ............................................................................................ 10

TYPICAL POWER CONSUMPTION .................................................................... 11

SIGNAL TIMING REQUIREMENTS .................................................................... 13

SYSTEM CLOCK TIMING .............................................................................................. 13

AUDIO INTERFACE TIMING – MASTER MODE .......................................................... 13

AUDIO INTERFACE TIMING – SLAVE MODE .............................................................. 14

CONTROL INTERFACE TIMING – 2-WIRE MODE ....................................................... 15

INTERNAL POWER ON RESET CIRCUIT .......................................................... 16

DEVICE DESCRIPTION ...................................................................................... 18

INTRODUCTION ............................................................................................................ 18

INPUT SIGNAL PATH .................................................................................................... 19

ANALOGUE TO DIGITAL CONVERTER (ADC) ............................................................ 26

AUTOMATIC LEVEL CONTROL (ALC) ......................................................................... 28

OUTPUT SIGNAL PATH ................................................................................................ 31

ANALOGUE OUTPUTS ................................................................................................. 37

ENABLING THE OUTPUTS ........................................................................................... 41

HEADPHONE OUTPUT ................................................................................................. 41

CLASS D SPEAKER OUTPUTS .................................................................................... 42

VOLUME UPDATES ...................................................................................................... 43

HEADPHONE JACK DETECT ....................................................................................... 45

THERMAL SHUTDOWN ................................................................................................ 46

GENERAL PURPOSE INPUT/OUTPUT ........................................................................ 47

DIGITAL AUDIO INTERFACE ........................................................................................ 48

AUDIO INTERFACE CONTROL .................................................................................... 52

CLOCKING AND SAMPLE RATES ................................................................................ 56

CONTROL INTERFACE................................................................................................. 63

POWER MANAGEMENT ............................................................................................... 63

REGISTER MAP .................................................................................................. 67

REGISTER BITS BY ADDRESS .................................................................................... 68

DIGITAL FILTER CHARACTERISTICS .............................................................. 82

ADC FILTER RESPONSES ........................................................................................... 83

DAC FILTER RESPONSES ........................................................................................... 83

DE-EMPHASIS FILTER RESPONSES .......................................................................... 85

APPLICATIONS INFORMATION ........................................................................ 86

RECOMMENDED EXTERNAL COMPONENTS ............................................................ 86

IMPORTANT NOTICE ......................................................................................... 90

ADDRESS: ..................................................................................................................... 90

REVISION HISTORY ........................................................................................... 91

w

PD, August 2013, Rev 4.2

2

�

WM8960

Production Data

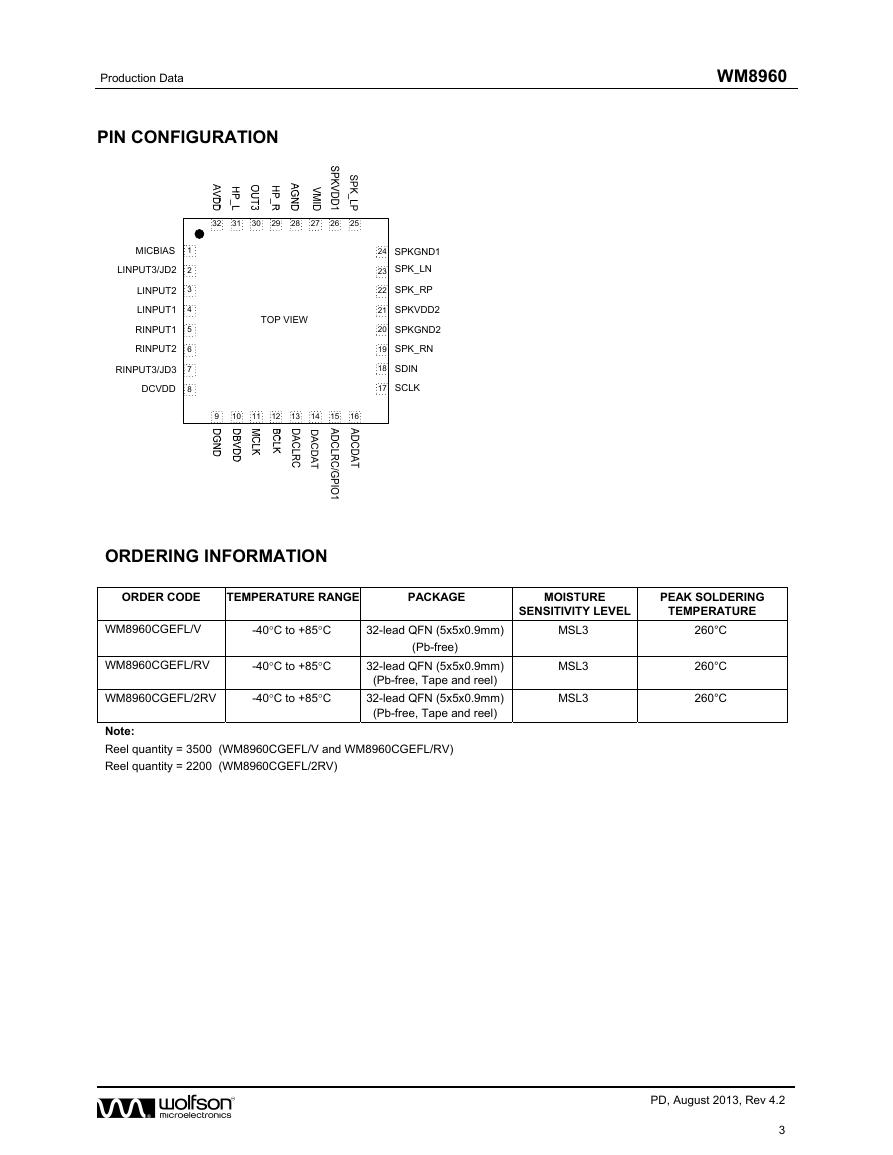

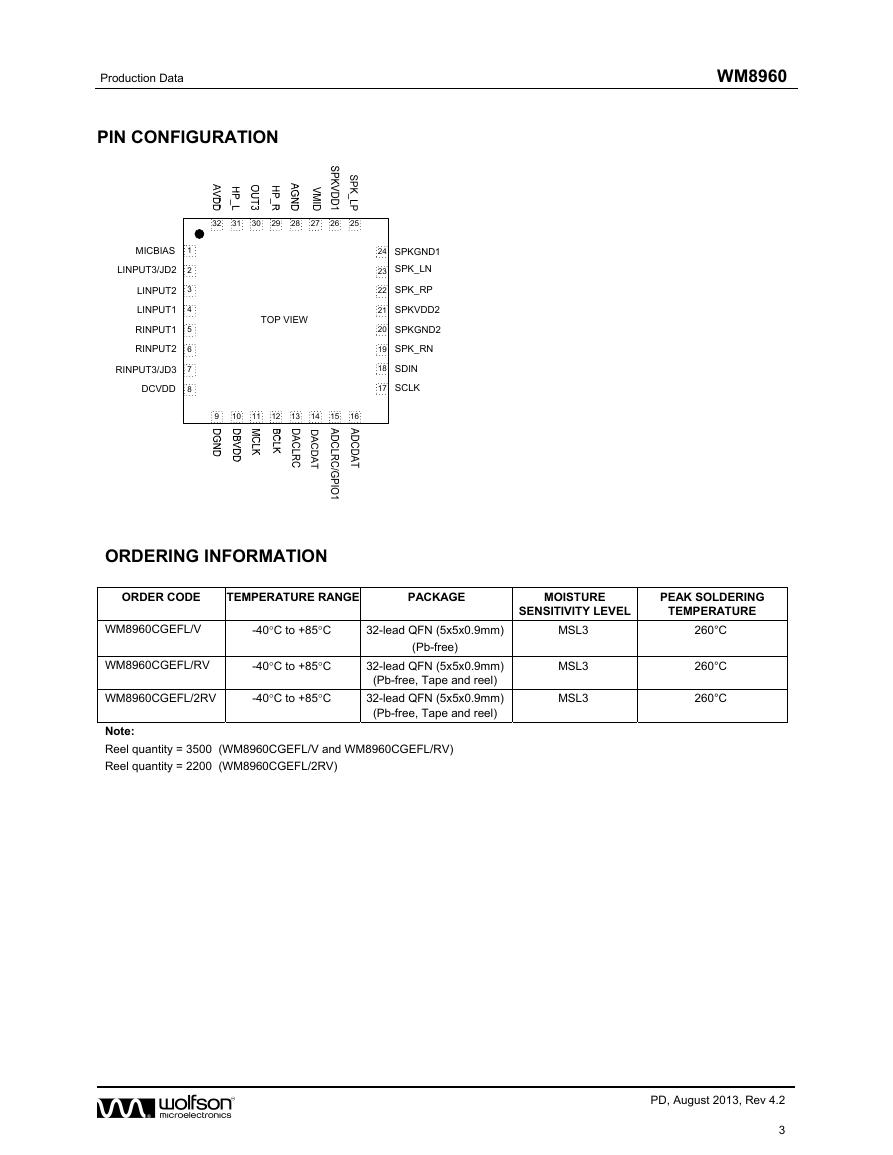

PIN CONFIGURATION

MICBIAS

LINPUT3/JD2

LINPUT2

LINPUT1

RINPUT1

RINPUT2

RINPUT3/JD3

DCVDD

1

2

3

4

5

6

7

8

32

31

30

29

28

27

26

25

TOP VIEW

9

10

11

12

13

14

15

16

24

23

22

21

20

19

18

17

SPKGND1

SPK_LN

SPK_RP

SPKVDD2

SPKGND2

SPK_RN

SDIN

SCLK

ORDERING INFORMATION

ORDER CODE

TEMPERATURE RANGE

PACKAGE

MOISTURE

SENSITIVITY LEVEL

PEAK SOLDERING

TEMPERATURE

WM8960CGEFL/V

-40C to +85C

32-lead QFN (5x5x0.9mm)

WM8960CGEFL/RV

-40C to +85C

WM8960CGEFL/2RV

-40C to +85C

(Pb-free)

32-lead QFN (5x5x0.9mm)

(Pb-free, Tape and reel)

32-lead QFN (5x5x0.9mm)

(Pb-free, Tape and reel)

Note:

Reel quantity = 3500 (WM8960CGEFL/V and WM8960CGEFL/RV)

Reel quantity = 2200 (WM8960CGEFL/2RV)

MSL3

MSL3

MSL3

260°C

260°C

260°C

w

PD, August 2013, Rev 4.2

3

�

WM8960

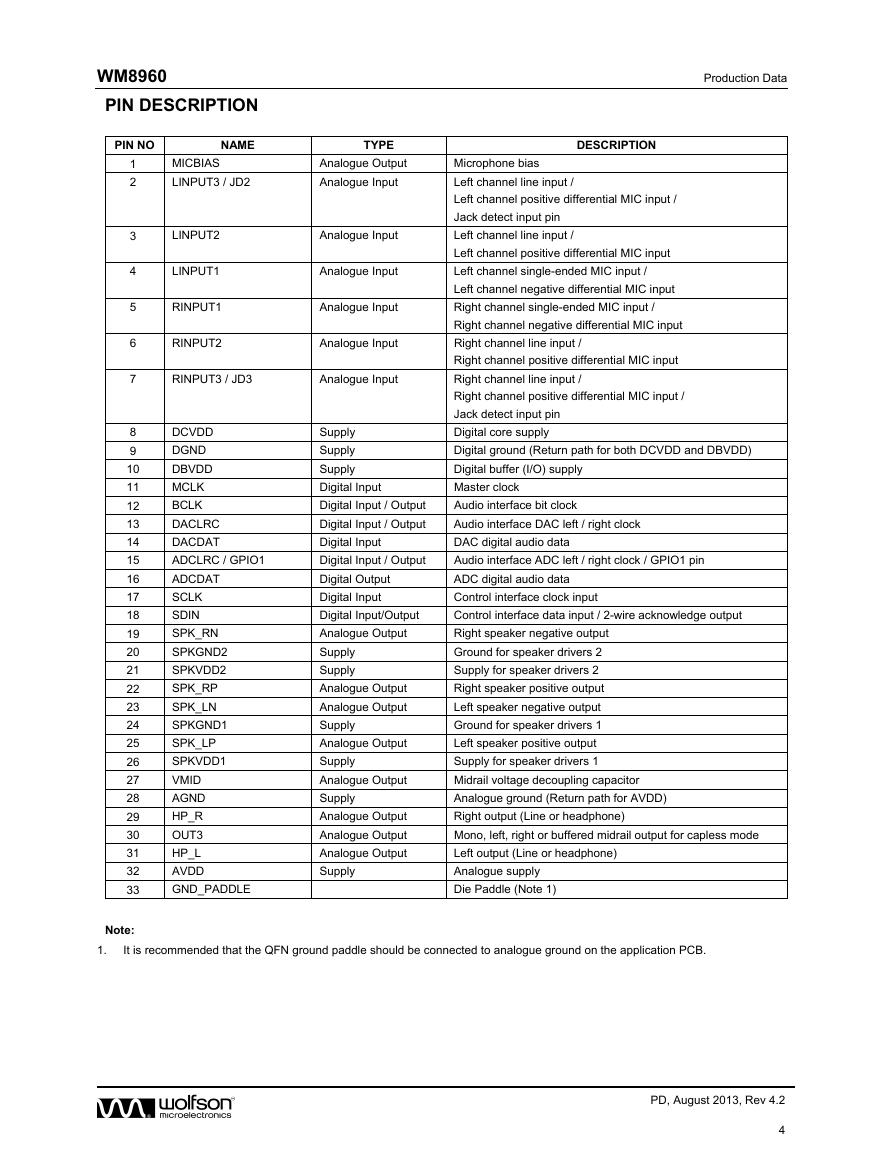

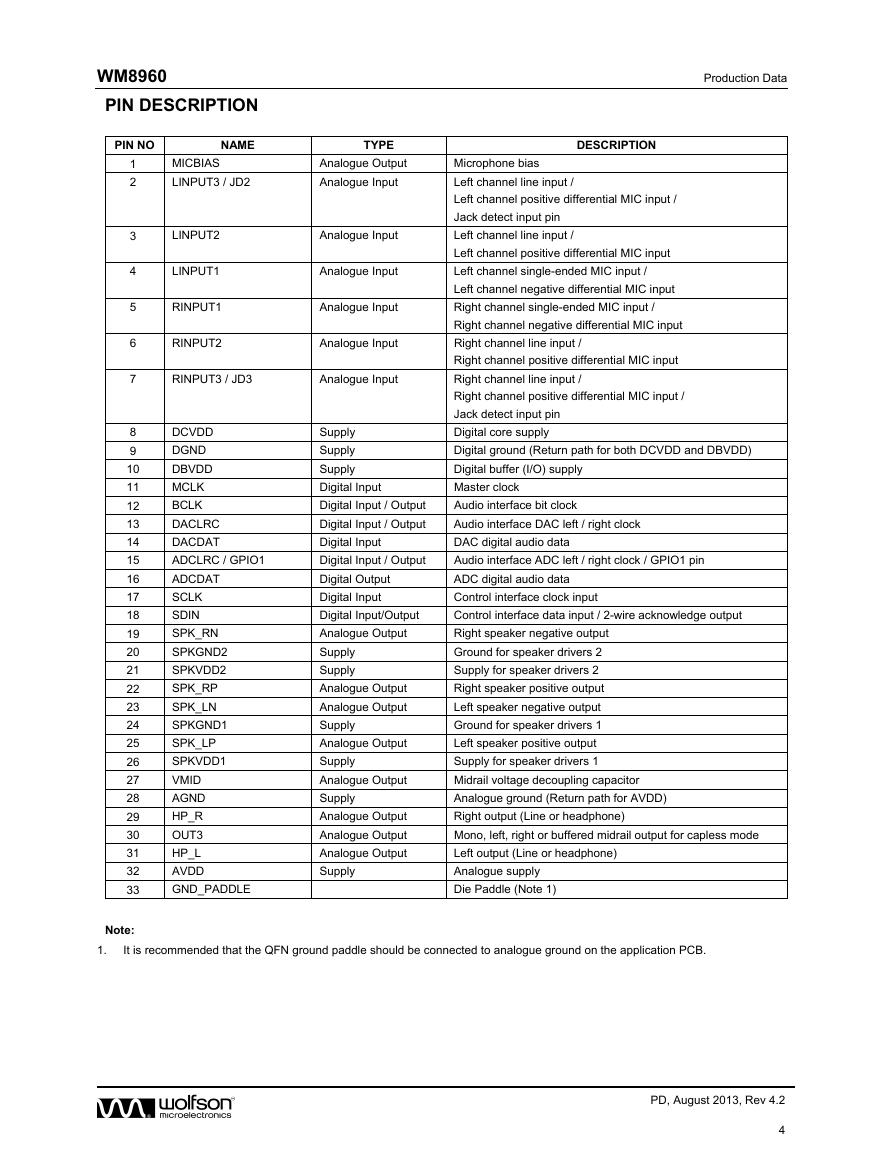

PIN DESCRIPTION

Production Data

PIN NO

NAME

MICBIAS

LINPUT3 / JD2

LINPUT2

LINPUT1

RINPUT1

RINPUT2

TYPE

Analogue Output

Analogue Input

Analogue Input

Analogue Input

Analogue Input

Analogue Input

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

RINPUT3 / JD3

Analogue Input

DCVDD

DGND

DBVDD

MCLK

BCLK

DACLRC

DACDAT

ADCLRC / GPIO1

ADCDAT

SCLK

SDIN

SPK_RN

SPKGND2

SPKVDD2

SPK_RP

SPK_LN

SPKGND1

SPK_LP

SPKVDD1

VMID

AGND

HP_R

OUT3

HP_L

AVDD

GND_PADDLE

Supply

Supply

Supply

Digital Input

Digital Input / Output

Digital Input / Output

Digital Input

Digital Input / Output

Digital Output

Digital Input

Digital Input/Output

Analogue Output

Supply

Supply

Analogue Output

Analogue Output

Supply

Analogue Output

Supply

Analogue Output

Supply

Analogue Output

Analogue Output

Analogue Output

Supply

DESCRIPTION

Microphone bias

Left channel line input /

Left channel positive differential MIC input /

Jack detect input pin

Left channel line input /

Left channel positive differential MIC input

Left channel single-ended MIC input /

Left channel negative differential MIC input

Right channel single-ended MIC input /

Right channel negative differential MIC input

Right channel line input /

Right channel positive differential MIC input

Right channel line input /

Right channel positive differential MIC input /

Jack detect input pin

Digital core supply

Digital ground (Return path for both DCVDD and DBVDD)

Digital buffer (I/O) supply

Master clock

Audio interface bit clock

Audio interface DAC left / right clock

DAC digital audio data

Audio interface ADC left / right clock / GPIO1 pin

ADC digital audio data

Control interface clock input

Control interface data input / 2-wire acknowledge output

Right speaker negative output

Ground for speaker drivers 2

Supply for speaker drivers 2

Right speaker positive output

Left speaker negative output

Ground for speaker drivers 1

Left speaker positive output

Supply for speaker drivers 1

Midrail voltage decoupling capacitor

Analogue ground (Return path for AVDD)

Right output (Line or headphone)

Mono, left, right or buffered midrail output for capless mode

Left output (Line or headphone)

Analogue supply

Die Paddle (Note 1)

Note:

1.

It is recommended that the QFN ground paddle should be connected to analogue ground on the application PCB.

w

PD, August 2013, Rev 4.2

4

�

Production Data

WM8960

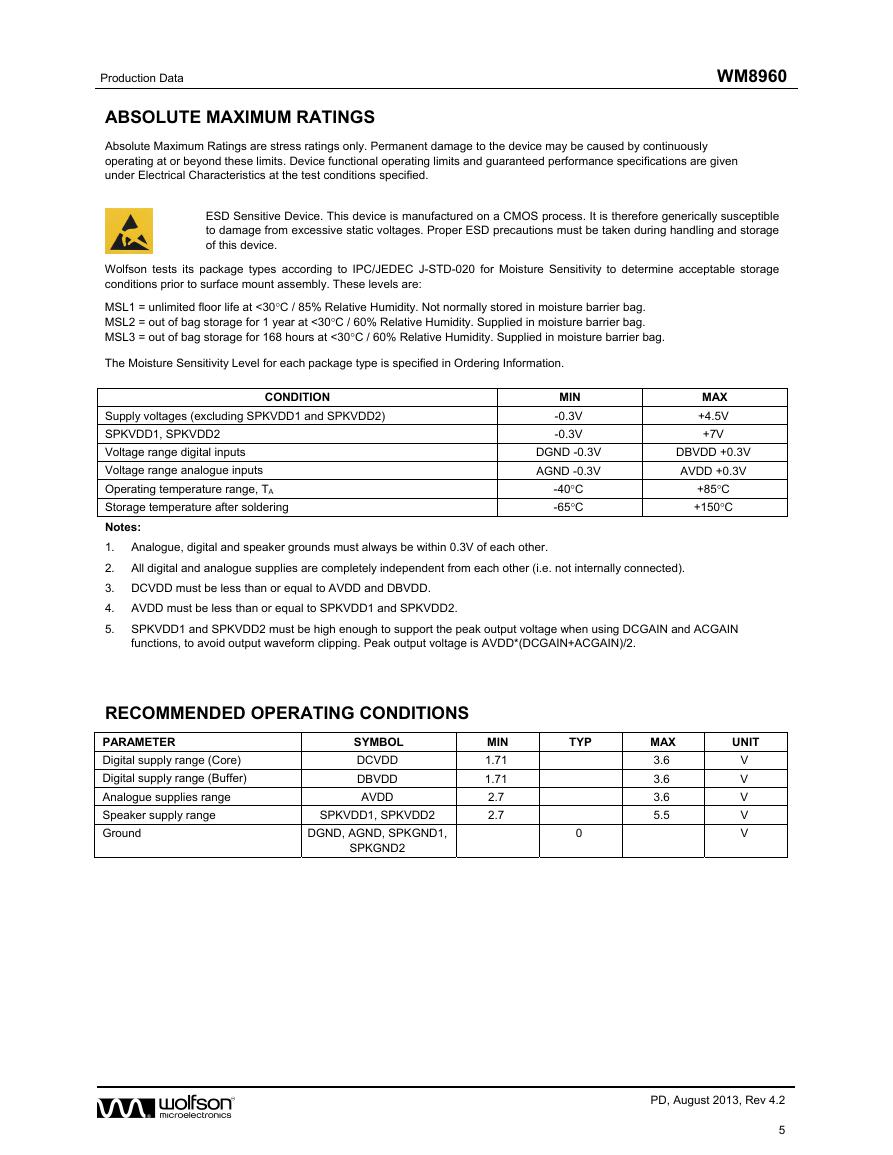

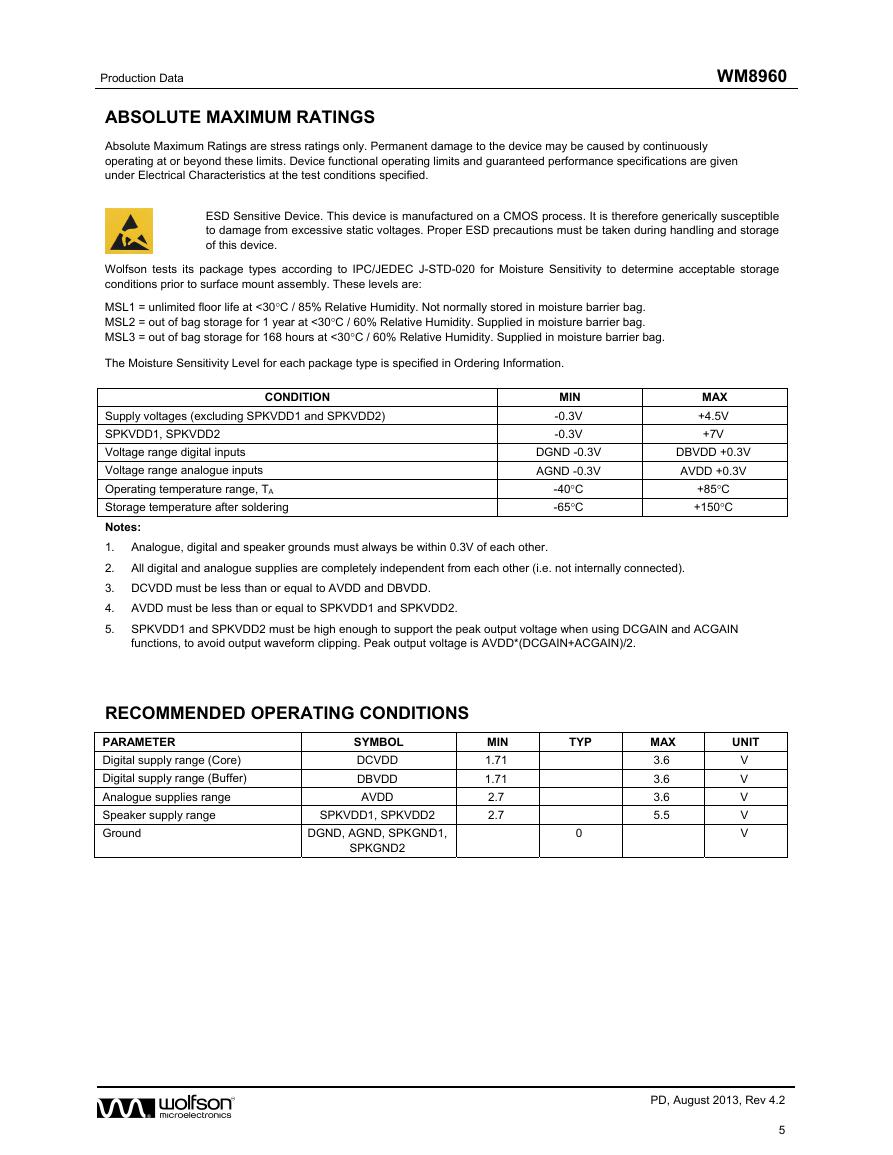

ABSOLUTE MAXIMUM RATINGS

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously

operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given

under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible

to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage

of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020 for Moisture Sensitivity to determine acceptable storage

conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

MIN

-0.3V

-0.3V

MAX

+4.5V

+7V

DBVDD +0.3V

AVDD +0.3V

CONDITION

Supply voltages (excluding SPKVDD1 and SPKVDD2)

SPKVDD1, SPKVDD2

Voltage range digital inputs

Voltage range analogue inputs

Operating temperature range, TA

Storage temperature after soldering

Notes:

1. Analogue, digital and speaker grounds must always be within 0.3V of each other.

2. All digital and analogue supplies are completely independent from each other (i.e. not internally connected).

3. DCVDD must be less than or equal to AVDD and DBVDD.

4. AVDD must be less than or equal to SPKVDD1 and SPKVDD2.

5. SPKVDD1 and SPKVDD2 must be high enough to support the peak output voltage when using DCGAIN and ACGAIN

DGND -0.3V

AGND -0.3V

+85C

+150C

-40C

-65C

functions, to avoid output waveform clipping. Peak output voltage is AVDD*(DCGAIN+ACGAIN)/2.

RECOMMENDED OPERATING CONDITIONS

PARAMETER

Digital supply range (Core)

Digital supply range (Buffer)

Analogue supplies range

Speaker supply range

Ground

SYMBOL

DCVDD

DBVDD

AVDD

DGND, AGND, SPKGND1,

SPKVDD1, SPKVDD2

SPKGND2

MIN

1.71

1.71

2.7

2.7

TYP

0

MAX

3.6

3.6

3.6

5.5

UNIT

V

V

V

V

V

w

PD, August 2013, Rev 4.2

5

�

WM8960

Production Data

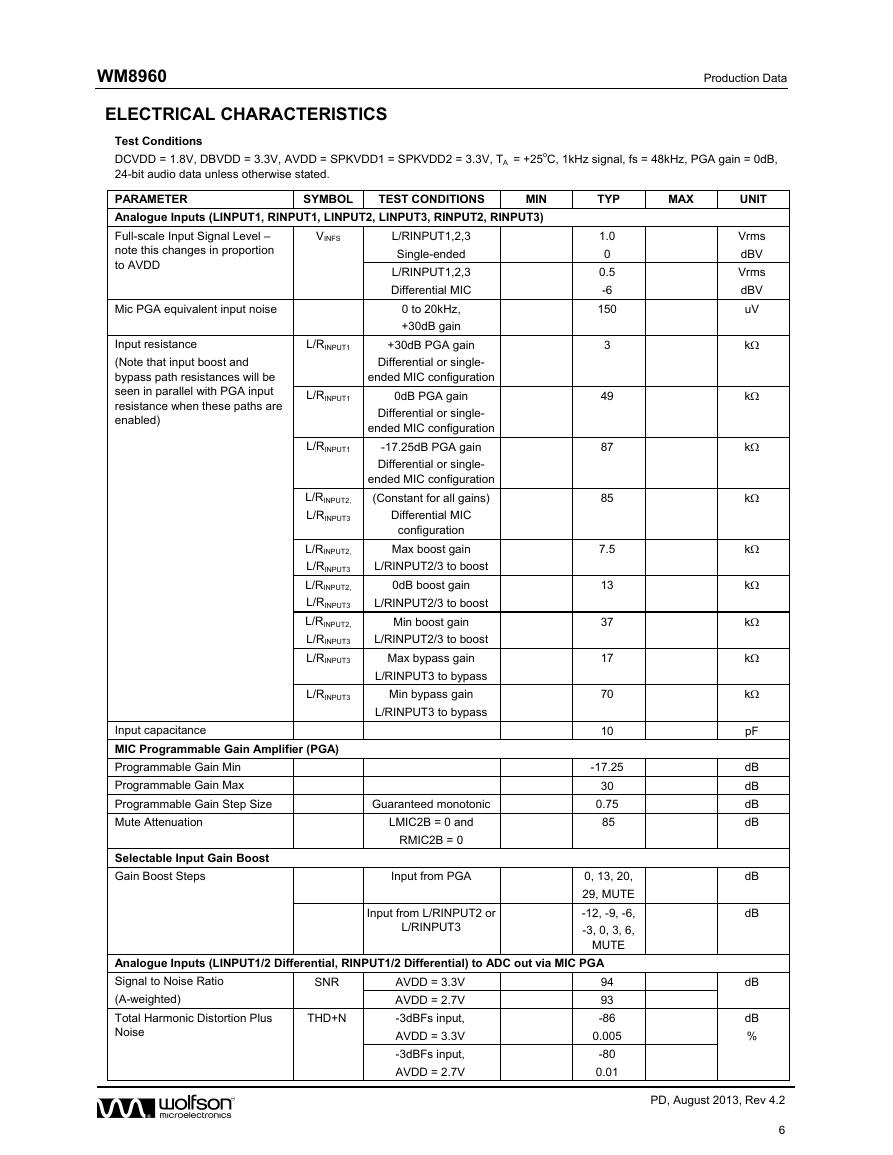

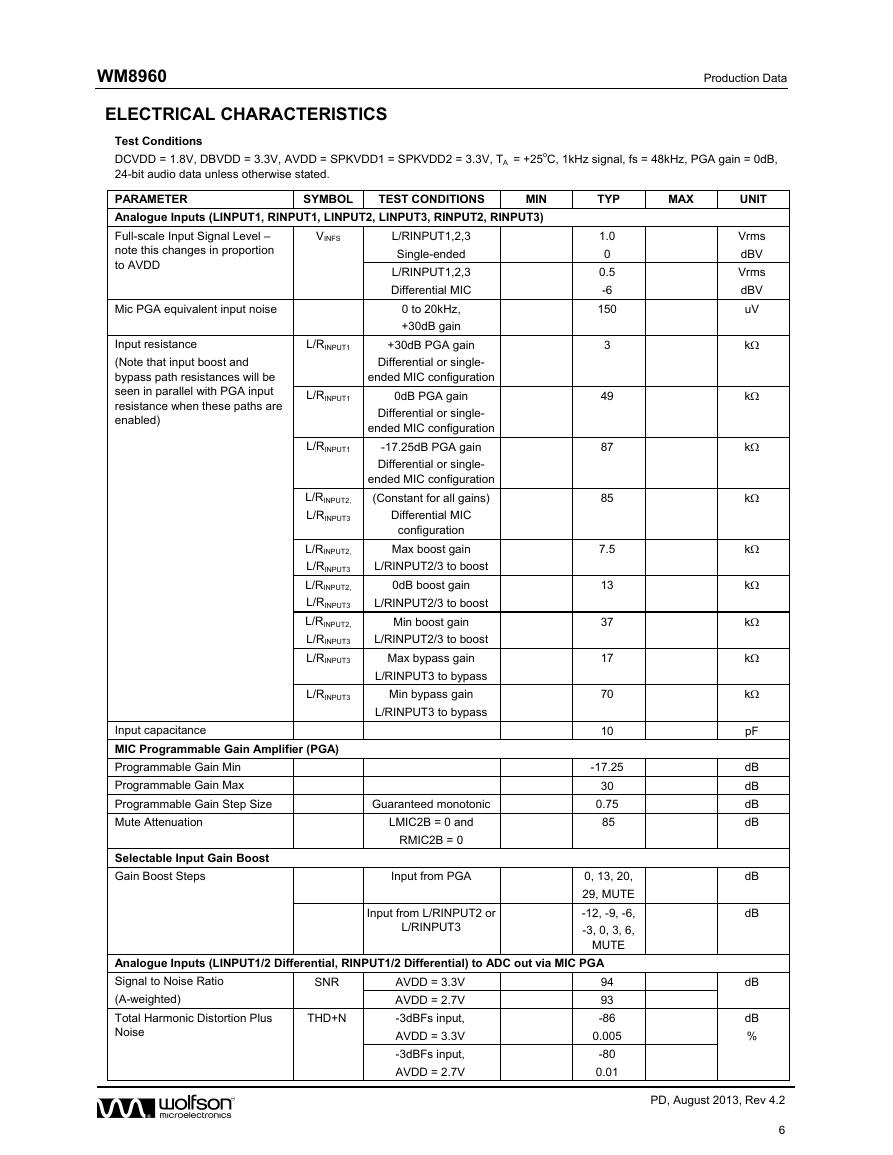

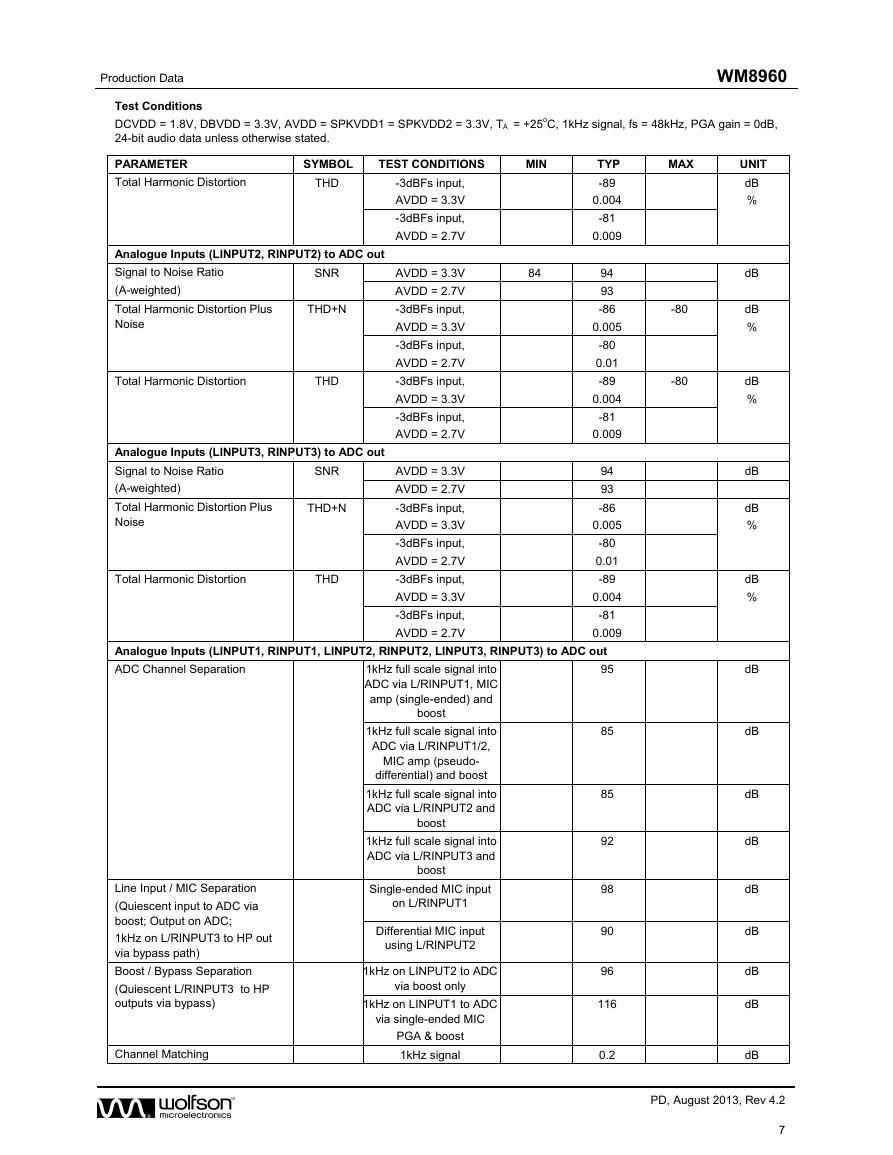

ELECTRICAL CHARACTERISTICS

Test Conditions

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = SPKVDD1 = SPKVDD2 = 3.3V, TA = +25oC, 1kHz signal, fs = 48kHz, PGA gain = 0dB,

24-bit audio data unless otherwise stated.

TYP

MAX

UNIT

SYMBOL

PARAMETER

MIN

Analogue Inputs (LINPUT1, RINPUT1, LINPUT2, LINPUT3, RINPUT2, RINPUT3)

Full-scale Input Signal Level –

note this changes in proportion

to AVDD

TEST CONDITIONS

VINFS

L/RINPUT1,2,3

Single-ended

L/RINPUT1,2,3

Differential MIC

Mic PGA equivalent input noise

0 to 20kHz,

+30dB gain

Input resistance

(Note that input boost and

bypass path resistances will be

seen in parallel with PGA input

resistance when these paths are

enabled)

L/RINPUT1

+30dB PGA gain

Differential or single-

ended MIC configuration

L/RINPUT1

0dB PGA gain

L/RINPUT1

L/RINPUT2,

L/RINPUT3

L/RINPUT2,

L/RINPUT3

L/RINPUT2,

L/RINPUT3

L/RINPUT2,

L/RINPUT3

L/RINPUT3

Differential or single-

ended MIC configuration

-17.25dB PGA gain

Differential or single-

ended MIC configuration

(Constant for all gains)

Differential MIC

configuration

Max boost gain

L/RINPUT2/3 to boost

0dB boost gain

L/RINPUT2/3 to boost

Min boost gain

L/RINPUT2/3 to boost

Max bypass gain

L/RINPUT3 to bypass

L/RINPUT3

Min bypass gain

L/RINPUT3 to bypass

Input capacitance

MIC Programmable Gain Amplifier (PGA)

Programmable Gain Min

Programmable Gain Max

Programmable Gain Step Size

Mute Attenuation

Selectable Input Gain Boost

Gain Boost Steps

Guaranteed monotonic

LMIC2B = 0 and

RMIC2B = 0

Input from PGA

Input from L/RINPUT2 or

L/RINPUT3

1.0

0

0.5

-6

150

3

49

87

85

7.5

13

37

17

70

10

-17.25

30

0.75

85

0, 13, 20,

29, MUTE

-12, -9, -6,

-3, 0, 3, 6,

MUTE

94

93

-86

0.005

-80

0.01

Vrms

dBV

Vrms

dBV

uV

k

k

k

k

k

k

k

k

k

pF

dB

dB

dB

dB

dB

dB

dB

dB

%

Analogue Inputs (LINPUT1/2 Differential, RINPUT1/2 Differential) to ADC out via MIC PGA

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise

THD+N

SNR

AVDD = 3.3V

AVDD = 2.7V

-3dBFs input,

AVDD = 3.3V

-3dBFs input,

AVDD = 2.7V

w

PD, August 2013, Rev 4.2

6

�

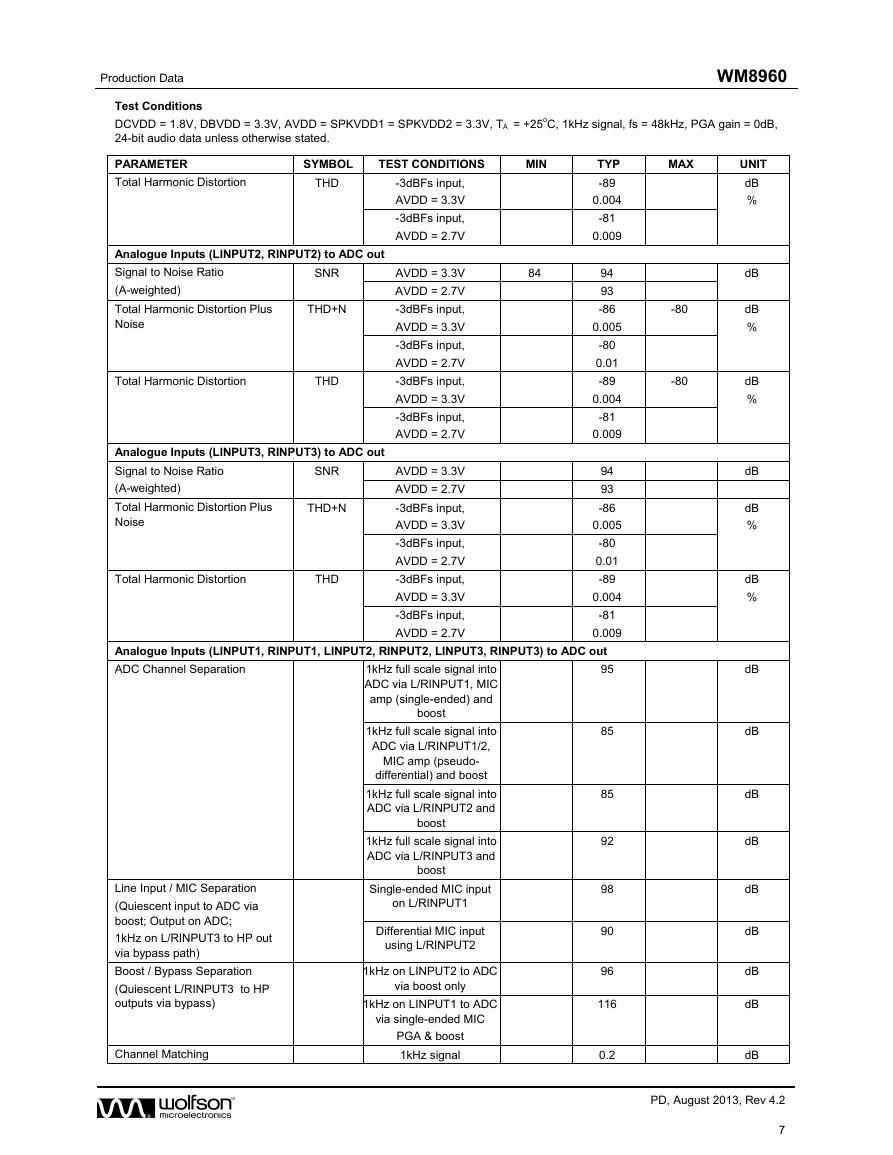

Production Data

WM8960

Test Conditions

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = SPKVDD1 = SPKVDD2 = 3.3V, TA = +25oC, 1kHz signal, fs = 48kHz, PGA gain = 0dB,

24-bit audio data unless otherwise stated.

SYMBOL

TEST CONDITIONS

MIN

PARAMETER

Total Harmonic Distortion

THD

Analogue Inputs (LINPUT2, RINPUT2) to ADC out

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise

THD+N

SNR

Total Harmonic Distortion

THD

Analogue Inputs (LINPUT3, RINPUT3) to ADC out

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise

THD+N

SNR

Total Harmonic Distortion

THD

Analogue Inputs (LINPUT1, RINPUT1, LINPUT2, RINPUT2, LINPUT3, RINPUT3) to ADC out

ADC Channel Separation

95

1kHz full scale signal into

ADC via L/RINPUT1, MIC

amp (single-ended) and

boost

1kHz full scale signal into

ADC via L/RINPUT1/2,

MIC amp (pseudo-

differential) and boost

1kHz full scale signal into

ADC via L/RINPUT2 and

boost

1kHz full scale signal into

ADC via L/RINPUT3 and

boost

Single-ended MIC input

on L/RINPUT1

Differential MIC input

using L/RINPUT2

1kHz on LINPUT2 to ADC

via boost only

1kHz on LINPUT1 to ADC

via single-ended MIC

PGA & boost

1kHz signal

Line Input / MIC Separation

(Quiescent input to ADC via

boost; Output on ADC;

1kHz on L/RINPUT3 to HP out

via bypass path)

Boost / Bypass Separation

(Quiescent L/RINPUT3 to HP

outputs via bypass)

Channel Matching

w

85

85

92

98

90

96

116

0.2

-3dBFs input,

AVDD = 3.3V

-3dBFs input,

AVDD = 2.7V

AVDD = 3.3V

AVDD = 2.7V

-3dBFs input,

AVDD = 3.3V

-3dBFs input,

AVDD = 2.7V

-3dBFs input,

AVDD = 3.3V

-3dBFs input,

AVDD = 2.7V

AVDD = 3.3V

AVDD = 2.7V

-3dBFs input,

AVDD = 3.3V

-3dBFs input,

AVDD = 2.7V

-3dBFs input,

AVDD = 3.3V

-3dBFs input,

AVDD = 2.7V

84

TYP

-89

0.004

-81

0.009

94

93

-86

0.005

-80

0.01

-89

0.004

-81

0.009

94

93

-86

0.005

-80

0.01

-89

0.004

-81

0.009

MAX

-80

-80

UNIT

dB

%

dB

dB

%

dB

%

dB

dB

%

dB

%

dB

dB

dB

dB

dB

dB

dB

dB

dB

PD, August 2013, Rev 4.2

7

�

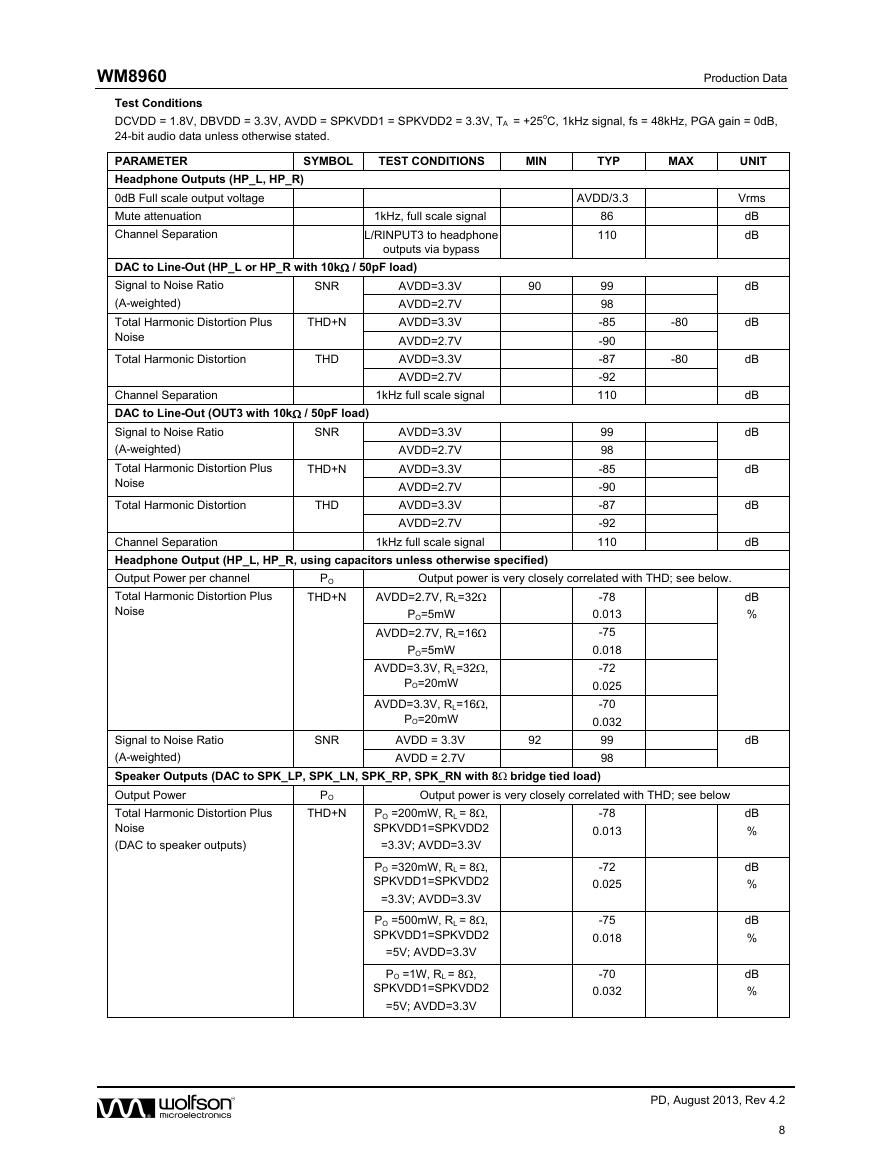

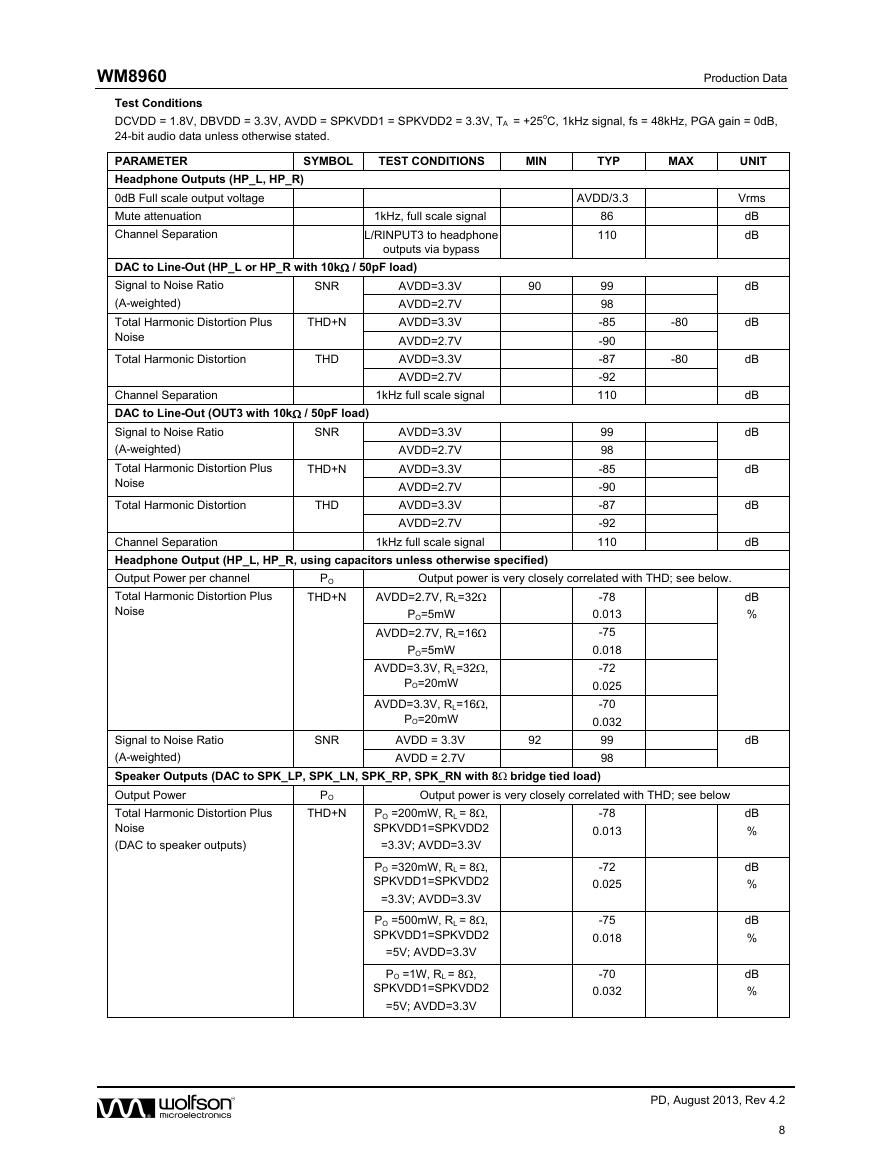

WM8960

Production Data

Test Conditions

DCVDD = 1.8V, DBVDD = 3.3V, AVDD = SPKVDD1 = SPKVDD2 = 3.3V, TA = +25oC, 1kHz signal, fs = 48kHz, PGA gain = 0dB,

24-bit audio data unless otherwise stated.

TEST CONDITIONS

MIN

TYP

MAX

UNIT

SYMBOL

PARAMETER

Headphone Outputs (HP_L, HP_R)

0dB Full scale output voltage

Mute attenuation

Channel Separation

1kHz, full scale signal

L/RINPUT3 to headphone

outputs via bypass

DAC to Line-Out (HP_L or HP_R with 10k / 50pF load)

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise

Total Harmonic Distortion

THD+N

SNR

THD

AVDD=3.3V

AVDD=2.7V

AVDD=3.3V

AVDD=2.7V

AVDD=3.3V

AVDD=2.7V

Channel Separation

DAC to Line-Out (OUT3 with 10k / 50pF load)

Signal to Noise Ratio

(A-weighted)

Total Harmonic Distortion Plus

Noise

Total Harmonic Distortion

THD+N

SNR

THD

1kHz full scale signal

AVDD=3.3V

AVDD=2.7V

AVDD=3.3V

AVDD=2.7V

AVDD=3.3V

AVDD=2.7V

AVDD/3.3

86

110

99

98

-85

-90

-87

-92

110

99

98

-85

-90

-87

-92

110

-80

-80

90

-78

0.013

-75

0.018

-72

0.025

-70

0.032

99

98

-78

0.013

-72

0.025

-75

0.018

-70

0.032

Vrms

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

%

dB

dB

%

dB

%

dB

%

dB

%

Channel Separation

Headphone Output (HP_L, HP_R, using capacitors unless otherwise specified)

Output Power per channel

Total Harmonic Distortion Plus

Noise

AVDD=2.7V, RL=32

1kHz full scale signal

THD+N

PO

PO=5mW

Output power is very closely correlated with THD; see below.

SNR

Signal to Noise Ratio

(A-weighted)

Speaker Outputs (DAC to SPK_LP, SPK_LN, SPK_RP, SPK_RN with 8 bridge tied load)

Output Power

Total Harmonic Distortion Plus

Noise

(DAC to speaker outputs)

THD+N

92

PO

Output power is very closely correlated with THD; see below

AVDD=2.7V, RL=16

PO=5mW

AVDD=3.3V, RL=32,

PO=20mW

AVDD=3.3V, RL=16,

PO=20mW

AVDD = 3.3V

AVDD = 2.7V

PO =200mW, RL = 8,

SPKVDD1=SPKVDD2

=3.3V; AVDD=3.3V

PO =320mW, RL = 8,

SPKVDD1=SPKVDD2

=3.3V; AVDD=3.3V

PO =500mW, RL = 8,

SPKVDD1=SPKVDD2

=5V; AVDD=3.3V

PO =1W, RL = 8,

SPKVDD1=SPKVDD2

=5V; AVDD=3.3V

w

PD, August 2013, Rev 4.2

8

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf