Preliminary

TTP229

TonTouchTM

16 KEYS OR 8 KEYS TOUCH PAD DETECTOR IC

GENERAL DESCRIPTION

The TTP229 TonTouchTM IC is capacitive sensing design specifically for touch pad controls. The

device built in regulator for touch sensor. Stable sensing method can cover diversity conditions. Human

interfaces control panel links through non-conductive dielectric material. The main application is

focused at replacing of the mechanical switch or button. The ASSP can independently handle the 8

touch pads or up to 16 touch pads.

FEATURES

APPLICATION

Wide consumer products

Button key replacement

09’/10/30 Page 1 of 19 Ver : 1.0

Operating voltage:2.4V~5.5V for built-in regulator enable

2.0V~5.5V for built-in regulator disable

Built-in regulator with external enable/disable option

Stand-by current

At 3V, and sleep mode slow sampling rate 8Hz:

Internal regulator is enabled, the Stand-by current

=> Typical 2.5uA for 16 input keys

=> Typical 2.0uA for 8 input keys

Internal regulator is disabled, the Stand-by current

=> Typical 2.5uA for 16 input keys

=> Typical 2.0uA for 8 input keys

Provides to set 8 direct keys or 16 direct keys by option

Provides to set 8 separate outputs only for 8 direct input keys mode

Has two kinds of serial output interface, both can use for 8 and 16 direct input keys mode

Include 2-wires serial interface and I2C-bus slave interface, they are selected by option

8 separate outputs can select output driving types by option

(CMOS/OD/OC with active high/low)

2-wires serial interface can select active high or low by option

Offer multi-key or single-key feature by option

Provides two kinds of sampling rate that slow sampling rate 8Hz

and fast sampling rate 64Hz at sleep mode

Have the maximum key-on time about 60sec by pin option

Sensitivity can adjust by the capacitance(1~50pF) outside

After power-on have about 0.5sec stable-time,

During the time do not touch the key pad, and all functions are disabled

Auto calibration for environment changing

And the re-calibration period is about 4.0sec, when all keys are not activated for fixed time

�

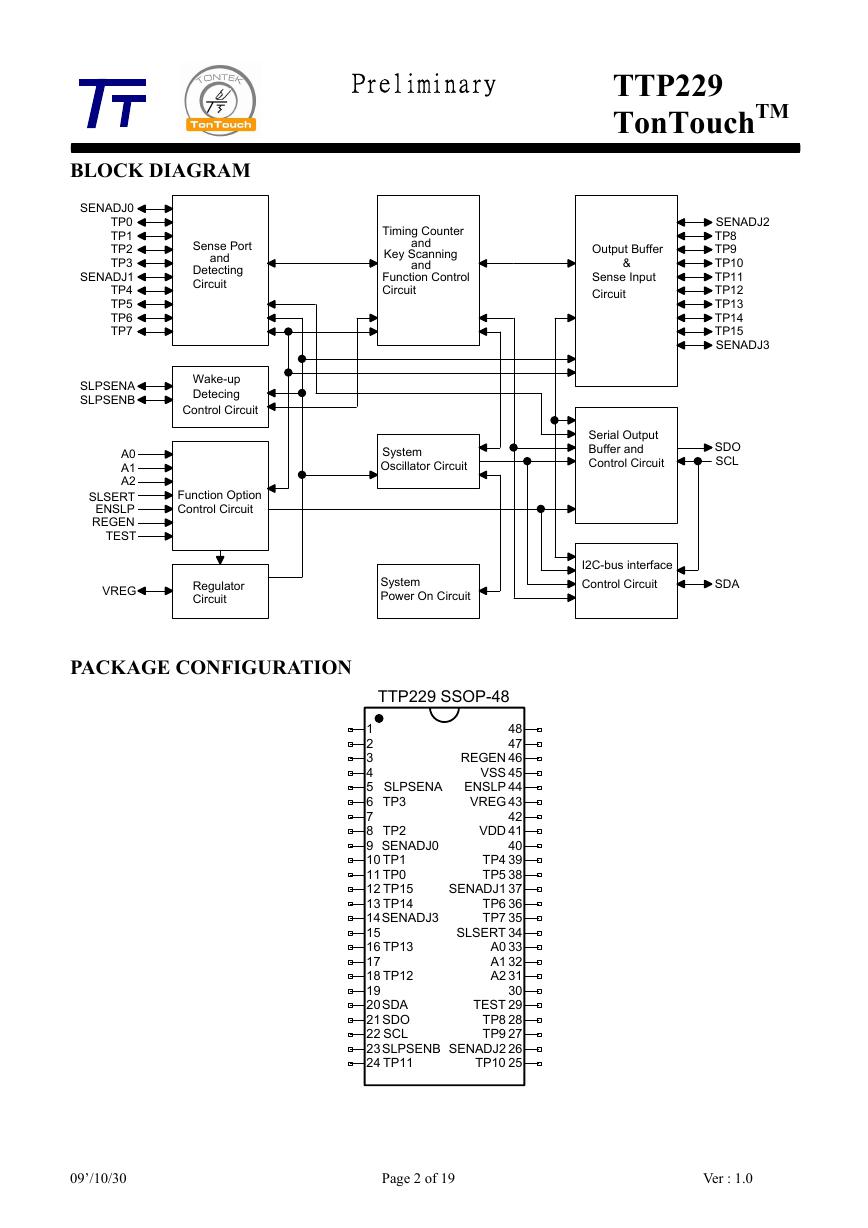

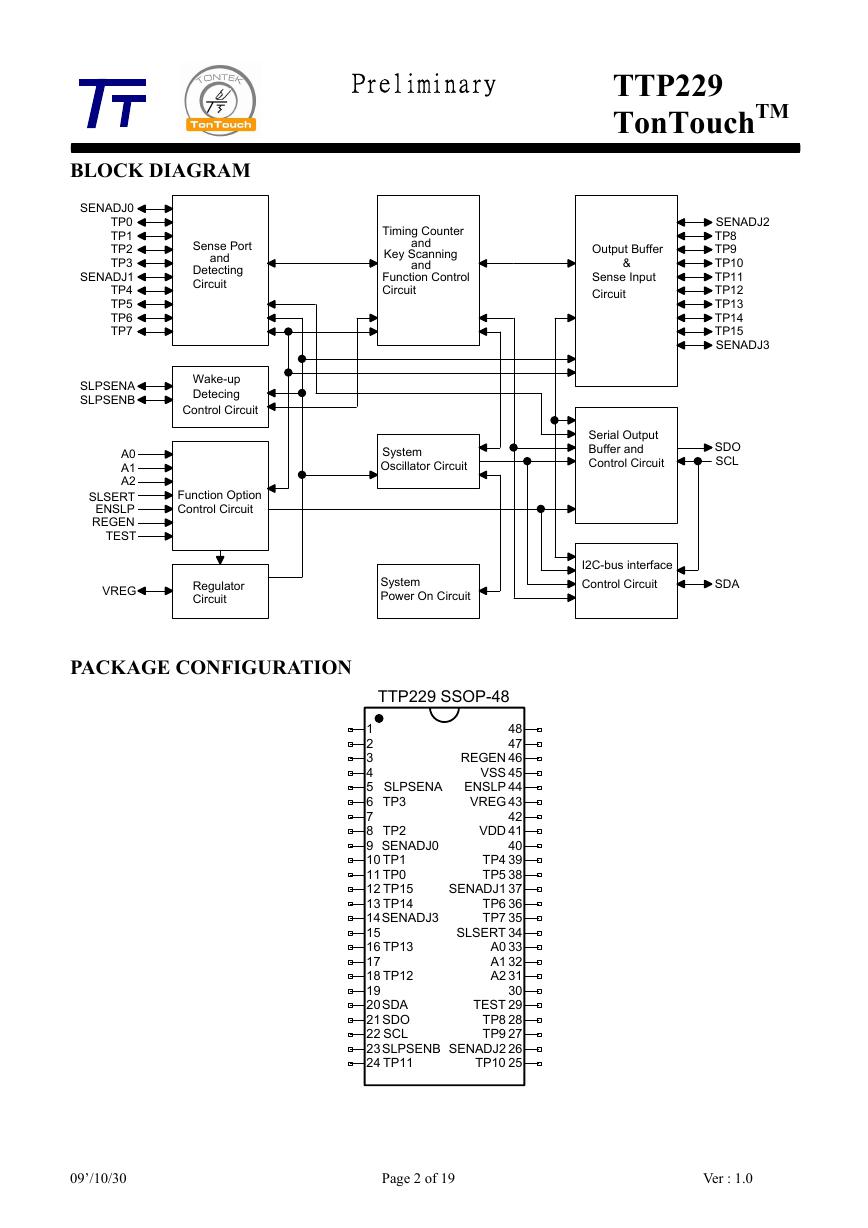

BLOCK DIAGRAM

Preliminary

TTP229

TonTouchTM

SENADJ0

TP0

TP1

TP2

TP3

SENADJ1

TP4

TP5

TP6

TP7

SLPSENA

SLPSENB

A0

A1

A2

SLSERT

ENSLP

REGEN

TEST

VREG

Sense Port

and

Detecting

Circuit

Timing Counter

and

and

Key Scanning

Function Control

Circuit

Output Buffer

&

Sense Input

Circuit

SENADJ2

TP8

TP9

TP10

TP11

TP12

TP13

TP14

TP15

SENADJ3

Wake-up

Detecing

Control Circuit

Function Option

Control Circuit

System

Oscillator Circuit

Serial Output

Buffer and

Control Circuit

SDO

SCL

I2C-bus interface

Control Circuit

SDA

Regulator

Circuit

System

Power On Circuit

PACKAGE CONFIGURATION

TTP229 SSOP-48

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

REGEN

VSS

ENSLP

VREG

VDD

TP4

TP5

SENADJ1

TP6

TP7

SLSERT

A0

A1

A2

SLPSENA

TP3

TP2

SENADJ0

TP1

TP0

TP15

TP14

SENADJ3

TP13

TP12

SDA

SDO

SCL

SLPSENB

TP11

TEST

TP8

TP9

SENADJ2

TP10

48

47

46

45

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

09’/10/30 Page 2 of 19 Ver : 1.0

�

Preliminary

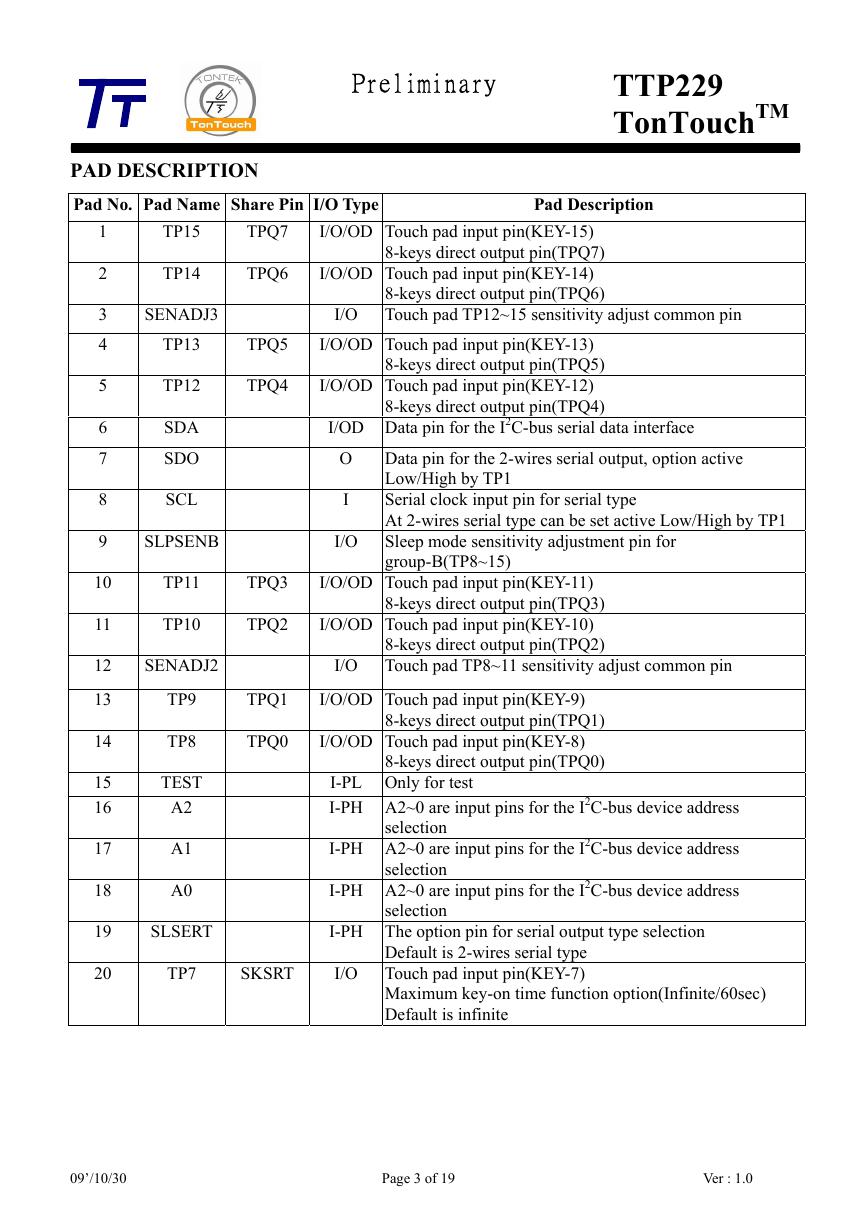

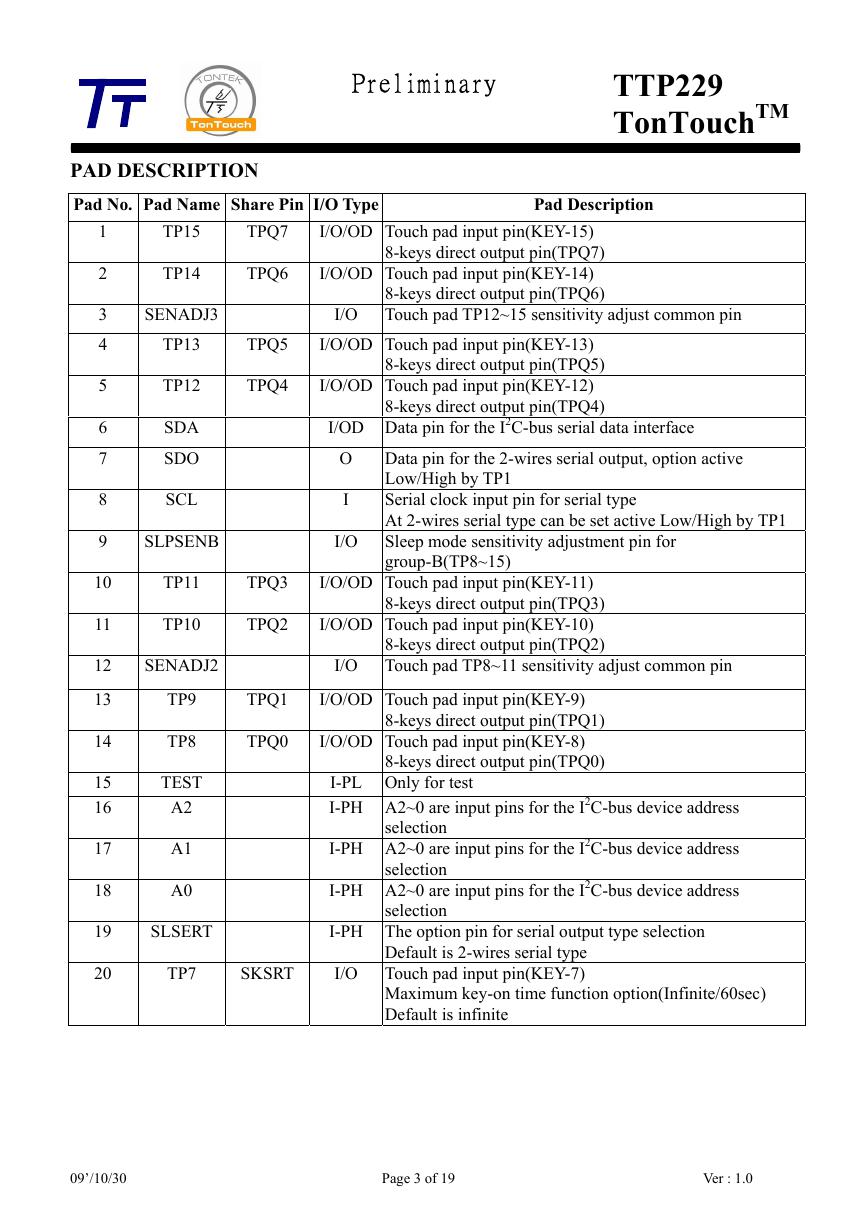

PAD DESCRIPTION

Pad No. Pad Name Share Pin I/O Type

TTP229

TonTouchTM

Pad Description

TP15

TP14

TPQ7

TPQ6

SENADJ3

I/O/OD Touch pad input pin(KEY-15)

8-keys direct output pin(TPQ7)

I/O/OD Touch pad input pin(KEY-14)

8-keys direct output pin(TPQ6)

Touch pad TP12~15 sensitivity adjust common pin

I/O

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

TP13

TP12

SDA

SDO

SCL

SLPSENB

TPQ5

TPQ4

TP11

TP10

TPQ3

TPQ2

SENADJ2

TP9

TP8

TEST

A2

A1

A0

SLSERT

TPQ1

TPQ0

TP7

SKSRT

I/O

I/O/OD Touch pad input pin(KEY-13)

8-keys direct output pin(TPQ5)

I/O/OD Touch pad input pin(KEY-12)

8-keys direct output pin(TPQ4)

I/OD Data pin for the I2C-bus serial data interface

O

Data pin for the 2-wires serial output, option active

Low/High by TP1

Serial clock input pin for serial type

At 2-wires serial type can be set active Low/High by TP1

Sleep mode sensitivity adjustment pin for

group-B(TP8~15)

I

I/O

I/O/OD Touch pad input pin(KEY-11)

8-keys direct output pin(TPQ3)

I/O/OD Touch pad input pin(KEY-10)

8-keys direct output pin(TPQ2)

Touch pad TP8~11 sensitivity adjust common pin

I/O

I/O/OD Touch pad input pin(KEY-9)

8-keys direct output pin(TPQ1)

I/O/OD Touch pad input pin(KEY-8)

8-keys direct output pin(TPQ0)

I-PL Only for test

I-PH A2~0 are input pins for the I2C-bus device address

I-PH A2~0 are input pins for the I2C-bus device address

I-PH A2~0 are input pins for the I2C-bus device address

selection

selection

selection

I-PH The option pin for serial output type selection

Default is 2-wires serial type

Touch pad input pin(KEY-7)

Maximum key-on time function option(Infinite/60sec)

Default is infinite

09’/10/30 Page 3 of 19 Ver : 1.0

�

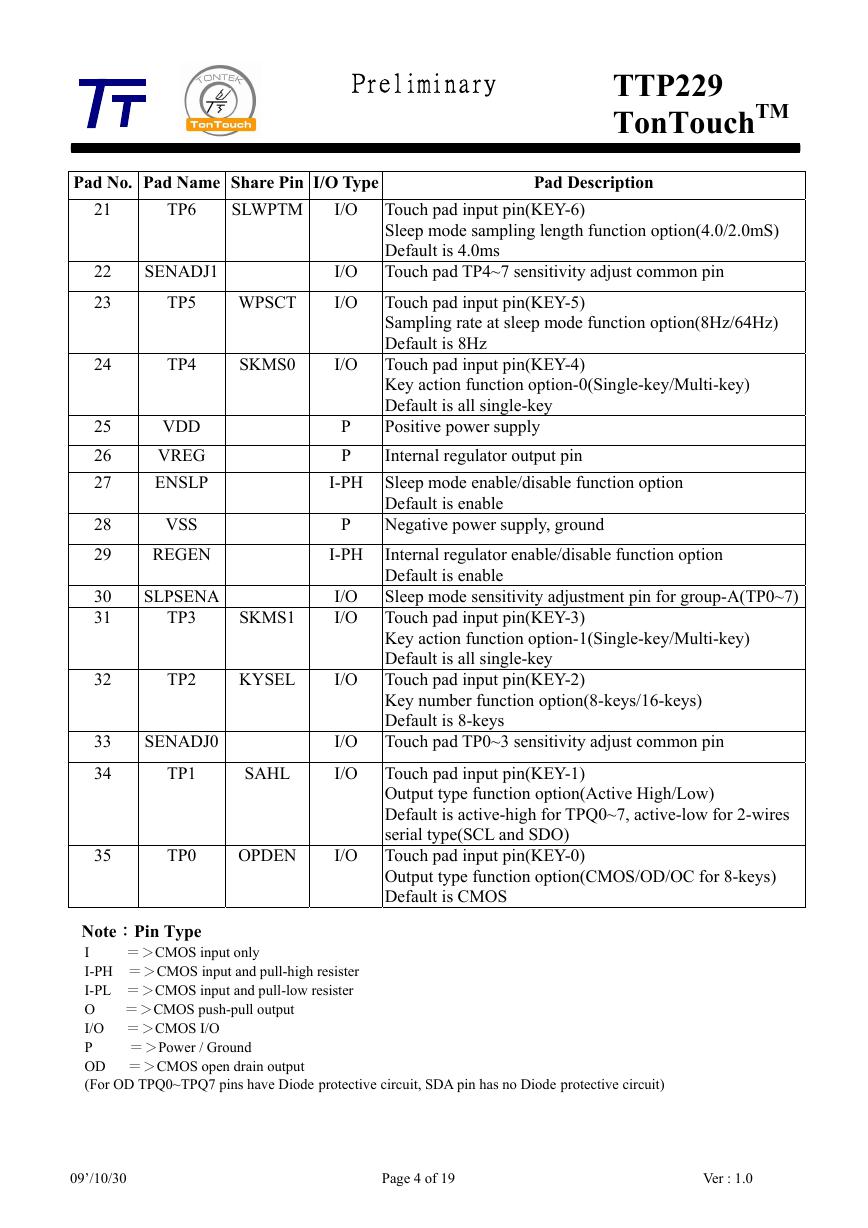

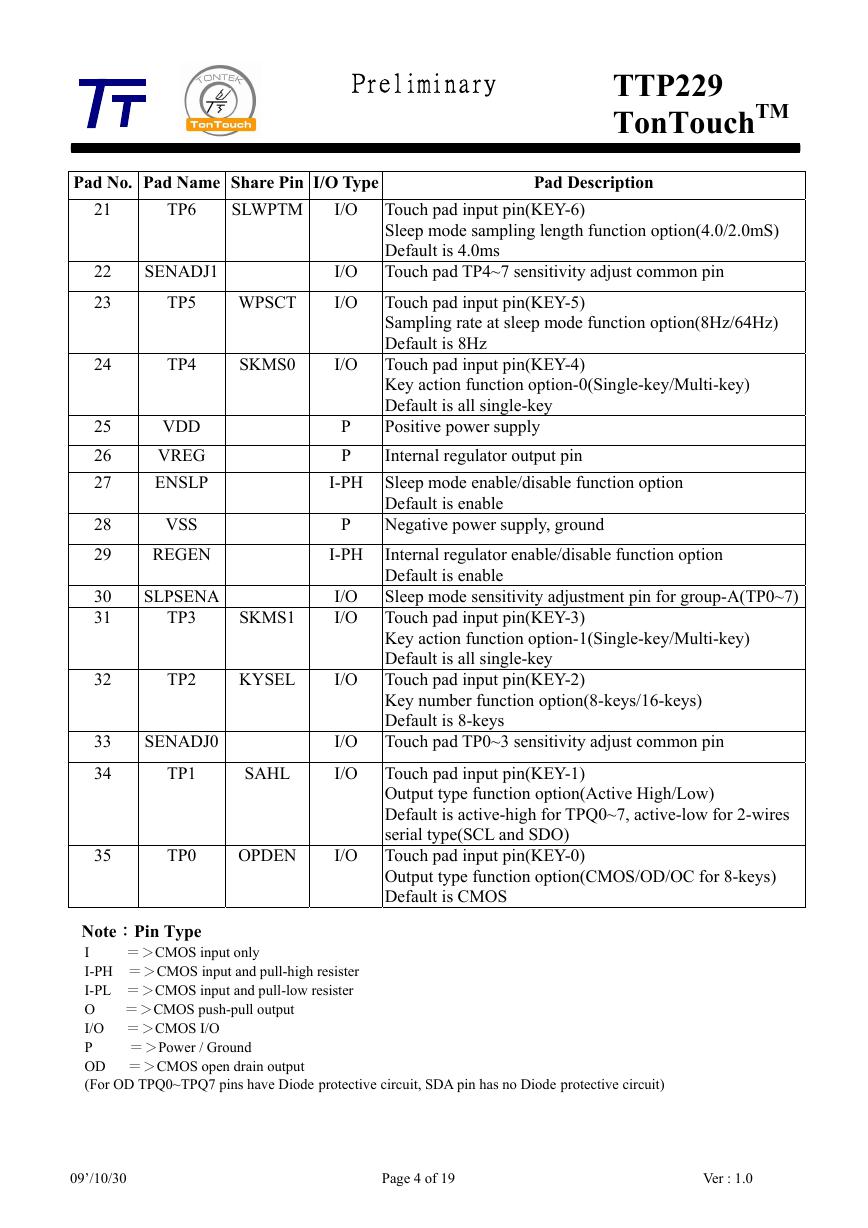

Pad No. Pad Name Share Pin I/O Type

Pad Description

Preliminary

TTP229

TonTouchTM

21

22

23

24

25

26

27

28

29

30

31

32

33

34

TP6

SLWPTM

I/O

SENADJ1

TP5

WPSCT

I/O

I/O

TP4

SKMS0

I/O

VDD

VREG

ENSLP

VSS

REGEN

SLPSENA

TP3

SKMS1

P

P

P

I-PH

I/O

I/O

TP2

KYSEL

I/O

SENADJ0

TP1

SAHL

I/O

I/O

I-PH Sleep mode enable/disable function option

Touch pad input pin(KEY-6)

Sleep mode sampling length function option(4.0/2.0mS)

Default is 4.0ms

Touch pad TP4~7 sensitivity adjust common pin

Touch pad input pin(KEY-5)

Sampling rate at sleep mode function option(8Hz/64Hz)

Default is 8Hz

Touch pad input pin(KEY-4)

Key action function option-0(Single-key/Multi-key)

Default is all single-key

Positive power supply

Internal regulator output pin

Default is enable

Negative power supply, ground

Internal regulator enable/disable function option

Default is enable

Sleep mode sensitivity adjustment pin for group-A(TP0~7)

Touch pad input pin(KEY-3)

Key action function option-1(Single-key/Multi-key)

Default is all single-key

Touch pad input pin(KEY-2)

Key number function option(8-keys/16-keys)

Default is 8-keys

Touch pad TP0~3 sensitivity adjust common pin

Touch pad input pin(KEY-1)

Output type function option(Active High/Low)

Default is active-high for TPQ0~7, active-low for 2-wires

serial type(SCL and SDO)

Touch pad input pin(KEY-0)

Output type function option(CMOS/OD/OC for 8-keys)

Default is CMOS

35

TP0

OPDEN

I/O

Note:Pin Type

I =>CMOS input only

I-PH =>CMOS input and pull-high resister

I-PL =>CMOS input and pull-low resister

O =>CMOS push-pull output

I/O =>CMOS I/O

P =>Power / Ground

OD =>CMOS open drain output

(For OD TPQ0~TPQ7 pins have Diode protective circuit, SDA pin has no Diode protective circuit)

09’/10/30 Page 4 of 19 Ver : 1.0

�

Preliminary

TTP229

TonTouchTM

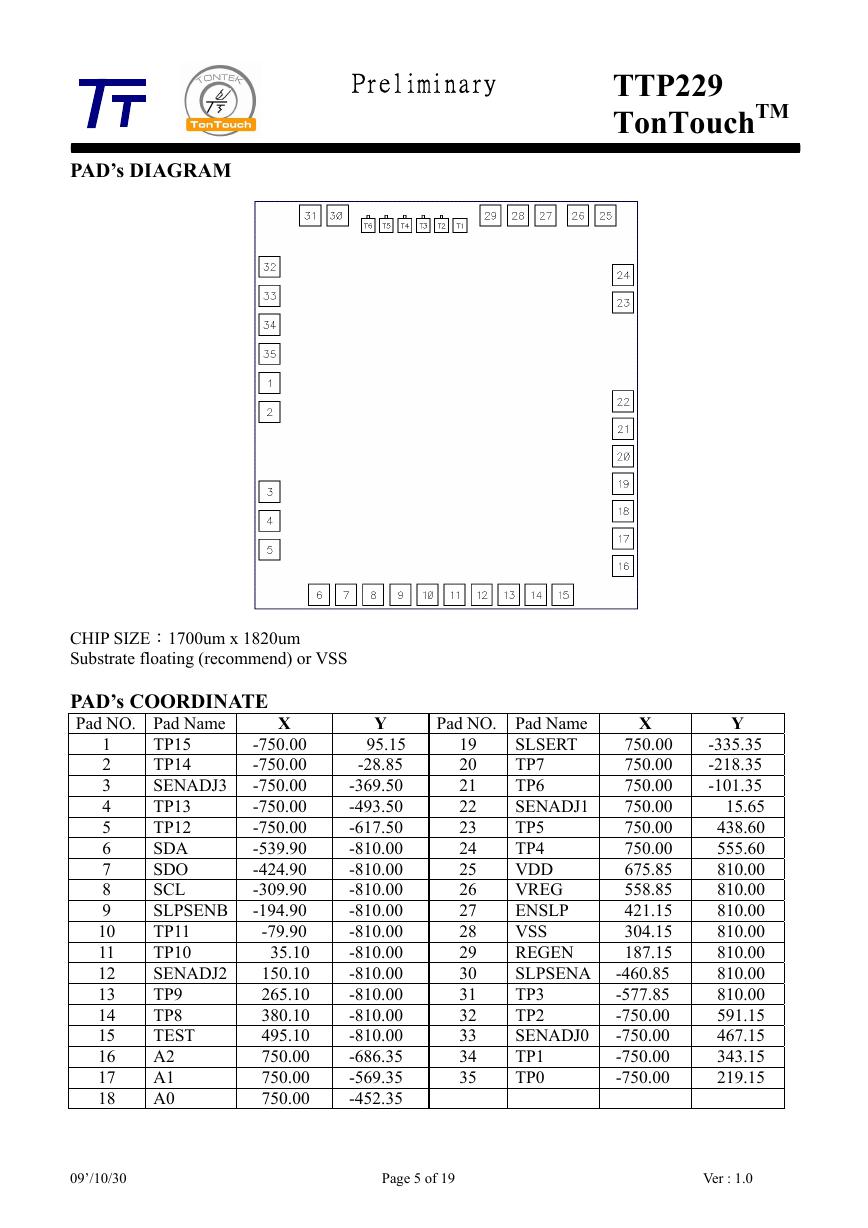

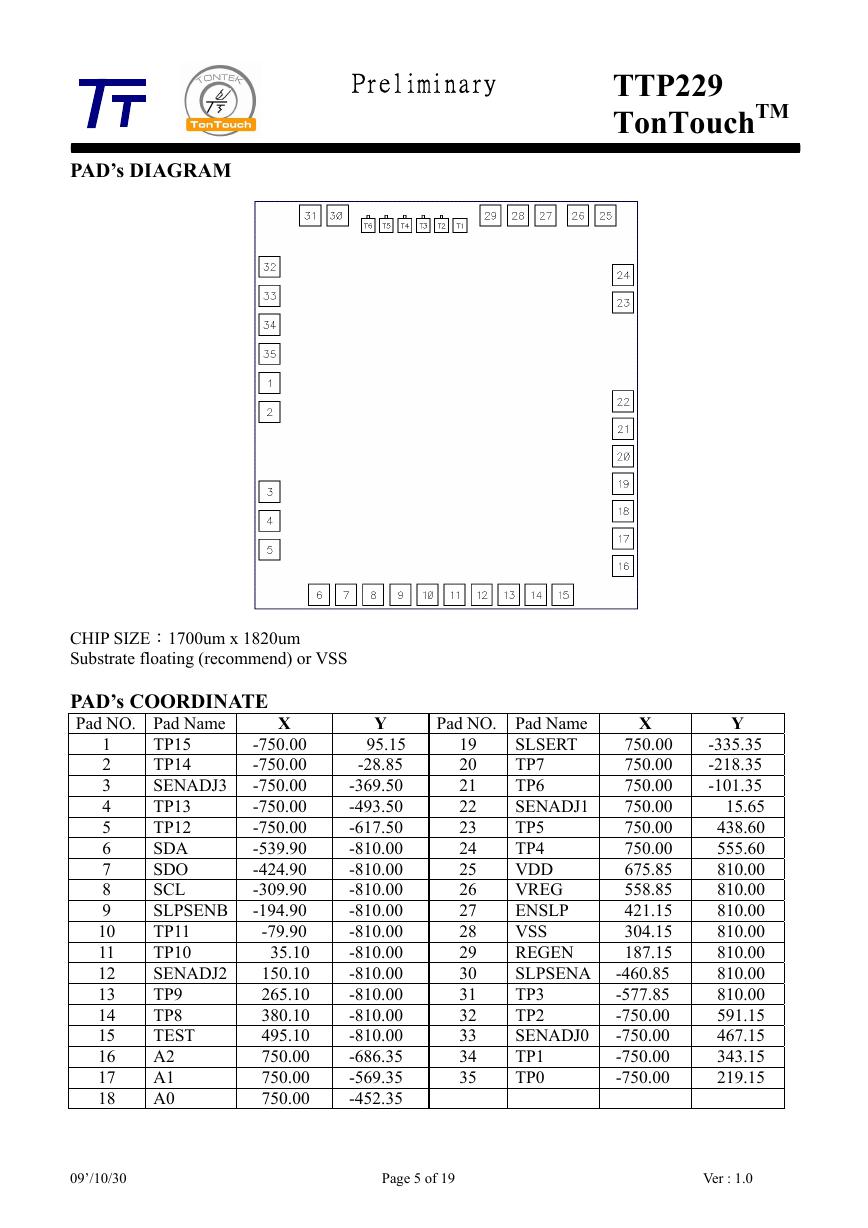

PAD’s DIAGRAM

CHIP SIZE:1700um x 1820um

Substrate floating (recommend) or VSS

PAD’s COORDINATE

Pad NO. Pad Name

X

X

Pad NO. Pad Name

750.00

SLSERT

750.00

TP7

750.00

TP6

750.00

SENADJ1

750.00

TP5

750.00

TP4

675.85

VDD

558.85

VREG

421.15

ENSLP

304.15

VSS

REGEN

187.15

SLPSENA -460.85

TP3

-577.85

-750.00

TP2

-750.00

SENADJ0

TP1

-750.00

-750.00

TP0

19

20

21

22

23

24

25

26

27

28

29

30

31

32

33

34

35

Y

-335.35

-218.35

-101.35

15.65

438.60

555.60

810.00

810.00

810.00

810.00

810.00

810.00

810.00

591.15

467.15

343.15

219.15

Y

95.15

-28.85

-369.50

-493.50

-617.50

-810.00

-810.00

-810.00

-810.00

-810.00

-810.00

-810.00

-810.00

-810.00

-810.00

-686.35

-569.35

-452.35

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

TP15

TP14

SENADJ3

TP13

TP12

SDA

SDO

SCL

SLPSENB

TP11

TP10

SENADJ2

TP9

TP8

TEST

A2

A1

A0

-750.00

-750.00

-750.00

-750.00

-750.00

-539.90

-424.90

-309.90

-194.90

-79.90

35.10

150.10

265.10

380.10

495.10

750.00

750.00

750.00

09’/10/30 Page 5 of 19 Ver : 1.0

�

Preliminary

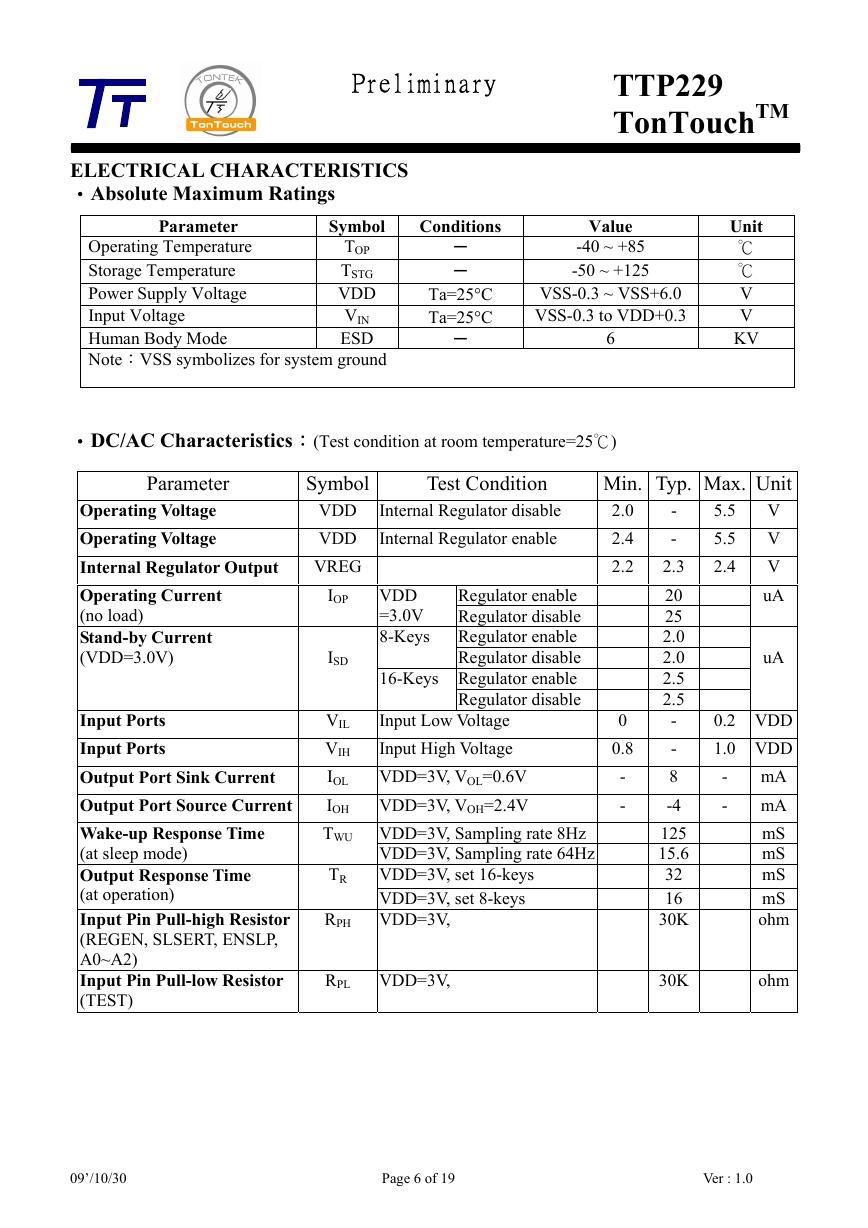

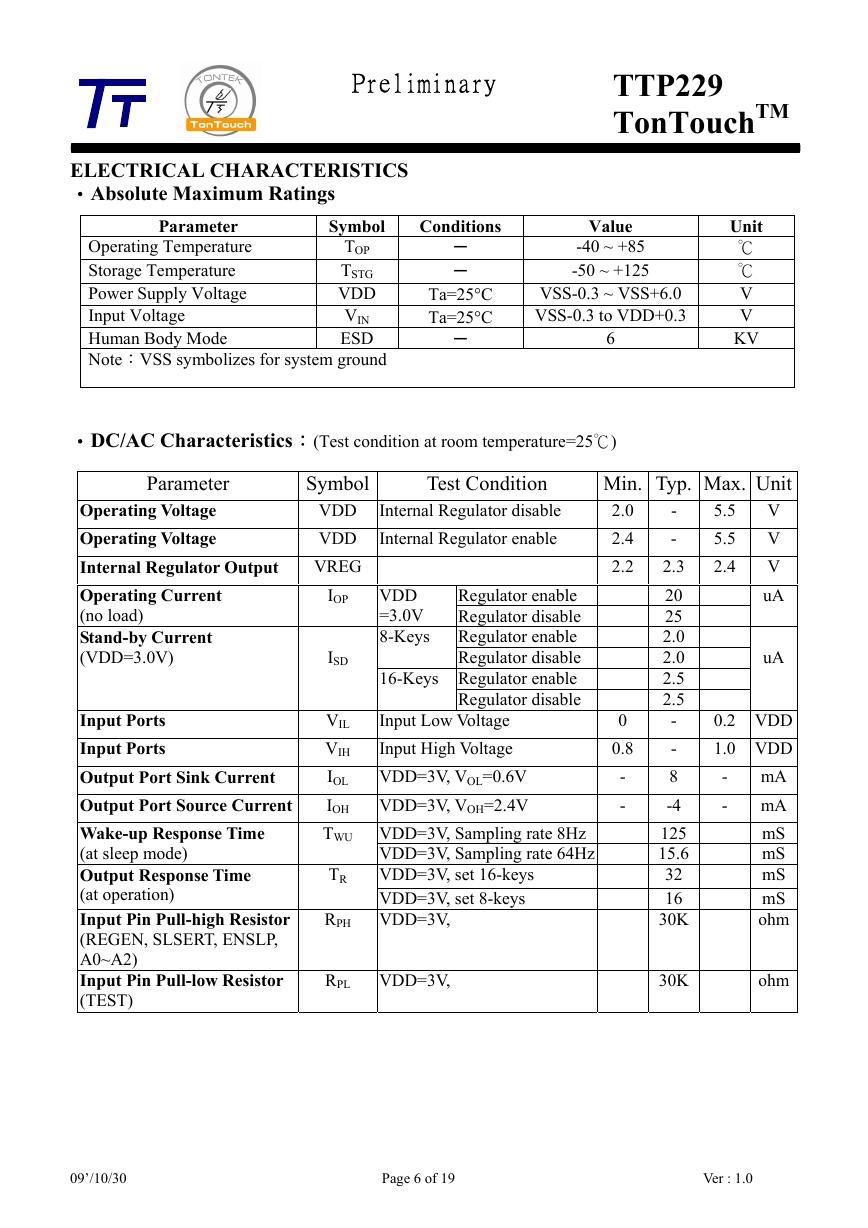

ELECTRICAL CHARACTERISTICS

‧Absolute Maximum Ratings

TTP229

TonTouchTM

Parameter

Operating Temperature

Storage Temperature

Power Supply Voltage

Input Voltage

Human Body Mode

Note:VSS symbolizes for system ground

Symbol

TOP

TSTG

VDD

VIN

ESD

Conditions

─

─

Ta=25°C

Ta=25°C

─

Value

-40 ~ +85

-50 ~ +125

VSS-0.3 ~ VSS+6.0

VSS-0.3 to VDD+0.3

6

Unit

℃

℃

V

V

KV

‧DC/AC Characteristics:(Test condition at room temperature=25℃)

uA

Min. Typ. Max. Unit

V

2.0

2.4

V

V

2.2

uA

0

0.8

-

-

5.5

5.5

2.4

0.2 VDD

1.0 VDD

-

mA

mA

-

mS

mS

mS

mS

ohm

-

-

2.3

20

25

2.0

2.0

2.5

2.5

-

-

8

-4

125

15.6

32

16

30K

Symbol

VDD

VDD

VREG

Test Condition

Internal Regulator disable

Internal Regulator enable

VDD

=3.0V

8-Keys

16-Keys

Regulator enable

Regulator disable

Regulator enable

Regulator disable

Regulator enable

Regulator disable

Input Low Voltage

Input High Voltage

VDD=3V, VOL=0.6V

VDD=3V, VOH=2.4V

VDD=3V, Sampling rate 8Hz

VDD=3V, Sampling rate 64Hz

VDD=3V, set 16-keys

VDD=3V, set 8-keys

RPH VDD=3V,

Parameter

Operating Voltage

Operating Voltage

Internal Regulator Output

Operating Current

(no load)

Stand-by Current

(VDD=3.0V)

Input Ports

Input Ports

Output Port Sink Current

Output Port Source Current

Wake-up Response Time

(at sleep mode)

Output Response Time

(at operation)

Input Pin Pull-high Resistor

(REGEN, SLSERT, ENSLP,

A0~A2)

Input Pin Pull-low Resistor

(TEST)

IOP

ISD

VIL

VIH

IOL

IOH

TWU

TR

RPL VDD=3V,

30K

ohm

09’/10/30 Page 6 of 19 Ver : 1.0

�

Preliminary

TTP229

TonTouchTM

FUNCTION DESCRIPTION

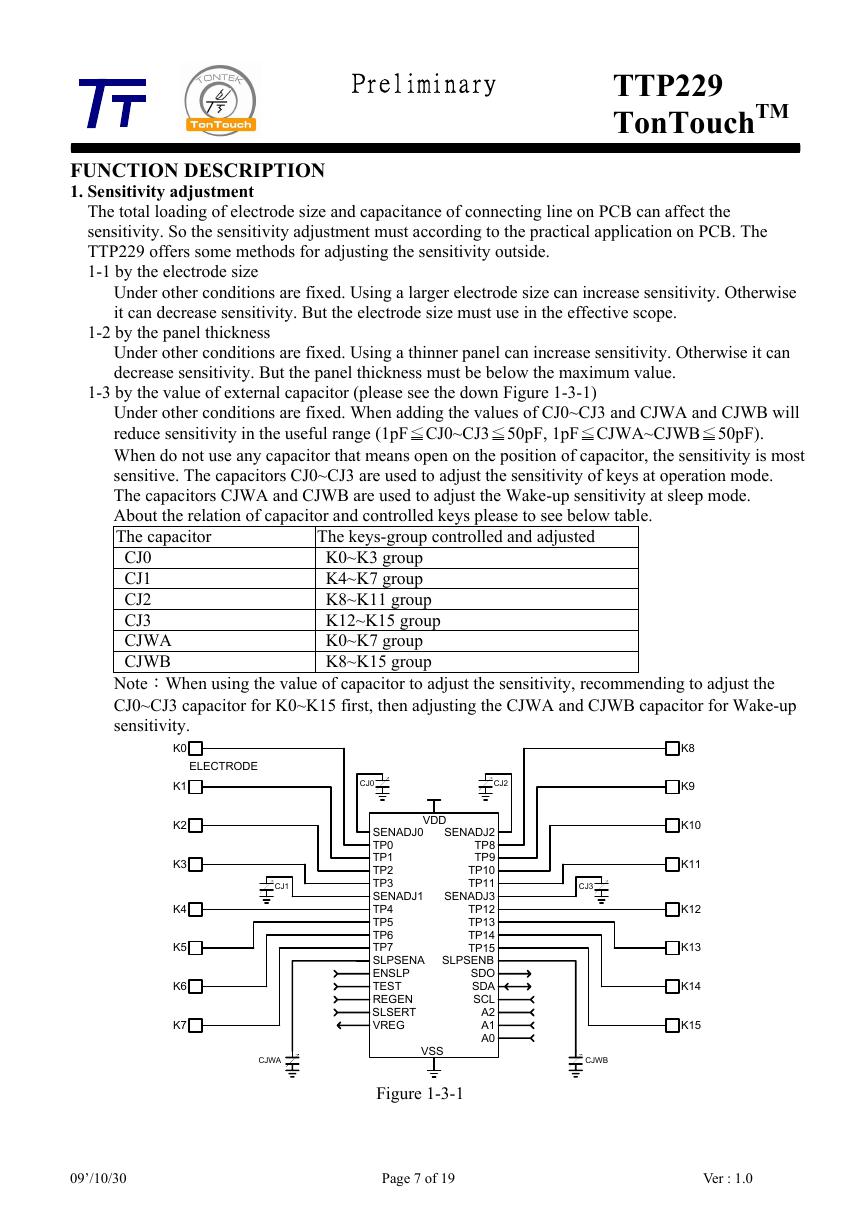

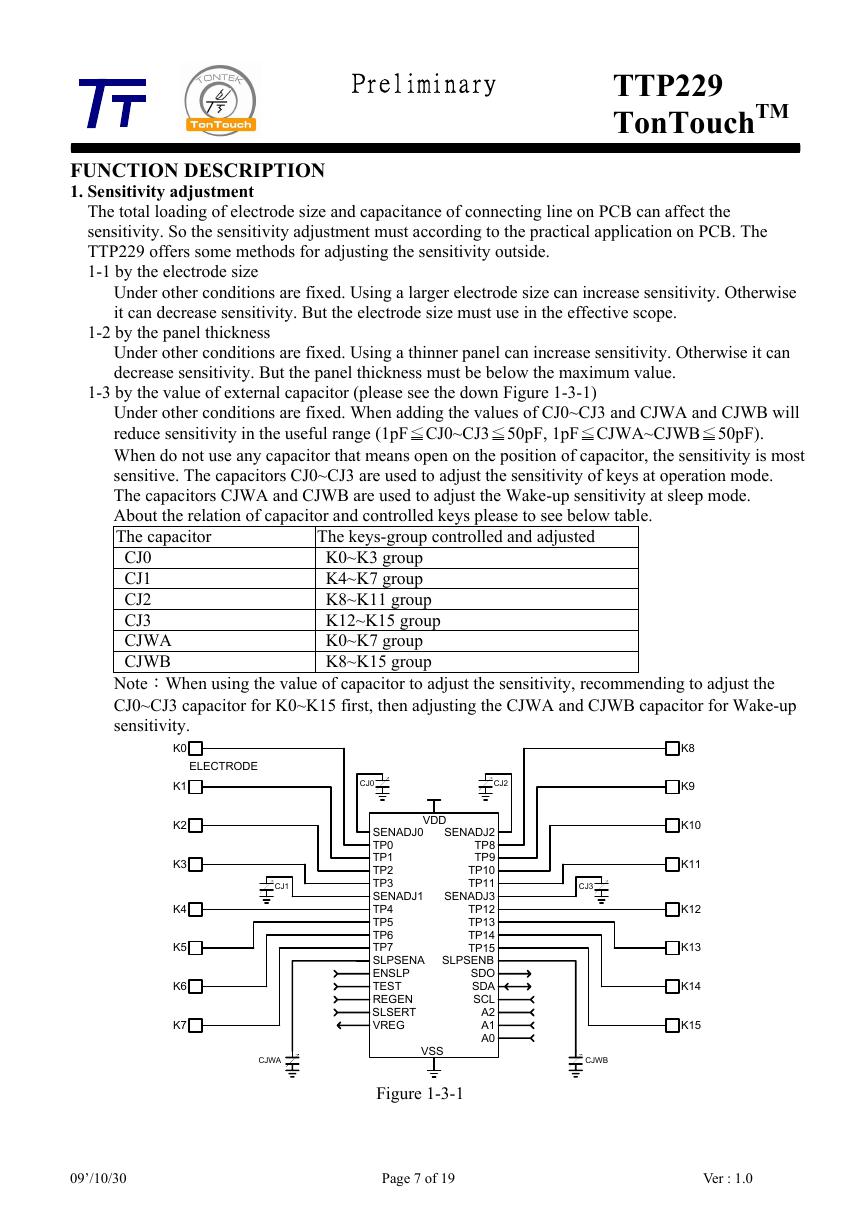

1. Sensitivity adjustment

The total loading of electrode size and capacitance of connecting line on PCB can affect the

sensitivity. So the sensitivity adjustment must according to the practical application on PCB. The

TTP229 offers some methods for adjusting the sensitivity outside.

1-1 by the electrode size

Under other conditions are fixed. Using a larger electrode size can increase sensitivity. Otherwise

it can decrease sensitivity. But the electrode size must use in the effective scope.

1-2 by the panel thickness

Under other conditions are fixed. Using a thinner panel can increase sensitivity. Otherwise it can

decrease sensitivity. But the panel thickness must be below the maximum value.

1-3 by the value of external capacitor (please see the down Figure 1-3-1)

Under other conditions are fixed. When adding the values of CJ0~CJ3 and CJWA and CJWB will

reduce sensitivity in the useful range (1pF≦CJ0~CJ3≦50pF, 1pF≦CJWA~CJWB≦50pF).

When do not use any capacitor that means open on the position of capacitor, the sensitivity is most

sensitive. The capacitors CJ0~CJ3 are used to adjust the sensitivity of keys at operation mode.

The capacitors CJWA and CJWB are used to adjust the Wake-up sensitivity at sleep mode.

About the relation of capacitor and controlled keys please to see below table.

The capacitor

CJ0

CJ1

CJ2

CJ3

CJWA

CJWB

Note:When using the value of capacitor to adjust the sensitivity, recommending to adjust the

CJ0~CJ3 capacitor for K0~K15 first, then adjusting the CJWA and CJWB capacitor for Wake-up

sensitivity.

K0

The keys-group controlled and adjusted

K0~K3 group

K4~K7 group

K8~K11 group

K12~K15 group

K0~K7 group

K8~K15 group

K8

K1

K2

K3

K4

K5

K6

K7

ELECTRODE

CJ0

CJ2

VDD

SENADJ0

TP0

TP1

TP2

TP3

SENADJ1

TP4

TP5

TP6

TP7

SLPSENA

ENSLP

TEST

REGEN

SLSERT

VREG

SENADJ2

TP8

TP9

TP10

TP11

SENADJ3

TP12

TP13

TP14

TP15

SLPSENB

SDO

SDA

SCL

A2

A1

A0

VSS

CJ1

CJWA

Figure 1-3-1

CJ3

K9

K10

K11

K12

K13

K14

K15

CJWB

09’/10/30 Page 7 of 19 Ver : 1.0

�

Preliminary

TTP229

TonTouchTM

2. Input keys number select

3. Output mode

The TTP229 has 8 keys input mode and 16 keys input mode. These modes are selected via high-value

resistor connected to the TP2(KYSEL) pin to VSS, or not. The default that TP2(KYSEL) pin is not used

resistor connected to VSS is selected 8 keys input mode. Another is selected 16 keys input mode that

has used a high-value resistor connected to VSS.

The TTP229 has 8 pins direct output mode and two kinds of serial output interface mode. The output

of 16 keys input mode only offer serial output interface. The 8 keys input mode has two kinds of

output that 8 pins direct output and serial output interface. The 8 pins direct output only use at 8 keys

input mode. The two kinds of serial output interface mode include I2C-bus slave interface and 2-wires

serial interface. The two modes use common clock input pin that is SCL pin. At the same time only

one mode can work. They are selected by the SLSERT pin. The default that the SLSERT pin is

floating or connected to VDD is set 2-wires serial interface. When the SLSERT pin is connected to

VSS, it is set I2C-bus slave interface.

3-1 At the 8 pins direct output mode, the TTP229 has two kinds of output type that they are CMOS

type output and OD (Open Drain) type output. These are selected by the TP0(OPDEN) pin. The CMOS

type output is default that the TP0(OPDEN) pin is not used any component to VSS. When the

TP0(OPDEN) pin is used a high-value resistor connected to VSS, it is selected OD type output.

3-2 When selecting 8 pins direct CMOS output mode, the output channels can be set active-high or

active-low by TP1(SAHL) pin. The default that the TP1(SAHL) pin is not used a high-value resistor, it is

set active-high. When the TP1(SAHL) pin has a high-value resistor connected to VSS, it is set

active-low.

3-3 At 8 pins direct OD output mode, it has OD (Open Drain) or OC (Open collector) output mode to

be selected by the TP1(SAHL) pin. The TP1(SAHL) pin has a high-value resistor connected to VSS, it is

selected OC mode. Another it is selected OD mode that does not has a resistor. The default is OD

mode. The states of OD mode are floating and active-low. And the states of OC mode are floating and

active-high.

Note:the output pins have Diode protective circuit in the chip. So when it selected OD or OC mode.

Do not propose to connect other device that uses the different voltage. That avoids to occurring the

leakage current in the system.

3-4 The 2-wires serial output interface mode can be selected by the SLSERT pin that it has to be

floated or connected to VDD. At the mode the SDO pin is data output pin, the SCL is clock input pin,

both can be set active-high and active-low by TP1(SAHL) pin. The default is active-low that TP1(SAHL)

pin is not used resistor connected to VSS. Another it is active-high that is used a high-value resistor

connected to VSS.

The 2-wires serial mode supports always polling data for other device on the system. Or other device

can wait that TTP229 outputs the data valid (DV) signal by the SDO pin, and it can give the clock

signal to TTP229 SCL pin and get the key data from SDO pin.

The TTP229 2-wires serial interface supports a timeout mechanism for SCL pin. If the SCL pin has no

signal edge change over 2ms, the 2-wires serial interface will reset itself and return to stand-by state.

09’/10/30 Page 8 of 19 Ver : 1.0

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf