www.ti.com

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

3.3-V CAN TRANSCEIVERS

Check for Samples: SN65HVD230, SN65HVD231, SN65HVD232

Industrial Automation

APPLICATIONS

• Motor Control

•

• Basestation Control and Status

• Robotics

• Automotive

• UPS Control

1FEATURES

2• Operates With a 3.3-V Supply

• Low Power Replacement for the PCA82C250

Footprint

• Bus/Pin ESD Protection Exceeds 16 kV HBM

• High Input Impedance Allows for 120 Nodes on

a Bus

• Controlled Driver Output Transition Times for

Improved Signal Quality on the SN65HVD230

and SN65HVD231

• Unpowered Node Does Not Disturb the Bus

• Compatible With the Requirements of the ISO

11898 Standard

• Low-Current SN65HVD230 Standby Mode

370 μA Typical

• Low-Current SN65HVD231 Sleep Mode 40 nA

Typical

• Designed for Signaling Rates(1) up to 1

Megabit/Second (Mbps)

• Thermal Shutdown Protection

• Open-Circuit Fail-Safe Design

• Glitch-Free Power-Up and Power-Down

(1)

Protection for Hot-Plugging Applications

The signaling rate of a line is the number of voltage

transitions that are made per second expressed in the units

bps (bits per second).

LOGIC DIAGRAM (POSITIVE LOGIC)

1

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas

Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

2TMS320Lx240x is a trademark of Texas Instruments.

PRODUCTION DATA information is current as of publication date.

Products conform to specifications per the terms of

the Texas

Instruments standard warranty. Production processing does not

necessarily include testing of all parameters.

© 2001–2011, Texas Instruments Incorporated

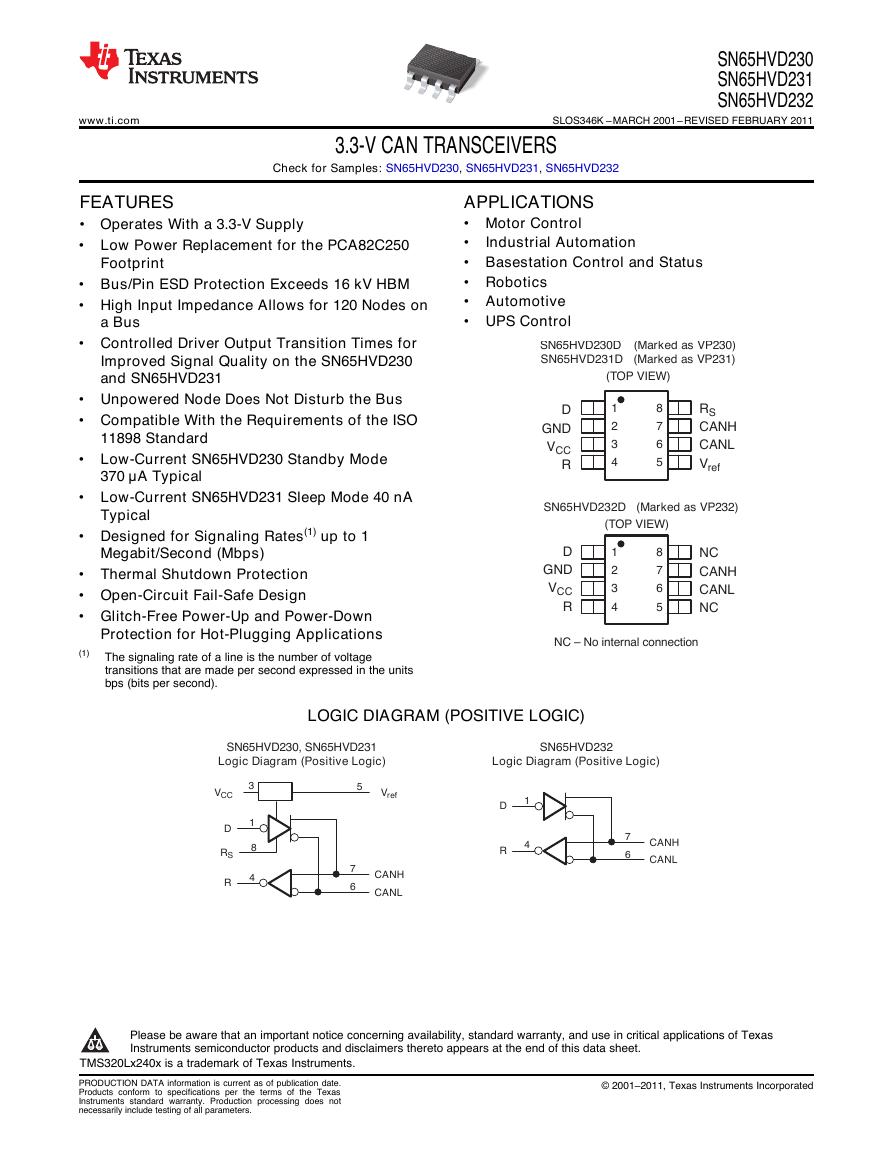

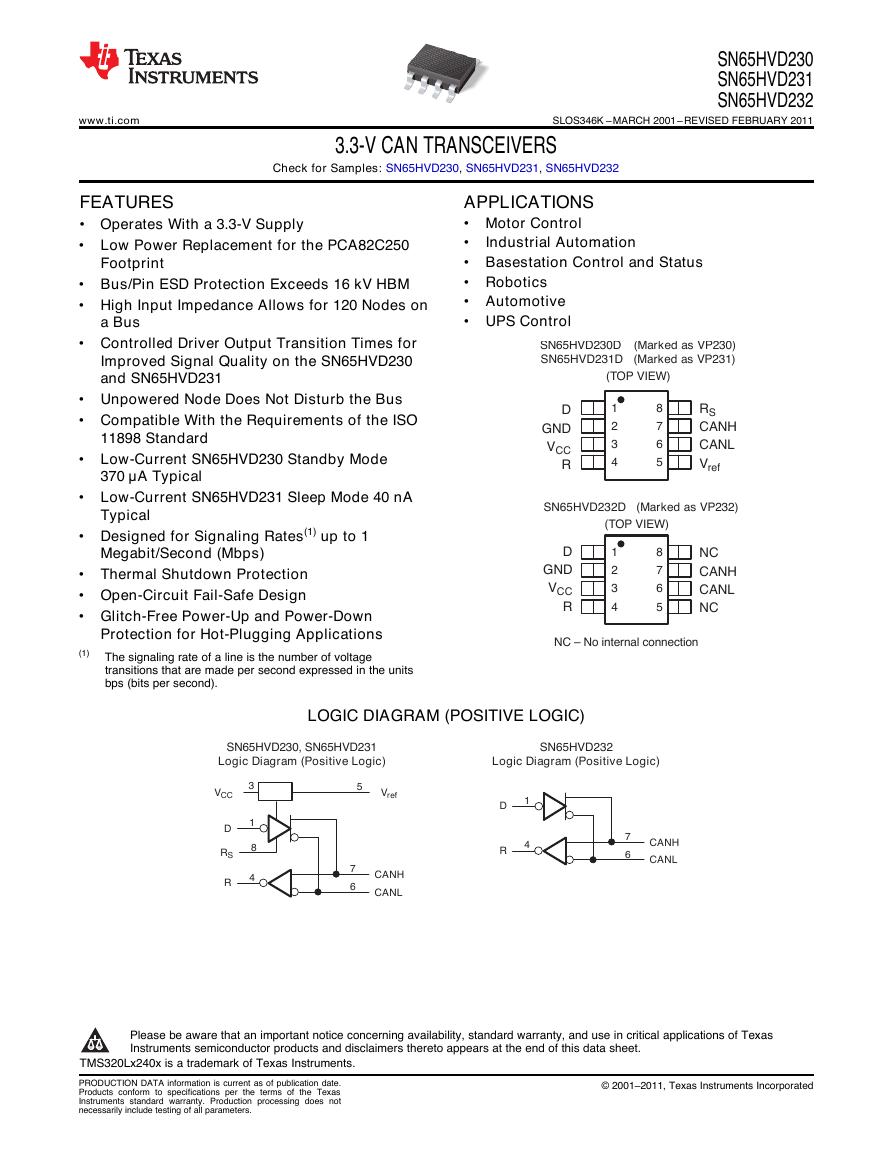

DGNDVCCRRSCANHCANLVrefSN65HVD230D (Marked as VP230)SN65HVD231D (Marked as VP231)(TOP VIEW)12348765NC – No internal connectionDGNDVCCRNCCANHCANLNCSN65HVD232D (Marked as VP232)(TOP VIEW)12348765CANLCANHRD1476SN65HVD230, SN65HVD231Logic Diagram (Positive Logic)RS8Vref53VCCCANLCANHRD1476SN65HVD232Logic Diagram (Positive Logic)�

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

www.ti.com

These devices have limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam

during storage or handling to prevent electrostatic damage to the MOS gates.

these devices feature cross-wire protection,

DESCRIPTION

The SN65HVD230, SN65HVD231, and SN65HVD232 controller area network (CAN) transceivers are designed

for use with the Texas Instruments TMS320Lx240x™

; 3.3-V DSPs with CAN controllers, or with

equivalent devices. They are intended for use in applications employing the CAN serial communication physical

layer in accordance with the ISO 11898 standard. Each CAN transceiver is designed to provide differential

transmit capability to the bus and differential receive capability to a CAN controller at speeds up to 1 Mbps.

Designed for operation in especially-harsh environments,

loss-of-ground and overvoltage protection, overtemperature protection, as well as wide common-mode range.

The transceiver interfaces the single-ended CAN controller with the differential CAN bus found in industrial,

building automation, and automotive applications. It operates over a -2-V to 7-V common-mode range on the

bus, and it can withstand common-mode transients of ±25 V.

On the SN65HVD230 and SN65HVD231, pin 8 provides three different modes of operation: high-speed, slope

control, and low-power modes. The high-speed mode of operation is selected by connecting pin 8 to ground,

allowing the transmitter output transistors to switch on and off as fast as possible with no limitation on the rise

and fall slopes. The rise and fall slopes can be adjusted by connecting a resistor to ground at pin 8, since the

slope is proportional to the pin's output current. This slope control is implemented with external resistor values of

10 kΩ, to achieve a 15-V/μs slew rate, to 100 kΩ, to achieve a 2-V/μs slew rate. See the Application Information

section of this data sheet.

The circuit of the SN65HVD230 enters a low-current standby mode during which the driver is switched off and

the receiver remains active if a high logic level is applied to pin 8. The DSP controller reverses this low-current

standby mode when a dominant state (bus differential voltage > 900 mV typical) occurs on the bus.

The unique difference between the SN65HVD230 and the SN65HVD231 is that both the driver and the receiver

are switched off in the SN65HVD231 when a high logic level is applied to pin 8 and remain in this sleep mode

until the circuit is reactivated by a low logic level on pin 8.

The Vref pin 5 on the SN65HVD230 and SN65HVD231 is available as a VCC/2 voltage reference.

The SN65HVD232 is a basic CAN transceiver with no added options; pins 5 and 8 are NC, no connection.

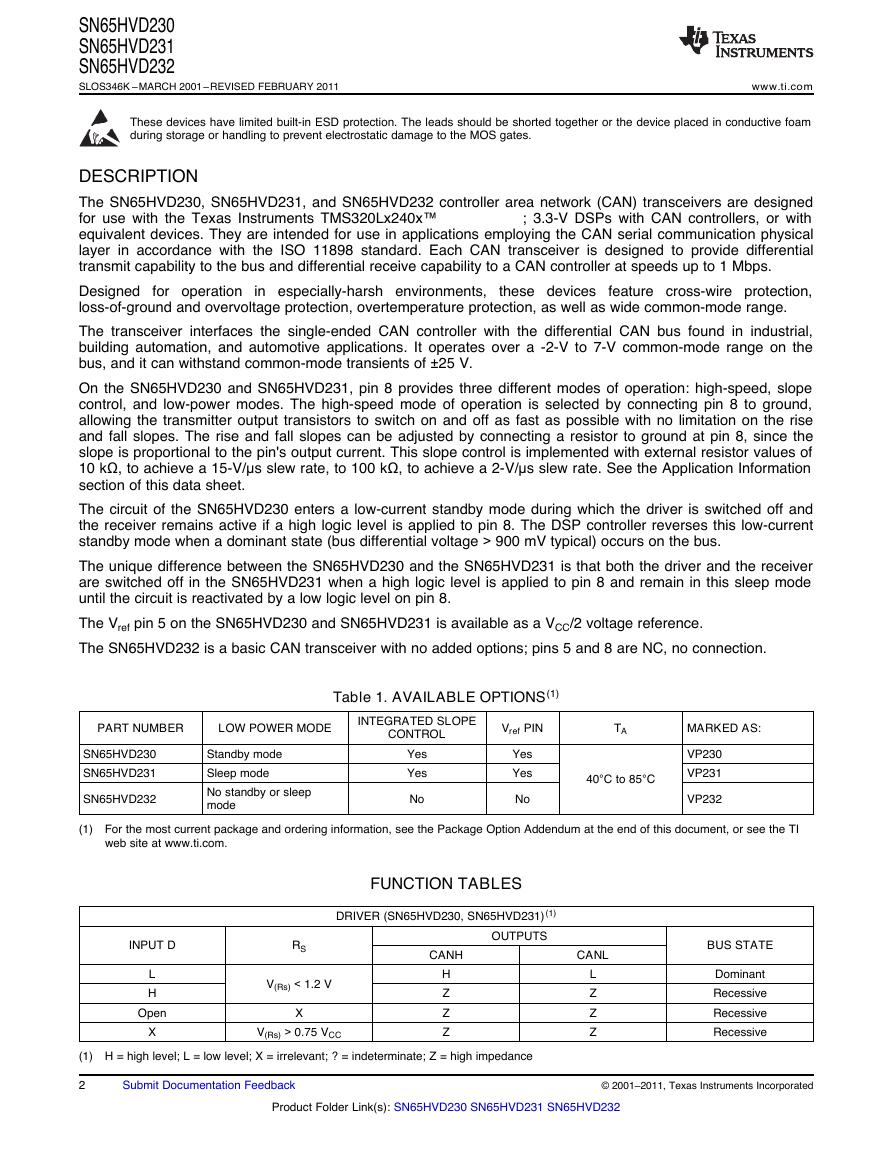

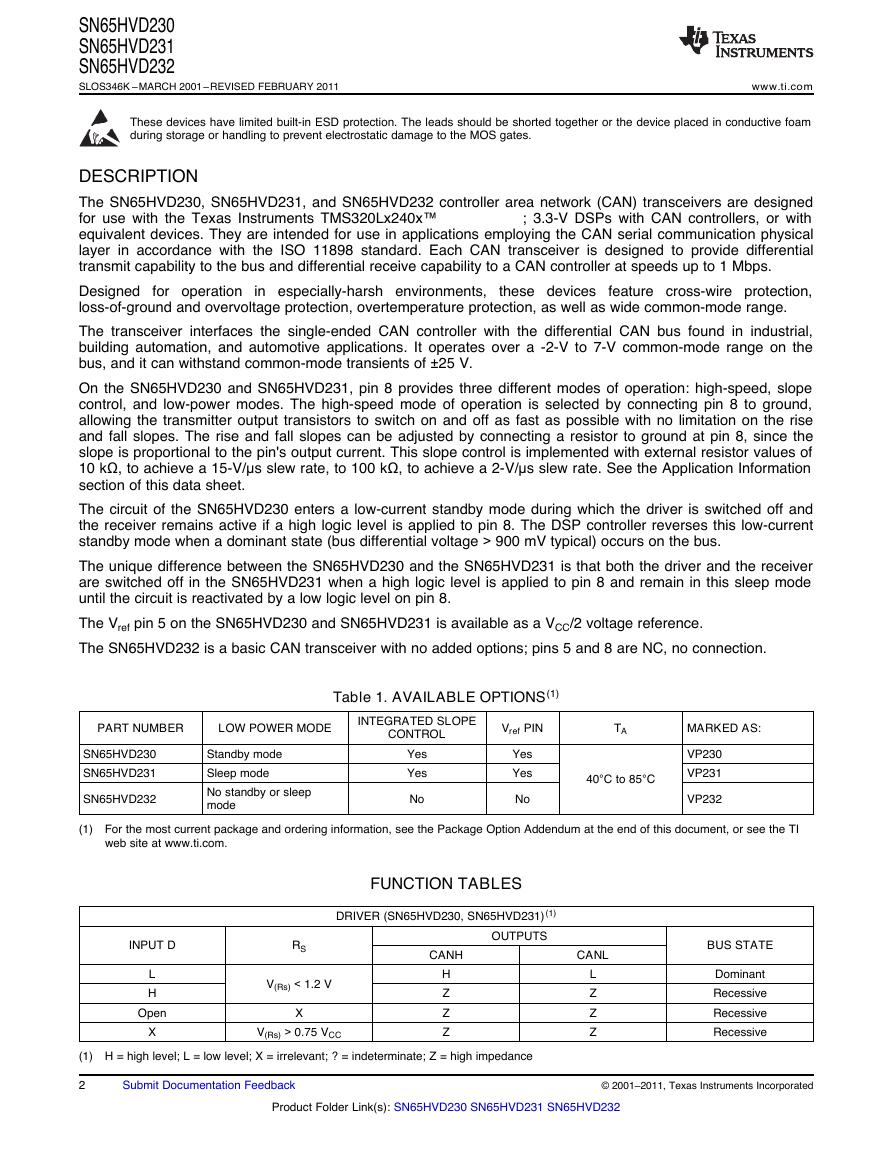

Table 1. AVAILABLE OPTIONS(1)

PART NUMBER

LOW POWER MODE

INTEGRATED SLOPE

CONTROL

Vref PIN

TA

MARKED AS:

SN65HVD230

SN65HVD231

SN65HVD232

Standby mode

Sleep mode

No standby or sleep

mode

Yes

Yes

No

Yes

Yes

No

40°C to 85°C

VP230

VP231

VP232

(1) For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI

web site at www.ti.com.

FUNCTION TABLES

DRIVER (SN65HVD230, SN65HVD231)(1)

INPUT D

RS

OUTPUTS

CANH

CANL

L

H

Open

X

V(Rs) < 1.2 V

X

V(Rs) > 0.75 VCC

H

Z

Z

Z

L

Z

Z

Z

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate; Z = high impedance

BUS STATE

Dominant

Recessive

Recessive

Recessive

2

Submit Documentation Feedback

© 2001–2011, Texas Instruments Incorporated

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

�

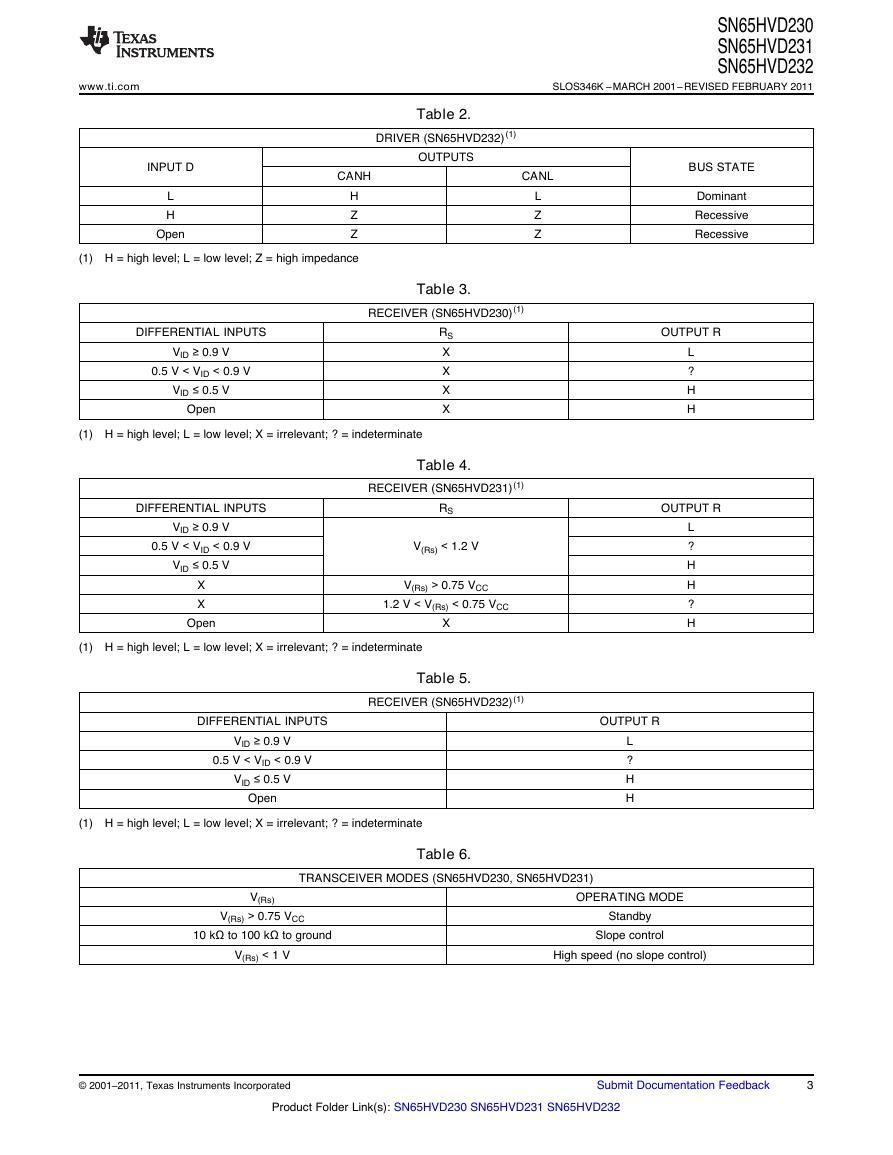

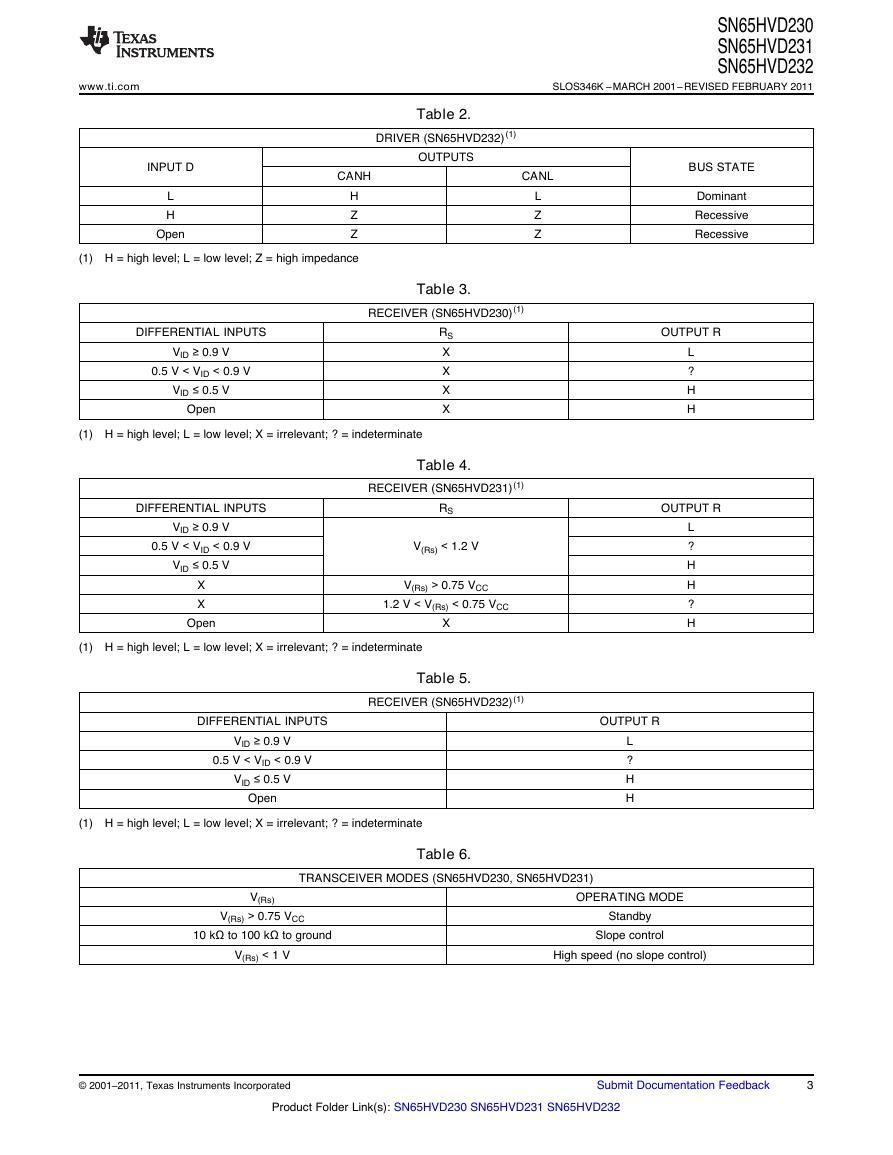

www.ti.com

INPUT D

L

H

Open

Table 2.

DRIVER (SN65HVD232)(1)

OUTPUTS

CANH

H

Z

Z

CANL

L

Z

Z

(1) H = high level; L = low level; Z = high impedance

DIFFERENTIAL INPUTS

VID ≥ 0.9 V

0.5 V < VID < 0.9 V

VID ≤ 0.5 V

Open

Table 3.

RECEIVER (SN65HVD230)(1)

RS

X

X

X

X

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate

DIFFERENTIAL INPUTS

VID ≥ 0.9 V

0.5 V < VID < 0.9 V

VID ≤ 0.5 V

X

X

Open

Table 4.

RECEIVER (SN65HVD231)(1)

RS

V(Rs) < 1.2 V

V(Rs) > 0.75 VCC

1.2 V < V(Rs) < 0.75 VCC

X

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

BUS STATE

Dominant

Recessive

Recessive

OUTPUT R

L

?

H

H

OUTPUT R

L

?

H

H

?

H

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate

Table 5.

RECEIVER (SN65HVD232)(1)

DIFFERENTIAL INPUTS

VID ≥ 0.9 V

0.5 V < VID < 0.9 V

VID ≤ 0.5 V

Open

(1) H = high level; L = low level; X = irrelevant; ? = indeterminate

OUTPUT R

L

?

H

H

Table 6.

TRANSCEIVER MODES (SN65HVD230, SN65HVD231)

V(Rs)

V(Rs) > 0.75 VCC

10 kΩ to 100 kΩ to ground

V(Rs) < 1 V

OPERATING MODE

Standby

Slope control

High speed (no slope control)

© 2001–2011, Texas Instruments Incorporated

Submit Documentation Feedback

3

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

�

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

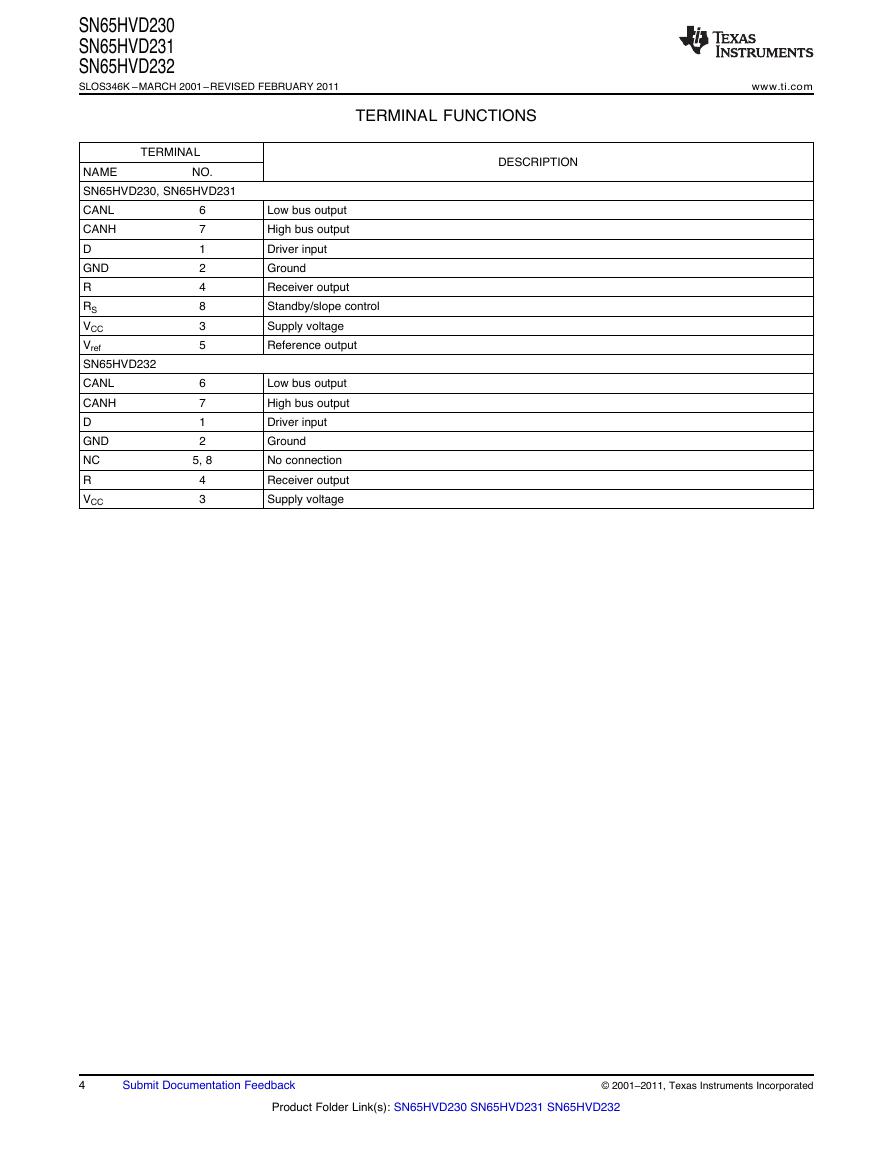

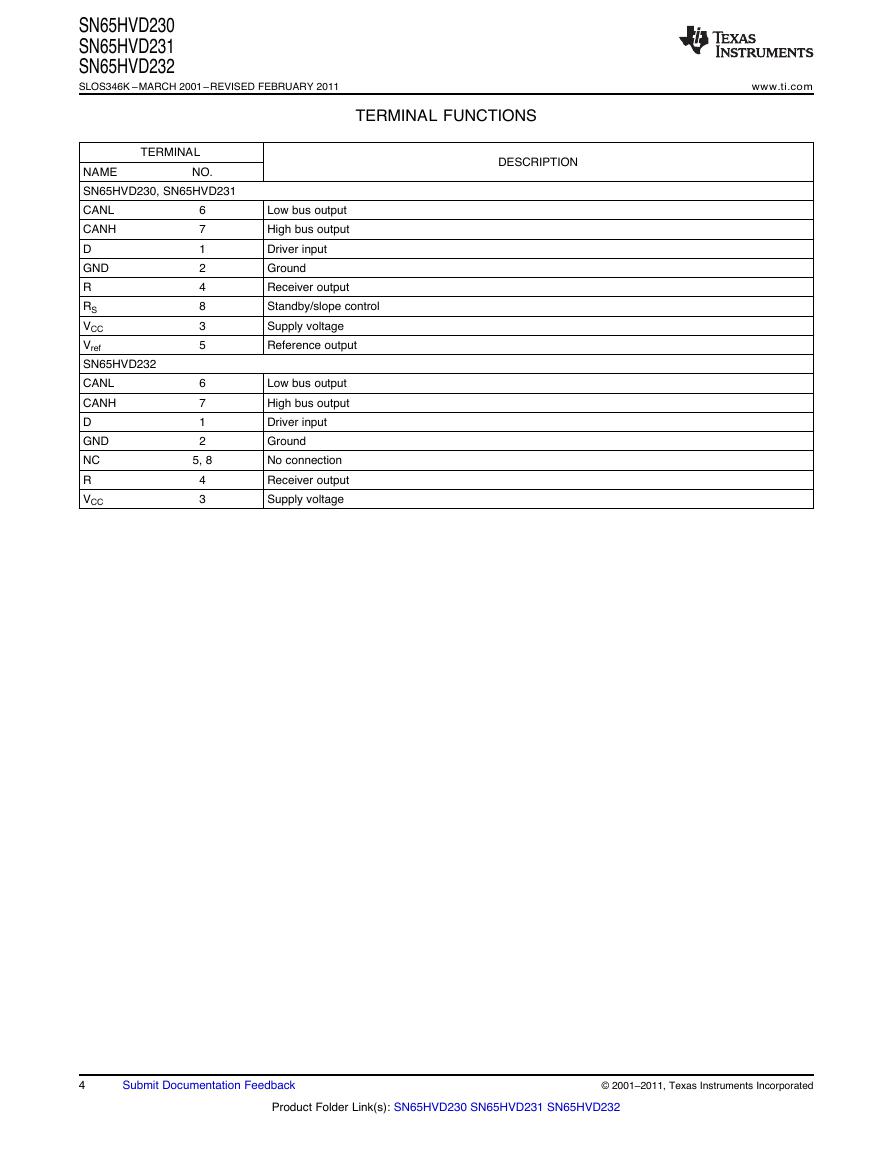

TERMINAL

TERMINAL FUNCTIONS

DESCRIPTION

www.ti.com

NO.

6

7

1

2

4

8

3

5

NAME

SN65HVD230, SN65HVD231

CANL

CANH

D

GND

R

RS

VCC

Vref

SN65HVD232

CANL

CANH

D

GND

NC

R

VCC

6

7

1

2

5, 8

4

3

Low bus output

High bus output

Driver input

Ground

Receiver output

Standby/slope control

Supply voltage

Reference output

Low bus output

High bus output

Driver input

Ground

No connection

Receiver output

Supply voltage

4

Submit Documentation Feedback

© 2001–2011, Texas Instruments Incorporated

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

�

www.ti.com

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

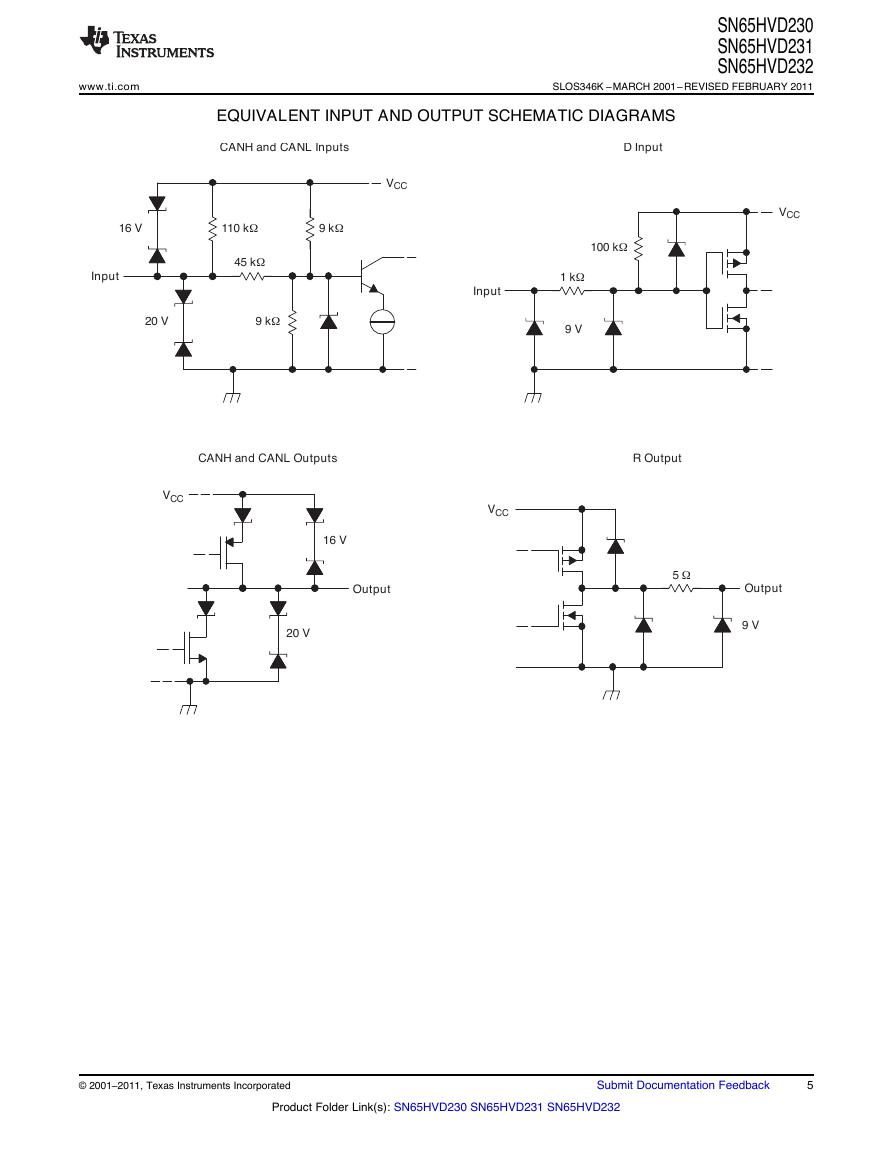

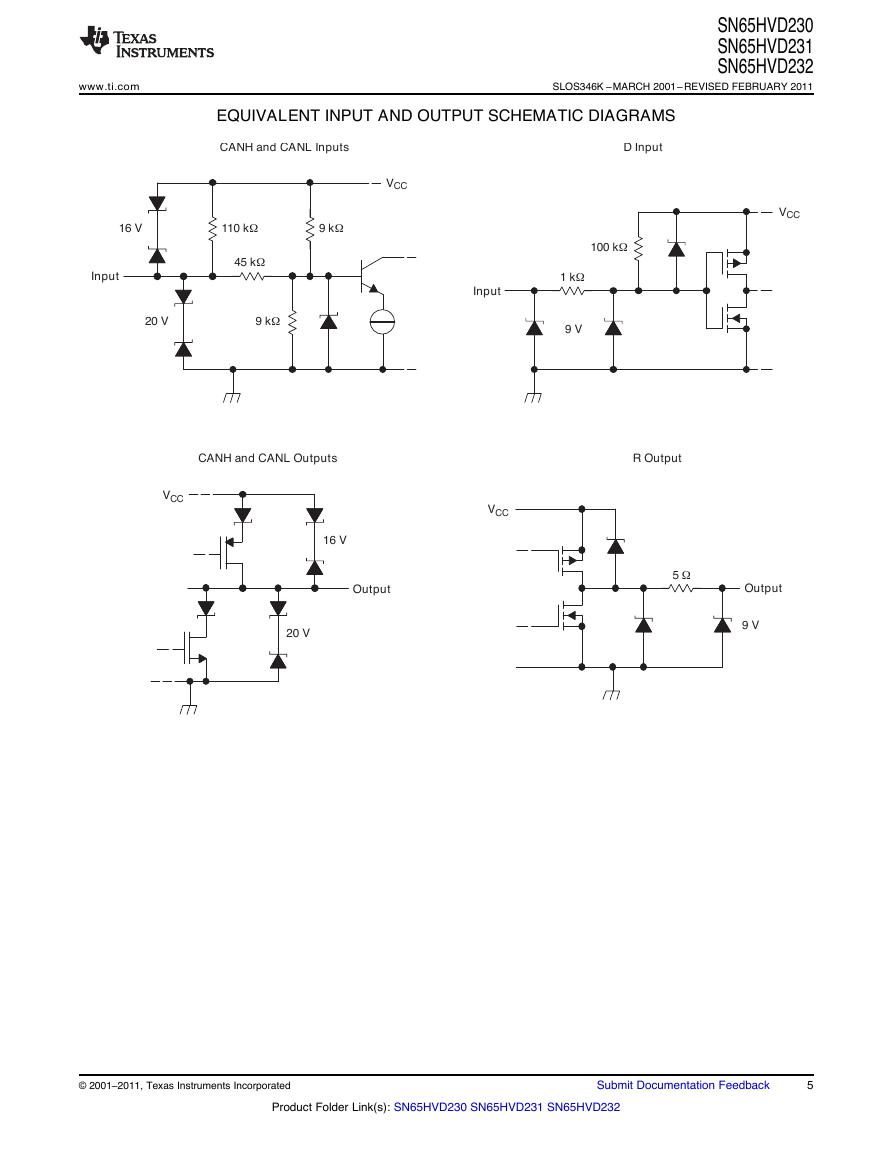

EQUIVALENT INPUT AND OUTPUT SCHEMATIC DIAGRAMS

© 2001–2011, Texas Instruments Incorporated

Submit Documentation Feedback

5

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

VCCD Input1 kW9 VInput100 kWVCCOutput16 VCANH and CANL Outputs20 VVCC5 W9 VOutputR OutputVCCInput16 VCANH and CANL Inputs20 V110 kW45 kW9 kW9 kW�

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

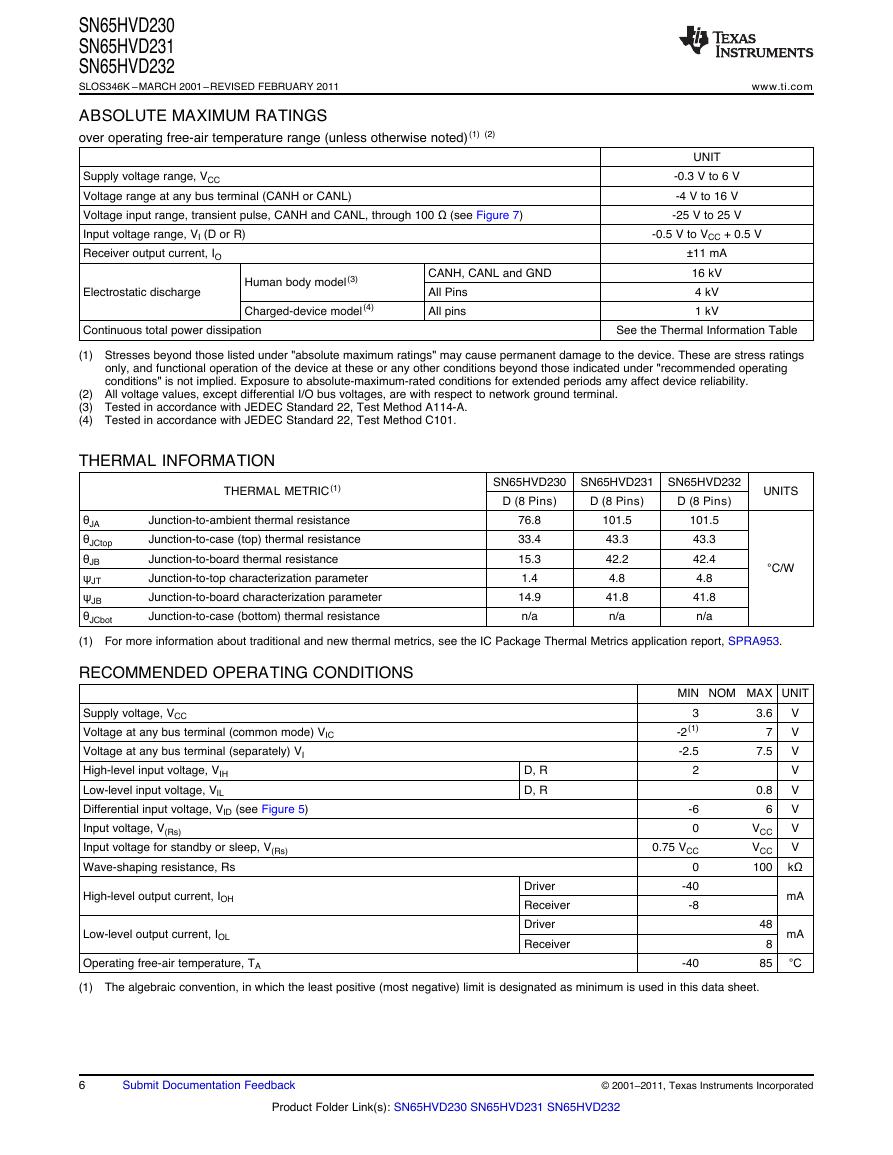

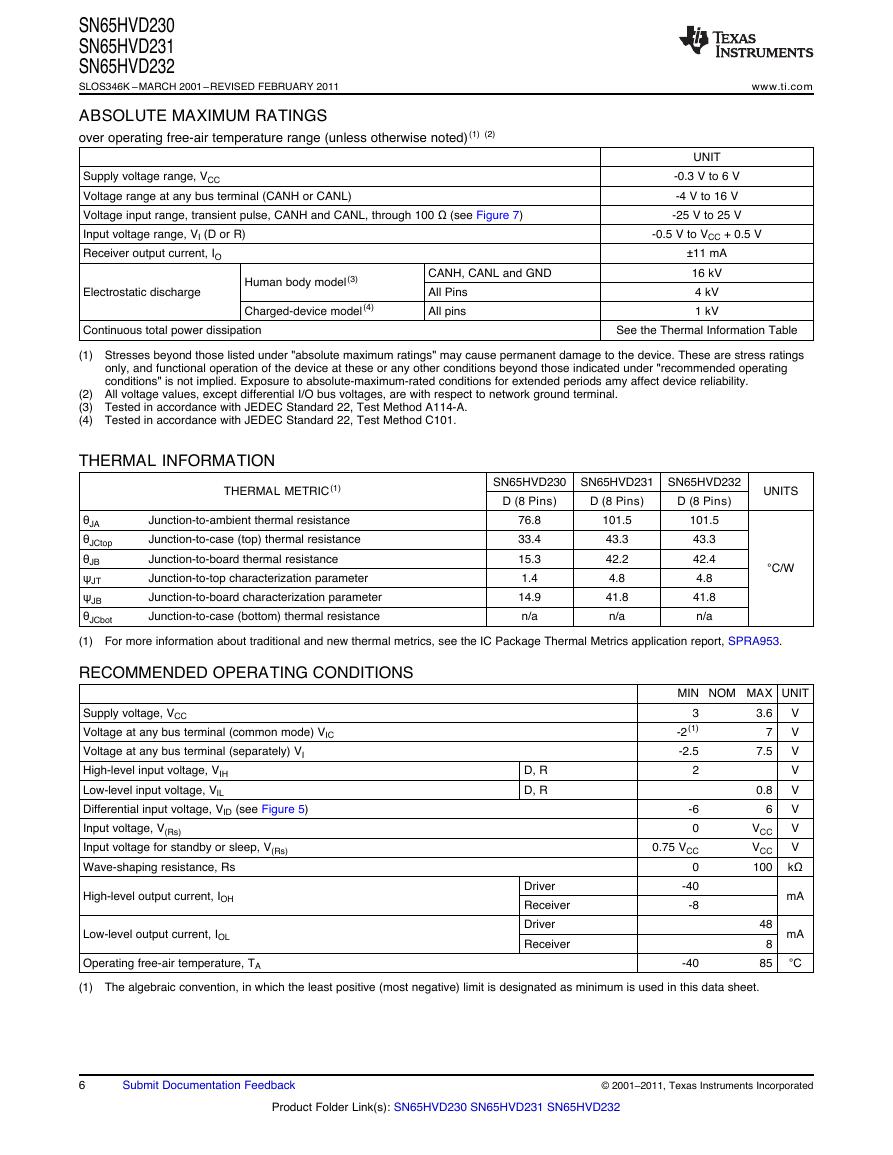

ABSOLUTE MAXIMUM RATINGS

over operating free-air temperature range (unless otherwise noted) (1) (2)

Supply voltage range, VCC

Voltage range at any bus terminal (CANH or CANL)

Voltage input range, transient pulse, CANH and CANL, through 100 Ω (see Figure 7)

Input voltage range, VI (D or R)

Receiver output current, IO

Electrostatic discharge

Human body model (3)

Charged-device model (4)

CANH, CANL and GND

All Pins

All pins

www.ti.com

UNIT

-0.3 V to 6 V

-4 V to 16 V

-25 V to 25 V

-0.5 V to VCC + 0.5 V

±11 mA

16 kV

4 kV

1 kV

Continuous total power dissipation

See the Thermal Information Table

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings

only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating

conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods amy affect device reliability.

(2) All voltage values, except differential I/O bus voltages, are with respect to network ground terminal.

(3) Tested in accordance with JEDEC Standard 22, Test Method A114-A.

(4) Tested in accordance with JEDEC Standard 22, Test Method C101.

THERMAL INFORMATION

THERMAL METRIC(1)

θJA

θJCtop

θJB

ψJT

ψJB

θJCbot

Junction-to-ambient thermal resistance

Junction-to-case (top) thermal resistance

Junction-to-board thermal resistance

Junction-to-top characterization parameter

Junction-to-board characterization parameter

Junction-to-case (bottom) thermal resistance

SN65HVD230 SN65HVD231 SN65HVD232

D (8 Pins)

D (8 Pins)

D (8 Pins)

UNITS

76.8

33.4

15.3

1.4

14.9

n/a

101.5

43.3

42.2

4.8

41.8

n/a

101.5

43.3

42.4

4.8

41.8

n/a

°C/W

(1) For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

RECOMMENDED OPERATING CONDITIONS

Supply voltage, VCC

Voltage at any bus terminal (common mode) VIC

Voltage at any bus terminal (separately) VI

High-level input voltage, VIH

Low-level input voltage, VIL

Differential input voltage, VID (see Figure 5)

Input voltage, V(Rs)

Input voltage for standby or sleep, V(Rs)

Wave-shaping resistance, Rs

High-level output current, IOH

Low-level output current, IOL

Operating free-air temperature, TA

MIN NOM MAX UNIT

3

-2 (1)

-2.5

2

-6

0

0.75 VCC

0

-40

-8

-40

3.6

7

7.5

0.8

6

VCC

VCC

100

48

8

85

V

V

V

V

V

V

V

V

kΩ

mA

mA

°C

D, R

D, R

Driver

Receiver

Driver

Receiver

(1) The algebraic convention, in which the least positive (most negative) limit is designated as minimum is used in this data sheet.

6

Submit Documentation Feedback

© 2001–2011, Texas Instruments Incorporated

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

�

www.ti.com

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

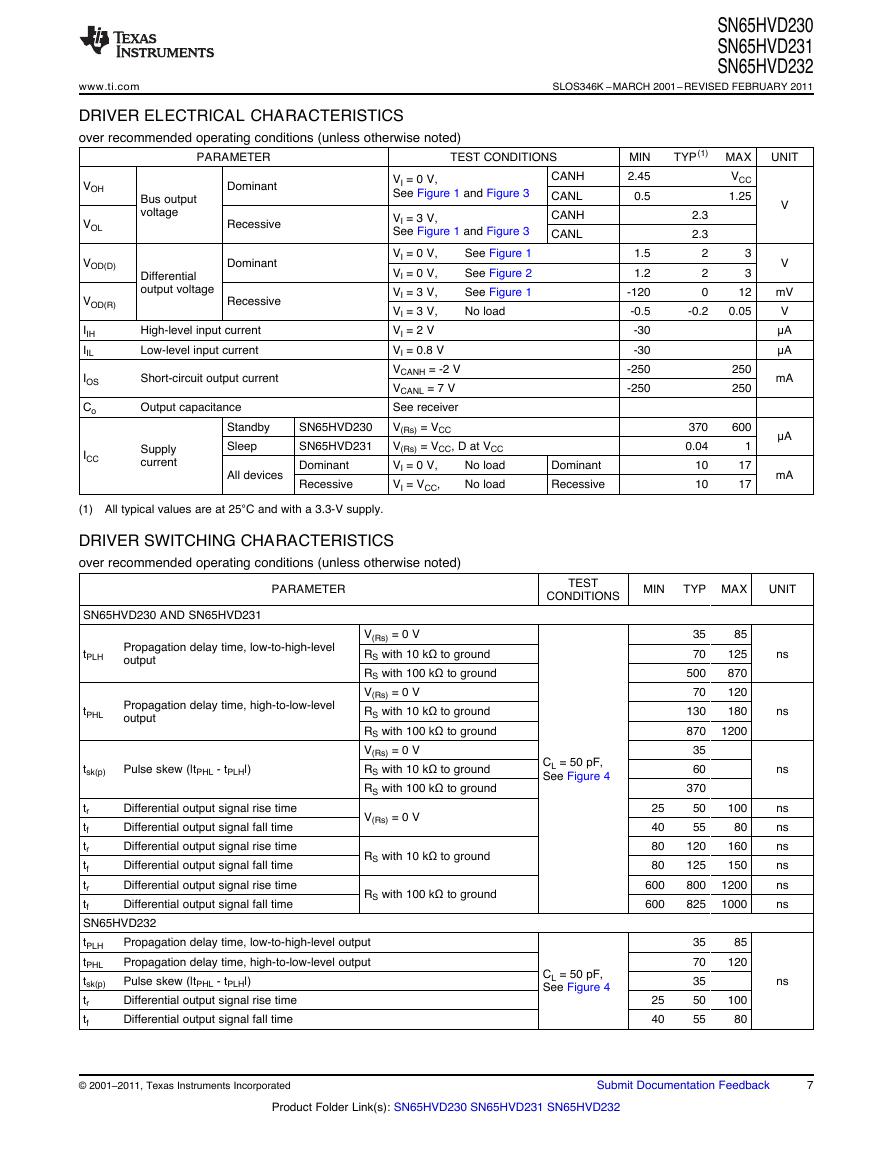

DRIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAMETER

TEST CONDITIONS

VOH

VOL

VOD(D)

VOD(R)

IIH

IIL

IOS

Co

ICC

Bus output

voltage

Differential

output voltage

Dominant

Recessive

Dominant

Recessive

High-level input current

Low-level input current

Short-circuit output current

Output capacitance

Supply

current

Standby

Sleep

All devices

SN65HVD230

SN65HVD231

Dominant

Recessive

VI = 0 V,

See Figure 1 and Figure 3

VI = 3 V,

See Figure 1 and Figure 3

See Figure 1

See Figure 2

See Figure 1

No load

VI = 0 V,

VI = 0 V,

VI = 3 V,

VI = 3 V,

VI = 2 V

VI = 0.8 V

VCANH = -2 V

VCANL = 7 V

See receiver

V(Rs) = VCC

V(Rs) = VCC, D at VCC

No load

VI = 0 V,

VI = VCC,

No load

CANH

CANL

CANH

CANL

Dominant

Recessive

(1) All typical values are at 25°C and with a 3.3-V supply.

DRIVER SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

MIN

2.45

0.5

1.5

1.2

-120

-0.5

-30

-30

-250

-250

TYP(1) MAX

VCC

1.25

2.3

2.3

2

2

0

-0.2

370

0.04

10

10

3

3

12

0.05

250

250

600

1

17

17

UNIT

V

V

mV

V

μA

μA

mA

μA

mA

PARAMETER

SN65HVD230 AND SN65HVD231

tPLH

Propagation delay time, low-to-high-level

output

tPHL

Propagation delay time, high-to-low-level

output

tsk(p)

Pulse skew (|tPHL - tPLH|)

V(Rs) = 0 V

RS with 10 kΩ to ground

RS with 100 kΩ to ground

V(Rs) = 0 V

RS with 10 kΩ to ground

RS with 100 kΩ to ground

V(Rs) = 0 V

RS with 10 kΩ to ground

RS with 100 kΩ to ground

V(Rs) = 0 V

RS with 10 kΩ to ground

RS with 100 kΩ to ground

TEST

CONDITIONS

MIN

TYP MAX

UNIT

35

70

500

70

130

870

35

60

370

50

55

120

125

800

825

35

70

35

50

55

85

125

870

120

180

1200

100

80

160

150

1200

1000

85

120

100

80

25

40

80

80

600

600

25

40

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

CL = 50 pF,

See Figure 4

CL = 50 pF,

See Figure 4

Differential output signal rise time

Differential output signal fall time

Differential output signal rise time

Differential output signal fall time

Differential output signal rise time

Differential output signal fall time

tr

tf

tr

tf

tr

tf

SN65HVD232

tPLH

tPHL

tsk(p)

tr

tf

Propagation delay time, low-to-high-level output

Propagation delay time, high-to-low-level output

Pulse skew (|tPHL - tPLH|)

Differential output signal rise time

Differential output signal fall time

© 2001–2011, Texas Instruments Incorporated

Submit Documentation Feedback

7

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

�

SN65HVD230

SN65HVD231

SN65HVD232

SLOS346K –MARCH 2001–REVISED FEBRUARY 2011

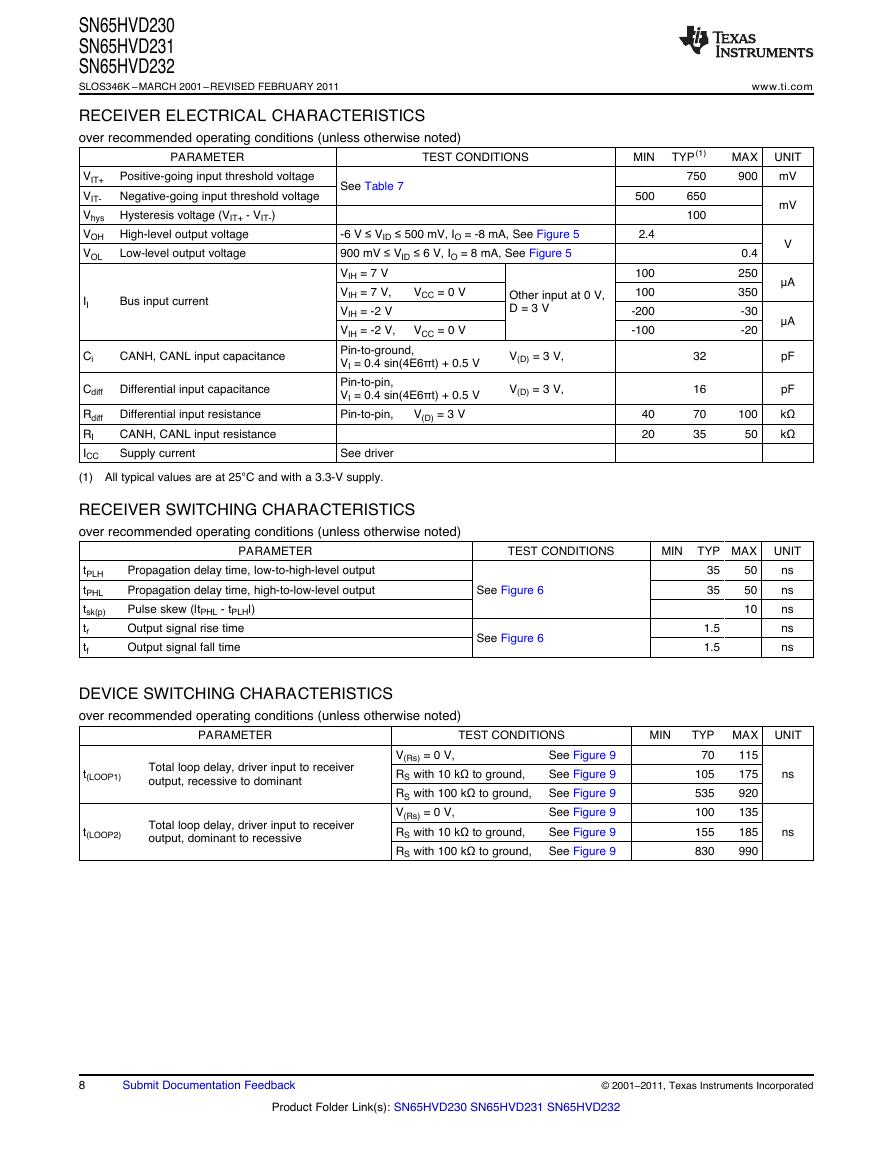

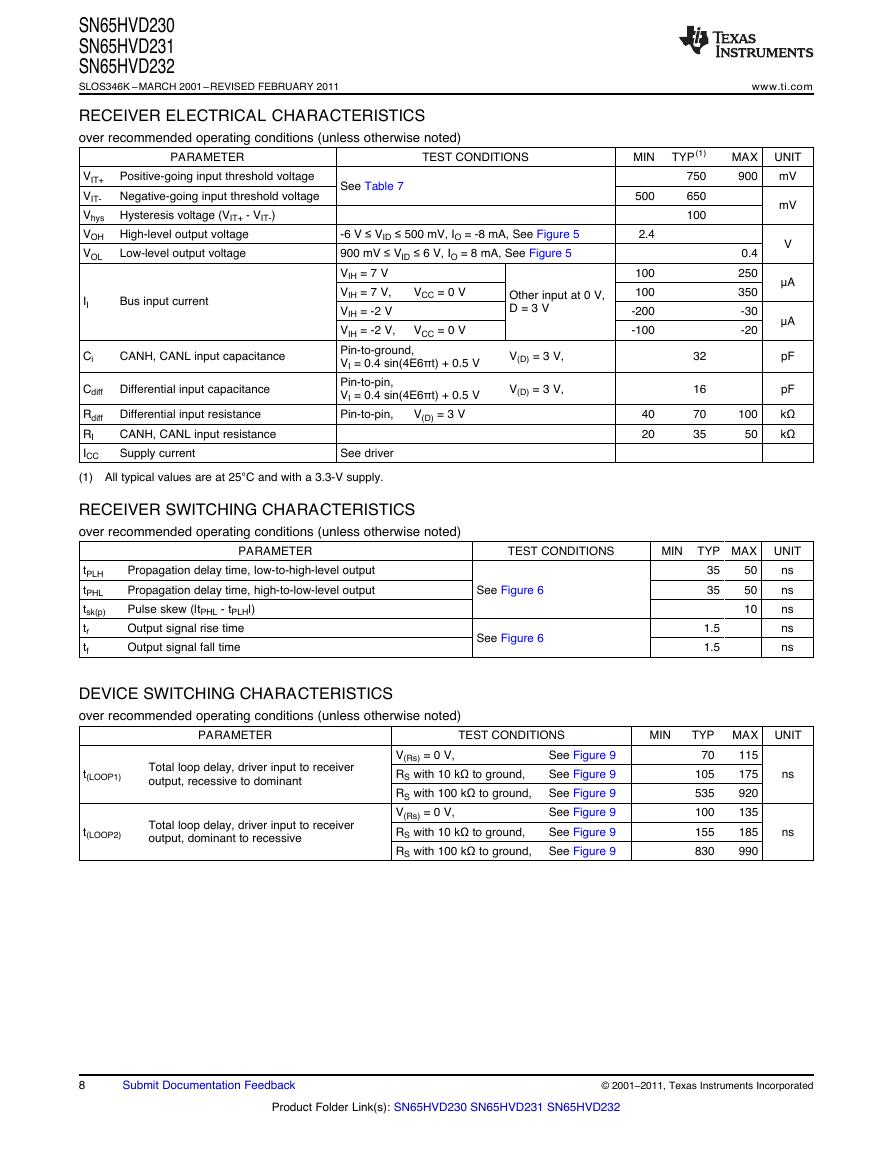

RECEIVER ELECTRICAL CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAMETER

TEST CONDITIONS

Positive-going input threshold voltage

Negative-going input threshold voltage

VIT+

VIT-

Vhys Hysteresis voltage (VIT+ - VIT-)

VOH High-level output voltage

VOL

Low-level output voltage

II

Ci

Bus input current

CANH, CANL input capacitance

Cdiff Differential input capacitance

Rdiff Differential input resistance

RI

ICC

(1) All typical values are at 25°C and with a 3.3-V supply.

CANH, CANL input resistance

Supply current

See driver

See Table 7

-6 V ≤ VID ≤ 500 mV, IO = -8 mA, See Figure 5

900 mV ≤ VID ≤ 6 V, IO = 8 mA, See Figure 5

VIH = 7 V

VIH = 7 V,

VIH = -2 V

VIH = -2 V,

Pin-to-ground,

VI = 0.4 sin(4E6πt) + 0.5 V

Pin-to-pin,

VI = 0.4 sin(4E6πt) + 0.5 V

Pin-to-pin,

V(D) = 3 V,

V(D) = 3 V,

V(D) = 3 V

VCC = 0 V

VCC = 0 V

Other input at 0 V,

D = 3 V

www.ti.com

MAX UNIT

900

mV

mV

V

μA

μA

pF

pF

kΩ

kΩ

0.4

250

350

-30

-20

100

50

MIN

500

2.4

100

100

-200

-100

40

20

TYP(1)

750

650

100

32

16

70

35

RECEIVER SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN TYP MAX UNIT

tPLH

tPHL

tsk(p)

tr

tf

Propagation delay time, low-to-high-level output

Propagation delay time, high-to-low-level output

Pulse skew (|tPHL - tPLH|)

Output signal rise time

Output signal fall time

See Figure 6

See Figure 6

35

35

1.5

1.5

50

50

10

ns

ns

ns

ns

ns

DEVICE SWITCHING CHARACTERISTICS

over recommended operating conditions (unless otherwise noted)

PARAMETER

TEST CONDITIONS

MIN

TYP MAX UNIT

t(LOOP1)

Total loop delay, driver input to receiver

output, recessive to dominant

t(LOOP2)

Total loop delay, driver input to receiver

output, dominant to recessive

V(Rs) = 0 V,

RS with 10 kΩ to ground,

RS with 100 kΩ to ground,

V(Rs) = 0 V,

RS with 10 kΩ to ground,

RS with 100 kΩ to ground,

See Figure 9

See Figure 9

See Figure 9

See Figure 9

See Figure 9

See Figure 9

70

105

535

100

155

830

115

175

920

135

185

990

ns

ns

8

Submit Documentation Feedback

© 2001–2011, Texas Instruments Incorporated

Product Folder Link(s): SN65HVD230 SN65HVD231 SN65HVD232

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf