Vivado 设计流程手册

Vivado 设计流程指导手册——2013.4

Vivado 设计分为 Project Mode 和 Non-project Mode 两种模式,一般简单设计中,我们常

用的是 Project Mode。在本手册中,我们将以一个简单的实验案例,一步一步的完成 Vivado

的整个设计流程。

一、新建工程

1 、 打 开 Vivado 2013.4 开 发 工 具 , 可 通 过 桌 面 快 捷 方 式 或 开 始 菜 单 中 Xilinx Design

Tools->Vivado 2013.4 下的 Vivado 2013.4 打开软件,开启后,软件如下所示:

2、单击上述界面中 Create New Project 图标,弹出新建工程向导,点击 Next。

-

Xilinx 全球合作伙伴

1 / 34

�

Vivado 设计流程手册

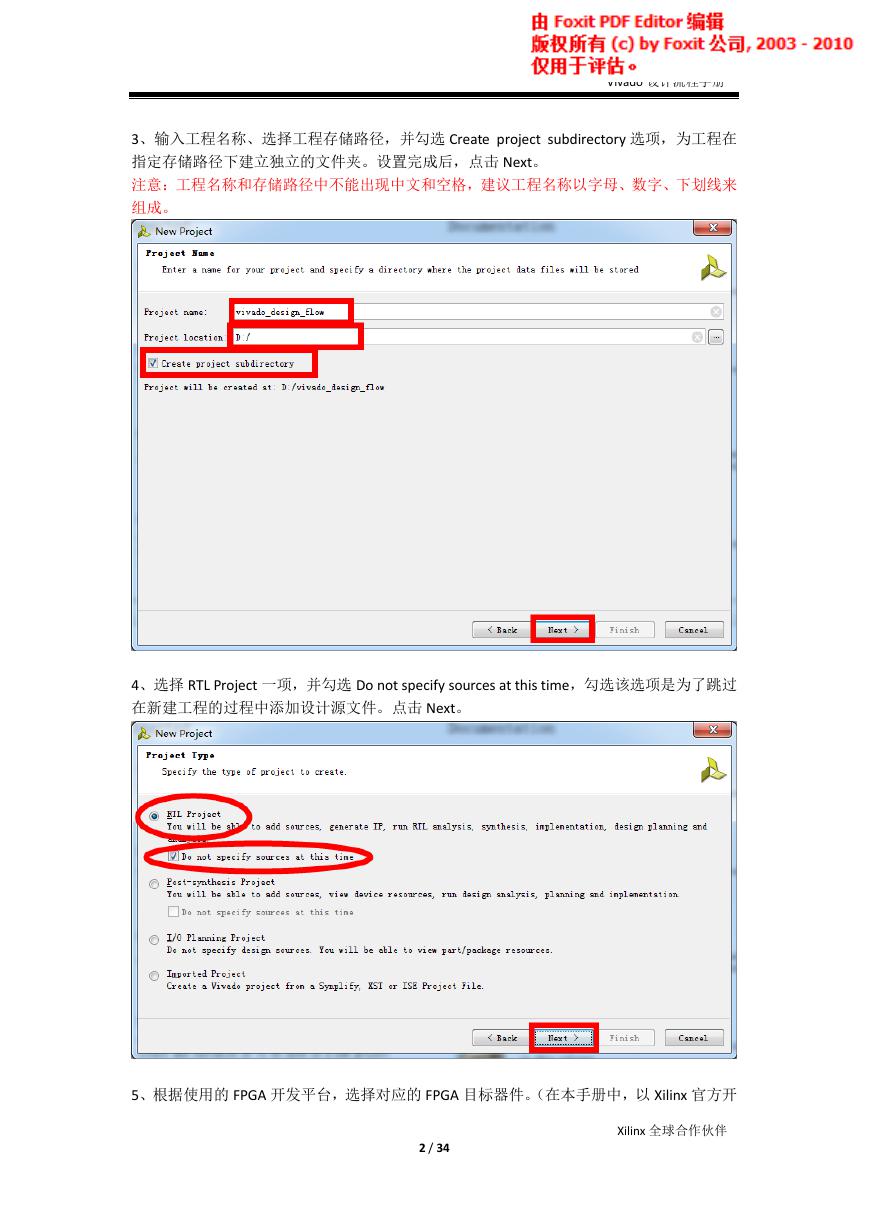

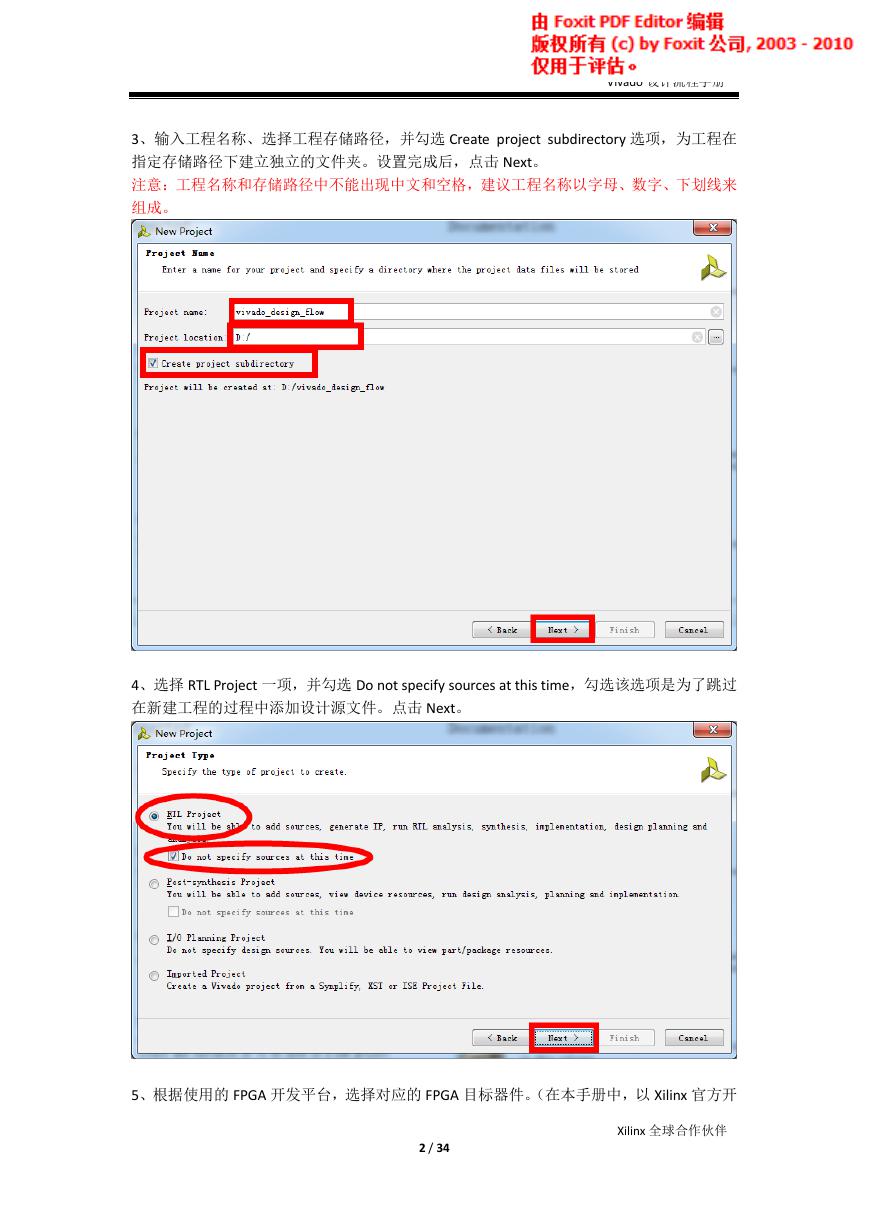

3、输入工程名称、选择工程存储路径,并勾选 Create project subdirectory 选项,为工程在

指定存储路径下建立独立的文件夹。设置完成后,点击 Next。

注意:工程名称和存储路径中不能出现中文和空格,建议工程名称以字母、数字、下划线来

组成。

4、选择 RTL Project 一项,并勾选 Do not specify sources at this time,勾选该选项是为了跳过

在新建工程的过程中添加设计源文件。点击 Next。

5、根据使用的 FPGA 开发平台,选择对应的 FPGA 目标器件。(在本手册中,以 Xilinx 官方开

Xilinx 全球合作伙伴

2 / 34

�

Vivado 设计流程手册

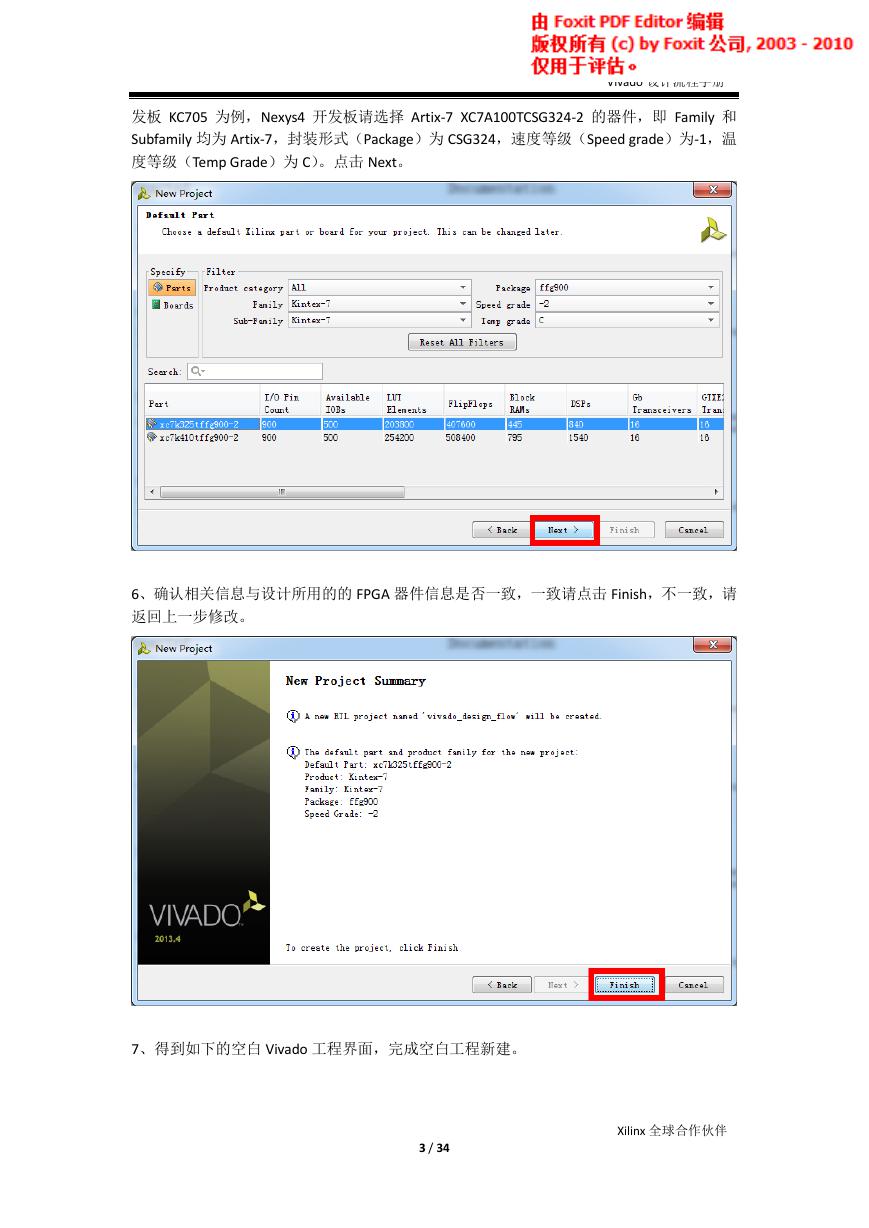

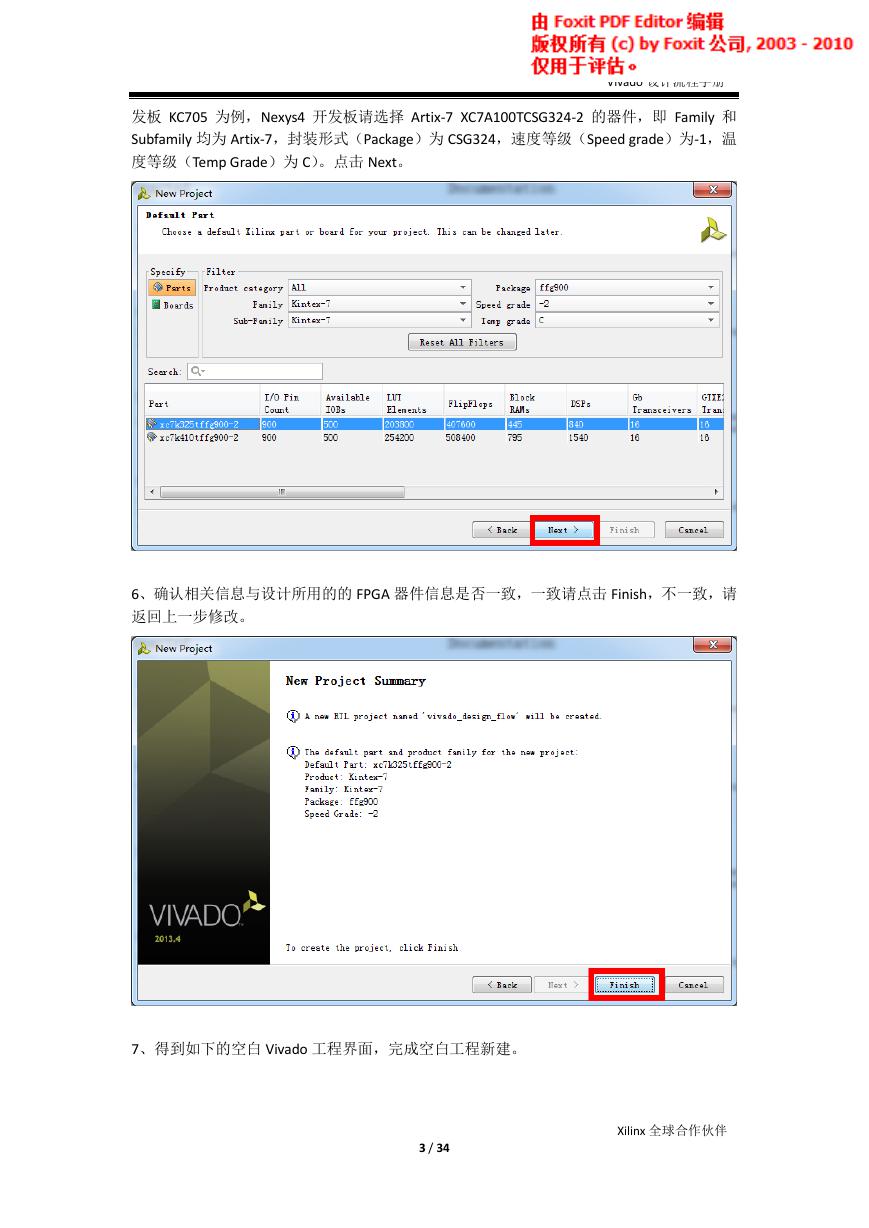

发板 KC705 为例,Nexys4 开发板请选择 Artix-7 XC7A100TCSG324-2 的器件,即 Family 和

Subfamily 均为 Artix-7,封装形式(Package)为 CSG324,速度等级(Speed grade)为-1,温

度等级(Temp Grade)为 C)。点击 Next。

6、确认相关信息与设计所用的的 FPGA 器件信息是否一致,一致请点击 Finish,不一致,请

返回上一步修改。

7、得到如下的空白 Vivado 工程界面,完成空白工程新建。

Xilinx 全球合作伙伴

3 / 34

�

Vivado 设计流程手册

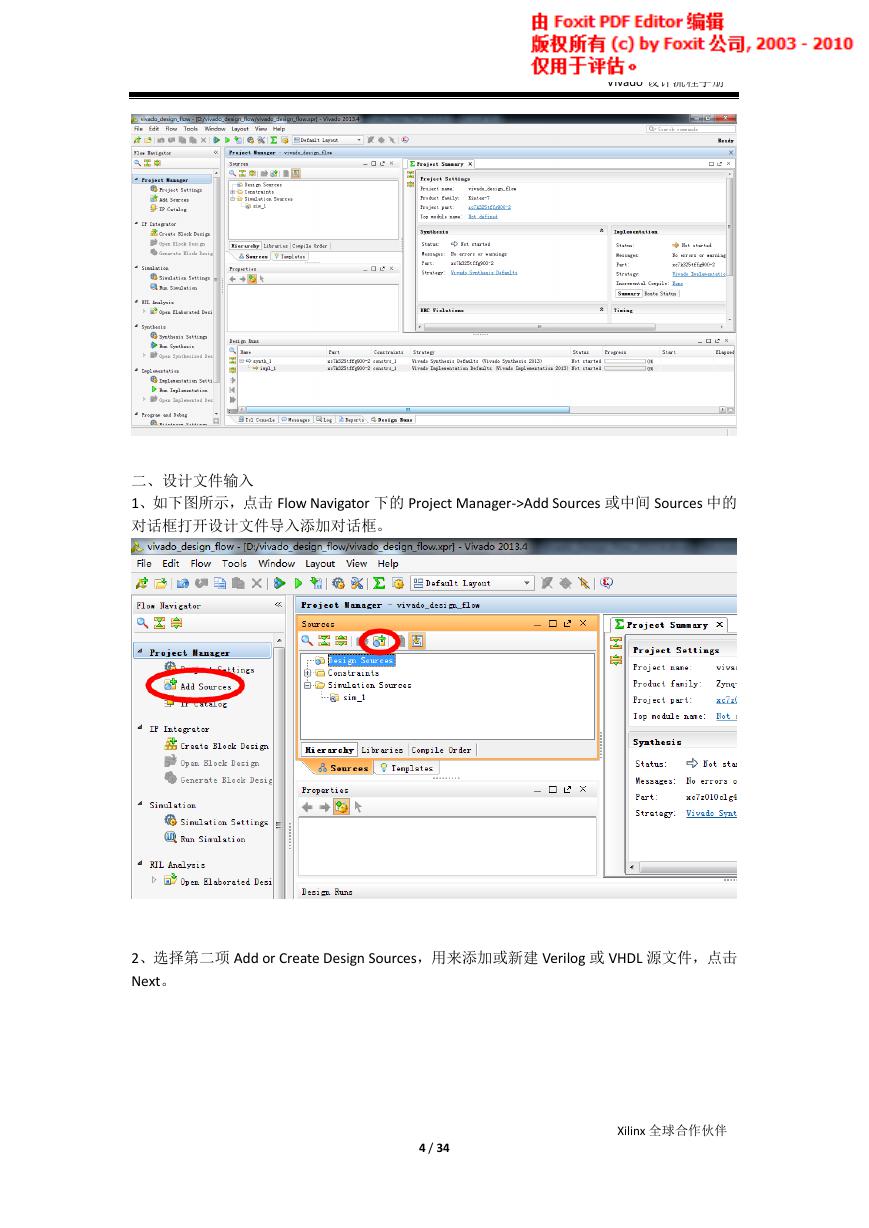

二、设计文件输入

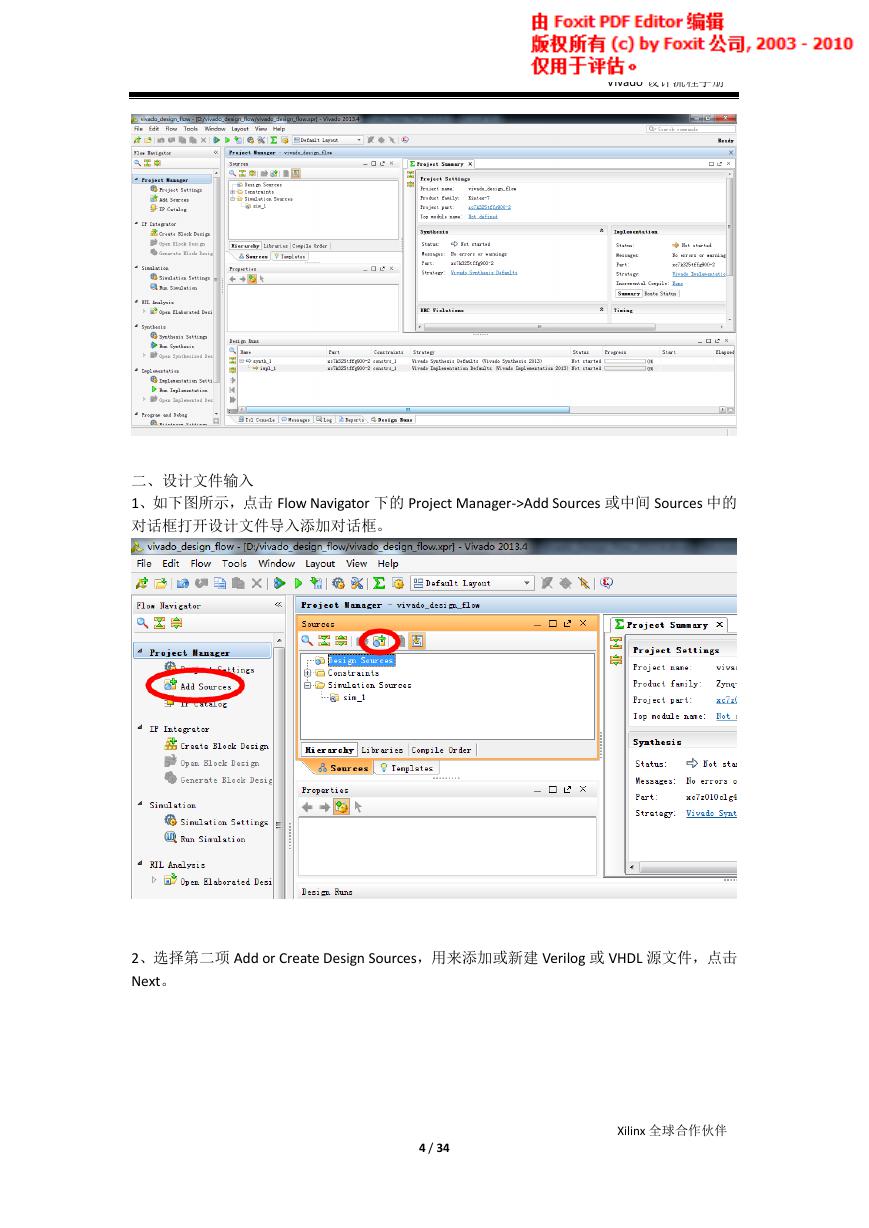

1、如下图所示,点击 Flow Navigator 下的 Project Manager->Add Sources 或中间 Sources 中的

对话框打开设计文件导入添加对话框。

2、选择第二项 Add or Create Design Sources,用来添加或新建 Verilog 或 VHDL 源文件,点击

Next。

Xilinx 全球合作伙伴

4 / 34

�

Vivado 设计流程手册

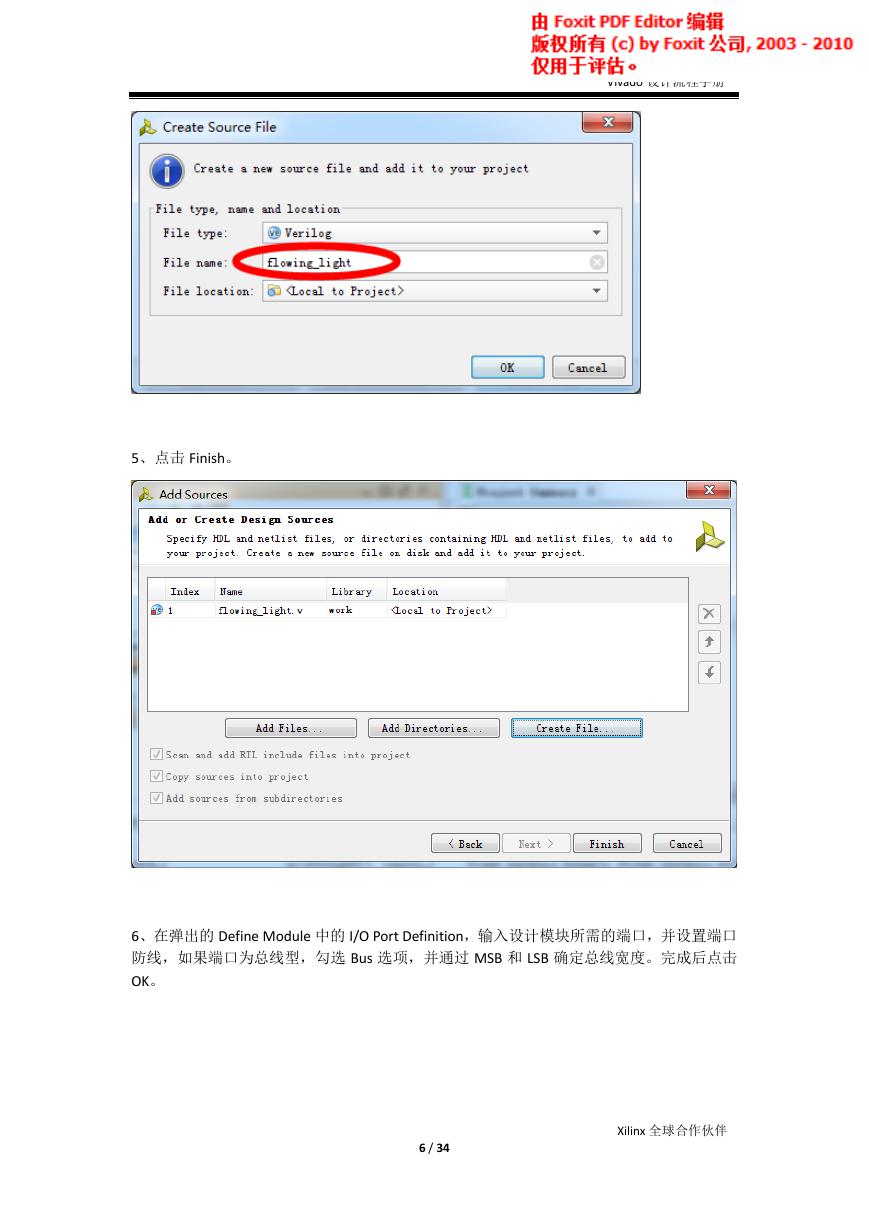

3、如果有现有的 V/VHD 文件,可以通过 Add Files 一项添加。在这里,我们要新建文件,所

以选择 Create File 一项。

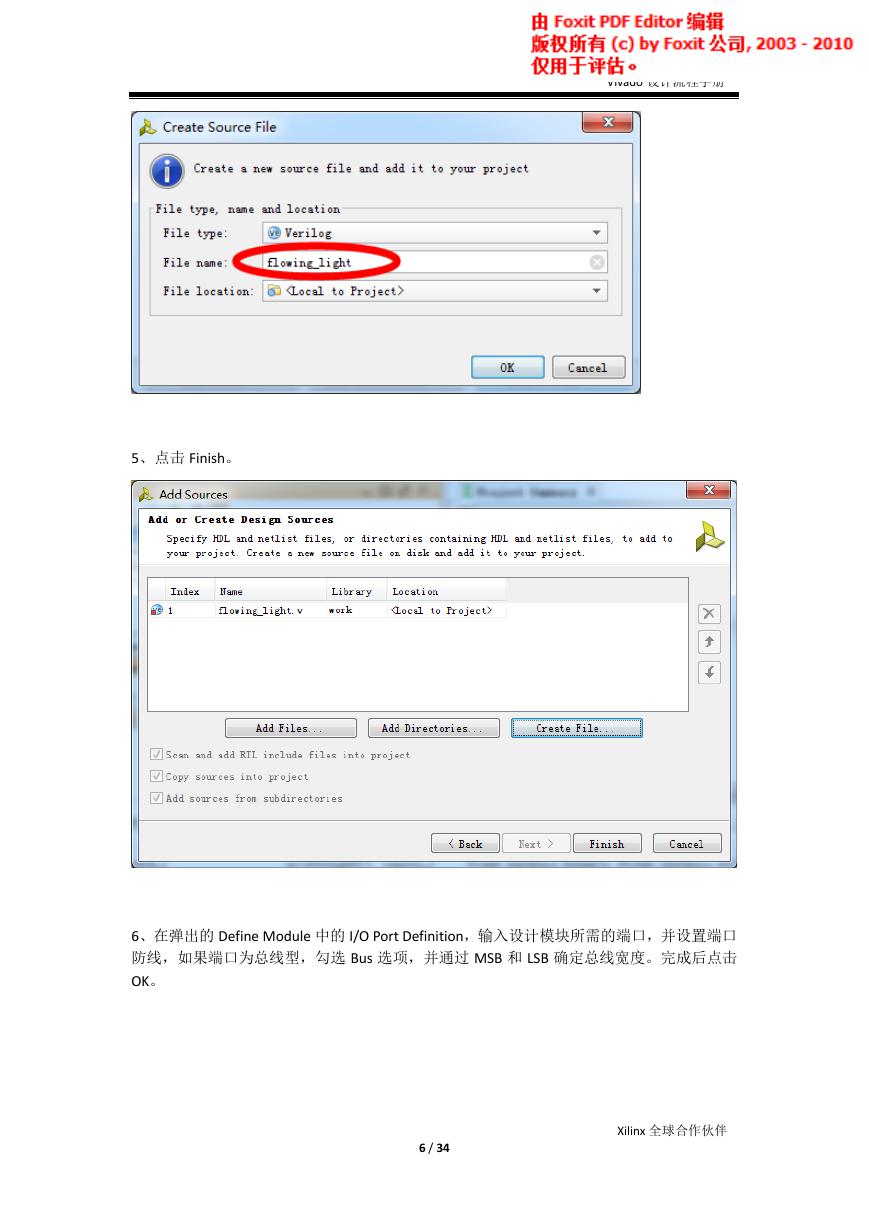

4、在 Create Source File 中输入 File Name,点击 OK。注:名称中不可出现中文和空格。

Xilinx 全球合作伙伴

5 / 34

�

Vivado 设计流程手册

5、点击 Finish。

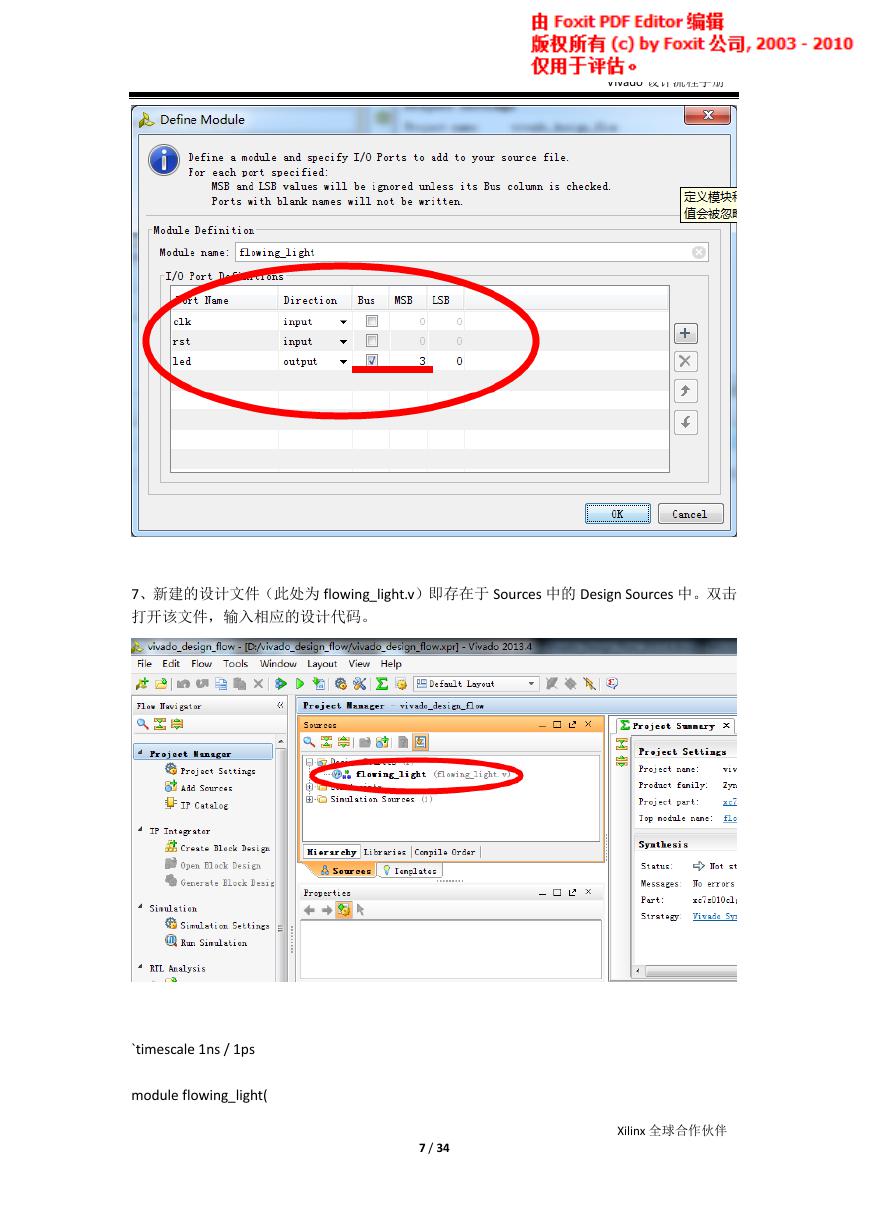

6、在弹出的 Define Module 中的 I/O Port Definition,输入设计模块所需的端口,并设置端口

防线,如果端口为总线型,勾选 Bus 选项,并通过 MSB 和 LSB 确定总线宽度。完成后点击

OK。

Xilinx 全球合作伙伴

6 / 34

�

Vivado 设计流程手册

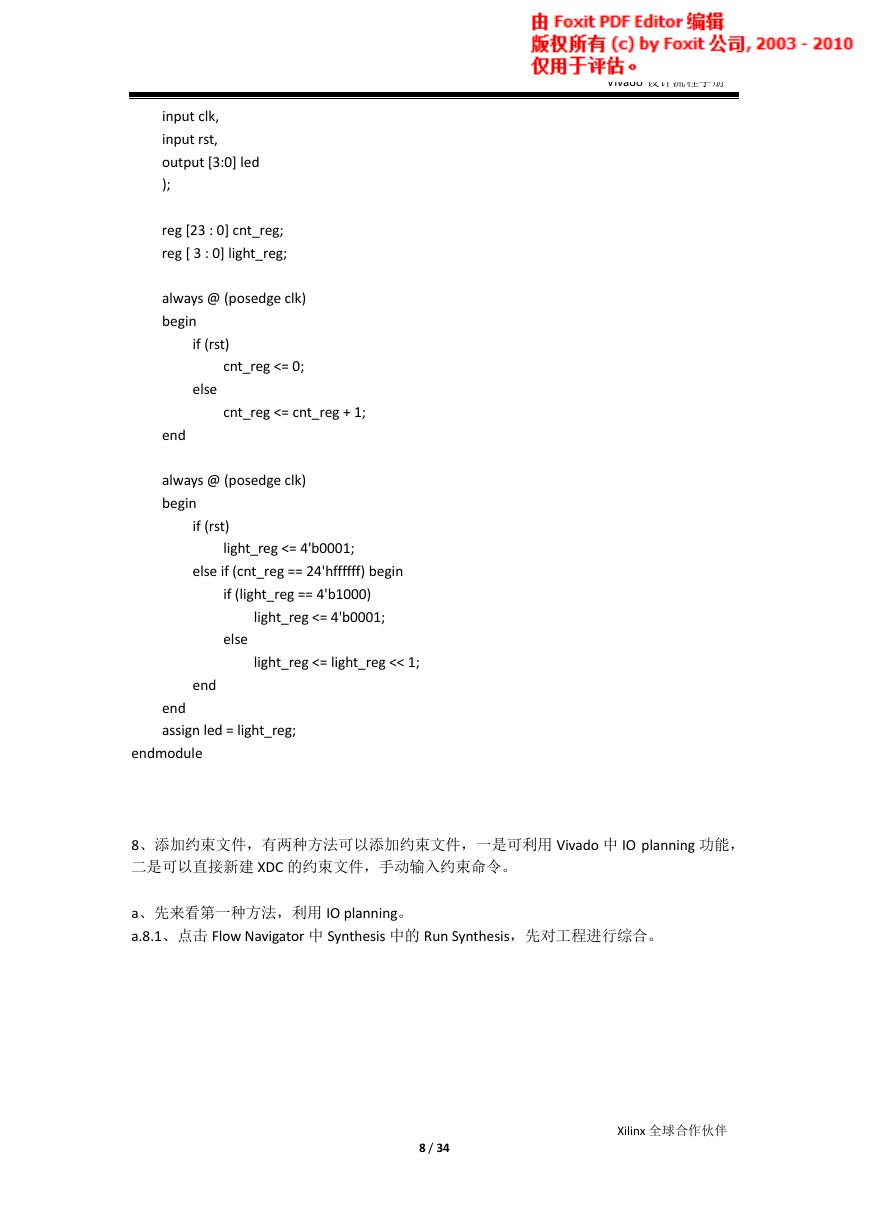

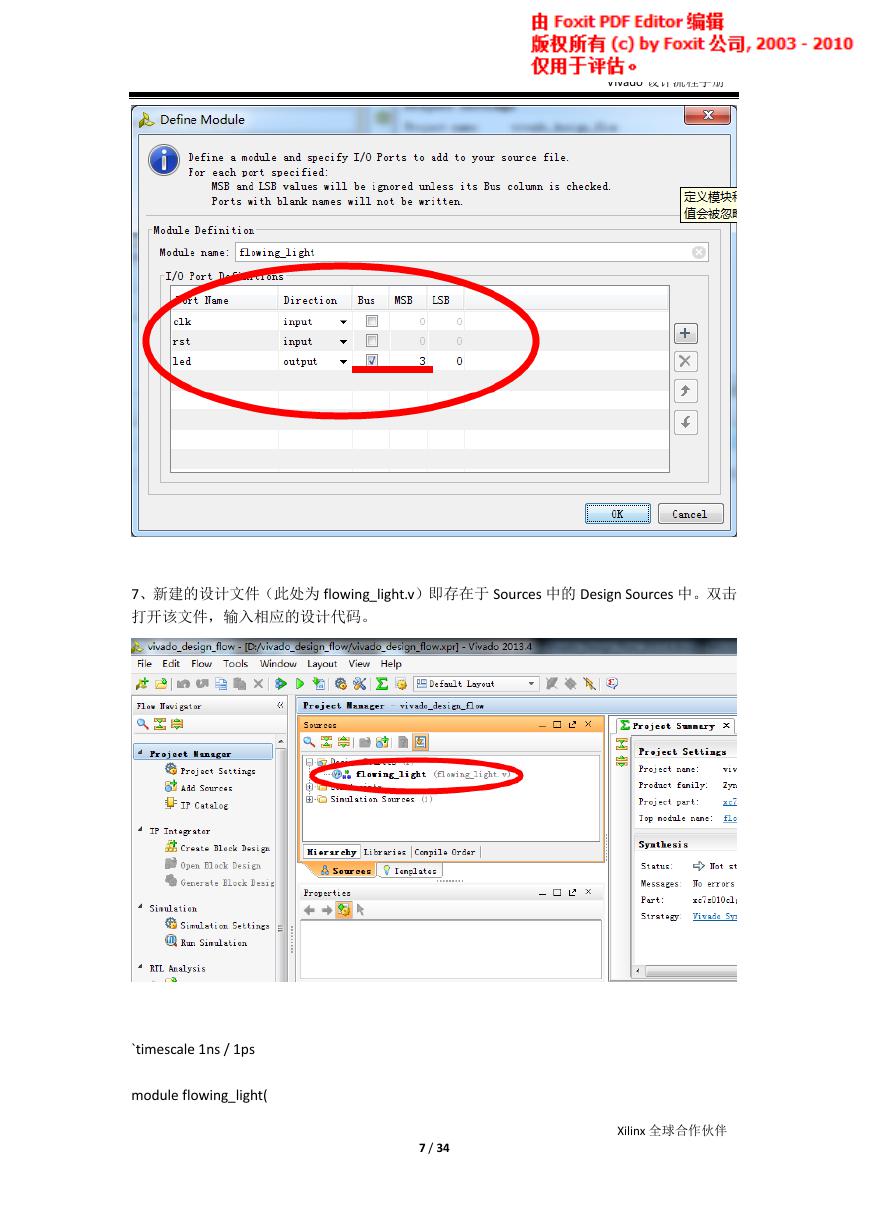

7、新建的设计文件(此处为 flowing_light.v)即存在于 Sources 中的 Design Sources 中。双击

打开该文件,输入相应的设计代码。

`timescale 1ns / 1ps

module flowing_light(

Xilinx 全球合作伙伴

7 / 34

�

Vivado 设计流程手册

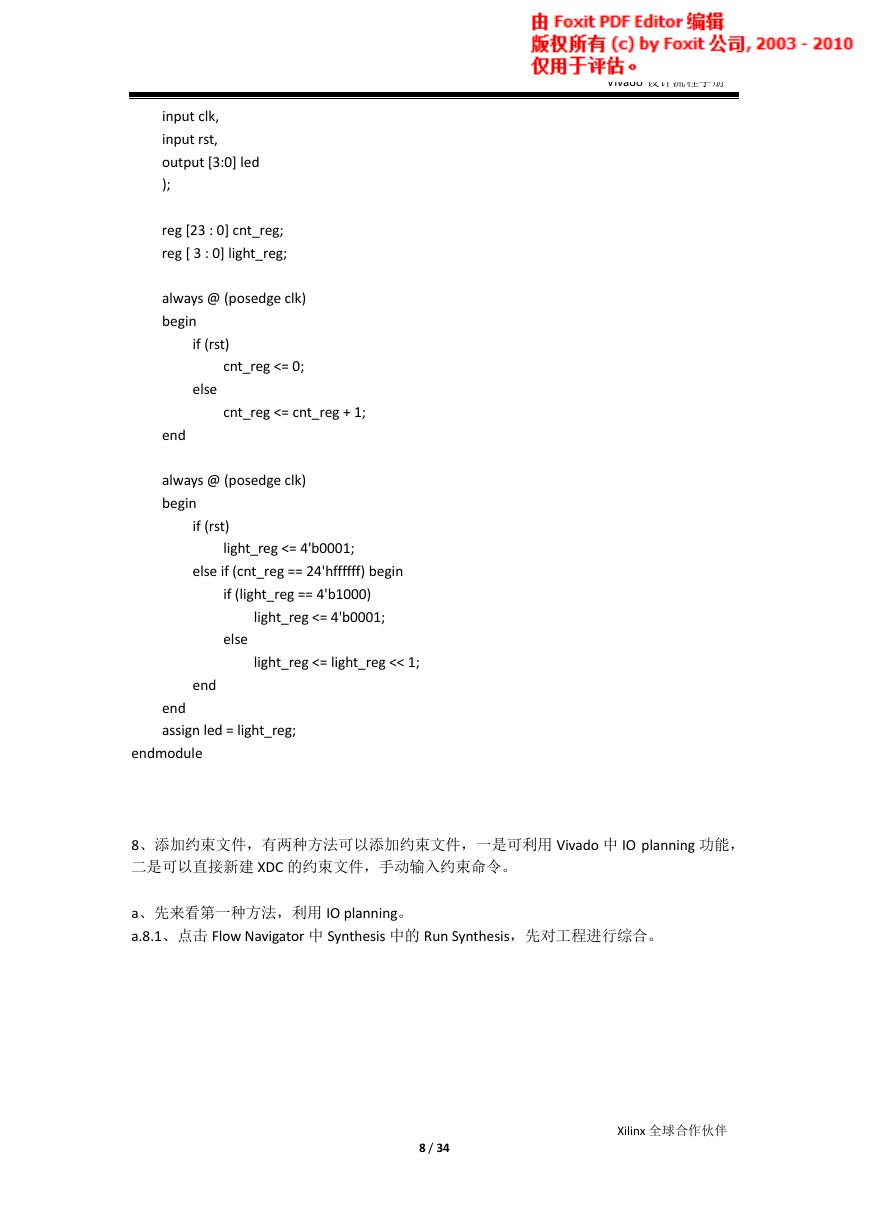

input clk,

input rst,

output [3:0] led

);

reg [23 : 0] cnt_reg;

reg [ 3 : 0] light_reg;

always @ (posedge clk)

begin

if (rst)

cnt_reg <= 0;

else

cnt_reg <= cnt_reg + 1;

end

always @ (posedge clk)

begin

if (rst)

light_reg <= 4'b0001;

else if (cnt_reg == 24'hffffff) begin

if (light_reg == 4'b1000)

light_reg <= 4'b0001;

else

light_reg <= light_reg << 1;

end

end

assign led = light_reg;

endmodule

8、添加约束文件,有两种方法可以添加约束文件,一是可利用 Vivado 中 IO planning 功能,

二是可以直接新建 XDC 的约束文件,手动输入约束命令。

a、先来看第一种方法,利用 IO planning。

a.8.1、点击 Flow Navigator 中 Synthesis 中的 Run Synthesis,先对工程进行综合。

Xilinx 全球合作伙伴

8 / 34

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf