1. Cyclone IV 收发器体系结构

November 2011

CYIV-52001-3.3

CYIV-52001-3.3

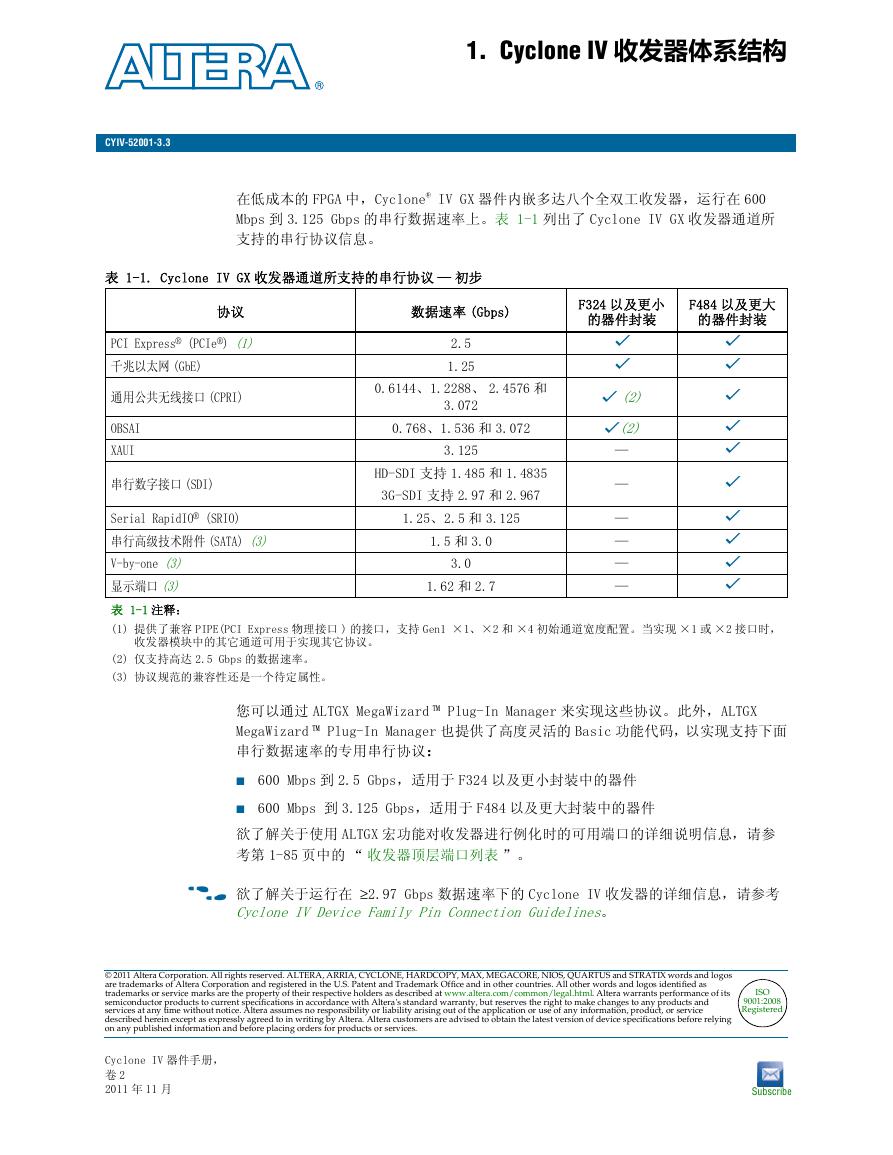

在低成本的 FPGA 中,Cyclone® IV GX 器件内嵌多达八个全双工收发器,运行在 600

Mbps 到 3.125 Gbps 的串行数据速率上。表 1-1 列出了 Cyclone IV GX 收发器通道所

支持的串行协议信息。

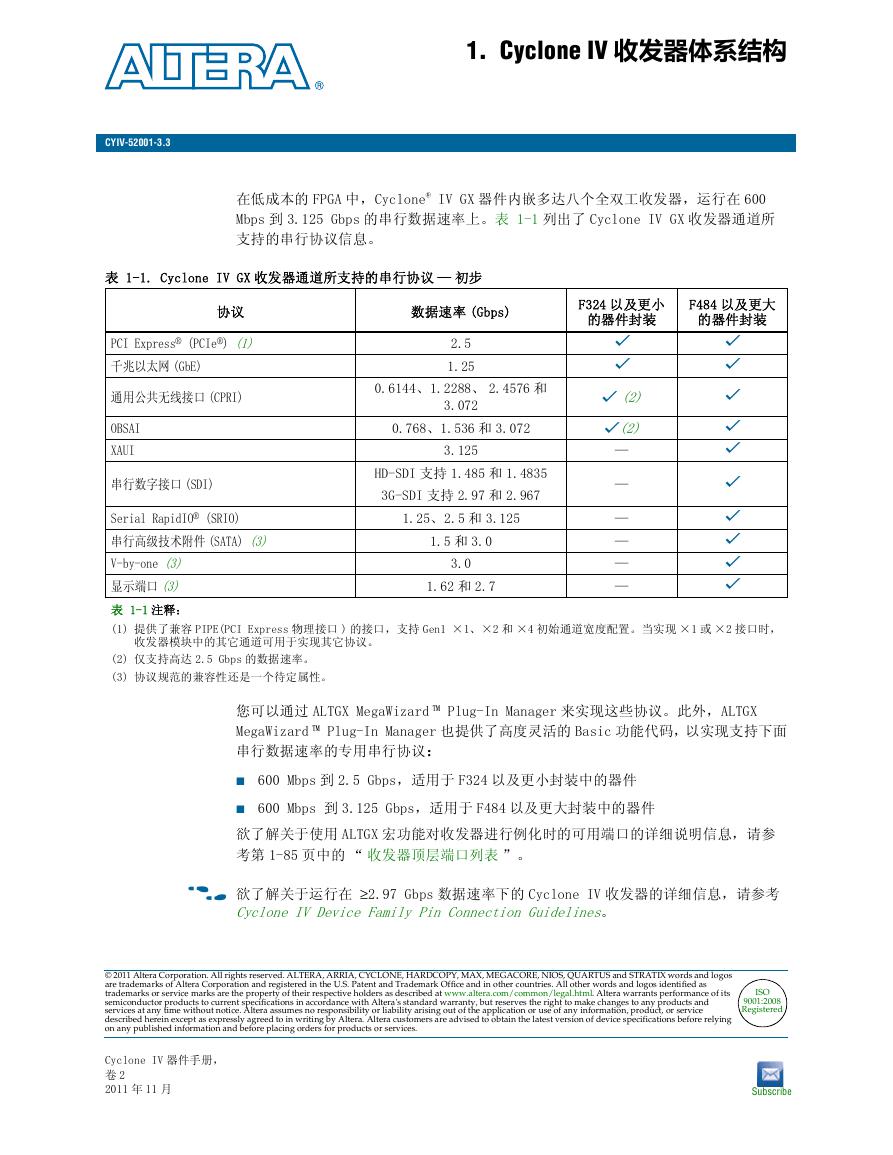

表 1-1. Cyclone IV GX 收发器通道所支持的串行协议 — 初步

协议

数据速率 (Gbps)

F324 以及更小

的器件封装

F484 以及更大

的器件封装

PCI Express® (PCIe®) (1)

千兆以太网 (GbE)

通用公共无线接口 (CPRI)

OBSAI

XAUI

串行数字接口 (SDI)

Serial RapidIO® (SRIO)

串行高级技术附件 (SATA) (3)

V-by-one (3)

显示端口 (3)

表 1-1 注释:

2.5

1.25

0.6144、1.2288、 2.4576 和

3.072

0.768、1.536 和 3.072

3.125

HD-SDI 支持 1.485 和 1.4835

3G-SDI 支持 2.97 和 2.967

1.25、2.5 和 3.125

1.5 和 3.0

3.0

1.62 和 2.7

v

v

v (2)

v(2)

—

—

—

—

—

—

v

v

v

v

v

v

v

v

v

v

(1) 提供了兼容 PIPE(PCI Express 物理接口 ) 的接口,支持 Gen1 ×1、×2 和 ×4 初始通道宽度配置。当实现 ×1 或 ×2 接口时,

收发器模块中的其它通道可用于实现其它协议。

(2) 仅支持高达 2.5 Gbps 的数据速率。

(3) 协议规范的兼容性还是一个待定属性。

您可以通过 ALTGX MegaWizard ™ Plug-In Manager 来实现这些协议。此外,ALTGX

MegaWizard ™ Plug-In Manager 也提供了高度灵活的 Basic 功能代码,以实现支持下面

串行数据速率的专用串行协议:

■ 600 Mbps 到 2.5 Gbps,适用于 F324 以及更小封装中的器件

■ 600 Mbps 到 3.125 Gbps,适用于 F484 以及更大封装中的器件

欲了解关于使用 ALTGX 宏功能对收发器进行例化时的可用端口的详细说明信息,请参

考第 1-85 页中的 “ 收发器顶层端口列表 ”。

f 欲了解关于运行在 ≥2.97 Gbps 数据速率下的 Cyclone IV 收发器的详细信息,请参考

Cyclone IV Device Family Pin Connection Guidelines。

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 2

2011 年 11 月

Subscribe

�

1–2

第 1 章 : Cyclone IV 收发器体系结构

收发器体系结构

1 Cyclone IV GX 器件包含一个 PCIe MegaCore® 功能的硬核知识产权 (IP) 实现,支持在主

节点或从节点模式下配置的 Gen1 ×1、×2 和 ×4 初始通道宽度。欲了解更多信息,

请参考第 1-46 页中的 “PCI-Express 硬核 IP 模块 ”。

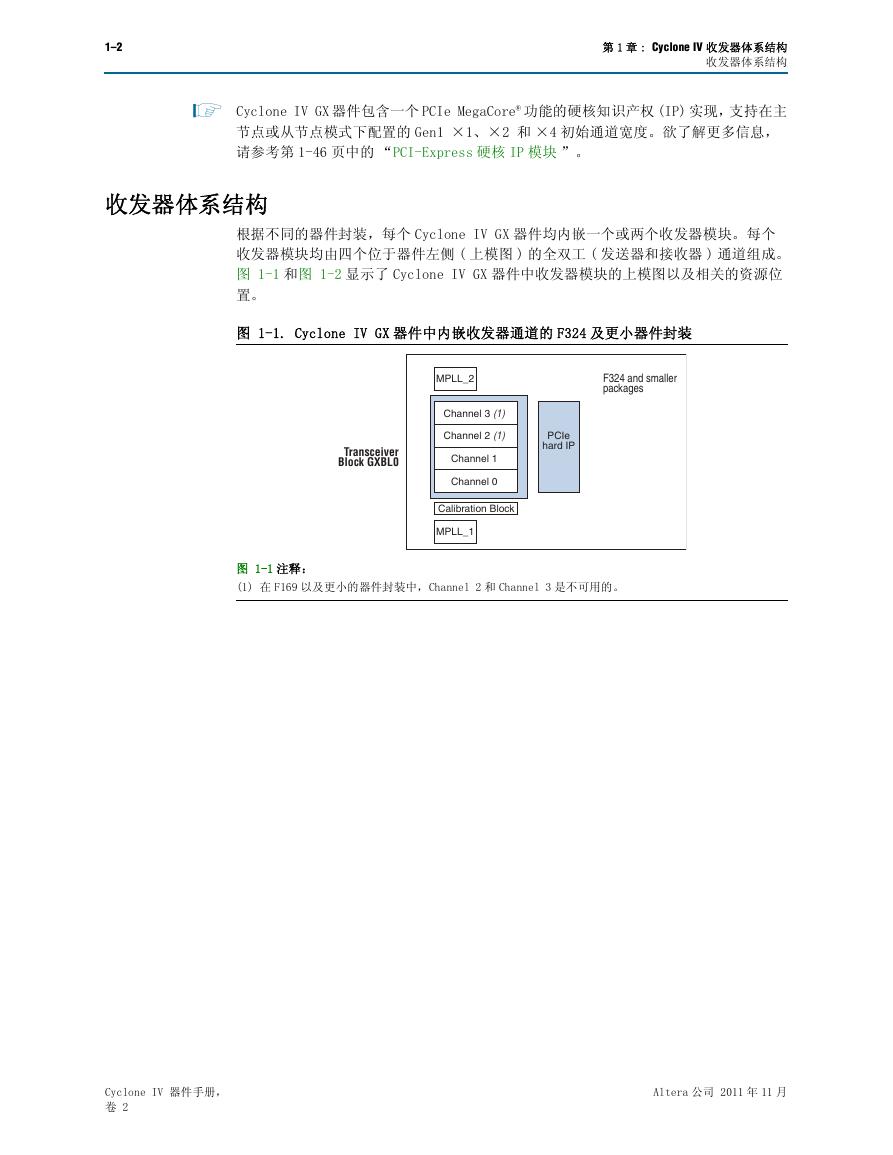

收发器体系结构

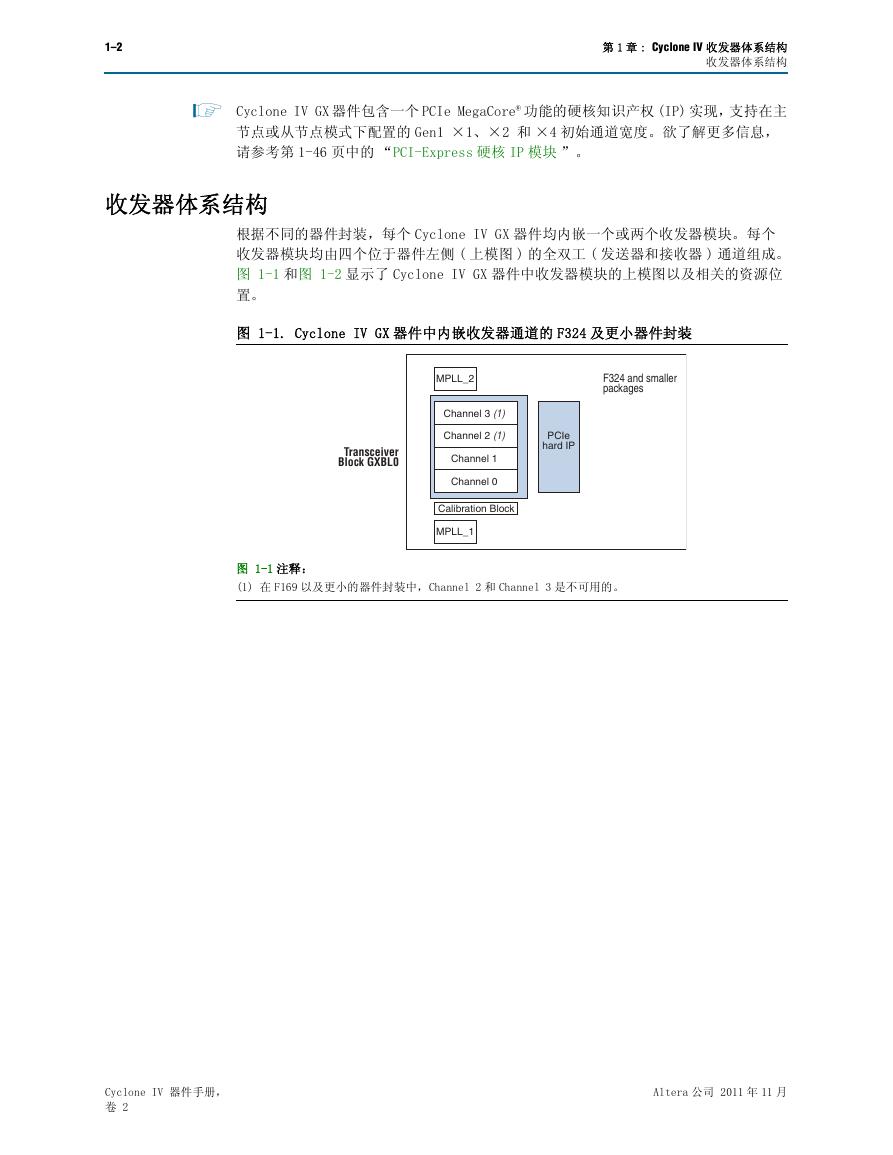

根据不同的器件封装,每个 Cyclone IV GX 器件均内嵌一个或两个收发器模块。每个

收发器模块均由四个位于器件左侧 ( 上模图 ) 的全双工 ( 发送器和接收器 ) 通道组成。

图 1-1 和图 1-2 显示了 Cyclone IV GX 器件中收发器模块的上模图以及相关的资源位

置。

图 1-1. Cyclone IV GX 器件中内嵌收发器通道的 F324 及更小器件封装

F324 and smaller

packages

PCIe

hard IP

Transceiver

Block GXBL0

MPLL_2

Channel 3 (1)

Channel 2 (1)

Channel 1

Channel 0

Calibration Block

MPLL_1

图 1-1 注释:

(1) 在 F169 以及更小的器件封装中,Channel 2 和 Channel 3 是不可用的。

Cyclone IV 器件手册,

卷 2

Altera 公司 2011 年 11 月

�

第 1 章 : Cyclone IV 收发器体系结构

收发器体系结构

1–3

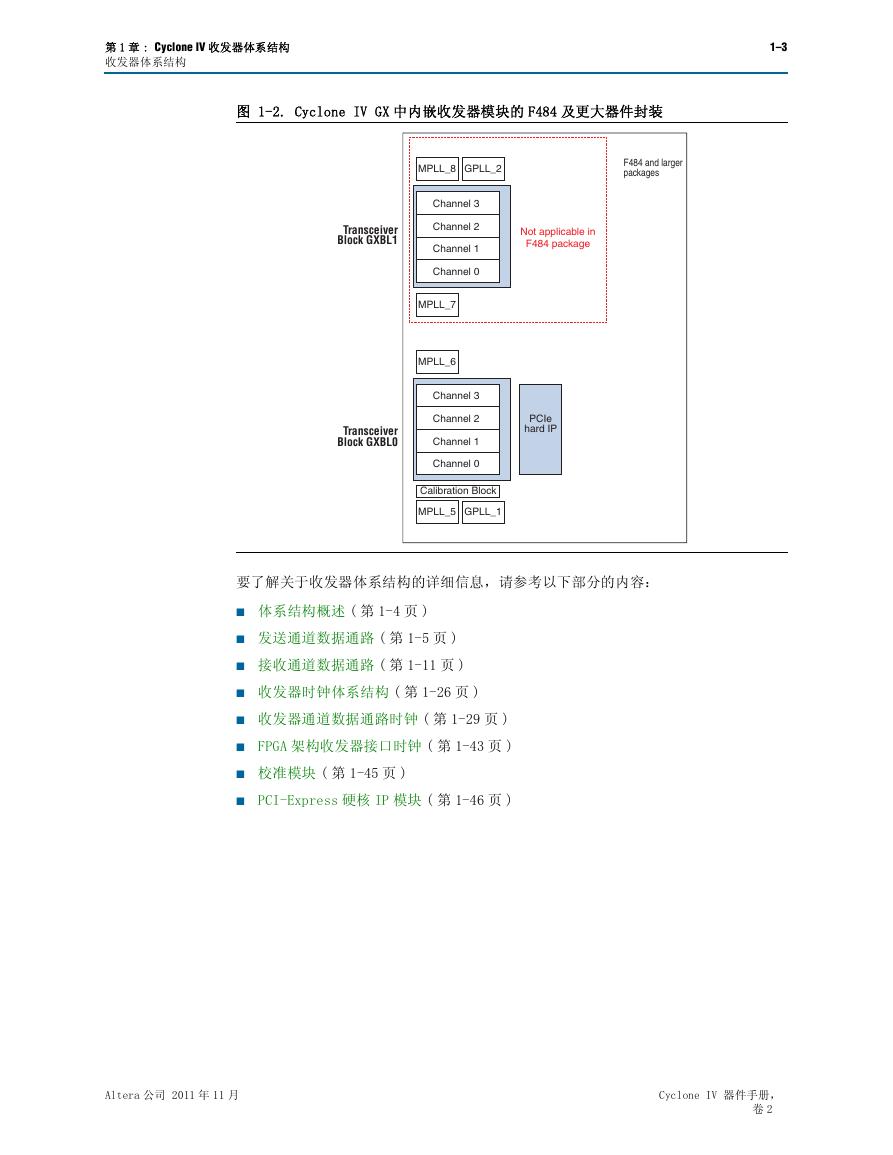

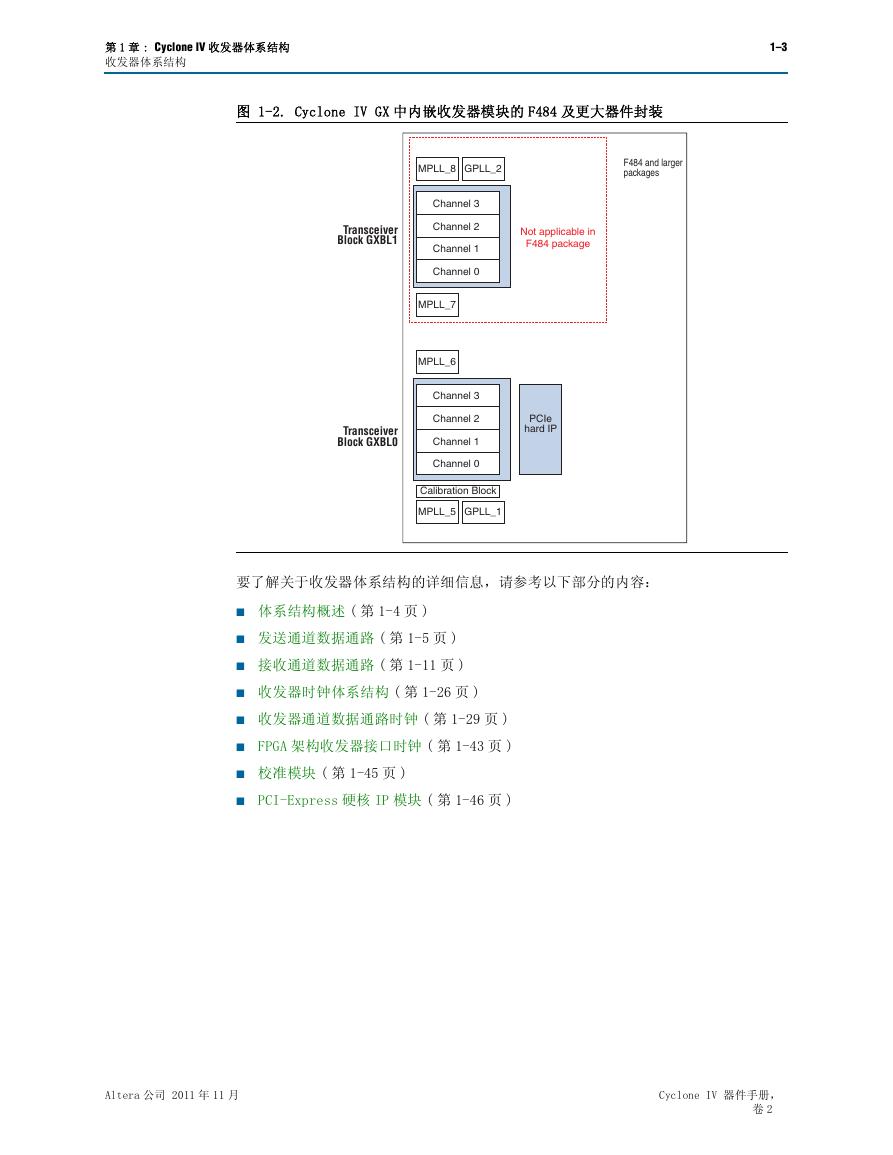

图 1-2. Cyclone IV GX 中内嵌收发器模块的 F484 及更大器件封装

MPLL_8 GPLL_2

F484 and larger

packages

Transceiver

Block GXBL1

Transceiver

Block GXBL0

Channel 3

Channel 2

Channel 1

Channel 0

MPLL_7

MPLL_6

Channel 3

Channel 2

Channel 1

Channel 0

Calibration Block

MPLL_5

GPLL_1

Not applicable in

F484 package

PCIe

hard IP

要了解关于收发器体系结构的详细信息,请参考以下部分的内容:

■ 体系结构概述 ( 第 1-4 页 )

■ 发送通道数据通路 ( 第 1-5 页 )

■ 接收通道数据通路 ( 第 1-11 页 )

■ 收发器时钟体系结构 ( 第 1-26 页 )

■ 收发器通道数据通路时钟 ( 第 1-29 页 )

■ FPGA 架构收发器接口时钟 ( 第 1-43 页 )

■ 校准模块 ( 第 1-45 页 )

■ PCI-Express 硬核 IP 模块 ( 第 1-46 页 )

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 2

�

1–4

体系结构概述

第 1 章 : Cyclone IV 收发器体系结构

体系结构概述

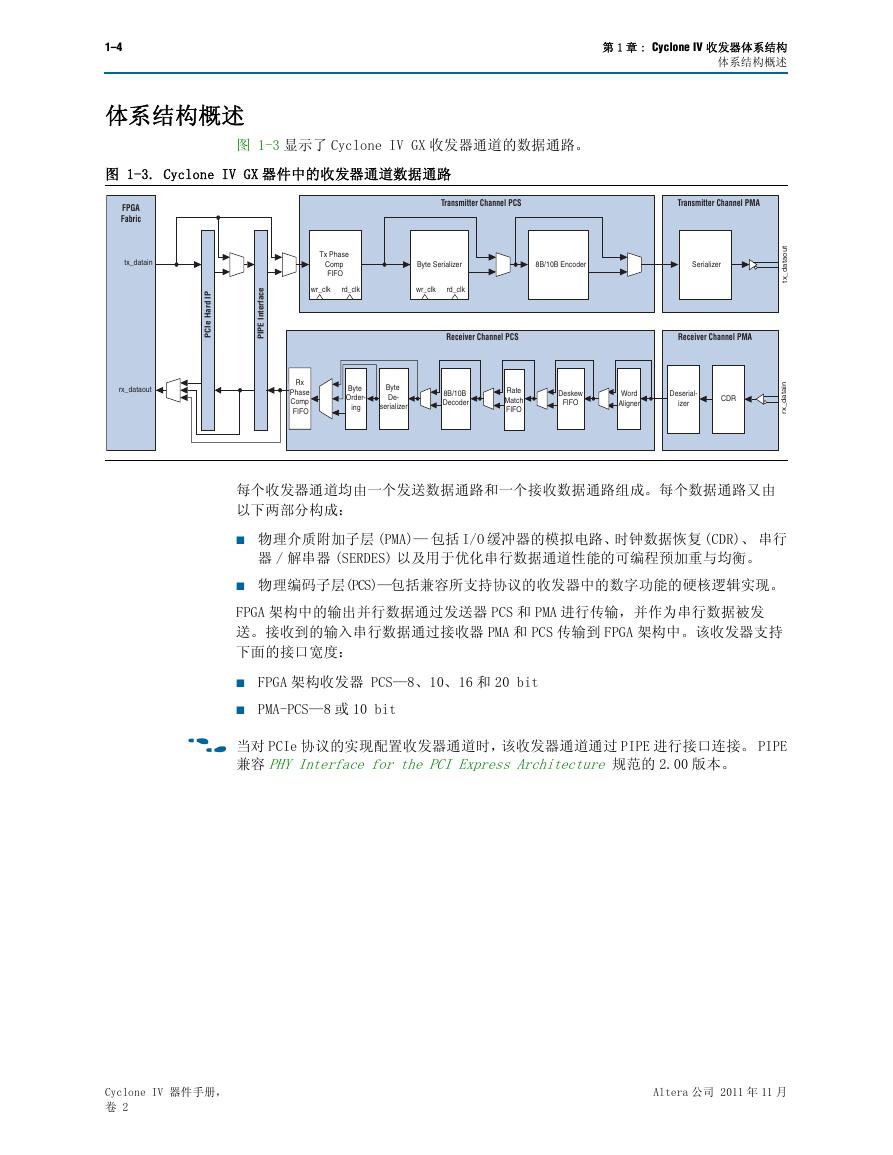

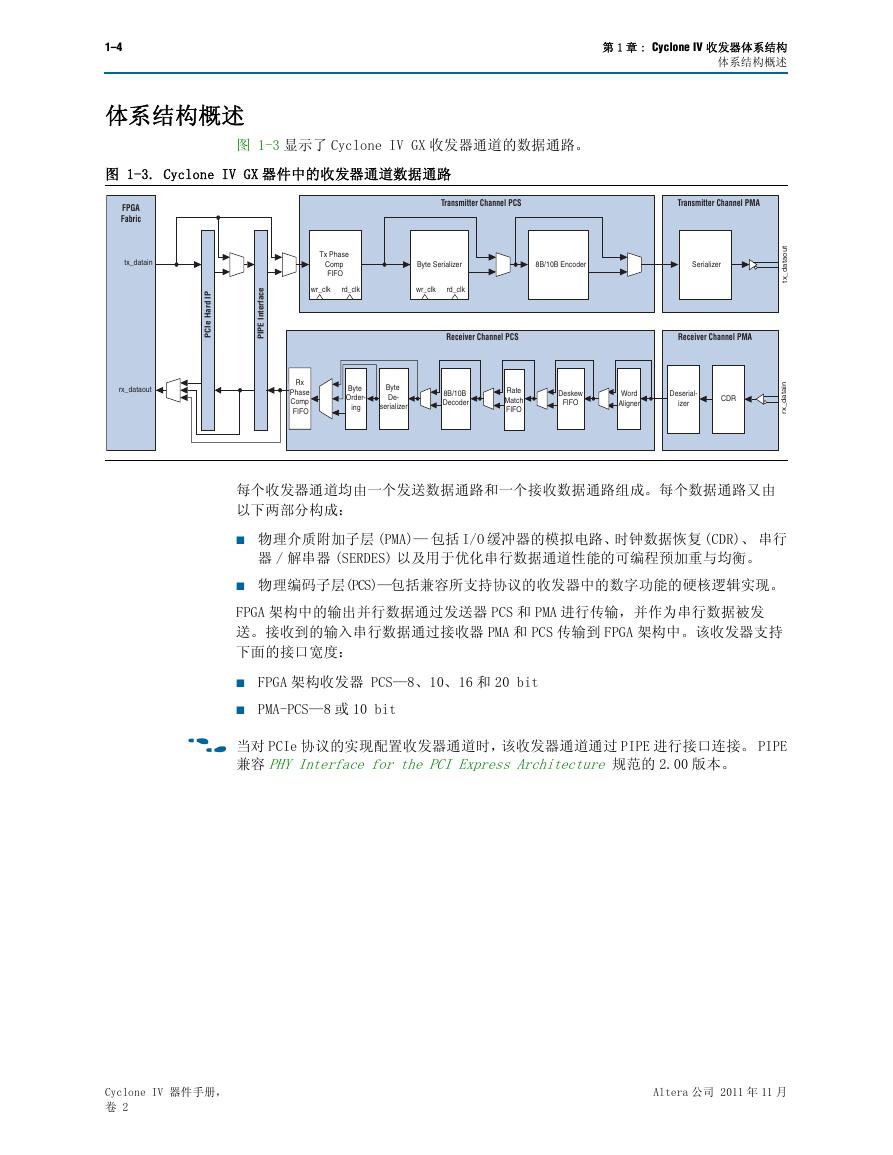

图 1-3 显示了 Cyclone IV GX 收发器通道的数据通路。

图 1-3. Cyclone IV GX 器件中的收发器通道数据通路

FPGA

Fabric

tx_datain

rx_dataout

P

I

d

r

a

H

e

I

C

P

e

c

a

f

r

e

t

n

I

E

P

P

I

Transmitter Channel PCS

Transmitter Channel PMA

Tx Phase

Comp

FIFO

Byte Serializer

8B/10B Encoder

Serializer

wr_clk

rd_clk

wr_clk

rd_clk

Receiver Channel PCS

Receiver Channel PMA

Rx

Phase

Comp

FIFO

Byte

Order-

ing

Byte

De-

serializer

8B/10B

Decoder

Rate

Match

FIFO

Deskew

FIFO

Word

Aligner

Deserial-

izer

CDR

t

u

o

a

t

a

d

_

x

t

n

a

i

t

a

d

_

x

r

每个收发器通道均由一个发送数据通路和一个接收数据通路组成。每个数据通路又由

以下两部分构成:

■ 物理介质附加子层 (PMA)— 包括 I/O 缓冲器的模拟电路、时钟数据恢复 (CDR)、 串行

器 / 解串器 (SERDES) 以及用于优化串行数据通道性能的可编程预加重与均衡。

■ 物理编码子层(PCS)—包括兼容所支持协议的收发器中的数字功能的硬核逻辑实现。

FPGA 架构中的输出并行数据通过发送器 PCS 和 PMA 进行传输,并作为串行数据被发

送。接收到的输入串行数据通过接收器 PMA 和 PCS 传输到 FPGA 架构中。该收发器支持

下面的接口宽度:

■ FPGA 架构收发器 PCS—8、10、16 和 20 bit

■ PMA-PCS—8 或 10 bit

f 当对 PCIe 协议的实现配置收发器通道时,该收发器通道通过 PIPE 进行接口连接。 PIPE

兼容 PHY Interface for the PCI Express Architecture 规范的 2.00 版本。

Cyclone IV 器件手册,

卷 2

Altera 公司 2011 年 11 月

�

第 1 章 : Cyclone IV 收发器体系结构

发送通道数据通路

发送通道数据通路

1–5

接下来的部分介绍了 Cyclone IV GX 发送通道数据通路的体系结构,如图 1-3 所示:

■

TX 相位补偿 FIFO

■ 字节串行器

■

8B/10B 编码器

■ 串行器

■ 发送器输出缓冲器

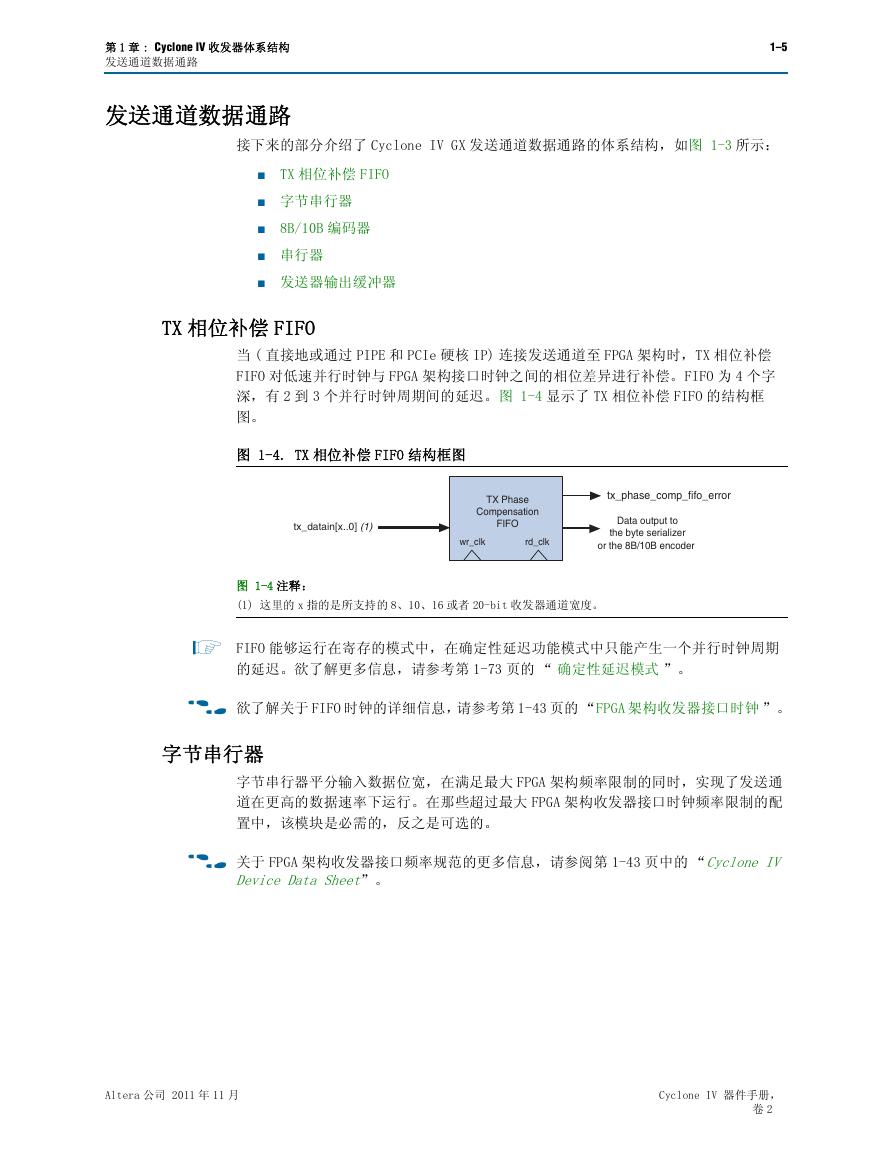

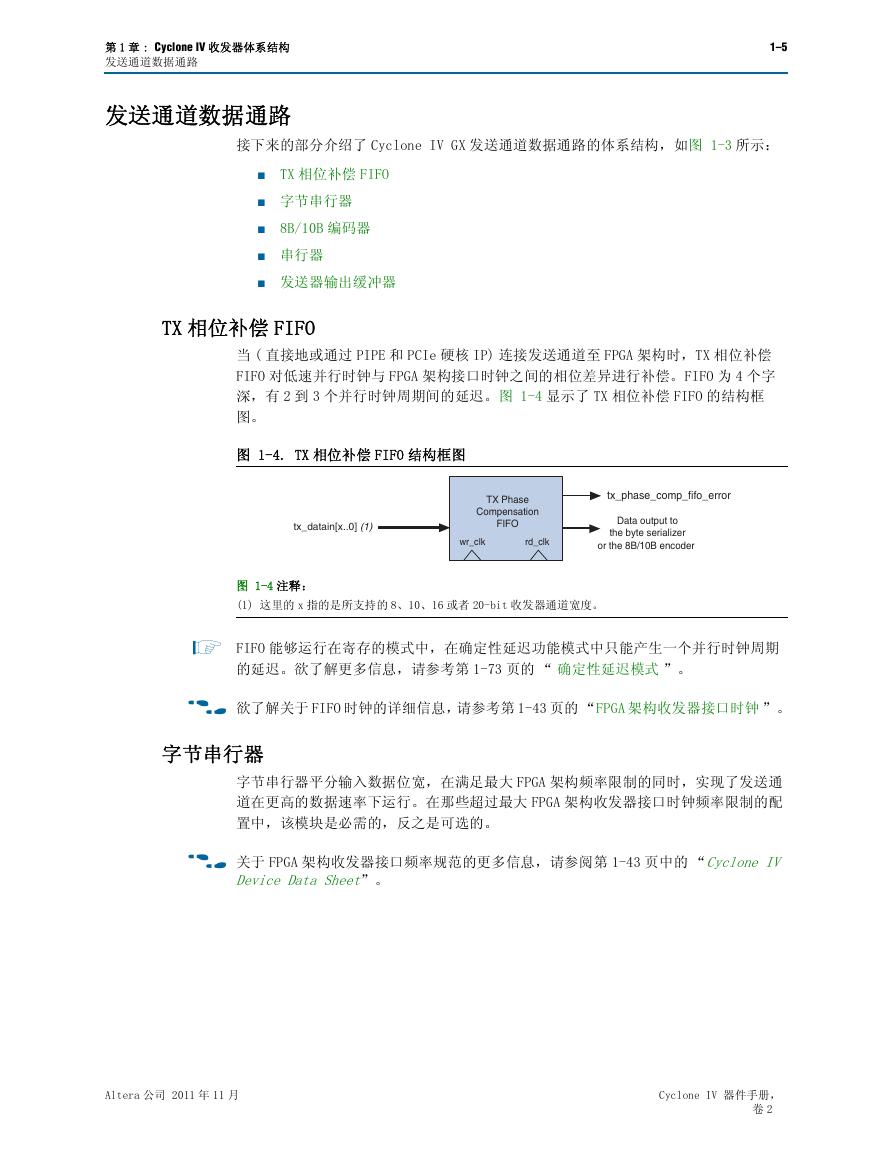

TX 相位补偿 FIFO

当 ( 直接地或通过 PIPE 和 PCIe 硬核 IP) 连接发送通道至 FPGA 架构时,TX 相位补偿

FIFO 对低速并行时钟与 FPGA 架构接口时钟之间的相位差异进行补偿。FIFO 为 4 个字

深,有 2 到 3 个并行时钟周期间的延迟。图 1-4 显示了 TX 相位补偿 FIFO 的结构框

图。

图 1-4. TX 相位补偿 FIFO 结构框图

tx_datain[x..0] (1)

TX Phase

Compensation

FIFO

wr_clk

rd_clk

tx_phase_comp_fifo_error

Data output to

the byte serializer

or the 8B/10B encoder

图 1-4 注释:

(1) 这里的 x 指的是所支持的 8、10、16 或者 20-bit 收发器通道宽度。

1 FIFO 能够运行在寄存的模式中,在确定性延迟功能模式中只能产生一个并行时钟周期

的延迟。欲了解更多信息,请参考第 1-73 页的 “ 确定性延迟模式 ”。

f 欲了解关于 FIFO 时钟的详细信息,请参考第 1-43 页的 “FPGA 架构收发器接口时钟 ”。

字节串行器

字节串行器平分输入数据位宽,在满足最大 FPGA 架构频率限制的同时,实现了发送通

道在更高的数据速率下运行。在那些超过最大 FPGA 架构收发器接口时钟频率限制的配

置中,该模块是必需的,反之是可选的。

f 关于 FPGA 架构收发器接口频率规范的更多信息,请参阅第 1-43 页中的 “Cyclone IV

Device Data Sheet”。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 2

�

1–6

第 1 章 : Cyclone IV 收发器体系结构

发送通道数据通路

举例说明,在不使用字节串行器的情况下,当一个 EP4CGX150 发送通道运行在 3.125

Gbps 时,FPGA 架构频率为 312.5 MHz (3.125 Gbps/10)。该实现违反了频率限制,从

而没有被支持。当使用字节串行器时,3.125 Gbps 的通道操作是被支持的,其中的

FPGA 架构频率为 156.25 MHz (3.125 Gbps/20)。

字节串行器首先转发最低有效位,然后转发最高有效位。

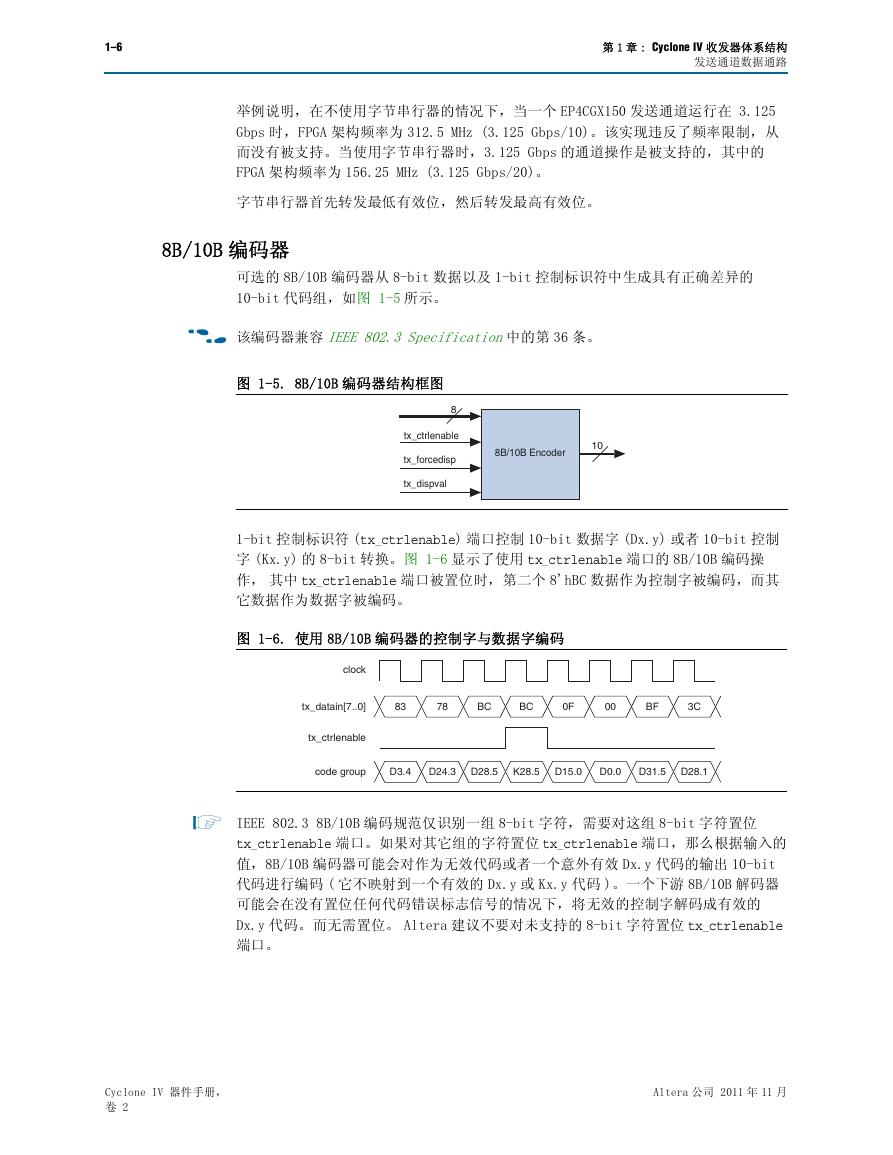

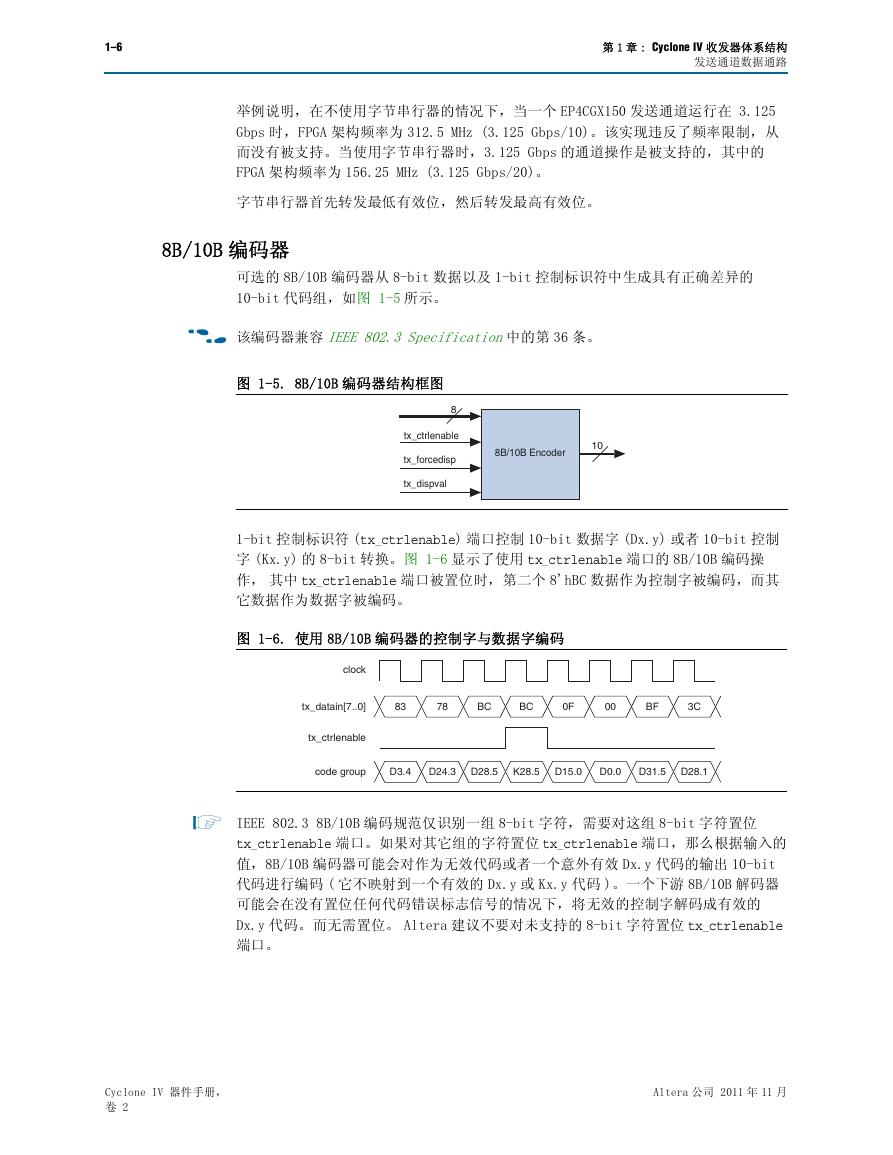

8B/10B 编码器

可选的 8B/10B 编码器从 8-bit 数据以及 1-bit 控制标识符中生成具有正确差异的

10-bit 代码组,如图 1-5 所示。

f 该编码器兼容 IEEE 802.3 Specification中的第 36 条。

图 1-5. 8B/10B 编码器结构框图

8

tx_ctrlenable

tx_forcedisp

tx_dispval

8B/10B Encoder

10

1-bit 控制标识符 (tx_ctrlenable) 端口控制 10-bit 数据字 (Dx.y) 或者 10-bit 控制

字 (Kx.y) 的 8-bit 转换。图 1-6 显示了使用 tx_ctrlenable 端口的 8B/10B 编码操

作, 其中 tx_ctrlenable 端口被置位时,第二个 8'hBC 数据作为控制字被编码,而其

它数据作为数据字被编码。

图 1-6. 使用 8B/10B 编码器的控制字与数据字编码

clock

tx_datain[7..0]

83

78

BC

BC

0F

00

BF

3C

tx_ctrlenable

code group

D3.4

D24.3

D28.5

K28.5

D15.0

D0.0

D31.5

D28.1

1 IEEE 802.3 8B/10B 编码规范仅识别一组 8-bit 字符,需要对这组 8-bit 字符置位

tx_ctrlenable 端口。如果对其它组的字符置位 tx_ctrlenable 端口,那么根据输入的

值,8B/10B 编码器可能会对作为无效代码或者一个意外有效 Dx.y 代码的输出 10-bit

代码进行编码 ( 它不映射到一个有效的 Dx.y 或 Kx.y 代码 )。一个下游 8B/10B 解码器

可能会在没有置位任何代码错误标志信号的情况下,将无效的控制字解码成有效的

Dx.y 代码。而无需置位。 Altera 建议不要对未支持的 8-bit 字符置位 tx_ctrlenable

端口。

Cyclone IV 器件手册,

卷 2

Altera 公司 2011 年 11 月

�

第 1 章 : Cyclone IV 收发器体系结构

发送通道数据通路

1–7

下面介绍了复位情况下的 8B/10B 编码器行为 ( 如图 1-7 所示 ):

■ 复位过程中,8B/10B 编码器忽略来自 FPGA 架构的输入数据 (tx_datain 和

tx_ctrlenable 端口 ),并连续输出 RD 列中的 K28.5 码型,直到 tx_digitalreset

端口被置位。

■ 当 tx_digitalreset 端口被置位时,8B/10B 编码器从负差异开始编码。8B/10B 编码

器开始编码和在它的输出端发送数据之前,将发送三个 K28.5 代码组,以实现同

步。

■ 发送器 PCS 的流水线数据处理导致了一些 "don't cares" (10'hxxx) 在三个同步的

K28.5 代码组之前被发送。

图 1-7. 复位情况下的 8B/10B 编码器行为

clock

tx_digitalreset

dataout[9..0]

K28.5- K28.5- K28.5-

xxx

xxx

K28.5-

K28.5+

K28.5- Dx.y+

During reset

Don’t cares after reset

Synchronization

Normal

operation

通过 tx_forcedisp 和 tx_dispval 端口,编码器支持将运行差异强制成正或负差异。

图 1-8 显示了 tx_forcedisp 和 tx_dispval 端口使用的一个实例,其中的数据表示为

十六进制基数。

图 1-8. 强制运行差异操作

n

n + 1

n + 2

n + 3

n + 4

n + 5

n + 6

n + 7

clock

txin[7..0]

tx_ctrlenable

tx_forcedisp

tx_dispval

BC

Current Disparity

RD-

RD+

RD+

RD-

RD+

RD-

RD-

RD+

dataout[9..0]

17C

283

17C

283

17C

283

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 2

�

1–8

第 1 章 : Cyclone IV 收发器体系结构

发送通道数据通路

在这一实例中,一系列的 K28.5 代码组被连续发送出去。 数据流在正差异 K28.5

(RD+) 与负差异 K28.5 (RD-) 之间交替变化,从而保持一个中性的总体差异。

time n + 1 中的当前运行差异表明 time n + 2 中的 K28.5 需要用负差异来编码。由于

tx_forcedisp 在 time n + 2 上为高电平,并且 tx_dispval 为低电平 ,因此 time n + 2

上的 K28.5 作为正差异代码组被编码。 在相同实例中,time n + 5 上的当前运行差异

表明 time n + 6 上的 K28.5 需要用正差异来编码。由于 tx_forcedisp 在 time n + 6

上为高电平, tx_dispval 也为高电平,因此 time n + 6 上的 K28.5 作为负差异代码组

被编码。

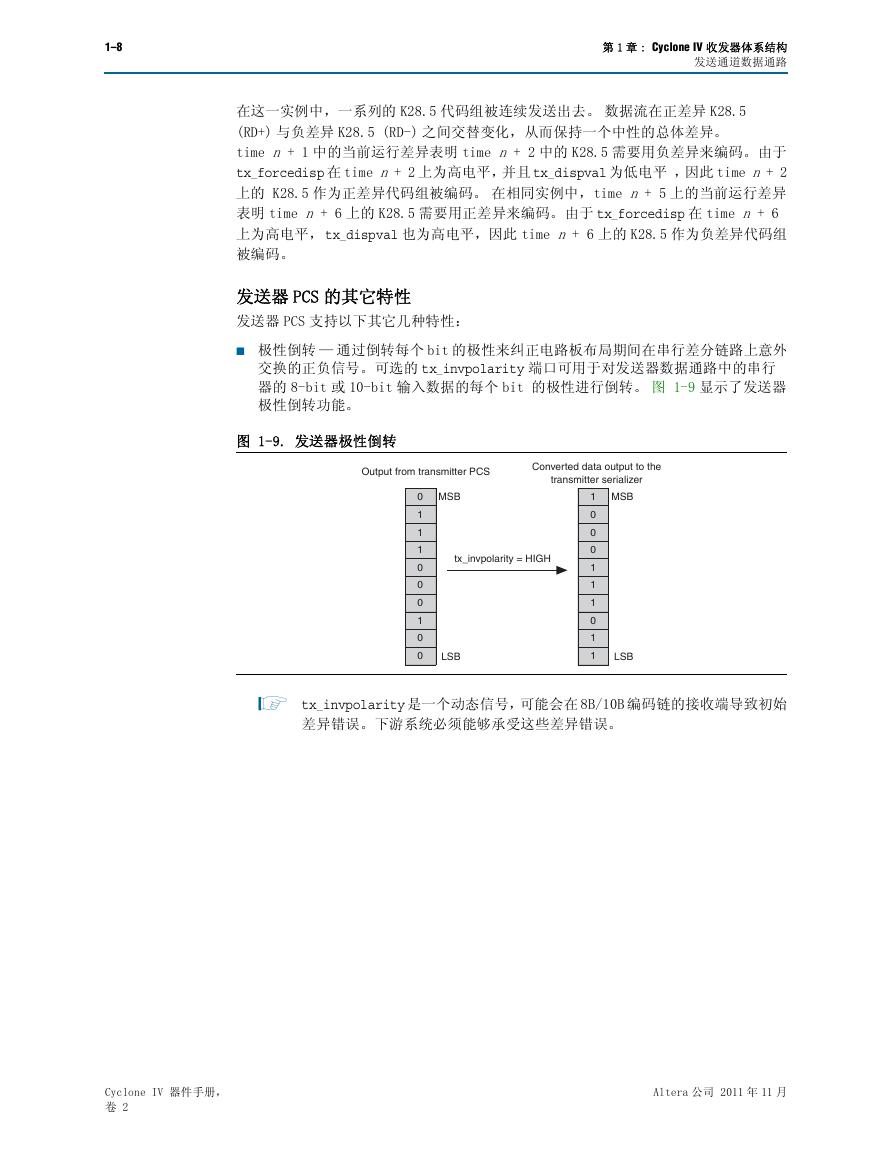

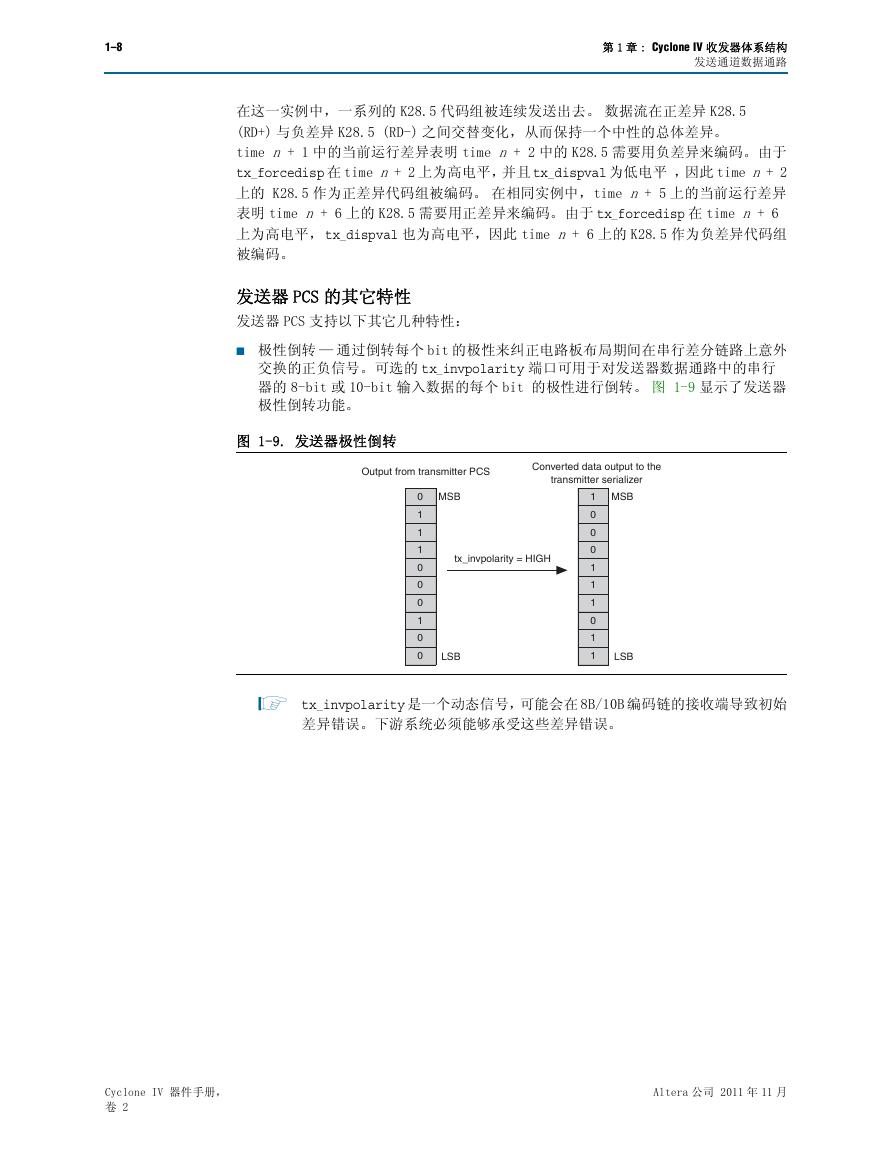

发送器 PCS 的其它特性

发送器 PCS 支持以下其它几种特性:

■ 极性倒转 — 通过倒转每个 bit 的极性来纠正电路板布局期间在串行差分链路上意外

交换的正负信号。可选的 tx_invpolarity 端口可用于对发送器数据通路中的串行

器的 8-bit 或 10-bit 输入数据的每个 bit 的极性进行倒转。 图 1-9 显示了发送器

极性倒转功能。

图 1-9. 发送器极性倒转

Output from transmitter PCS

Converted data output to the

transmitter serializer

0

1

1

1

0

0

0

1

0

0

MSB

tx_invpolarity = HIGH

LSB

1

0

0

0

1

1

1

0

1

1

MSB

LSB

1 tx_invpolarity 是一个动态信号,可能会在 8B/10B 编码链的接收端导致初始

差异错误。下游系统必须能够承受这些差异错误。

Cyclone IV 器件手册,

卷 2

Altera 公司 2011 年 11 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf