Product Specification

Model NO.: 7.5inch HD e-Paper

Product VER:A1

Page 1 of 31

�

Version

A0

A1

Content

New release

Increasing the Brand of components

Date

Producer

Page 2 of 31

�

CONTENTS

1 General Description ... ........................................................................................................... .4

2 Features ... ............................................................................................................................ .... 4

3 Application... .......................................................................................................................... ..4

4 Mechanical Specification ... ................................................................................................... ..4

5 Mechanical Drawing of EPD module ... .............................................................................. ..5

6 Input/Output Terminals ... ...................................................................................................... ..6

7 MCU Interface.. ..................................................................................................................... ..7

7.1 MCU Interface Selection ... ............................................................................................ ..7

7.2 MCU Serial Peripheral Interface (4-wire SPI) ... .......................................................... ..7

7.3 MCU Serial Peripheral Interface (3-wire SPI) ... ........................................................... ..8

8 COMMAND TABLE.. ............................................................................................................. 9

9 Reference Circuit.. ................................................................................................................... .19

10 Absolute Maximum Rating ... ............................................................................................. .21

11 DC Characteristics... .............................................................................................................. .21

12 Serial Peripheral Interface Timing... ..................................................................................... .22

13 Power Consumption... ........................................................................................................... .22

14 Typical Operating Sequence... ............................................................................................. .........23

14.1 Normal Operation Flow ... .......................................................................................... ...23

14.2 Reference program code ... ........................................................................................ ....24

15 Optical Characteristics... ...................................................................................................... ..25

15.1 Specifications ... .......................................................................................................... ..25

15.2 Definition Of Contrast Ratio ... ......................................................................................25

16 Handing Safety And Environment Requirements... .......................................................... ..26

17 Reliability Test... ................................................................................................................... ..28

18 Block Diagram... ................................................................................................................... ..29

20 Point And Line Standard... .................................................................................................... ..30

Page 3 of 31

�

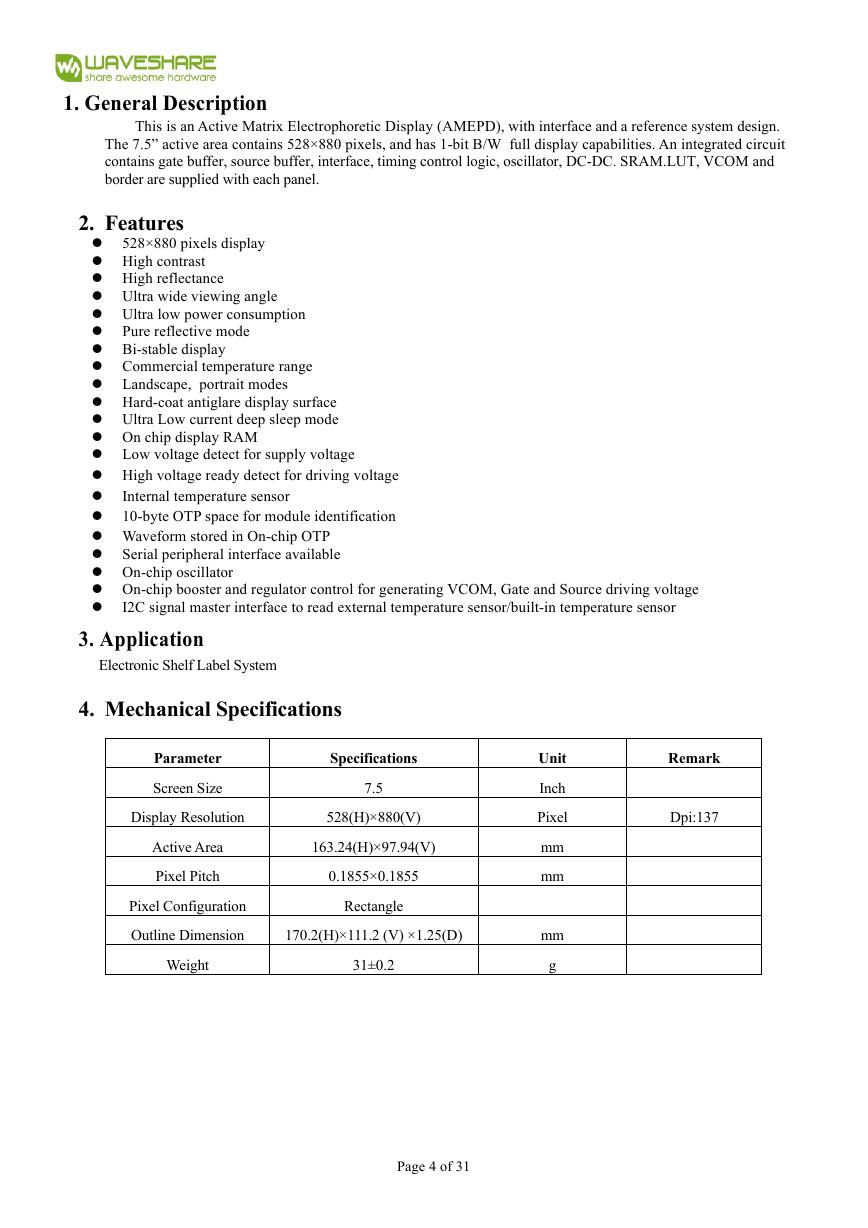

1. General Description

This is an Active Matrix Electrophoretic Display (AMEPD), with interface and a reference system design.

The 7.5” active area contains 528×880 pixels, and has 1-bit B/W full display capabilities. An integrated circuit

contains gate buffer, source buffer, interface, timing control logic, oscillator, DC-DC. SRAM.LUT, VCOM and

border are supplied with each panel.

2. Features

l 528×880 pixels display

l High contrast

l High reflectance

l Ultra wide viewing angle

l Ultra low power consumption

l Pure reflective mode

l Bi-stable display

l Commercial temperature range

l Landscape, portrait modes

l Hard-coat antiglare display surface

l Ultra Low current deep sleep mode

l On chip display RAM

l Low voltage detect for supply voltage

l High voltage ready detect for driving voltage

l

l 10-byte OTP space for module identification

l Waveform stored in On-chip OTP

l Serial peripheral interface available

l On-chip oscillator

l On-chip booster and regulator control for generating VCOM, Gate and Source driving voltage

l

3. Application

I2C signal master interface to read external temperature sensor/built-in temperature sensor

Internal temperature sensor

Electronic Shelf Label System

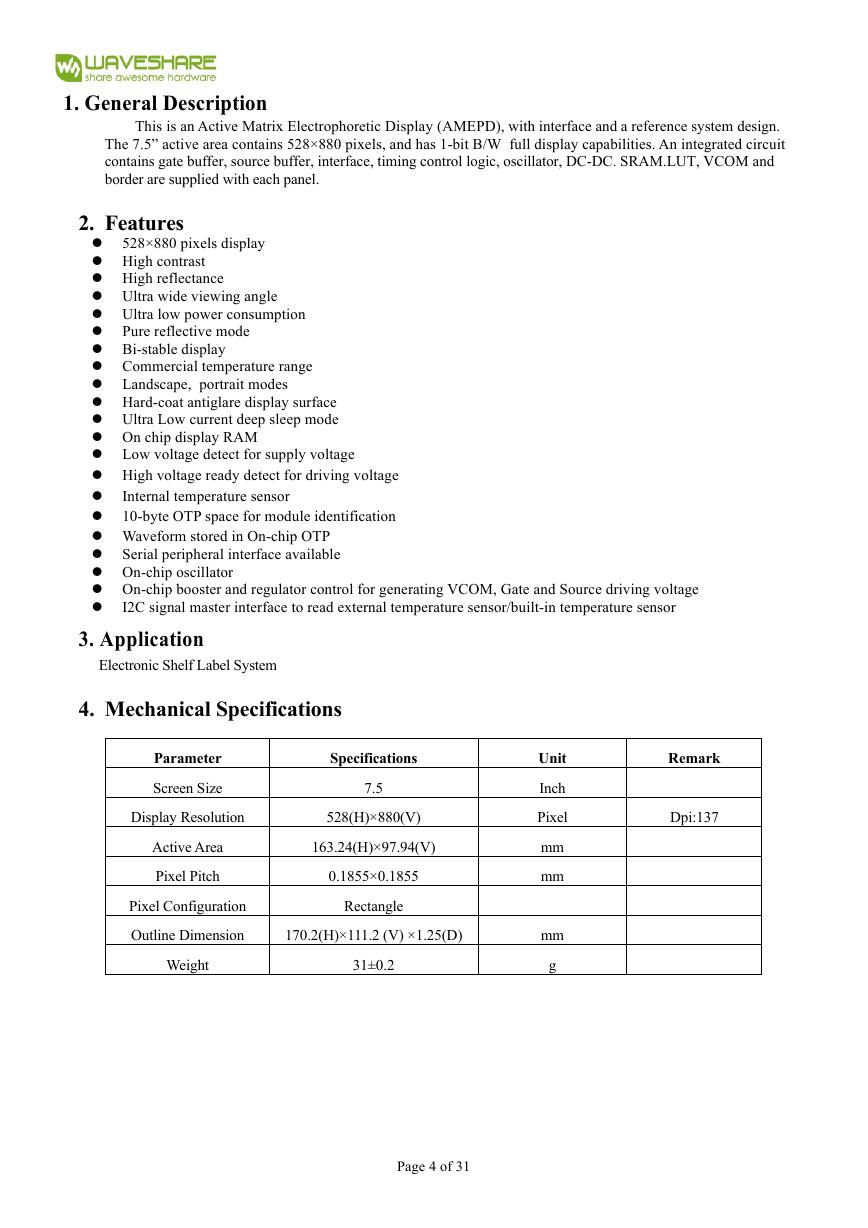

4. Mechanical Specifications

Parameter

Screen Size

Specifications

7.5

Display Resolution

528(H)×880(V)

Active Area

Pixel Pitch

Pixel Configuration

Outline Dimension

Weight

163.24(H)×97.94(V)

0.1855×0.1855

Rectangle

170.2(H)×111.2 (V) ×1.25(D)

31±0.2

Unit

Inch

Pixel

mm

mm

mm

g

Remark

Dpi:137

Page 4 of 31

�

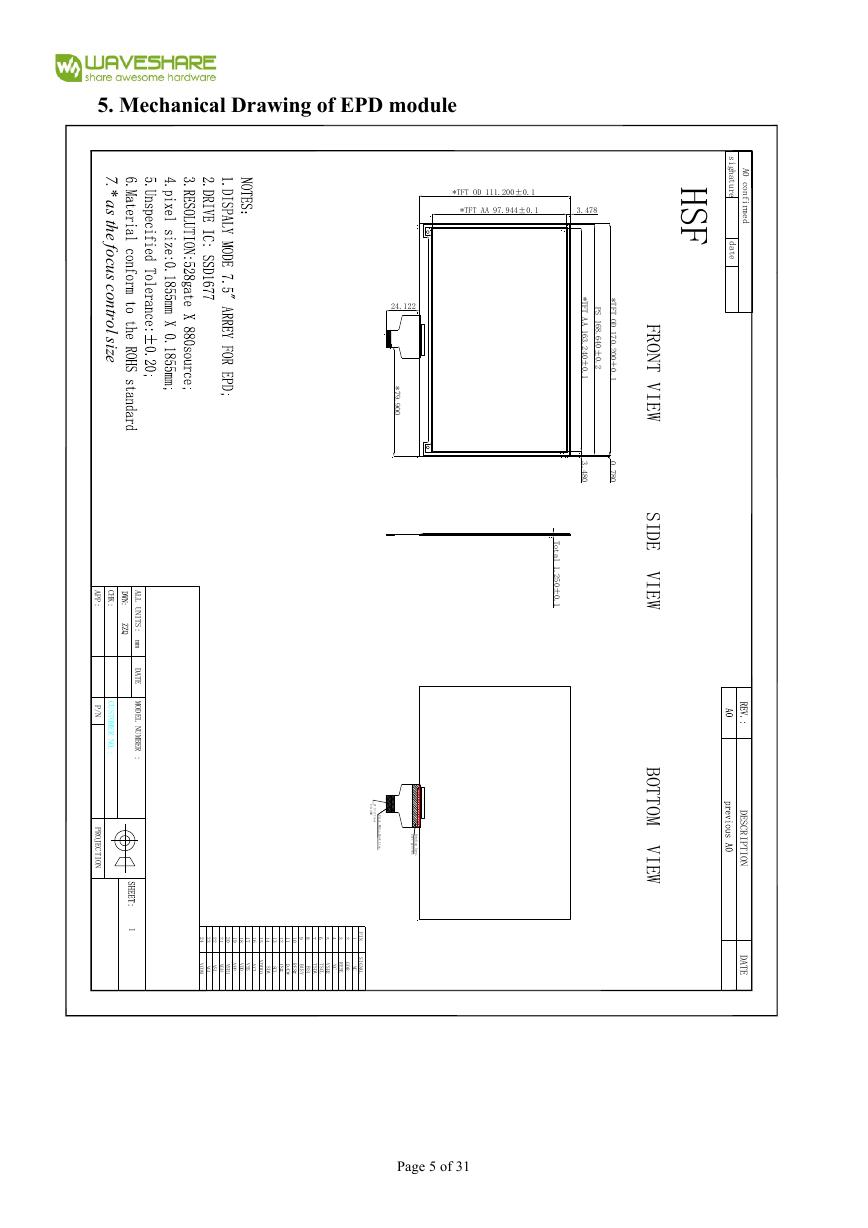

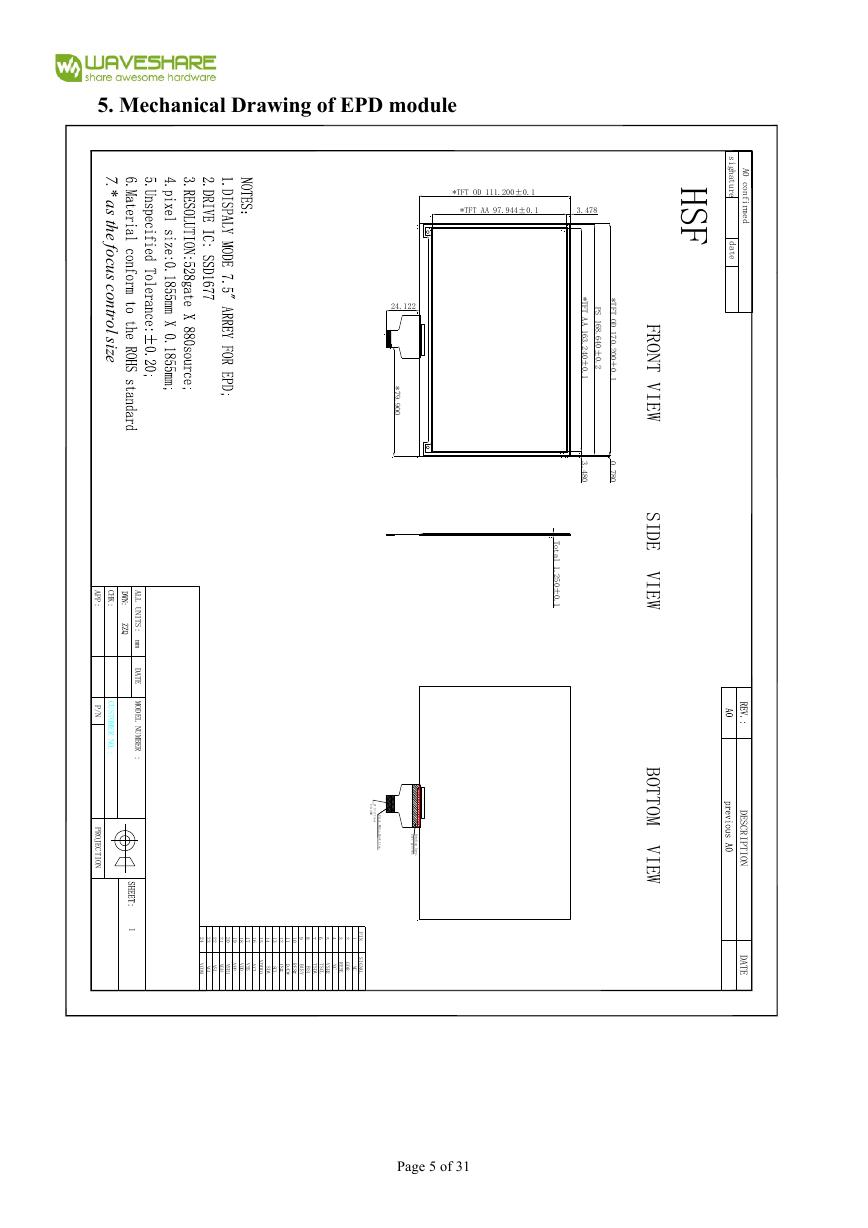

5. Mechanical Drawing of EPD module

7

.

*

a

s

t

h

e

f

o

c

u

s

c

o

n

t

r

o

l

s

i

z

e

0

C

=

8

B

A

.

3

0

B

4

3

4

=

C

1

4

.

0

.

2

7

:

.

.

#

=

2

C

A

B

4

=

.

9

4

2

B

8

=

B5B3Y

B5B00Y

,

7

A

5

0

H

S

R

K

N

U

J

I

V

N

L

M

G

W

U

J

I

G

W

J

B

5

B

0

0

*

Y

A

*

,

*

Y

B

5

B

3

Y

,

,

B

S

W

G

P

Y

5

=

B

D

8

4

E

A

8

3

4

D

8

4

E

1

B

B

D

8

4

E

.

3

4

A

2

8

B

8

=

3

0

B

4

B

/

8

A

W

N

K

K

J

R

J

U

U

N

R

W

E

7

N

W

J

G

U

O

N

R

J

A

S

K

W

T

U

S

H

J

V

V

1

J

R

I

N

R

L

0

U

J

G

,

*

*,

D

2

D

6

D

A

D

6

7

D

A

7

D

D

3

3

D

A

A

D

2

8

D

3

3

8

A

3

0

A

2

2

A

3

#

2

4

A

1

C

A

F

B

A

3

0

B

A

2

D

A

7

1

A

=

2

6

3

4

A

4

=

2

8

=

A

8

6

=

0

Page 5 of 31

�

6. Input/Output Terminals

Pin #

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

23

24

Single

NC

GDR

RESE

NC

VSH2

TSCL

TSDA

BS1

BUSY

RES #

D/C #

CS #

SCL

SDA

VDDIO

VCI

VSS

VDD

VPP

VSH1

VGH

VSL

VGL

Description

Remark

No connection and do not connect with other NC pins

Keep Open

N-Channel MOSFET Gate Drive Control

Current Sense Input for the Control Loop

No connection and do not connect with other NC pins e

Keep Open

Positive Source driving voltage

I2C Interface to digital temperature sensor Clock pin

I2C Interface to digital temperature sensor Date pin

Note 6-5

Note 6-4

Note 6-3

Note 6-2

Note 6-1

Bus selection pin

Busy state output pin

Reset

Data /Command control pin

Chip Select input pin

serial clock pin (SPI)

serial data pin (SPI)

Power for interface logic pins

Power Supply pin for the chip

Ground

Core logic power pin

Power Supply for OTP Programming

Positive Source driving voltage

Power Supply pin for Positive Gate driving voltage and

VSH

Negative Source driving voltage

Power Supply pin for Negative Gate driving voltage,

VCOM and VSL

VCOM

VCOM driving voltage

Note 6-1: This pin (CS#) is the chip select input connecting to the MCU. The chip is enabled for MCU

communication:only when CS# is pulled LOW.

Note 6-2: This pin (D/C#) is Data/Command control pin connecting to the MCU. When the pin is pulled HIGH,

the data will be interpreted as data. When the pin is pulled LOW, the data will be interpreted as command.

Note 6-3: This pin (RES#) is reset signal input. The Reset is active low.

Note 6-4: This pin (BUSY) is Busy state output pin. When Busy is High the operation of chip should not be

interrupted and any commands should not be issued to the module. The driver IC will put Busy pin High when

the driver IC is working such as:

- Outputting display waveform; or

Page 6 of 31

�

- Communicating with digital temperature sensor

Note 6-5: This pin (BS1) is for 3-line SPI or 4-line SPI selection. When it is “Low”, 4-line SPI is selected.

When it is “High”, 3-line SPI (9 bits SPI) is selected.

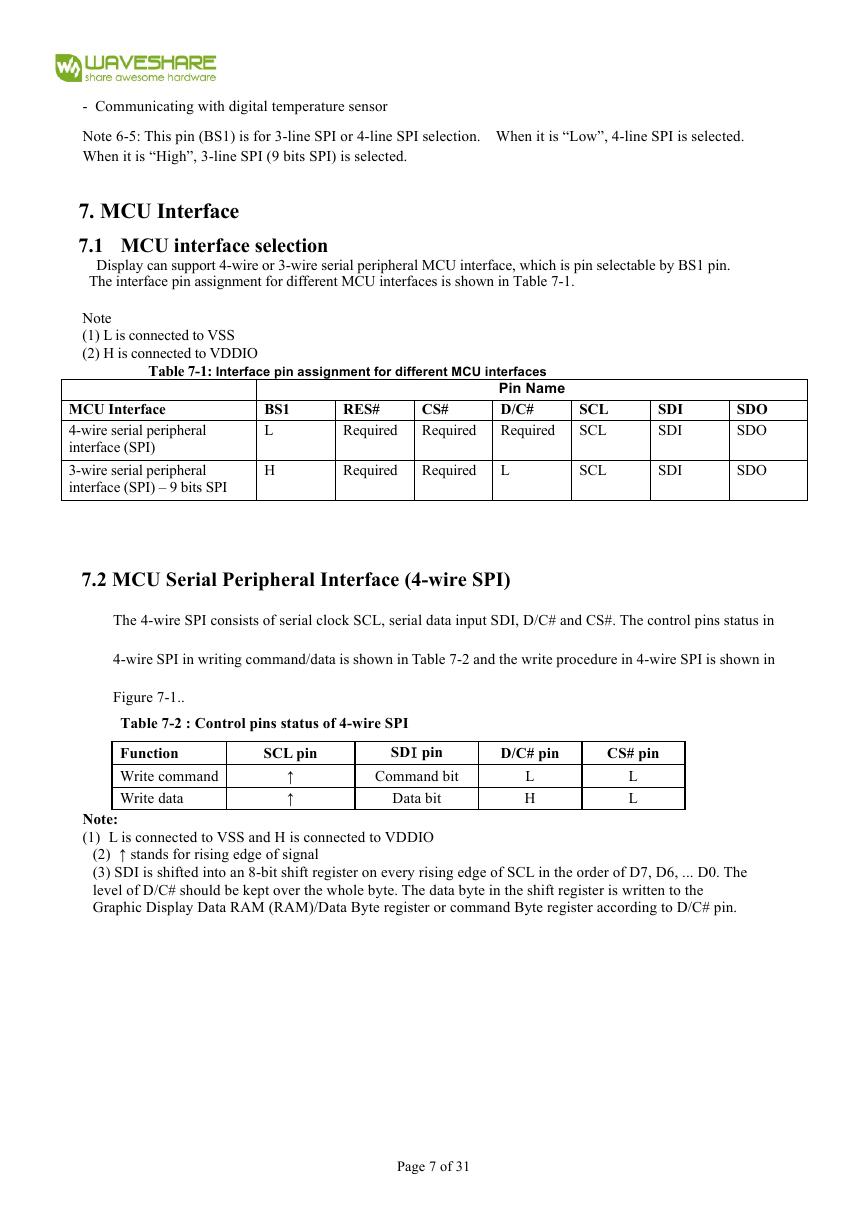

7. MCU Interface

7.1 MCU interface selection

Display can support 4-wire or 3-wire serial peripheral MCU interface, which is pin selectable by BS1 pin.

The interface pin assignment for different MCU interfaces is shown in Table 7-1.

Table 7-1: Interface pin assignment for different MCU interfaces

Note

(1) L is connected to VSS

(2) H is connected to VDDIO

MCU Interface

4-wire serial peripheral

interface (SPI)

3-wire serial peripheral

interface (SPI) – 9 bits SPI

BS1

L

H

RES#

Required

CS#

Required

Pin Name

D/C#

Required

Required

Required

L

SCL

SCL

SCL

SDI

SDI

SDI

SDO

SDO

SDO

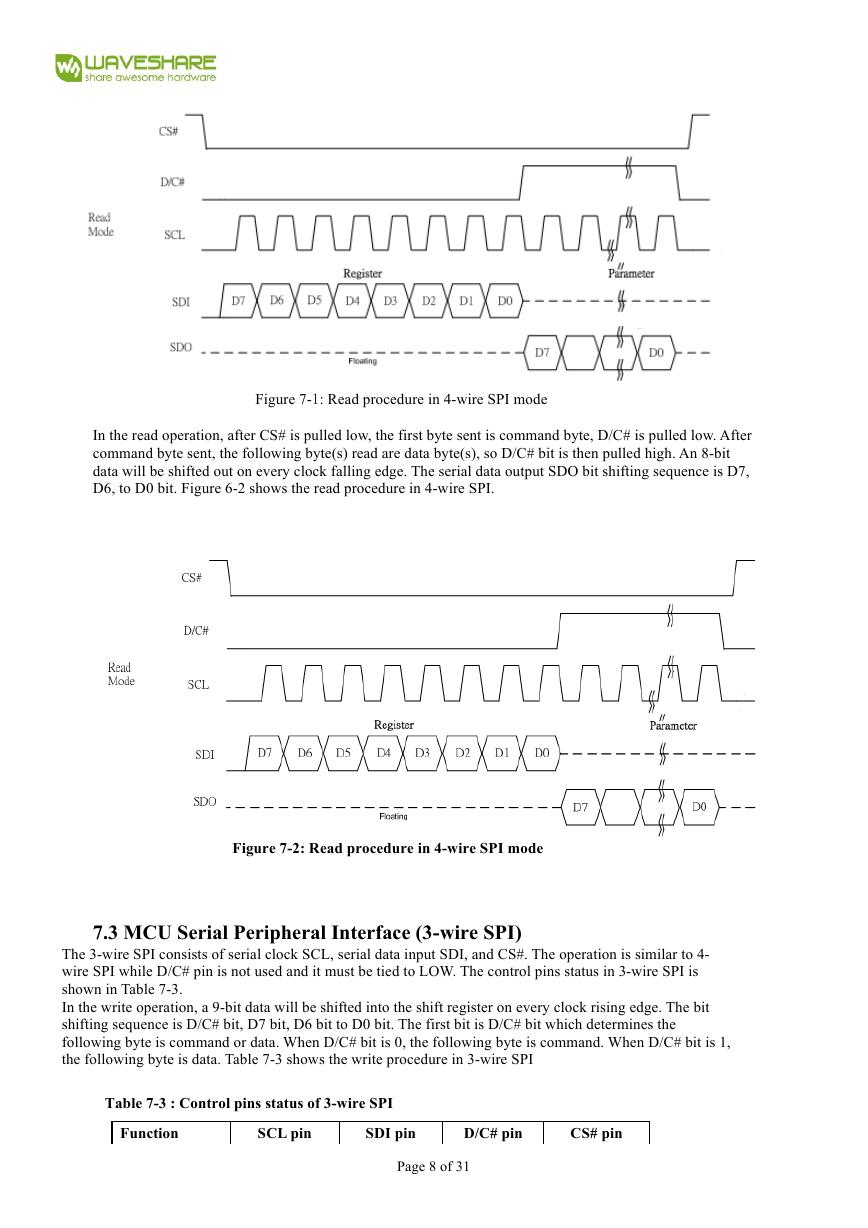

7.2 MCU Serial Peripheral Interface (4-wire SPI)

The 4-wire SPI consists of serial clock SCL, serial data input SDI, D/C# and CS#. The control pins status in

4-wire SPI in writing command/data is shown in Table 7-2 and the write procedure in 4-wire SPI is shown in

Figure 7-1..

Table 7-2 : Control pins status of 4-wire SPI

Function

Write command

Write data

SCL pin

↑

↑

SD pin

Command bit

Data bit

D/C# pin

CS# pin

L

H

L

L

Note:

(1) L is connected to VSS and H is connected to VDDIO

(2) ↑ stands for rising edge of signal

(3) SDI is shifted into an 8-bit shift register on every rising edge of SCL in the order of D7, D6, ... D0. The

level of D/C# should be kept over the whole byte. The data byte in the shift register is written to the

Graphic Display Data RAM (RAM)/Data Byte register or command Byte register according to D/C# pin.

Page 7 of 31

�

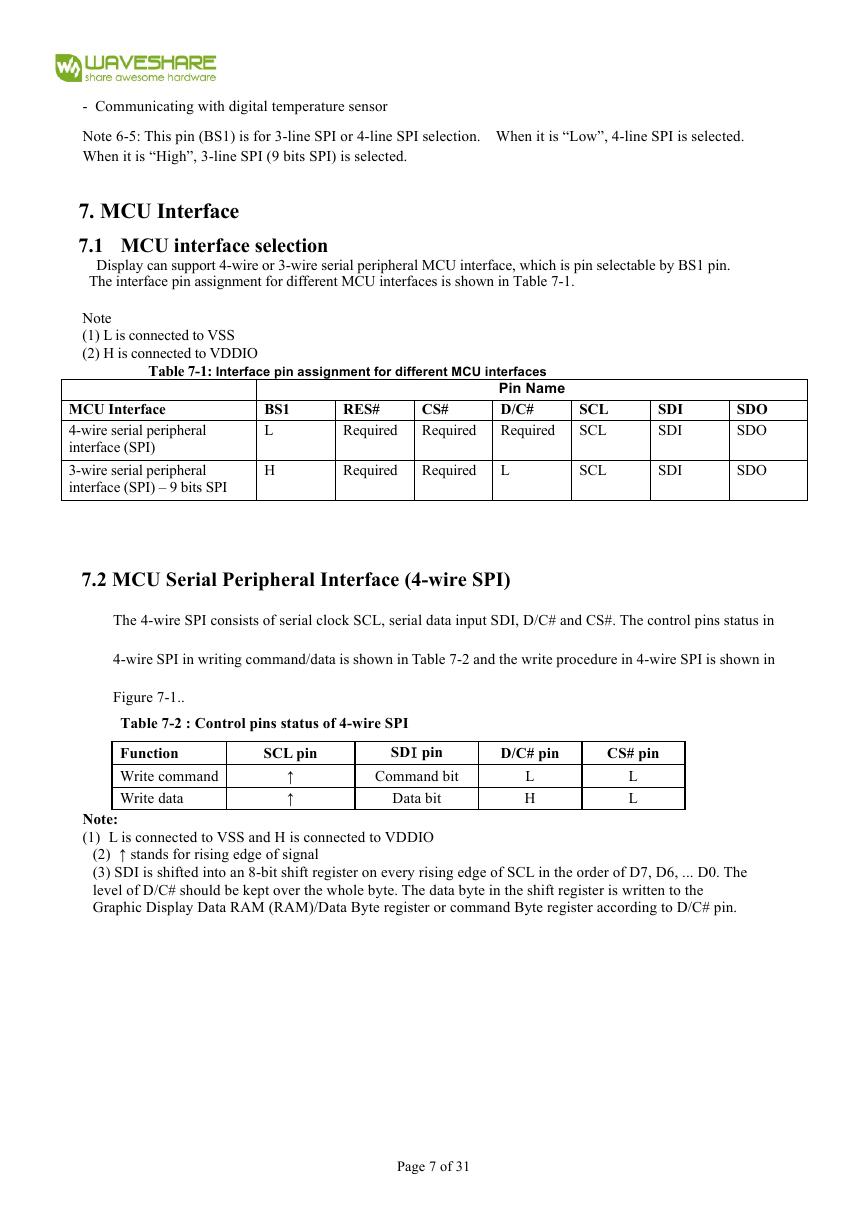

Figure 7- : Read procedure in 4-wire SPI mode

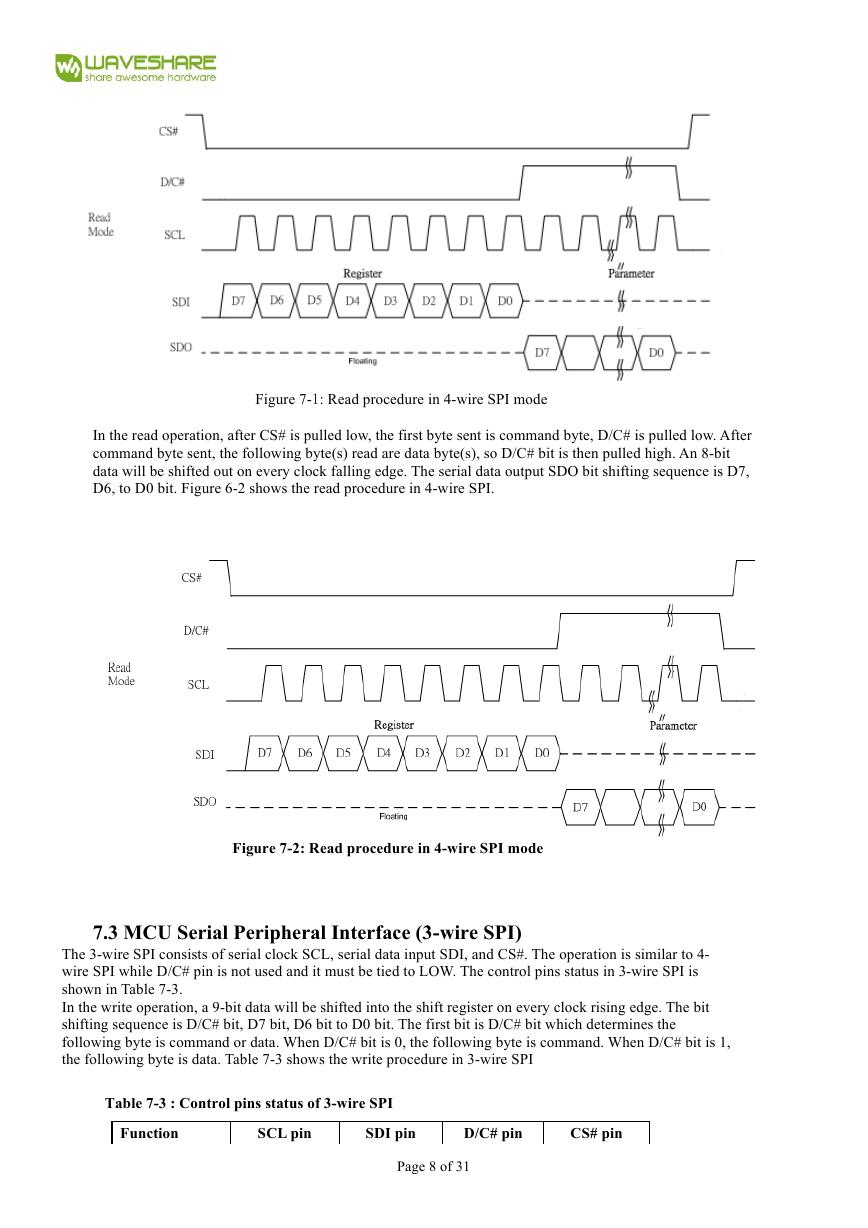

In the read operation, after CS# is pulled low, the first byte sent is command byte, D/C# is pulled low. After

command byte sent, the following byte(s) read are data byte(s), so D/C# bit is then pulled high. An 8-bit

data will be shifted out on every clock falling edge. The serial data output SDO bit shifting sequence is D7,

D6, to D0 bit. Figure 6-2 shows the read procedure in 4-wire SPI.

Figure 7-2: Read procedure in 4-wire SPI mode

7.3 MCU Serial Peripheral Interface (3-wire SPI)

The 3-wire SPI consists of serial clock SCL, serial data input SDI, and CS#. The operation is similar to 4-

wire SPI while D/C# pin is not used and it must be tied to LOW. The control pins status in 3-wire SPI is

shown in Table 7-3.

In the write operation, a 9-bit data will be shifted into the shift register on every clock rising edge. The bit

shifting sequence is D/C# bit, D7 bit, D6 bit to D0 bit. The first bit is D/C# bit which determines the

following byte is command or data. When D/C# bit is 0, the following byte is command. When D/C# bit is 1,

the following byte is data. Table 7-3 shows the write procedure in 3-wire SPI

Table 7-3 : Control pins status of 3-wire SPI

Function

SCL pin

SDI pin

D/C# pin

CS# pin

Page 8 of 31

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf