Contents

Contents

RReevviissiioonn HHiissttoorryy

CCoonntteennttss

11.. BBaassiicc SSppeecciiffiiccaattiioonnss

1.1 Display Specifications

1.2 Mechanical Specifications

1.3 Active Area / Memory Mapping & Pixel Construction

1.4 Mechanical Drawing

1.5 Pin Definition

22.. AAbbssoolluuttee MMaaxxiimmuumm RRaattiinnggss

33.. Optics & EElleeccttrriiccaall CChhaarraacctteerriissttiiccss

3.1 Optics Characteristics

3.2 DC Characteristics

3.3 AC Characteristics

3.3.1 68XX-Series MPU Parallel Interface Characteristics

3.3.2 80XX-Series MPU Parallel Interface Characteristics

3.3.3 Serial Interface Characteristics (4-wire SPI)

3.3.4 Serial Interface Characteristics (3-wire SPI)

3.3.5 I2C Interface Characteristics

44.. FFuunnccttiioonnaall SSppeecciiffiiccaattiioonn

4.1 Commands

4.2 Power down and Power up Sequence

4.2.1 Power up Sequence

4.2.2 Power down Sequence

4.3 Reset Circuit

4.4 Actual Application Example

4.4.1 VCC Supplied Externally

4.4.2 VCC Generated by Internal DC/DC Circuit

55.. RReelliiaabbiilliittyy

5.1 Contents of Reliability Tests

5.2 Failure Check Standard

66.. OOuuttggooiinngg QQuuaalliittyy CCoonnttrrooll SSppeecciiffiiccaattiioonnss

6.1 Environment Required

6.2 Sampling Plan

6.3 Criteria & Acceptable Quality Level

6.3.1 Cosmetic Check (Display Off) in Non-Active Area

6.3.2 Cosmetic Check (Display Off) in Active Area

6.3.3 Pattern Check (Display On) in Active Area

77.. PPaacckkaaggee SSppeecciiffiiccaattiioonnss

88.. PPrreeccaauuttiioonnss WWhheenn UUssiinngg TThheessee OOEELL DDiissppllaayy MMoodduulleess

8.1 Handling Precautions

8.2 Storage Precautions

8.3 Designing Precautions

8.4 Precautions when disposing of the OEL display modules

8.5 Other Precautions

WWaarrrraannttyy

NNoottiiccee

�

11.. BBaassiicc SSppeecciiffiiccaattiioonnss

1.1 Display Specifications

1) Display Mode:

2) Display Color:

3) Drive Duty:

Passive Matrix

Monochrome (White)

1/64 Duty

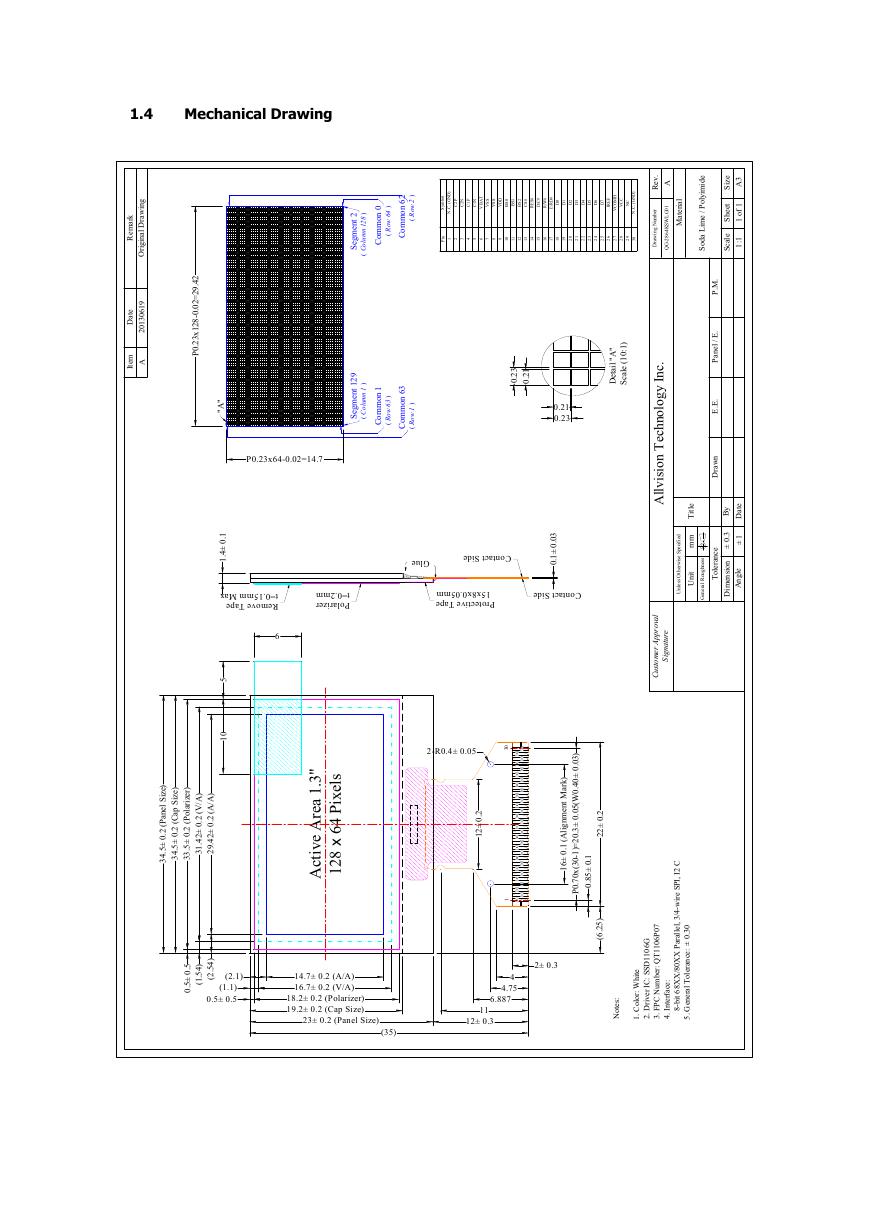

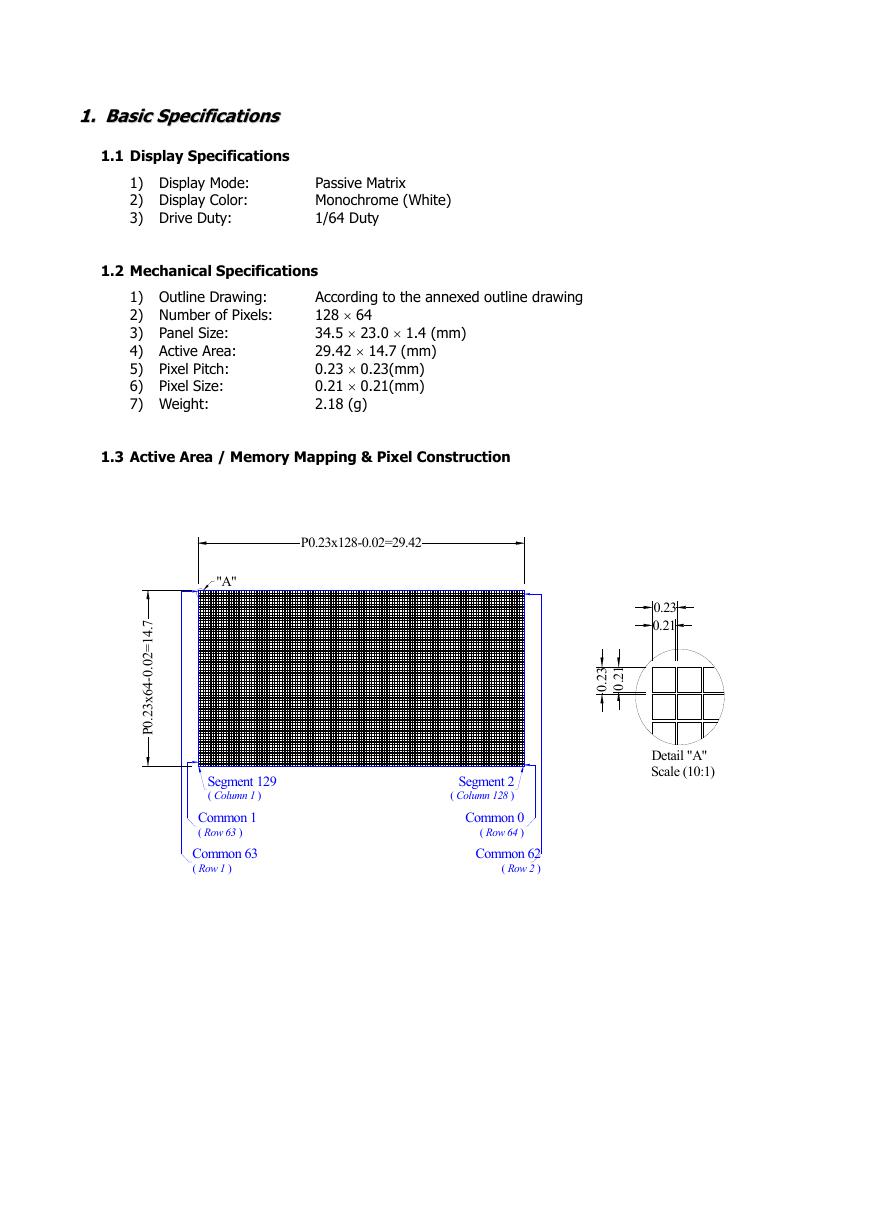

1.2 Mechanical Specifications

1) Outline Drawing:

2) Number of Pixels:

3) Panel Size:

4) Active Area:

5) Pixel Pitch:

6) Pixel Size:

7) Weight:

According to the annexed outline drawing

128 64

34.5 23.0 1.4 (mm)

29.42 14.7 (mm)

0.23 0.23(mm)

0.21 0.21(mm)

2.18 (g)

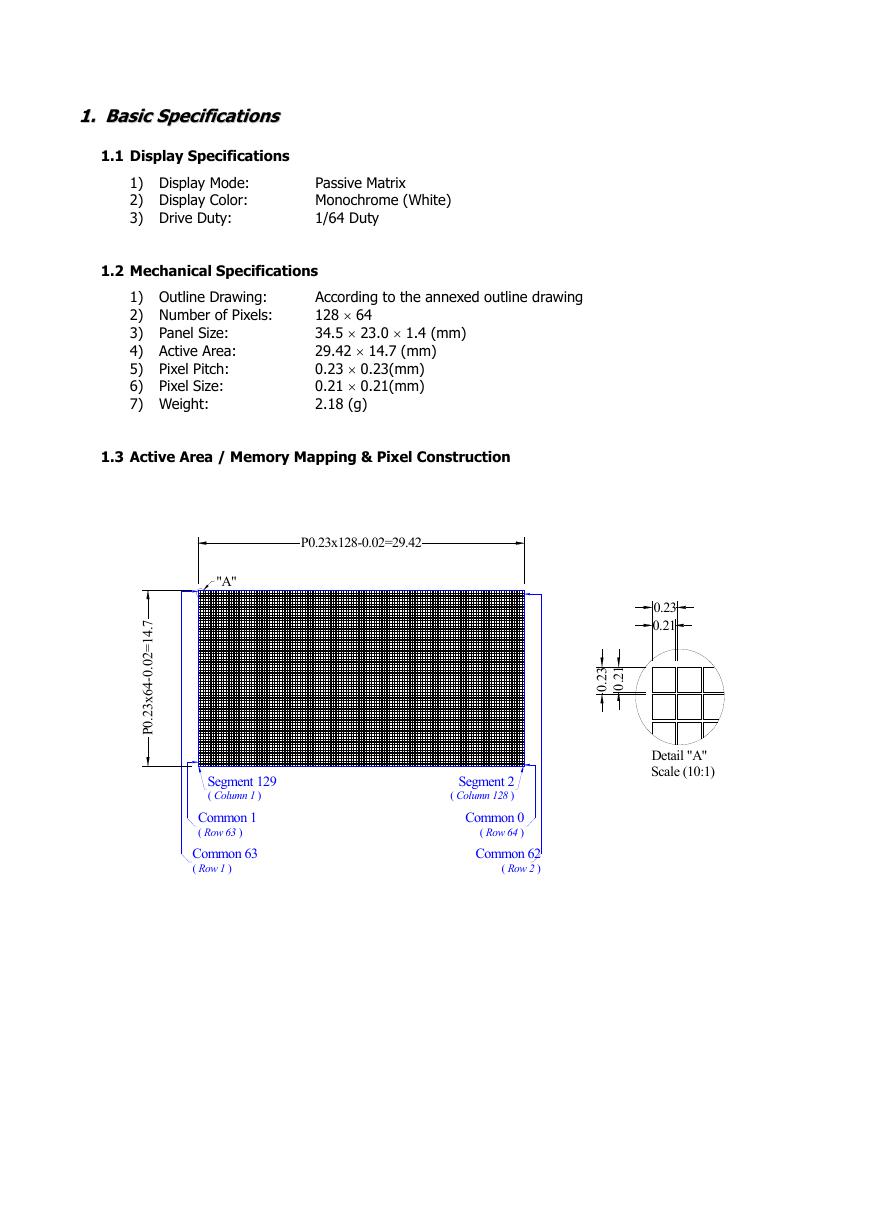

1.3 Active Area / Memory Mapping & Pixel Construction

P0.23x128-0.02=29.42

"A"

.

7

4

1

=

2

0

.

0

-

4

6

x

3

2

.

0

P

Segment 129

( Column 1 )

Common 1

( Row 63 )

Common 63

( Row 1 )

Segment 2

( Column 128 )

Common 0

( Row 64 )

Common 62

( Row 2 )

3

2

.

0

1

2

.

0

0.23

0.21

Detail "A"

Scale (10:1)

�

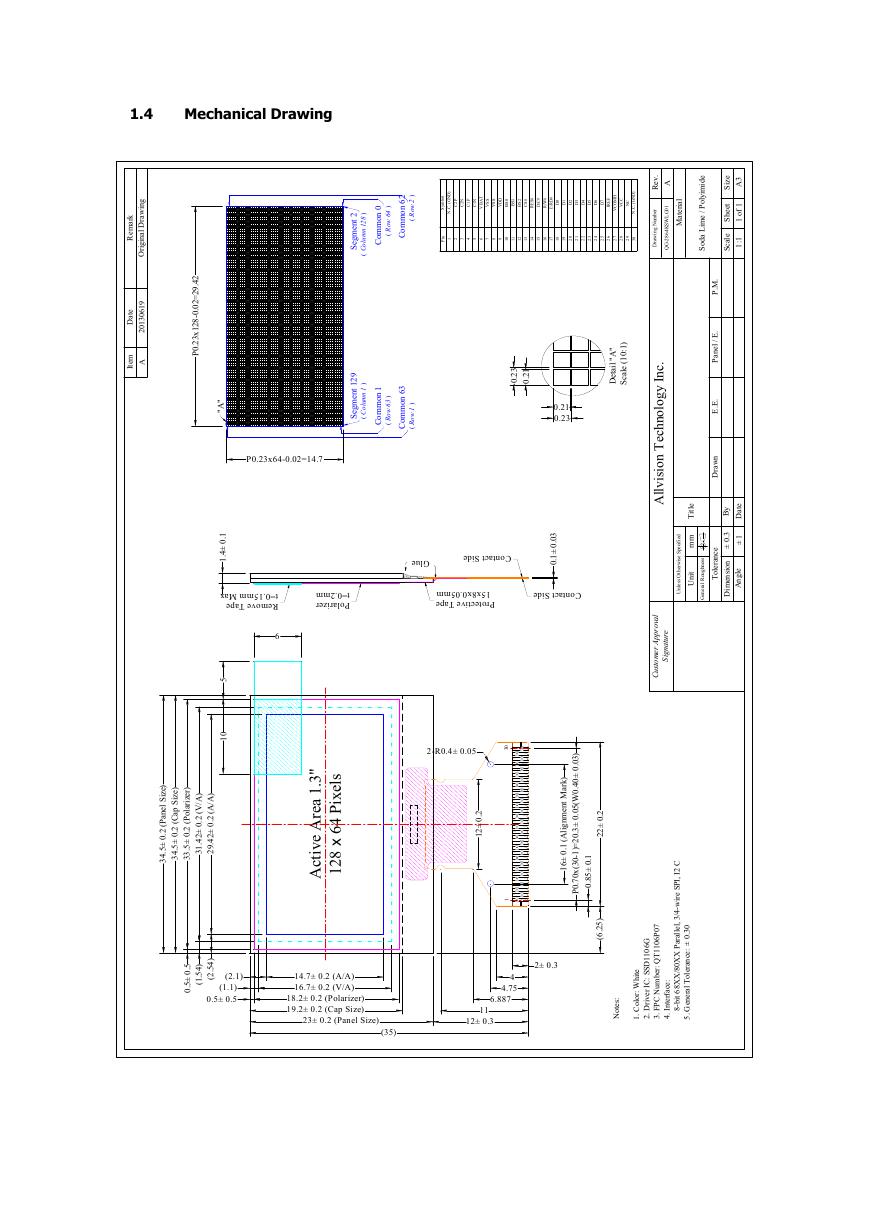

1.4

Mechanical Drawing

)

2

w

o

R

(

2

6

n

o

m

m

o

C

)

4

6

w

o

R

(

0

n

o

m

m

o

C

2

t

n

e

m

g

e

S

)

8

2

1

n

m

u

l

o

C

(

9

2

1

t

n

e

m

g

e

S

)

1

n

m

u

l

o

C

(

.

.

2

4

9

2

=

2

0

0

-

8

2

1

x

3

2

0

P

.

"

A

"

P0.23x64-0.02=14.7

1

n

o

m

m

o

C

)

3

6

w

o

R

(

3

6

n

o

m

m

o

C

)

1

w

o

R

(

k

r

a

m

e

R

g

n

i

w

a

r

D

l

a

n

i

g

i

r

O

e

t

a

D

9

1

6

0

3

1

0

2

m

e

t

I

A

)

e

z

i

S

l

e

n

a

P

(

2

.

0

±

5

.

4

3

)

e

z

i

S

p

a

C

(

2

.

0

±

5

4

3

.

)

r

e

z

i

r

a

l

o

P

(

2

.

0

±

5

.

3

3

)

A

V

/

(

2

.

0

±

2

4

.

1

3

)

4

5

.

1

(

5

.

0

±

5

.

0

)

A

A

/

(

2

.

0

±

2

4

.

9

2

)

4

5

.

2

(

l

o

b

m

y

S

)

D

N

G

(

.

.

C

N

P

2

C

N

2

C

P

1

C

N

1

C

T

A

B

V

S

S

V

S

S

V

D

D

V

0

S

B

1

S

B

2

S

B

#

S

C

#

S

E

R

#

C

D

/

#

W

R

/

#

D

R

E

/

0

D

1

D

2

D

3

D

4

D

5

D

6

D

7

D

F

E

R

I

H

M

O

C

V

C

C

V

C

N

)

D

N

G

(

.

.

C

N

n

i

P

5 76431

2

8

9

0

1

1

1

2

1

3

1

4

1

5

1

6

1

7

1

8

1

9

1

0

2

1

2

2

2

3

2

4

2

5

2

6

2

7

2

8

2

9

2

0

3

.

v

e

R

A

r

e

b

m

u

N

g

n

i

w

a

r

D

1

0

G

L

W

S

K

4

6

8

2

-

G

Q

l

a

i

r

e

t

a

M

e

d

i

m

i

y

l

o

P

i

/

e

m

L

a

d

o

S

e

z

i

S

3

A

t

e

e

h

S

1

f

o

1

e

l

a

c

S

1

:

1

.

M

P

.

)

1

:

0

1

(

e

l

a

c

S

"

A

"

l

i

a

t

e

D

3

2

0

.

1

2

0

.

0.21

0.23

.

c

n

I

y

g

o

l

o

n

h

c

e

T

n

o

i

s

i

v

l

l

A

.

E

/

l

e

n

a

P

.

E

E

.

n

w

a

r

D

e

l

t

i

T

m

m

t

i

n

U

d

e

i

f

i

c

e

p

S

e

s

i

w

r

e

h

t

O

s

s

e

l

n

U

y

B

e

t

a

D

.

3

0

±

1

±

n

o

i

s

n

e

m

D

i

e

l

g

n

A

e

c

n

a

r

e

l

o

T

s

s

e

n

h

g

u

o

R

l

a

r

e

n

e

G

.

1

0

±

4

.

1

Glue

Contact Side

.

3

0

0

±

1

.

0

t=0.15mm Max

Remove Tape

t=0.2mm

Polarizer

15x8x0.05mm

Protective Tape

Contact Side

6

5

0

1

.

"

3

1

a

e

r

A

e

v

i

t

c

A

s

l

e

x

i

P

4

6

x

8

2

1

2-R0.4± 0.05

0

3

N.C. (GND)

.

2

0

±

2

1

VCC

IREF

D6

D4

D2

D0

R/W#

RES#

BS2

NC

VSS

VBAT

C1P

C2P

NC

VCOMH

D7

D5

D3

D1

E/RD#

D/C#

CS#

BS1

VDD

VSS

C1N

C2N

1

N.C. (GND)

(2.1)

(1.1)

0.5± 0.5

14.7± 0.2 (A/A)

16.7± 0.2 (V/A)

18.2± 0.2 (Polarizer)

19.2± 0.2 (Cap Size)

23± 0.2 (Panel Size)

4

4.75

6.887

11

12± 0.3

(35)

l

a

v

o

r

p

p

A

r

e

m

o

t

s

u

C

e

r

u

t

a

n

g

i

S

)

3

0

.

.

0

±

0

4

0

W

(

5

0

.

.

0

±

3

0

2

=

)

1

-

0

3

(

x

0

7

.

0

P

1

.

0

±

5

8

.

0

.

2

0

±

2

2

C

2

I

,

I

P

S

e

r

i

w

-

4

/

3

,

l

e

l

l

a

r

a

P

X

X

0

8

/

X

X

8

6

t

i

b

-

8

0

3

.

0

±

:

e

c

n

a

r

e

l

o

T

l

a

r

e

n

e

G

.

5

:

e

c

a

f

r

e

t

n

I

.

4

7

0

P

6

0

1

1

T

Q

:

r

e

b

m

u

N

C

P

F

G

6

0

1

1

D

S

S

:

C

I

r

e

v

i

r

D

.

2

.

3

e

t

i

h

W

:

r

o

l

o

C

.

1

)

5

2

.

6

(

:

s

e

t

o

N

)

k

r

a

M

t

n

e

m

n

g

i

l

A

(

1

.

0

±

6

1

2± 0.3

�

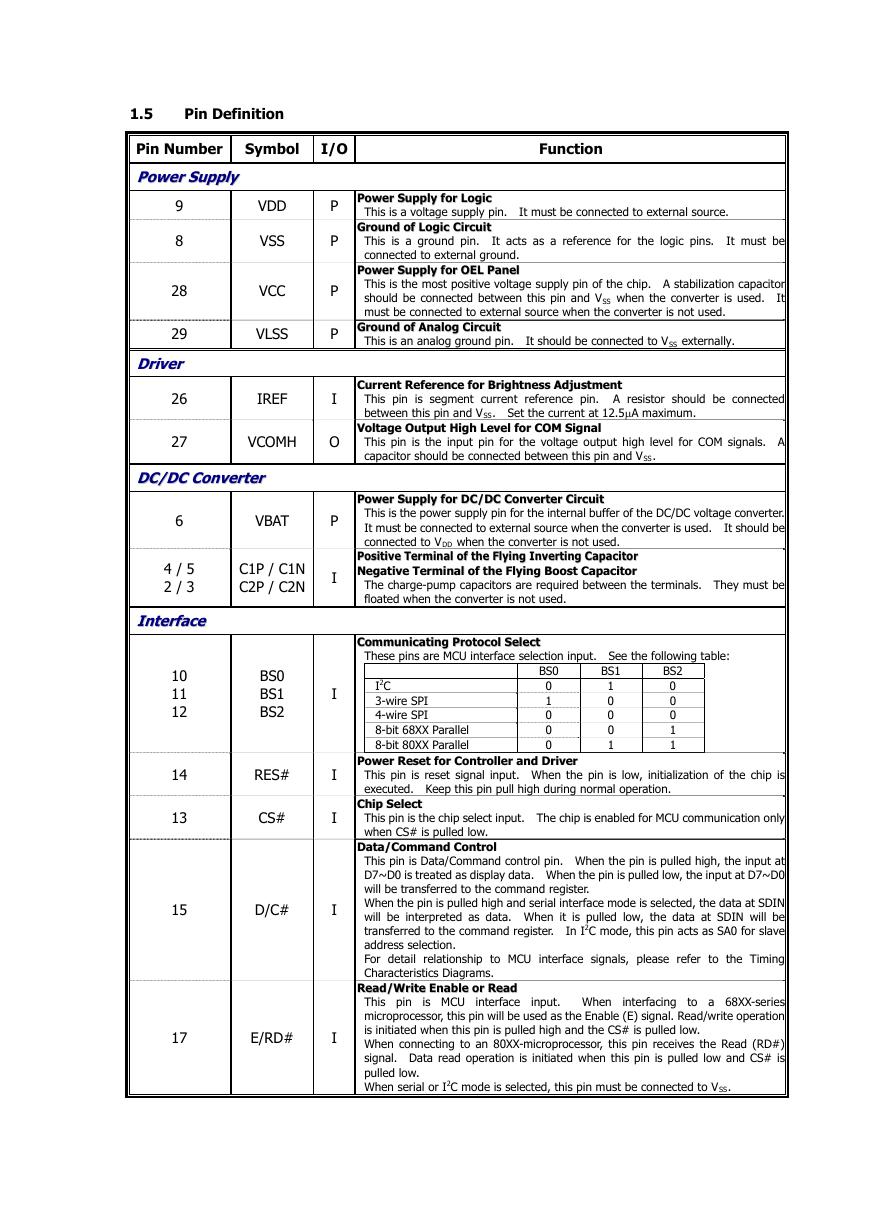

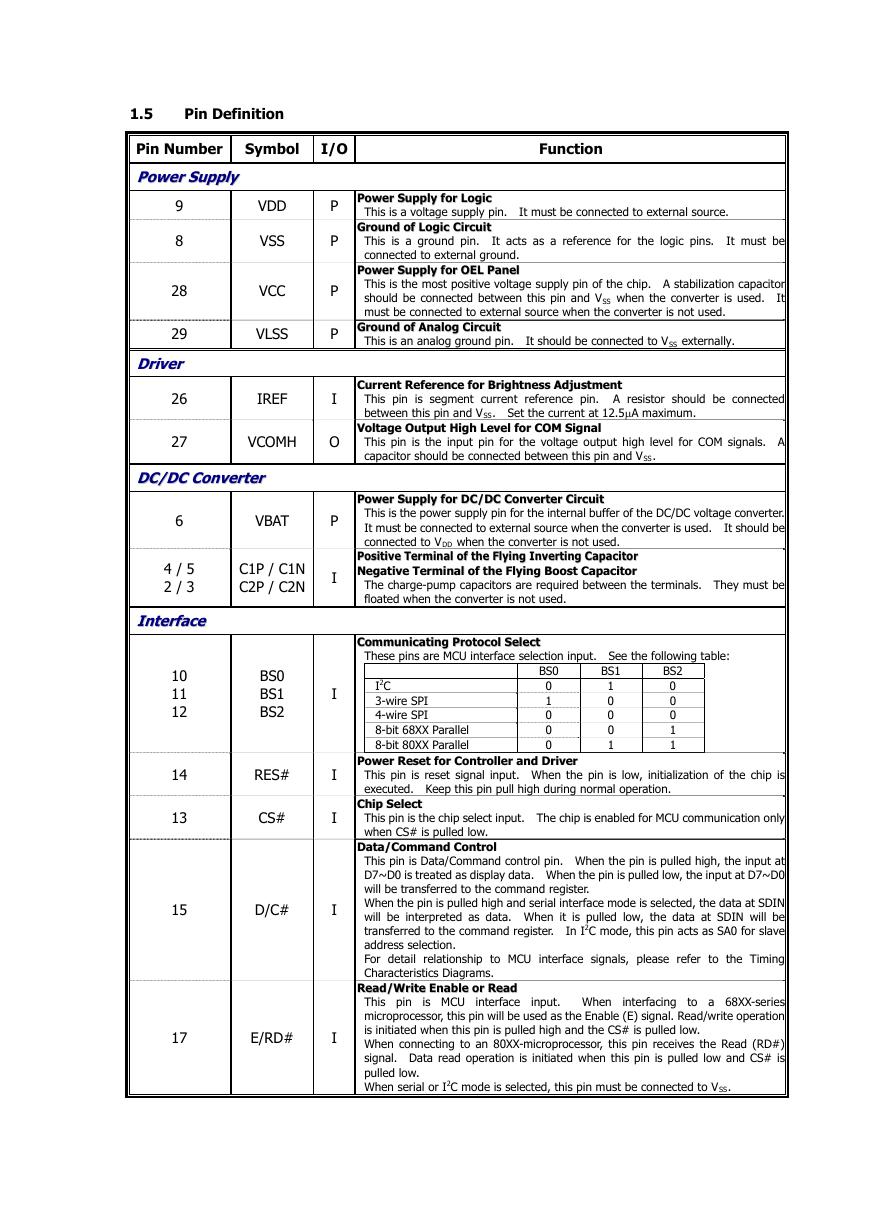

1.5

Pin Definition

Pin Number Symbol

PPoowweerr SSuuppppllyy

I/O

Function

9

8

28

29

DDrriivveerr

26

27

VDD

VSS

VCC

VLSS

IREF

VCOMH

DDCC//DDCC CCoonnvveerrtteerr

6

VBAT

4 / 5

2 / 3

C1P / C1N

C2P / C2N

IInntteerrffaaccee

10

11

12

14

13

BS0

BS1

BS2

RES#

CS#

I

O

P

I

I

I

I

15

D/C#

I

17

E/RD#

I

P

P PPoowweerr SSuuppppllyy ffoorr LLooggiicc

This is a voltage supply pin. It must be connected to external source.

GGrroouunndd ooff LLooggiicc CCiirrccuuiitt

This is a ground pin. It acts as a reference for the logic pins. It must be

connected to external ground.

PPoowweerr SSuuppppllyy ffoorr OOEELL PPaanneell

This is the most positive voltage supply pin of the chip. A stabilization capacitor

should be connected between this pin and VSS when the converter is used. It

must be connected to external source when the converter is not used.

P

P GGrroouunndd ooff AAnnaalloogg CCiirrccuuiitt

This is an analog ground pin. It should be connected to VSS externally.

CCuurrrreenntt RReeffeerreennccee ffoorr BBrriigghhttnneessss AAddjjuussttmmeenntt

This pin is segment current reference pin. A resistor should be connected

between this pin and VSS. Set the current at 12.5A maximum.

VVoollttaaggee OOuuttppuutt HHiigghh LLeevveell ffoorr CCOOMM SSiiggnnaall

This pin is the input pin for the voltage output high level for COM signals. A

capacitor should be connected between this pin and VSS.

PPoowweerr SSuuppppllyy ffoorr DDCC//DDCC CCoonnvveerrtteerr CCiirrccuuiitt

This is the power supply pin for the internal buffer of the DC/DC voltage converter.

It must be connected to external source when the converter is used. It should be

connected to VDD when the converter is not used.

PPoossiittiivvee TTeerrmmiinnaall ooff tthhee FFllyyiinngg IInnvveerrttiinngg CCaappaacciittoorr

NNeeggaattiivvee TTeerrmmiinnaall ooff tthhee FFllyyiinngg BBoooosstt CCaappaacciittoorr

The charge-pump capacitors are required between the terminals. They must be

floated when the converter is not used.

CCoommmmuunniiccaattiinngg PPrroottooccooll SSeelleecctt

These pins are MCU interface selection input. See the following table:

I2C

3-wire SPI

4-wire SPI

8-bit 68XX Parallel

8-bit 80XX Parallel

BS0

0

1

0

0

0

BS1

1

0

0

0

1

BS2

0

0

0

1

1

PPoowweerr RReesseett ffoorr CCoonnttrroolllleerr aanndd DDrriivveerr

This pin is reset signal input. When the pin is low, initialization of the chip is

executed. Keep this pin pull high during normal operation.

CChhiipp SSeelleecctt

This pin is the chip select input. The chip is enabled for MCU communication only

when CS# is pulled low.

DDaattaa//CCoommmmaanndd CCoonnttrrooll

This pin is Data/Command control pin. When the pin is pulled high, the input at

D7~D0 is treated as display data. When the pin is pulled low, the input at D7~D0

will be transferred to the command register.

When the pin is pulled high and serial interface mode is selected, the data at SDIN

will be interpreted as data. When it is pulled low, the data at SDIN will be

transferred to the command register. In I2C mode, this pin acts as SA0 for slave

address selection.

For detail relationship to MCU interface signals, please refer to the Timing

Characteristics Diagrams.

RReeaadd//WWrriittee EEnnaabbllee oorr RReeaadd

This pin is MCU interface input. When interfacing to a 68XX-series

microprocessor, this pin will be used as the Enable (E) signal. Read/write operation

is initiated when this pin is pulled high and the CS# is pulled low.

When connecting to an 80XX-microprocessor, this pin receives the Read (RD#)

signal. Data read operation is initiated when this pin is pulled low and CS# is

pulled low.

When serial or I2C mode is selected, this pin must be connected to VSS.

�

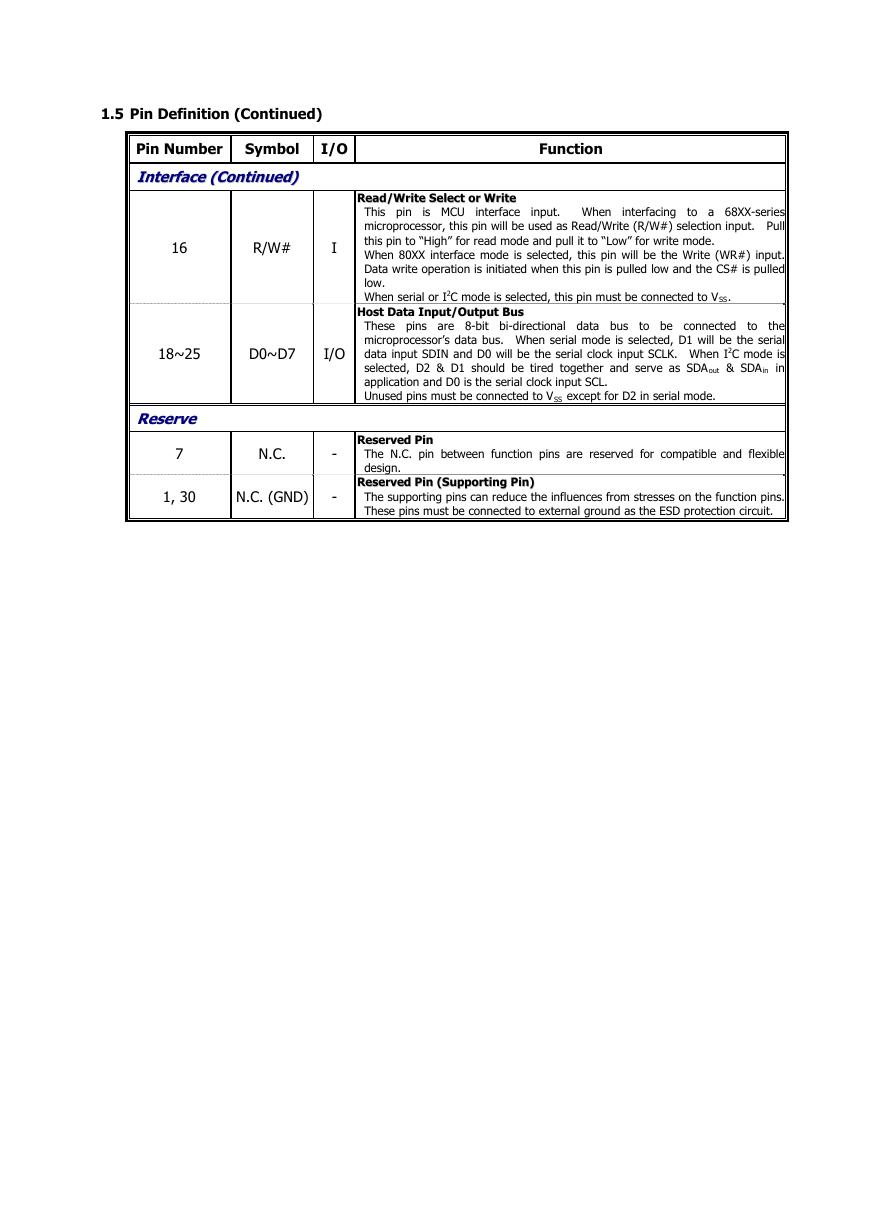

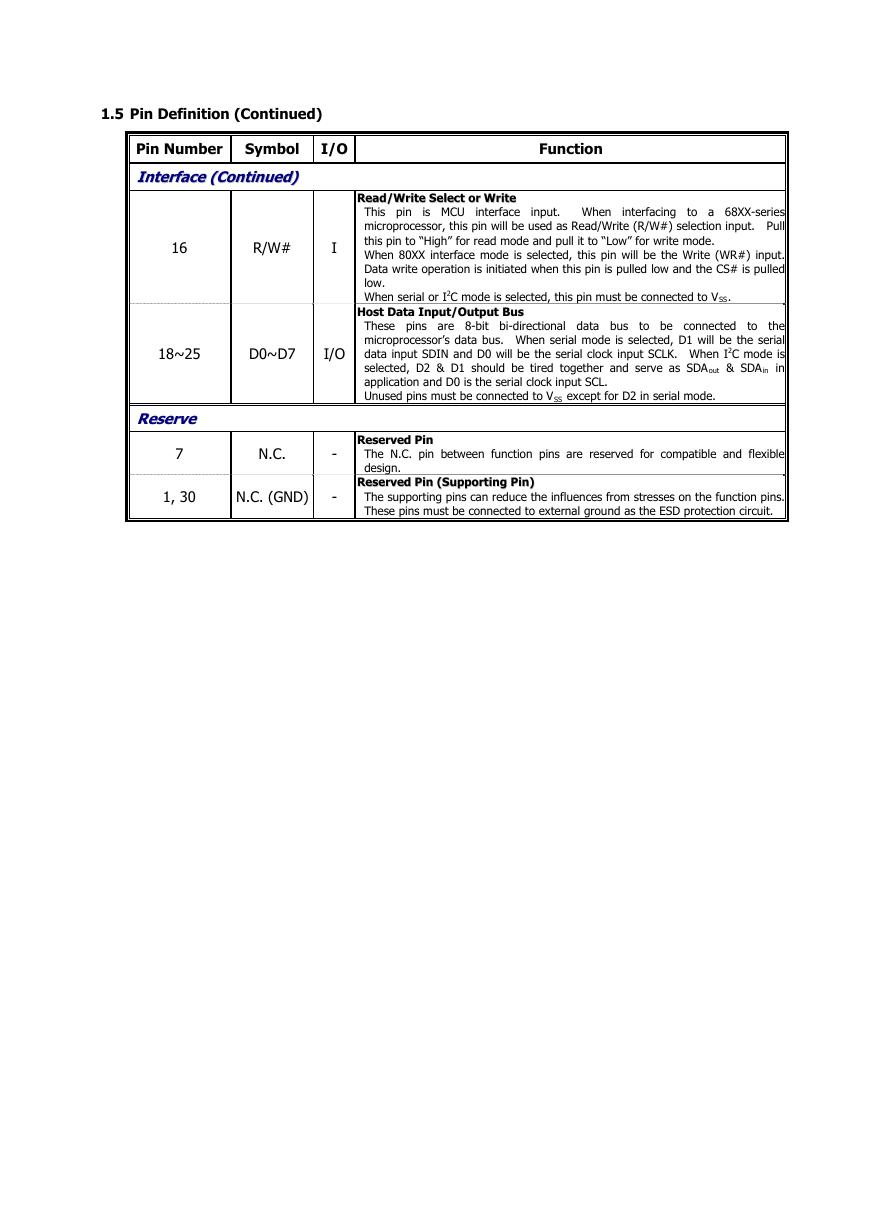

1.5 Pin Definition (Continued)

Pin Number Symbol

IInntteerrffaaccee ((CCoonnttiinnuueedd))

I/O

16

R/W#

I

18~25

D0~D7

I/O

RReesseerrvvee

Function

RReeaadd//WWrriittee SSeelleecctt oorr WWrriittee

This pin is MCU interface input. When interfacing to a 68XX-series

microprocessor, this pin will be used as Read/Write (R/W#) selection input. Pull

this pin to “High” for read mode and pull it to “Low” for write mode.

When 80XX interface mode is selected, this pin will be the Write (WR#) input.

Data write operation is initiated when this pin is pulled low and the CS# is pulled

low.

When serial or I2C mode is selected, this pin must be connected to VSS.

HHoosstt DDaattaa IInnppuutt//OOuuttppuutt BBuuss

These pins are 8-bit bi-directional data bus to be connected to the

microprocessor’s data bus. When serial mode is selected, D1 will be the serial

data input SDIN and D0 will be the serial clock input SCLK. When I2C mode is

selected, D2 & D1 should be tired together and serve as SDA out & SDAin in

application and D0 is the serial clock input SCL.

Unused pins must be connected to VSS except for D2 in serial mode.

7

N.C.

1, 30

N.C. (GND)

-

-

RReesseerrvveedd PPiinn

The N.C. pin between function pins are reserved for compatible and flexible

design.

RReesseerrvveedd PPiinn ((SSuuppppoorrttiinngg PPiinn))

The supporting pins can reduce the influences from stresses on the function pins.

These pins must be connected to external ground as the ESD protection circuit.

�

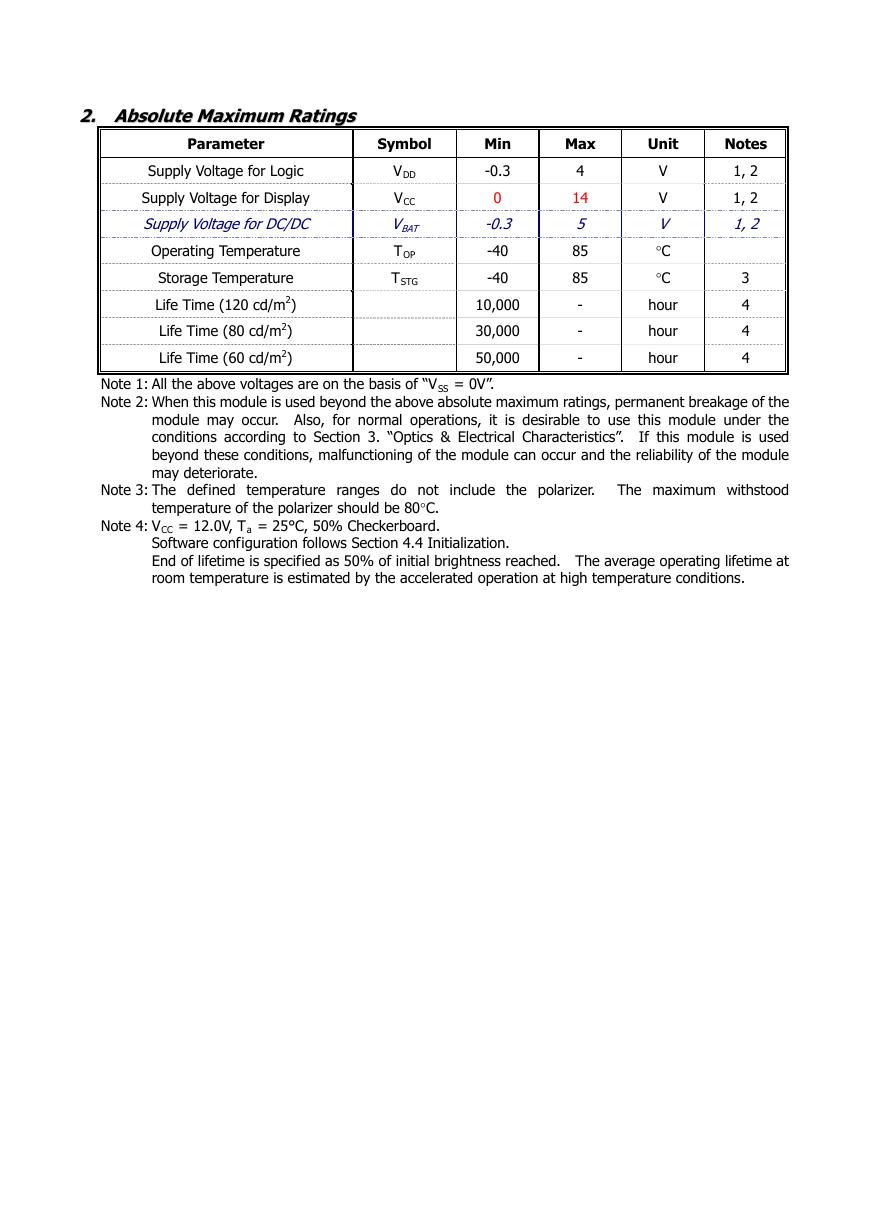

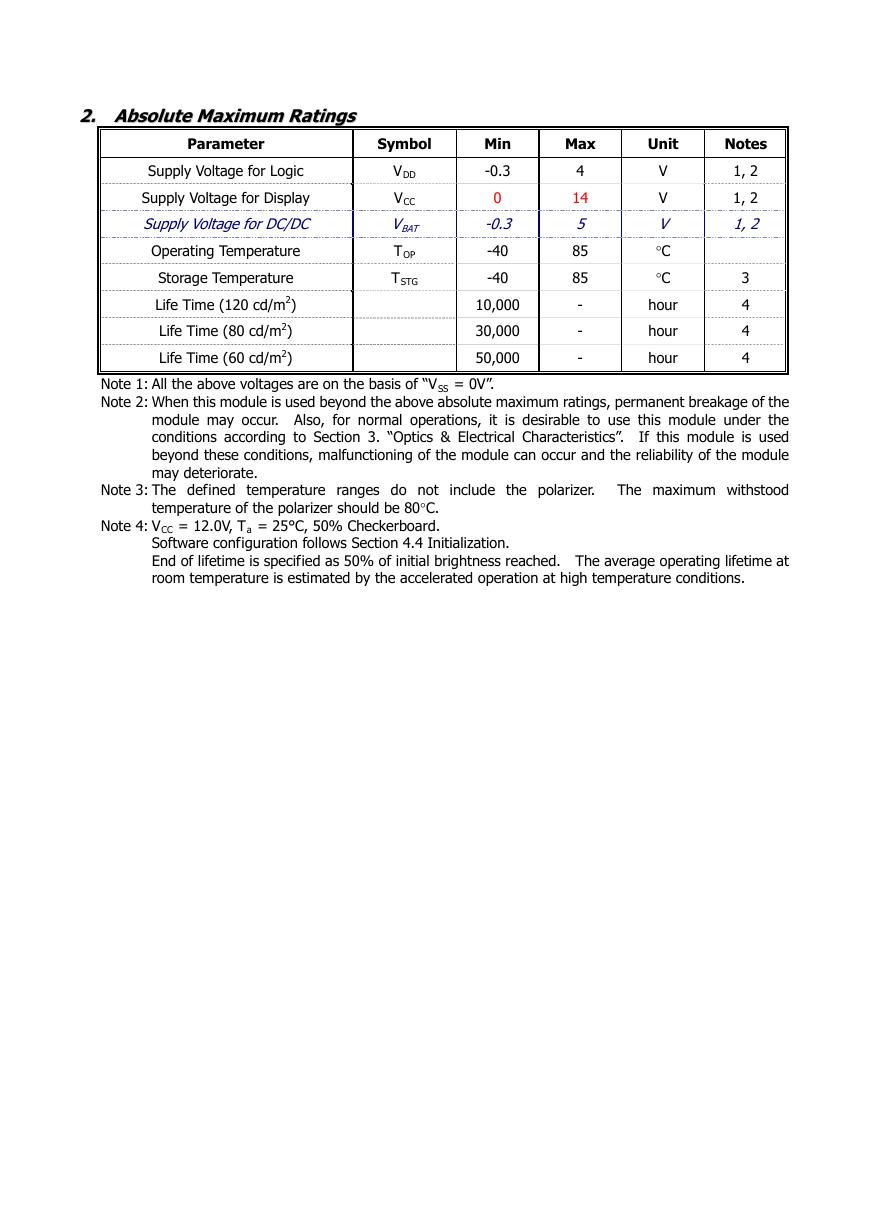

22.. AAbbssoolluuttee MMaaxxiimmuumm RRaattiinnggss

Parameter

Symbol

Supply Voltage for Logic

Supply Voltage for Display

Supply Voltage for DC/DC

Operating Temperature

Storage Temperature

Life Time (120 cd/m2)

Life Time (80 cd/m2)

Life Time (60 cd/m2)

VDD

VCC

VBAT

TOP

TSTG

Min

-0.3

0

-0.3

-40

-40

10,000

30,000

50,000

Max

4

14

5

85

85

-

-

-

Unit

V

V

V

C

C

hour

hour

hour

Notes

1, 2

1, 2

1, 2

3

4

4

4

Note 1: All the above voltages are on the basis of “VSS = 0V”.

Note 2: When this module is used beyond the above absolute maximum ratings, permanent breakage of the

module may occur. Also, for normal operations, it is desirable to use this module under the

conditions according to Section 3. “Optics & Electrical Characteristics”. If this module is used

beyond these conditions, malfunctioning of the module can occur and the reliability of the module

may deteriorate.

Note 3: The defined temperature ranges do not include the polarizer. The maximum withstood

temperature of the polarizer should be 80C.

Note 4: VCC = 12.0V, Ta = 25°C, 50% Checkerboard.

Software configuration follows Section 4.4 Initialization.

End of lifetime is specified as 50% of initial brightness reached. The average operating lifetime at

room temperature is estimated by the accelerated operation at high temperature conditions.

�

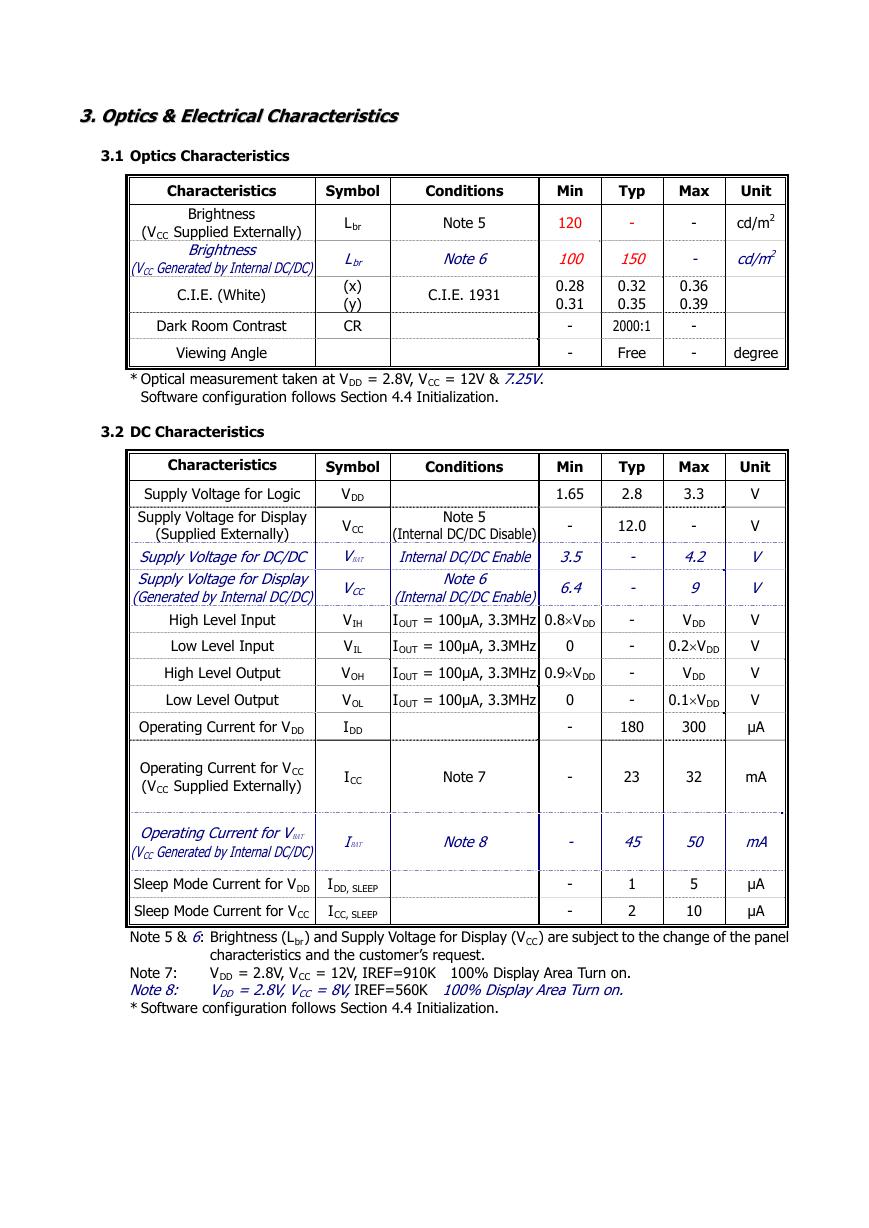

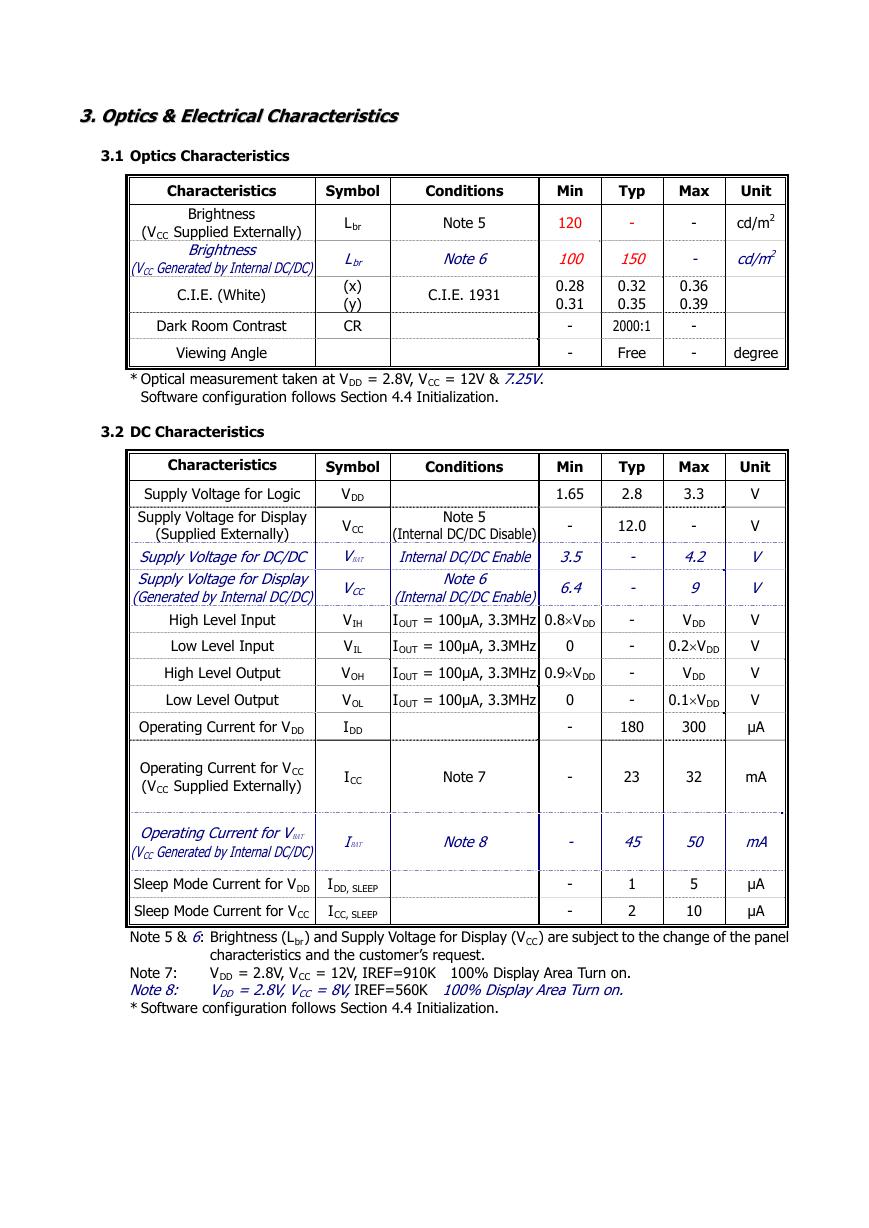

33.. OOppttiiccss && EElleeccttrriiccaall CChhaarraacctteerriissttiiccss

3.1 Optics Characteristics

Characteristics

Symbol

Conditions

Brightness

Lbr

Brightness

(VCC Supplied Externally)

(VCC Generated by Internal DC/DC) Lbr

(x)

(y)

CR

Dark Room Contrast

Viewing Angle

C.I.E. (White)

Note 5

Note 6

C.I.E. 1931

Min

120

Typ

Max

Unit

-

-

cd/m2

100 150

0.32

0.28

0.35

0.31

2000:1

Free

-

-

-

0.36

0.39

-

-

cd/m2

degree

* Optical measurement taken at VDD = 2.8V, VCC = 12V & 7.25V.

Software configuration follows Section 4.4 Initialization.

3.2 DC Characteristics

Characteristics

Symbol

Conditions

Supply Voltage for Logic

Supply Voltage for Display

(Supplied Externally)

VDD

VCC

Supply Voltage for DC/DC VBAT

Supply Voltage for Display

(Generated by Internal DC/DC) VCC

VIH

VIL

VOH

VOL

IDD

High Level Input

Low Level Input

High Level Output

Low Level Output

Operating Current for VDD

Note 5

Min

1.65

-

Note 6

(Internal DC/DC Disable)

Internal DC/DC Enable 3.5

(Internal DC/DC Enable) 6.4

IOUT = 100μA, 3.3MHz 0.8VDD

IOUT = 100μA, 3.3MHz

IOUT = 100μA, 3.3MHz 0.9VDD

IOUT = 100μA, 3.3MHz

0

0

-

Typ

2.8

12.0

-

-

-

-

-

-

180

Max

3.3

-

4.2

9

VDD

0.2VDD

VDD

0.1VDD

300

Unit

V

V

V

V

V

V

V

V

μA

Operating Current for VCC

(VCC Supplied Externally)

Operating Current for VBAT

(VCC Generated by Internal DC/DC)

ICC

IBAT

Note 7

-

23

32

mA

Note 8

-

45

50 mA

Sleep Mode Current for VDD

Sleep Mode Current for VCC

Note 5 & 6: Brightness (Lbr) and Supply Voltage for Display (VCC) are subject to the change of the panel

IDD, SLEEP

ICC, SLEEP

μA

μA

5

10

1

2

-

-

characteristics and the customer’s request.

VDD = 2.8V, VCC = 12V, IREF=910K 100% Display Area Turn on.

Note 7:

Note 8: VDD = 2.8V, VCC = 8V, IREF=560K 100% Display Area Turn on.

* Software configuration follows Section 4.4 Initialization.

�

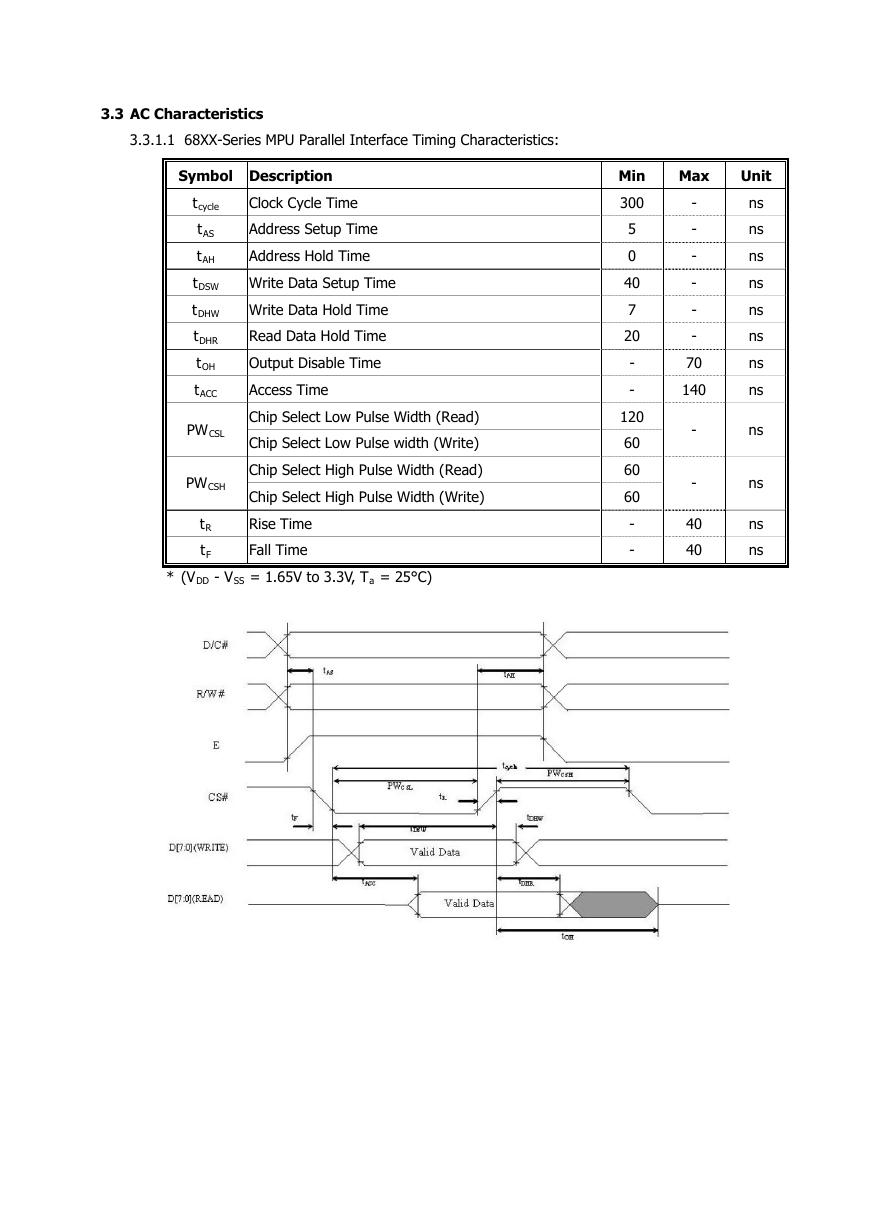

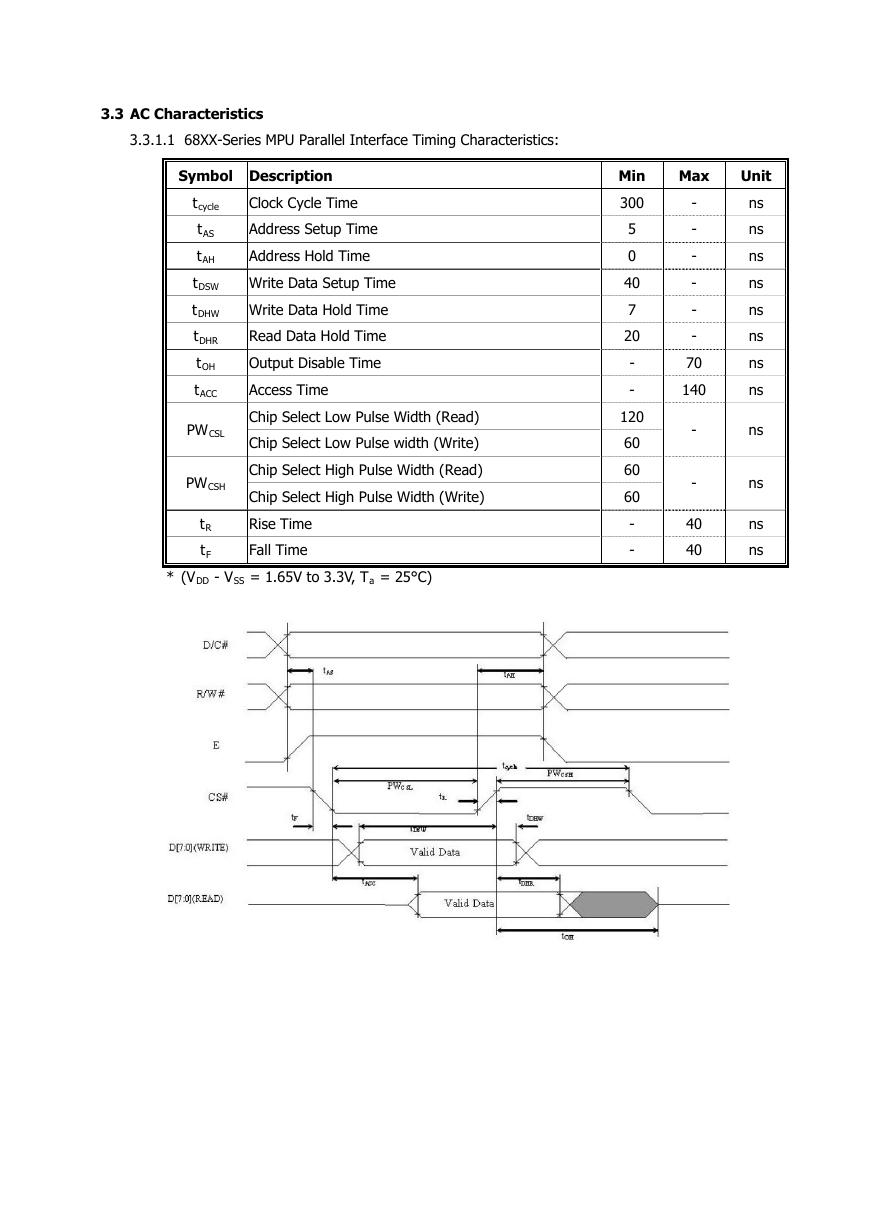

3.3 AC Characteristics

3.3.1.1 68XX-Series MPU Parallel Interface Timing Characteristics:

Symbol Description

Clock Cycle Time

Address Setup Time

Address Hold Time

tcycle

tAS

tAH

tDSW Write Data Setup Time

Write Data Hold Time

tDHW

tDHR

Read Data Hold Time

Output Disable Time

tOH

Access Time

tACC

Chip Select Low Pulse Width (Read)

Chip Select Low Pulse width (Write)

Chip Select High Pulse Width (Read)

Chip Select High Pulse Width (Write)

Rise Time

Fall Time

tR

tF

PWCSL

PWCSH

* (VDD - VSS = 1.65V to 3.3V, Ta = 25°C)

Min

300

5

0

40

7

20

-

-

120

60

60

60

-

-

Max

-

-

-

-

-

-

70

140

-

-

40

40

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf