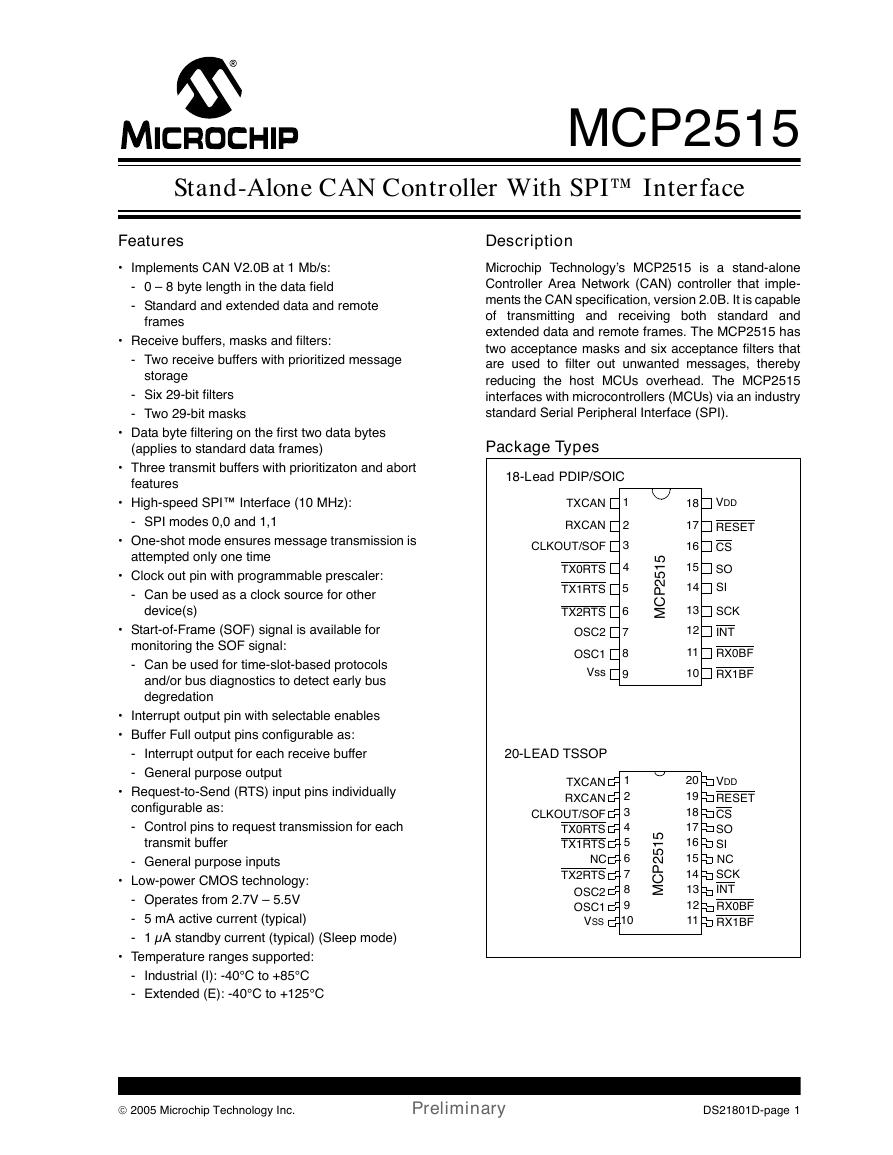

1.0 Device Overview

1.1 CAN Module

1.2 Control Logic

1.3 SPI Protocol Block

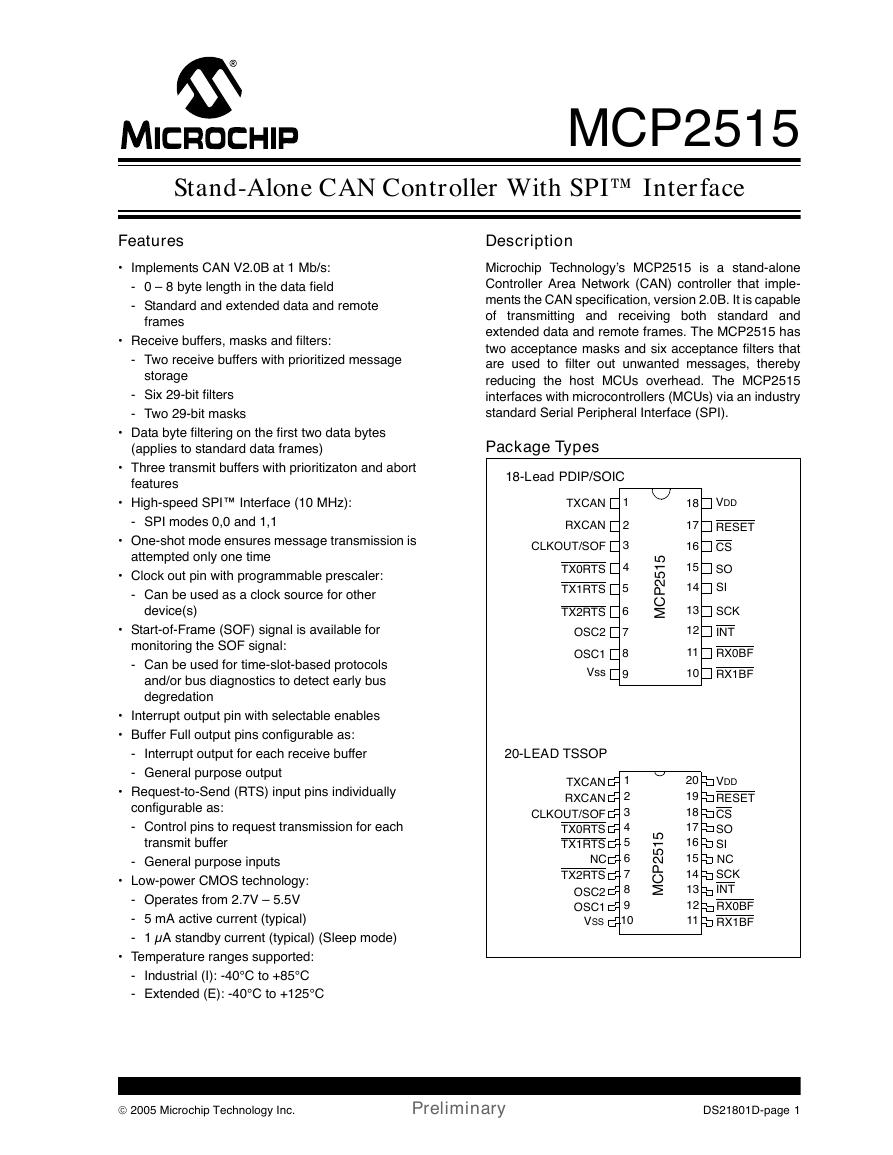

Figure 1-1: Block DIagram

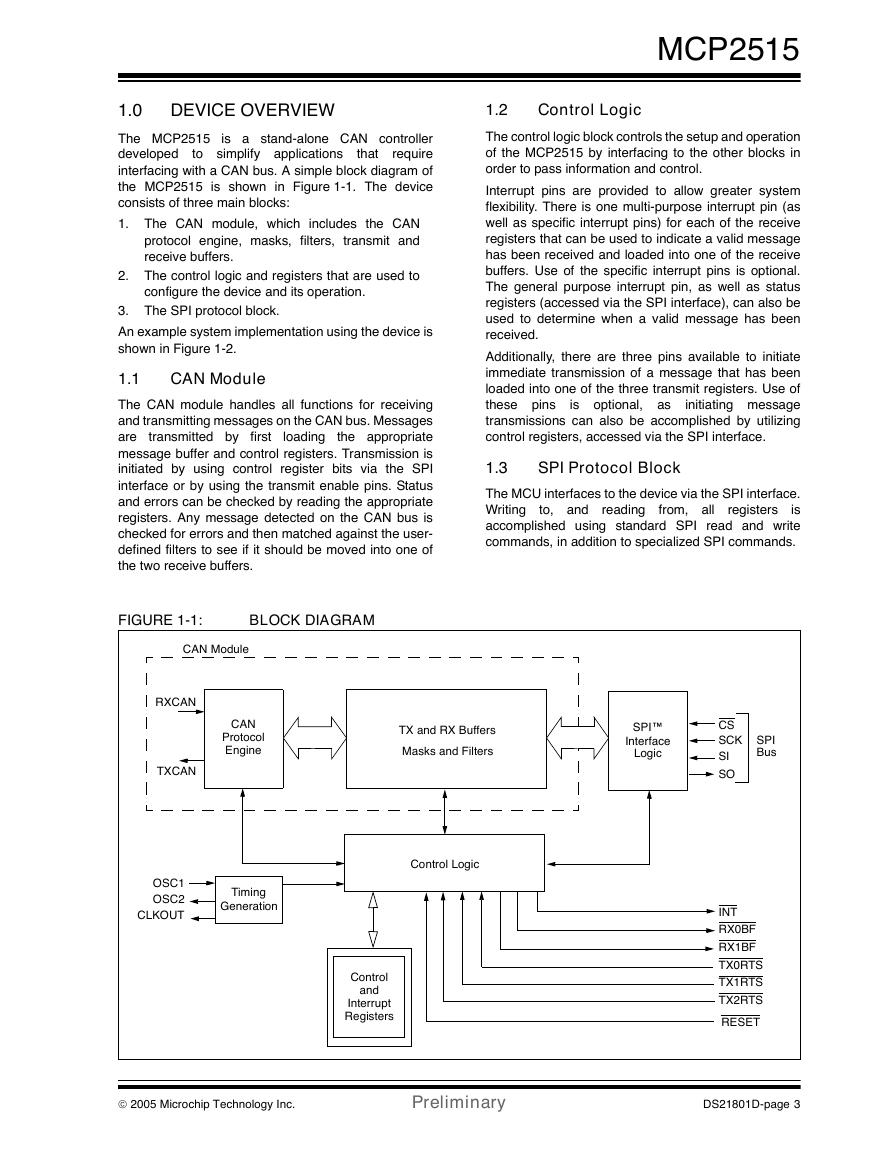

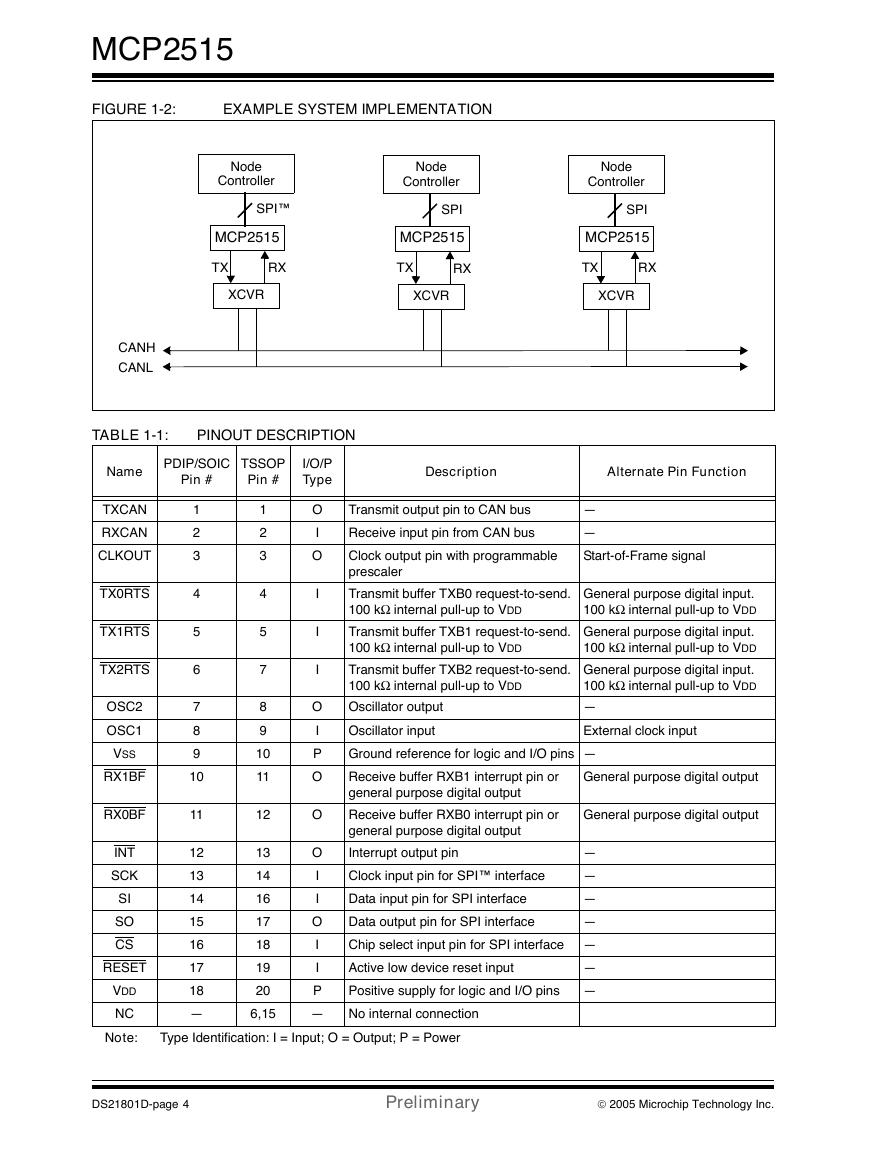

Figure 1-2: Example System Implementation

Table 1-1: Pinout Description

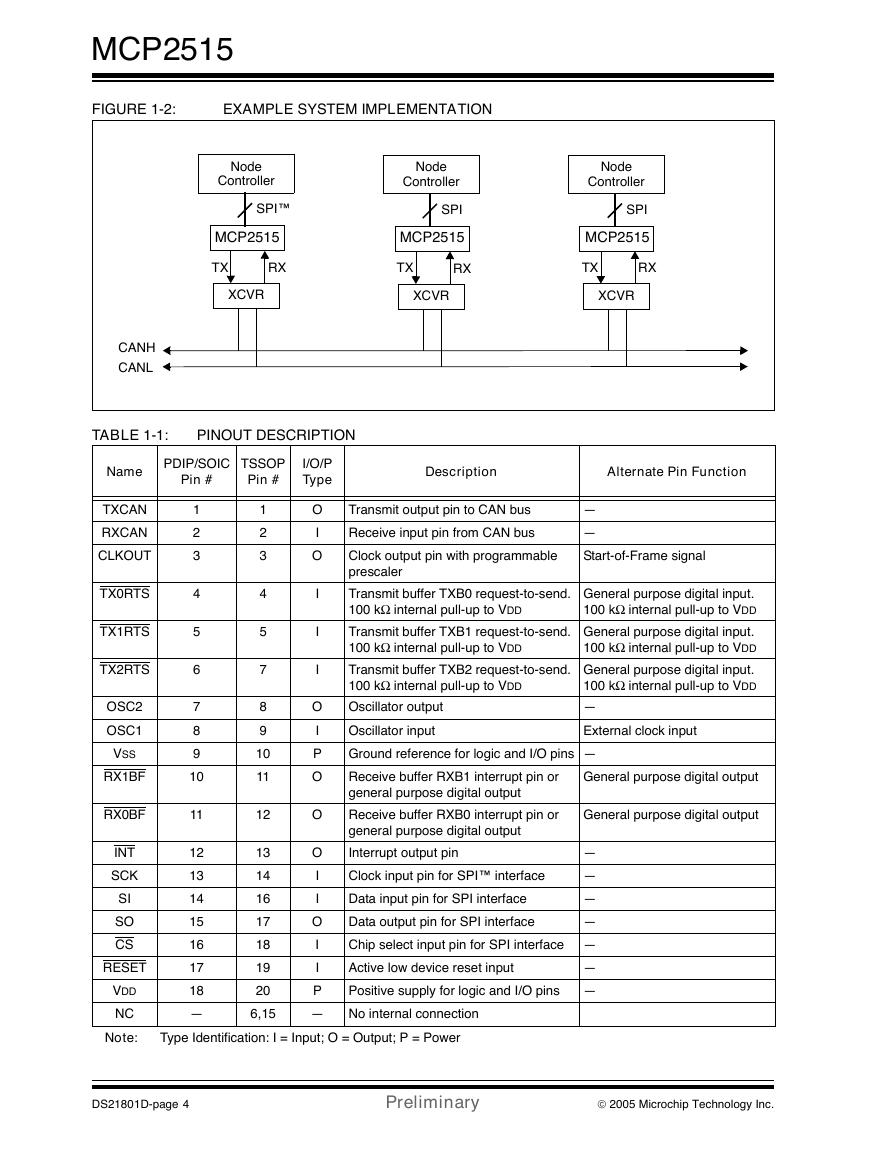

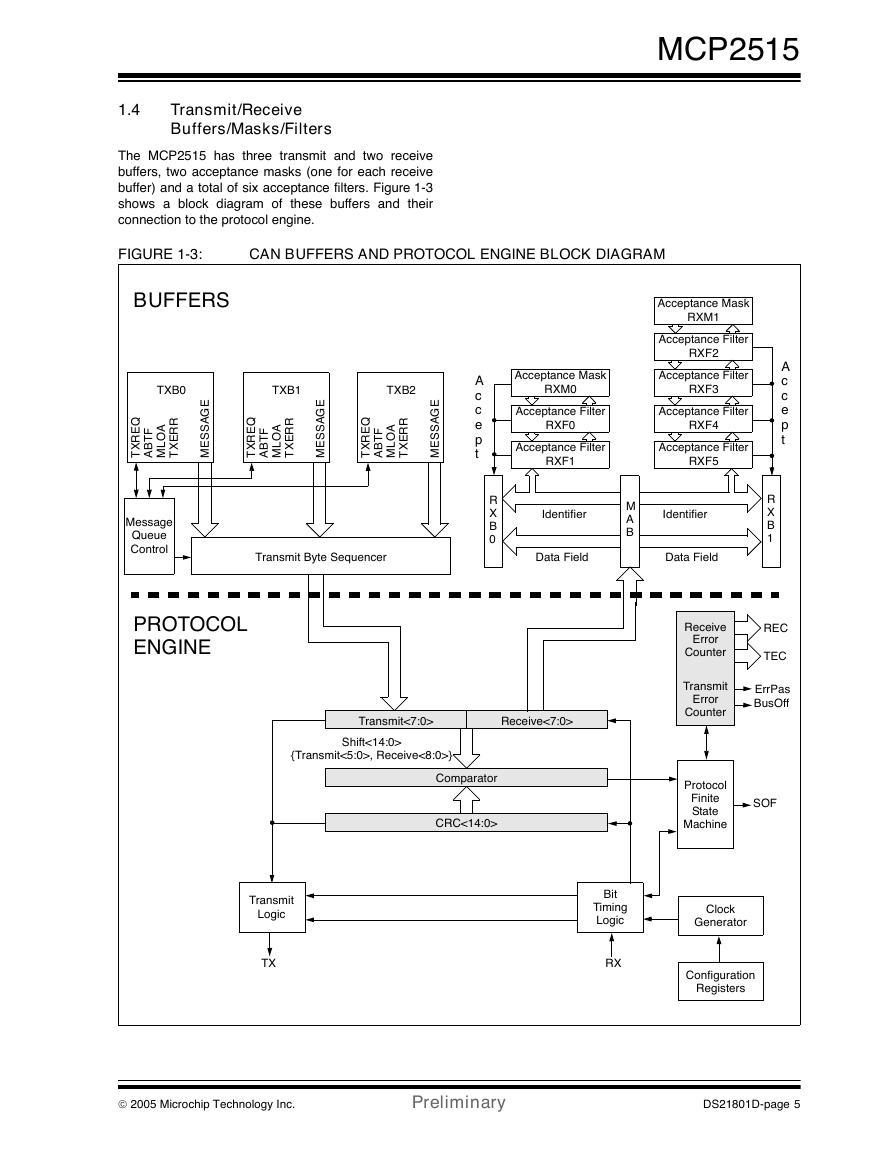

1.4 Transmit/Receive Buffers/Masks/Filters

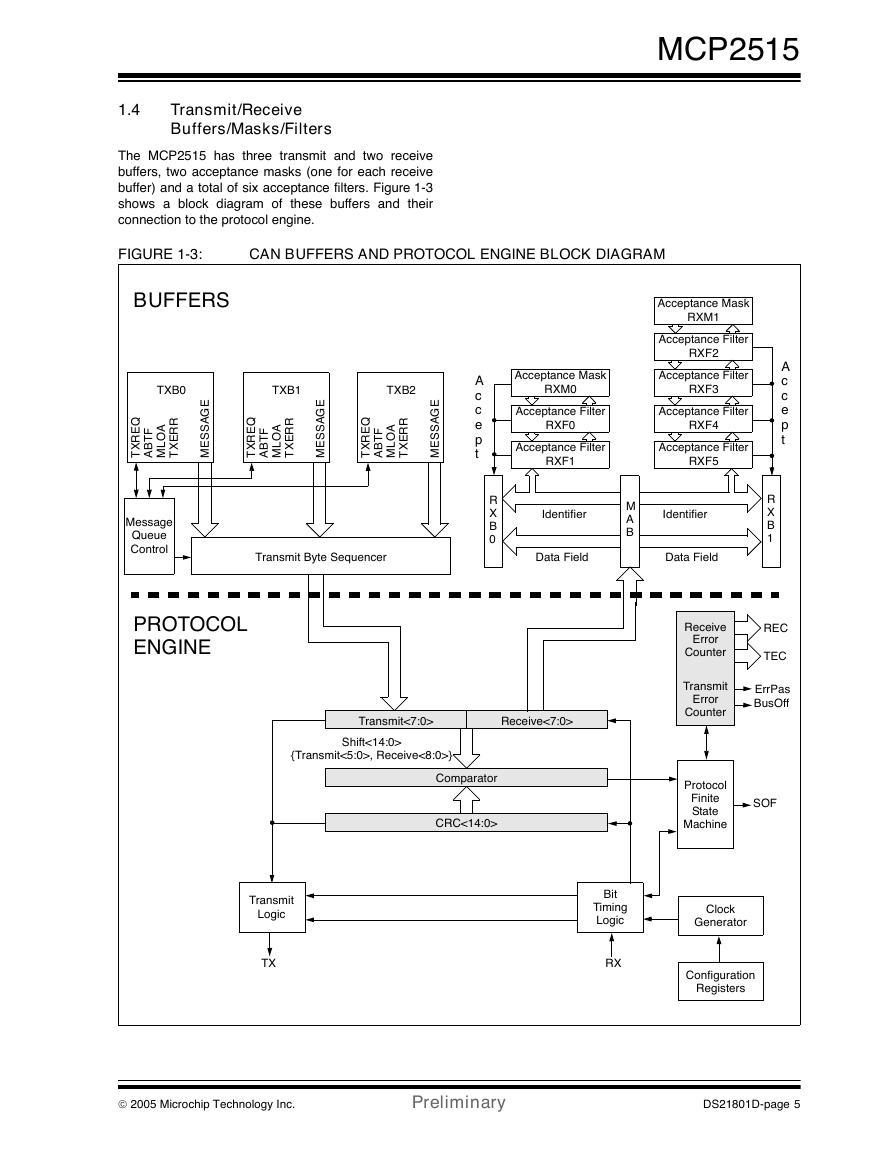

Figure 1-3: CAN Buffers and Protocol engine Block Diagram

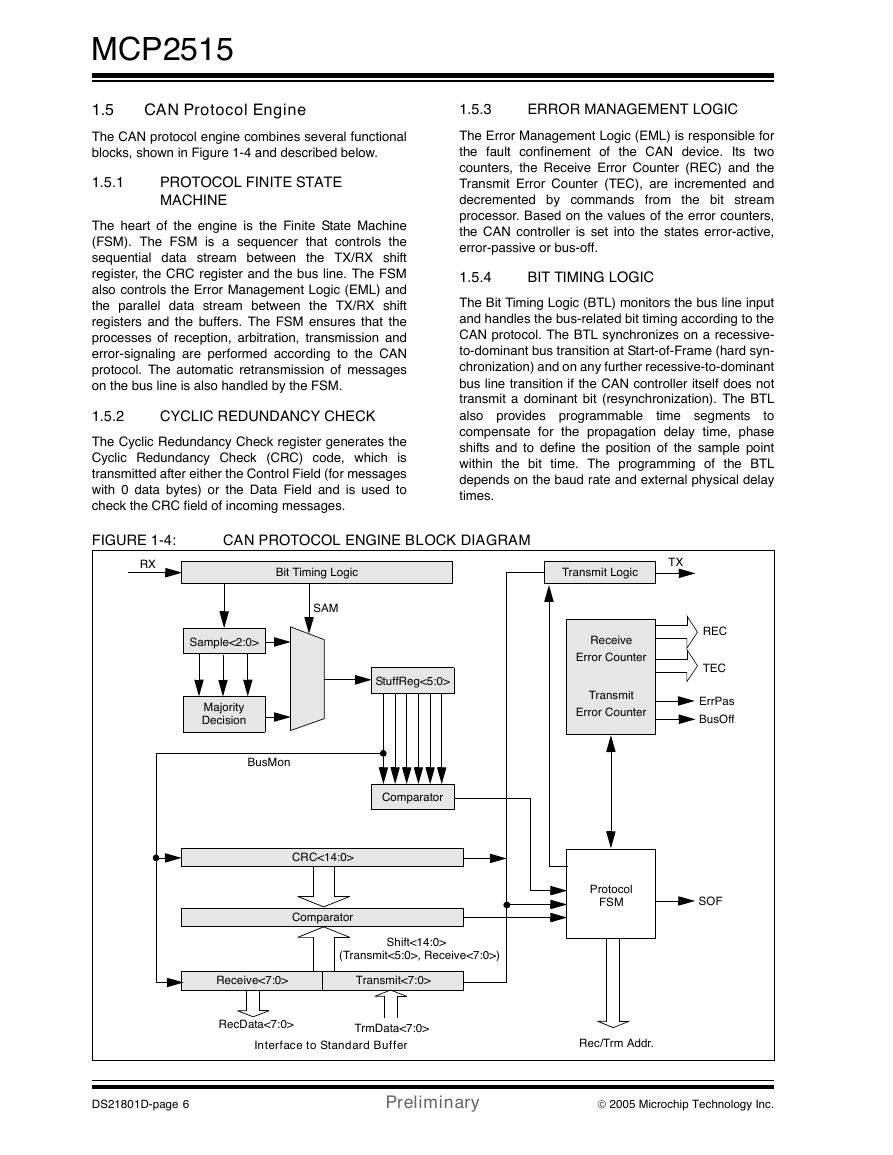

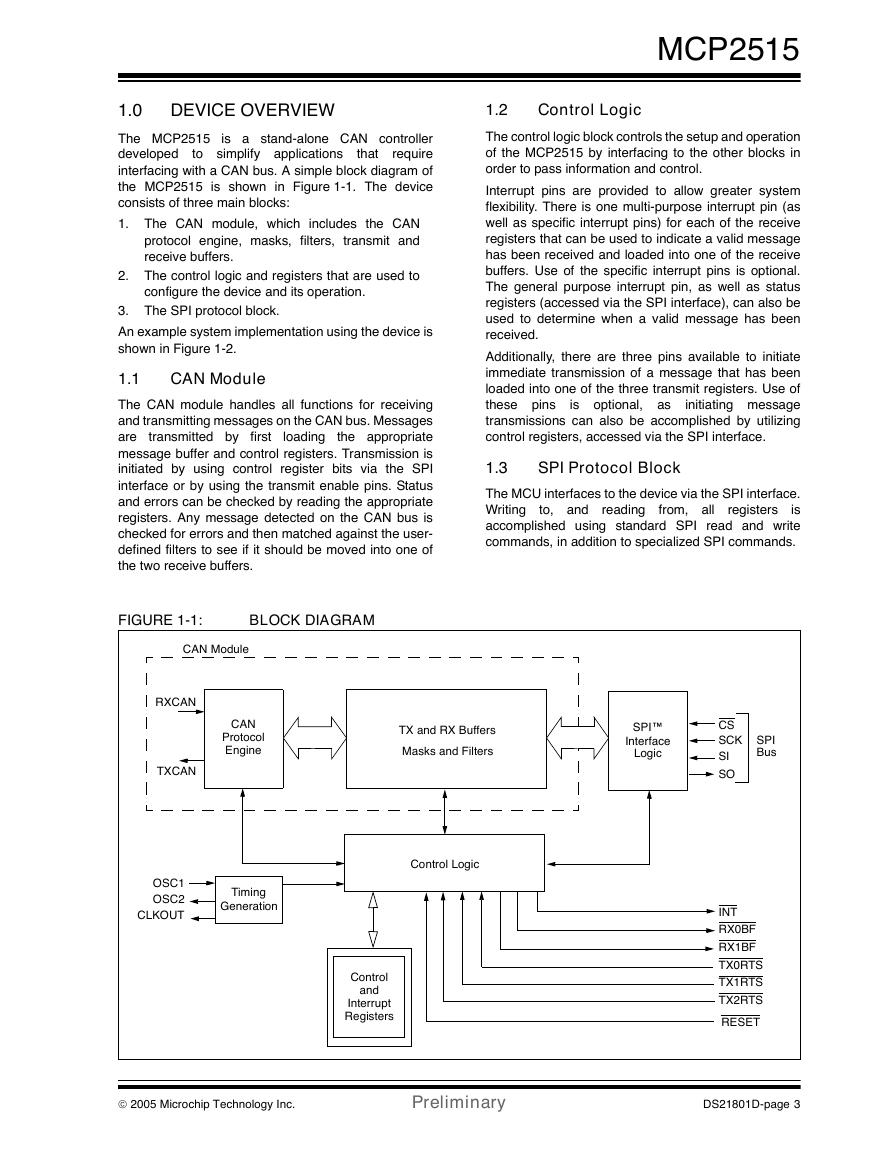

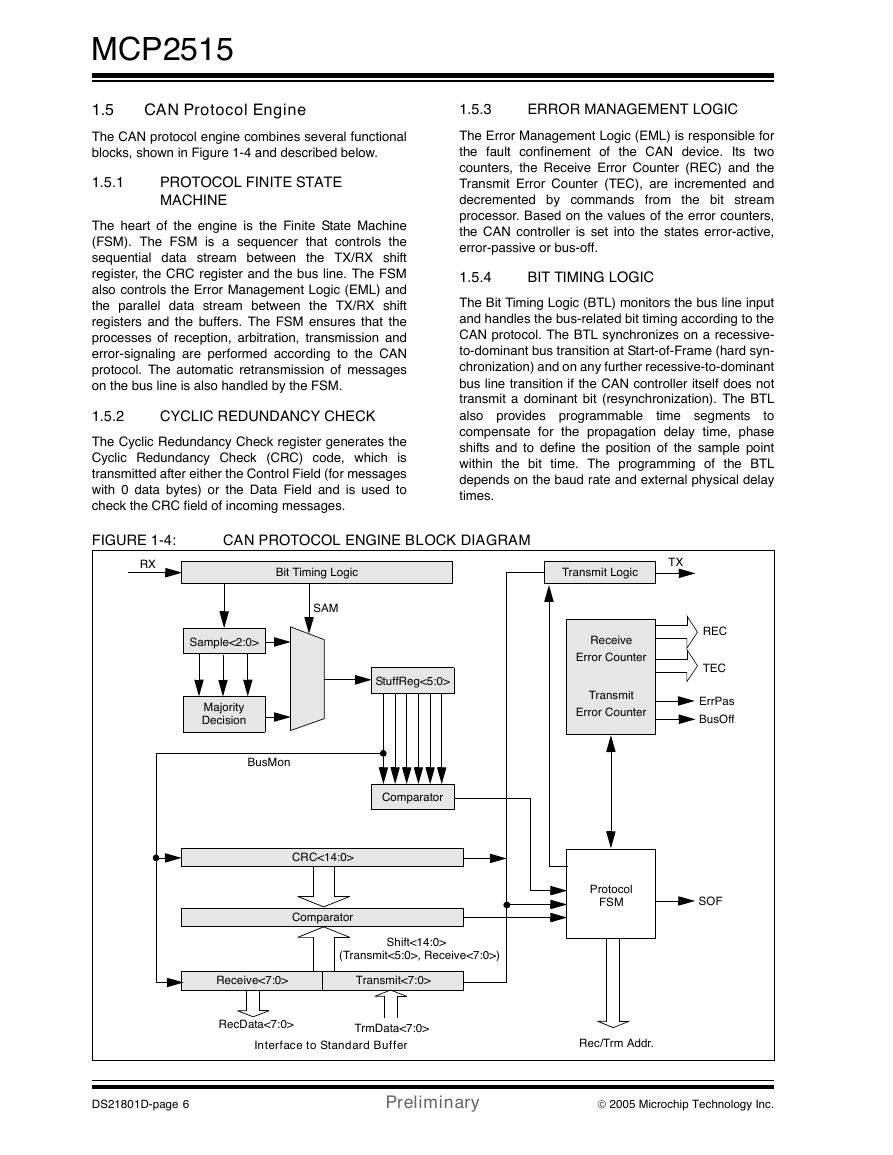

1.5 CAN Protocol Engine

Figure 1-4: CAN Protocol engine Block Diagram

2.0 Can Message Frames

2.1 Standard Data Frame

2.2 Extended Data Frame

2.3 Remote Frame

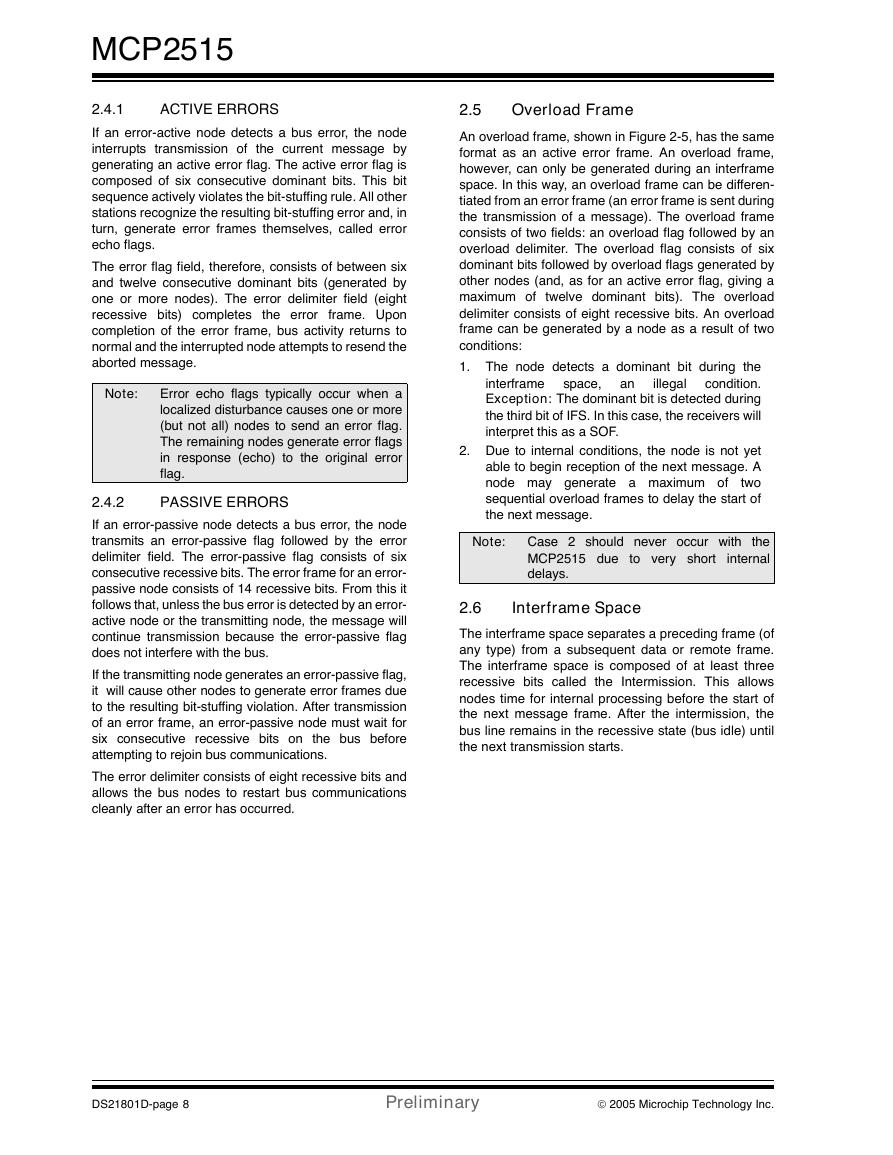

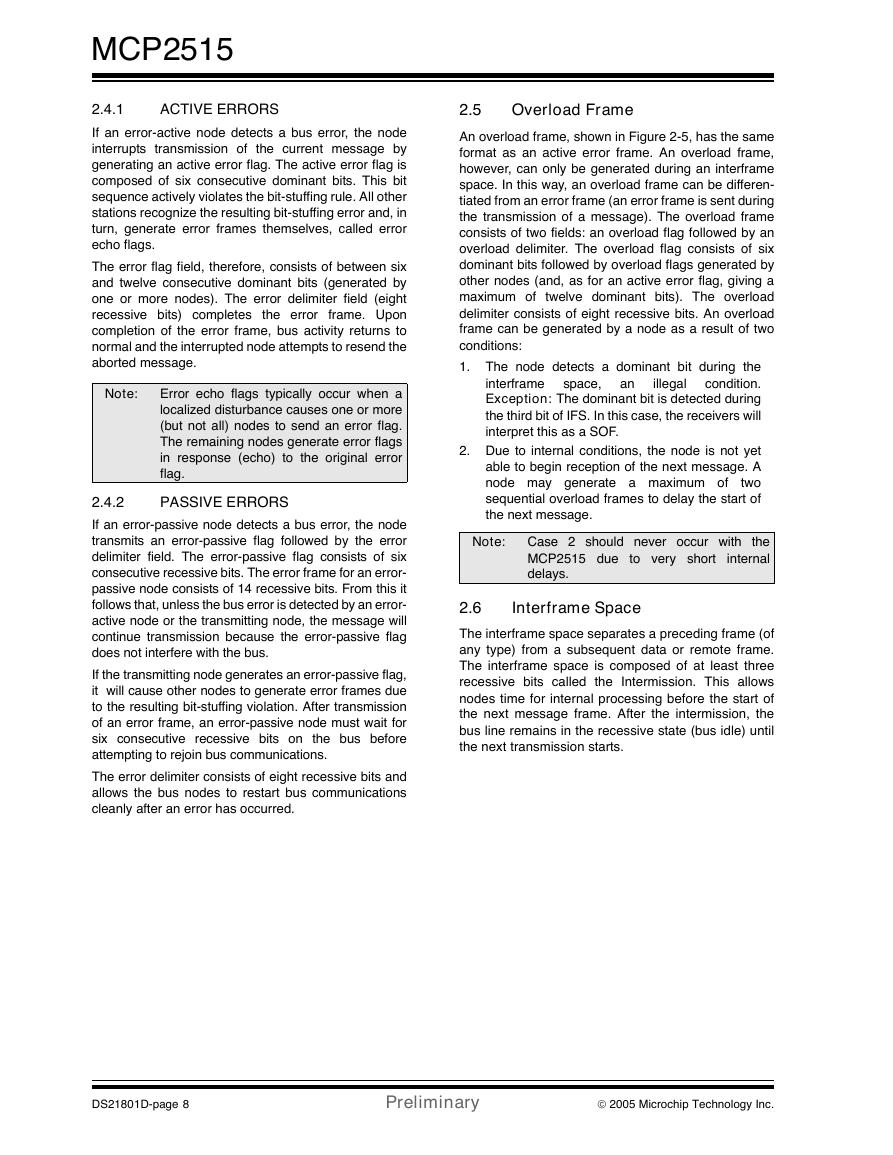

2.4 Error Frame

2.5 Overload Frame

2.6 Interframe Space

Figure 2-1: Standard Data Frame

Figure 2-2: Extended Data Frame

Figure 2-3: Remote Frame

Figure 2-4: Active Error Frame

Figure 2-5: Overload Frame

3.0 Message Transmission

3.1 Transmit Buffers

3.2 Transmit Priority

3.3 Initiating Transmission

3.4 One-Shot Mode

3.5 TXnRTS PINS

3.6 Aborting Transmission

Figure 3-1: Transmit Message Flowchart

4.0 Message Reception

4.1 Receive Message Buffering

4.2 Receive Priority

4.3 Start-of-Frame Signal

4.4 RX0BF and RX1BF Pins

Figure 4-1: StArt-Of-FrAme Signaling

Table 4-1: CONFIGURING RXnBF PINS

Figure 4-2: Receive Buffer Block Diagram

Figure 4-3: Receive Flow Flowchart

4.5 Message Acceptance Filters and Masks

Table 4-2: Filter/Mask Truth Table

Figure 4-4: Masks AnD Filters Apply to CAN Frames

Figure 4-5: Message Acceptance Mask and Filter Operation

5.0 Bit Timing

5.1 The CAN Bit TIme

Figure 5-1: can Bit time Segments

Figure 5-2: TQ and the Bit Period

5.2 Synchronization

Figure 5-3: Synchronizing the Bit Time

5.3 Programming Time Segments

5.4 Oscillator Tolerance

5.5 Bit Timing Configuration Registers

6.0 Error Detection

6.1 CRC Error

6.2 Acknowledge Error

6.3 Form Error

6.4 Bit Error

6.5 Stuff Error

6.6 Error States

6.7 Error Modes and Error Counters

Figure 6-1: ErrOr Modes State Diagram

7.0 Interrupts

7.1 Interrupt Code Bits

Table 7-1: ICOD<2:0> DecOde

7.2 Transmit Interrupt

7.3 Receive Interrupt

7.4 Message Error Interrupt

7.5 Bus Activity Wakeup Interrupt

7.6 Error Interrupt

7.7 Interrupt Acknowledge

8.0 Oscillator

8.1 Oscillator Startup Timer

8.2 CLKOUT Pin

Figure 8-1: Crystal/Ceramic Resonator Operation

Figure 8-2: External Clock Source

Figure 8-3: External Series Resonant Crystal Oscillator Circuit(1)

Table 8-1: CAPACITOR SELECTION FOR CERAMIC RESONATORS

Table 8-2: CAPACITOR SELECTION FOR CRYSTAL OSCILLATOR

9.0 RESET

Figure 9-1: RESET Pin Configuration Example

10.0 Modes of Operation

10.1 Configuration Mode

10.2 Sleep Mode

10.3 Listen-only Mode

10.4 Loopback Mode

10.5 Normal Mode

11.0 Register Map

Table 11-1: CAN Controller Register Map

Table 11-2: Control Register Summary

12.0 SPI™ Interface

12.1 Overview

12.2 Reset Instruction

12.3 Read Instruction

12.4 Read RX Buffer Instruction

12.5 Write Instruction

12.6 Load TX Buffer Instruction

12.7 Request-To-Send (RTS) Instruction

12.8 Read Status Instruction

12.9 RX Status Instruction

12.10 Bit Modify Instruction

Figure 12-1: Bit Modify

Table 12-1: SPI™ Instruction Set

Figure 12-2: Read instruction

Figure 12-3: Read RX Buffer Instruction

Figure 12-4: Byte Write instruction

Figure 12-5: Load TX Buffer

Figure 12-6: Request-to-send (RTS) instruction

Figure 12-7: BIT Modify instruction

Figure 12-8: Read Status instruction

Figure 12-9: RX StatUs Instruction

Figure 12-10: SPI™ Input Timing

Figure 12-11: SPI™ Output TIming

13.0 Electrical Characteristics

13.1 Absolute Maximum Ratings�†

Table 13-1: DC Characteristics

Table 13-2: Oscillator Timing Characteristics

Table 13-3: CAN Interface AC Characteristics

Table 13-4: Reset AC Characteristics

Table 13-5: CLKOUT Pin AC Characteristics

Figure 13-1: Start-of-frame Pin AC Characteristics

Table 13-6: SPI™ Interface AC Characteristics

14.0 PackAging Information

14.1 Package Marking Information�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf