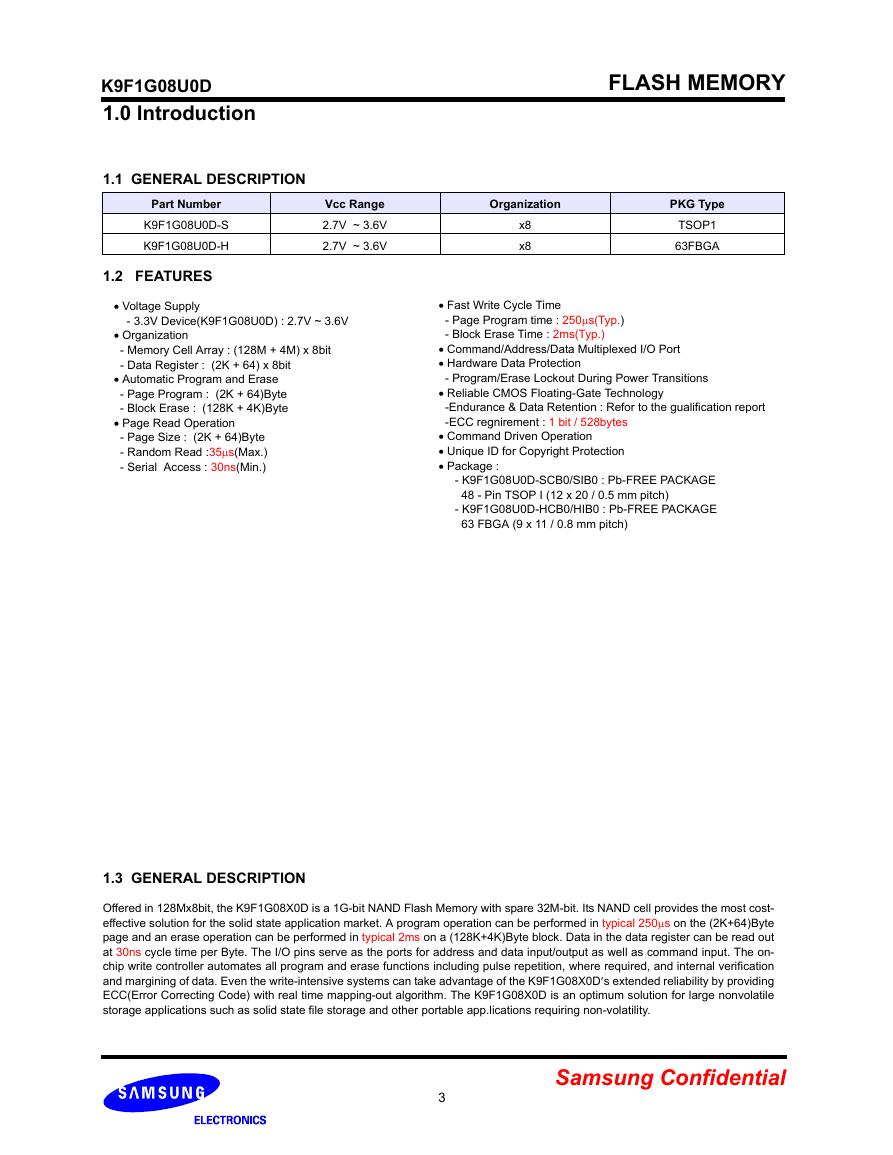

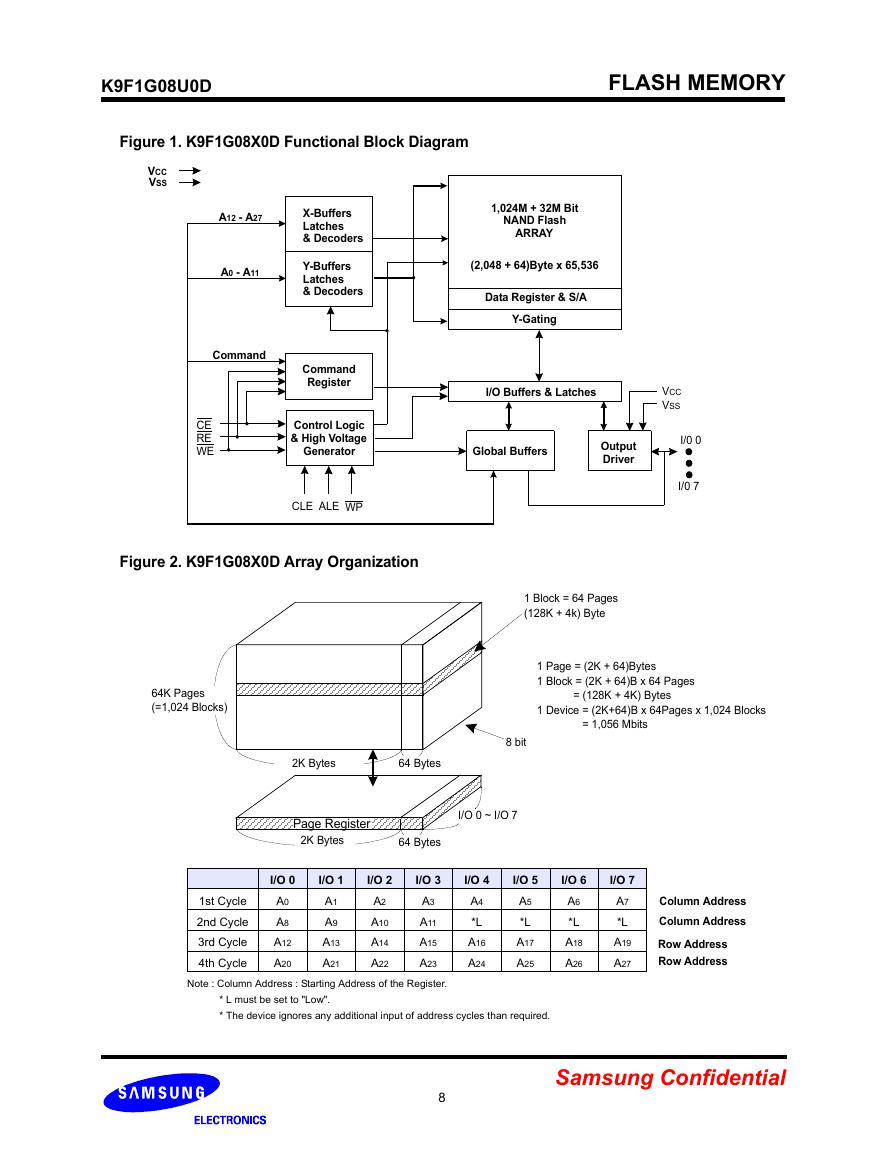

1.1 GENERAL DESCRIPTION

1.2 FEATURES

1.3 GENERAL DESCRIPTION

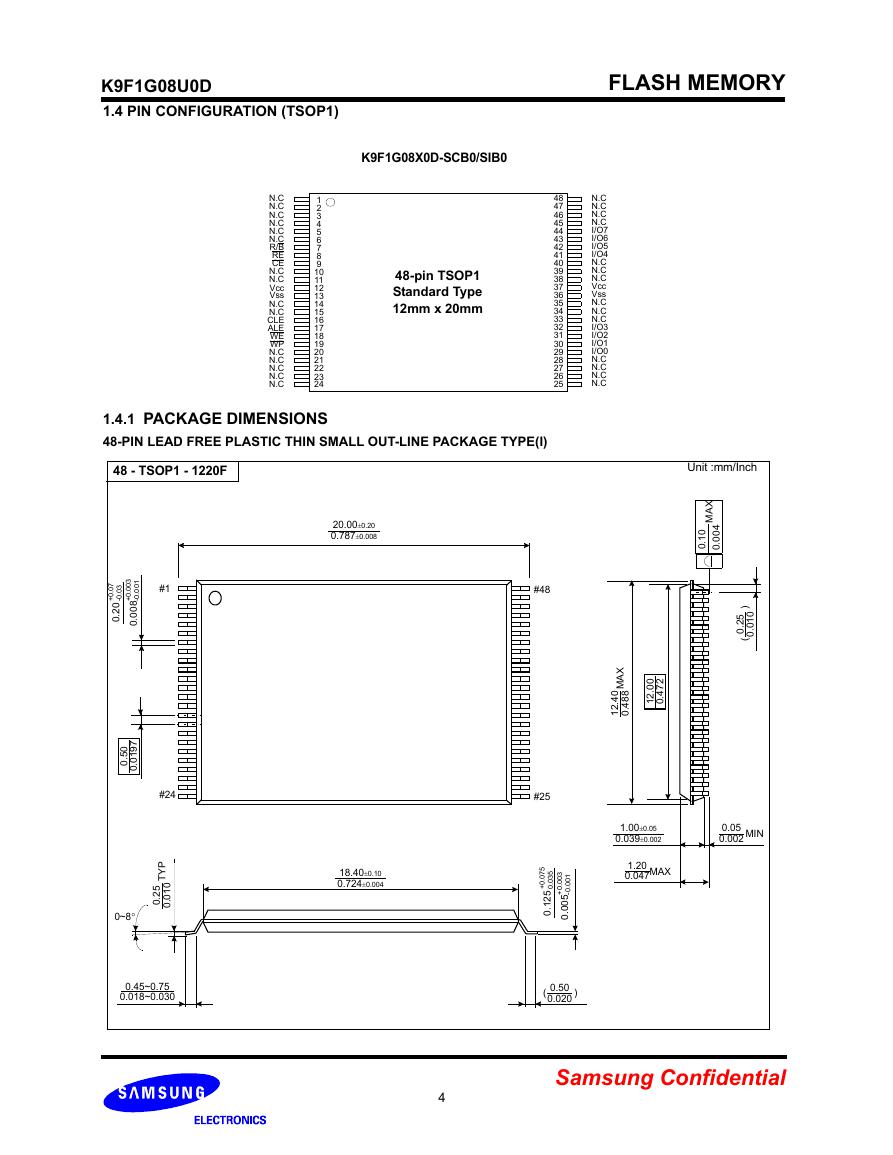

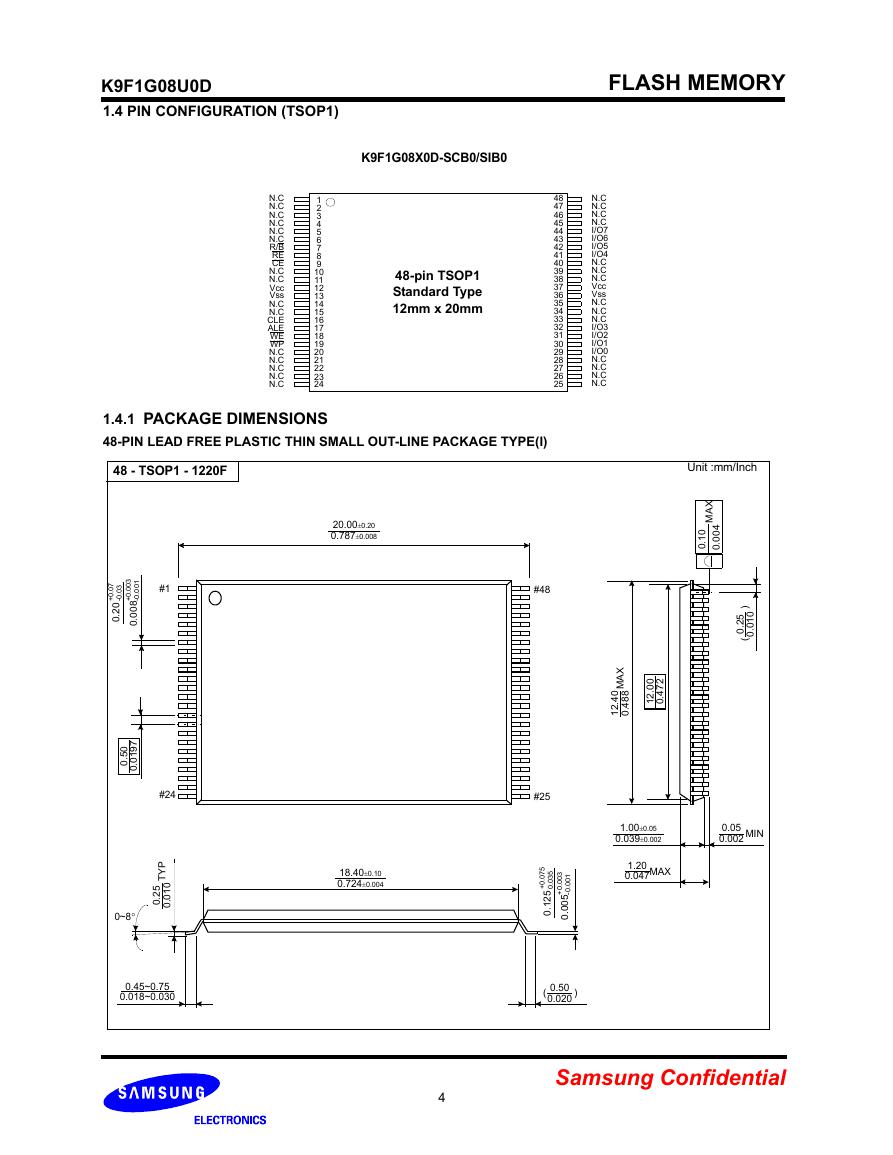

1.4 PIN CONFIGURATION (TSOP1)

1.4.1 PACKAGE DIMENSIONS

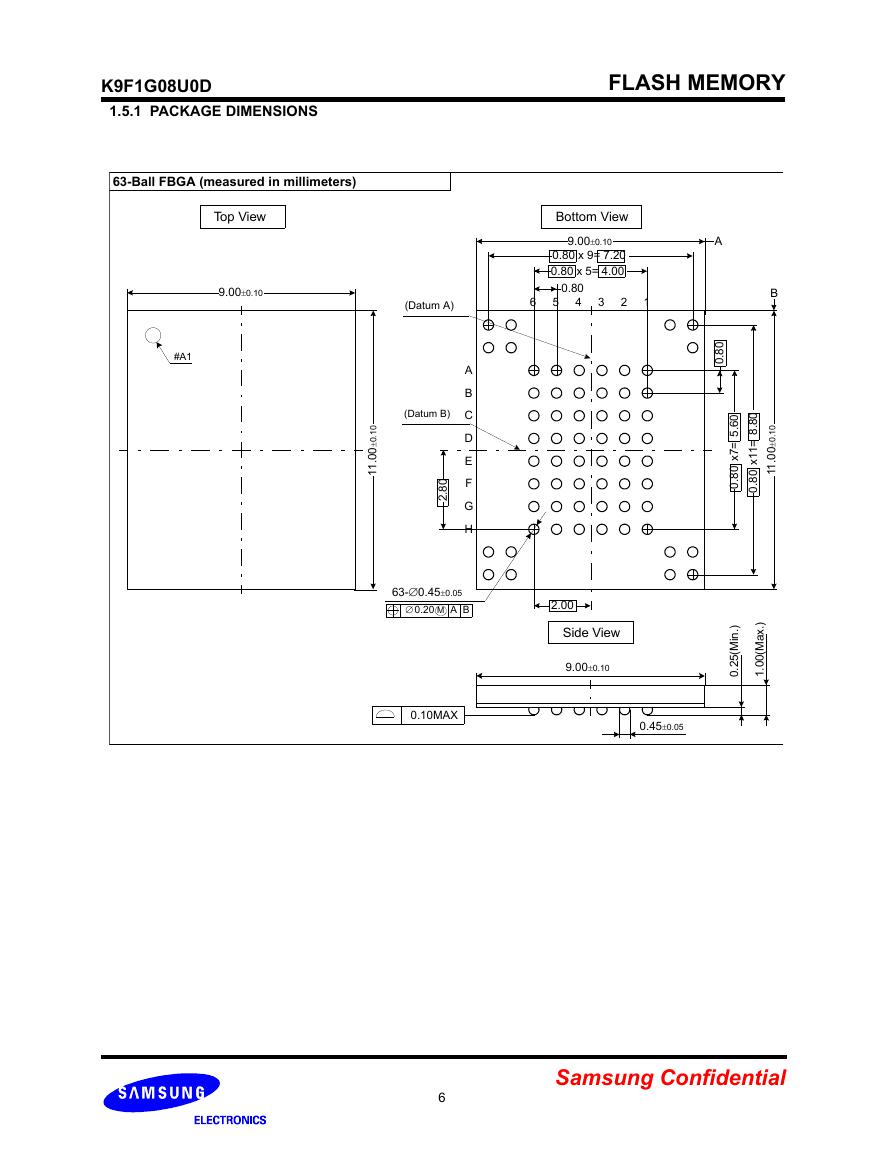

1.5 PIN CONFIGURATION (FBGA)

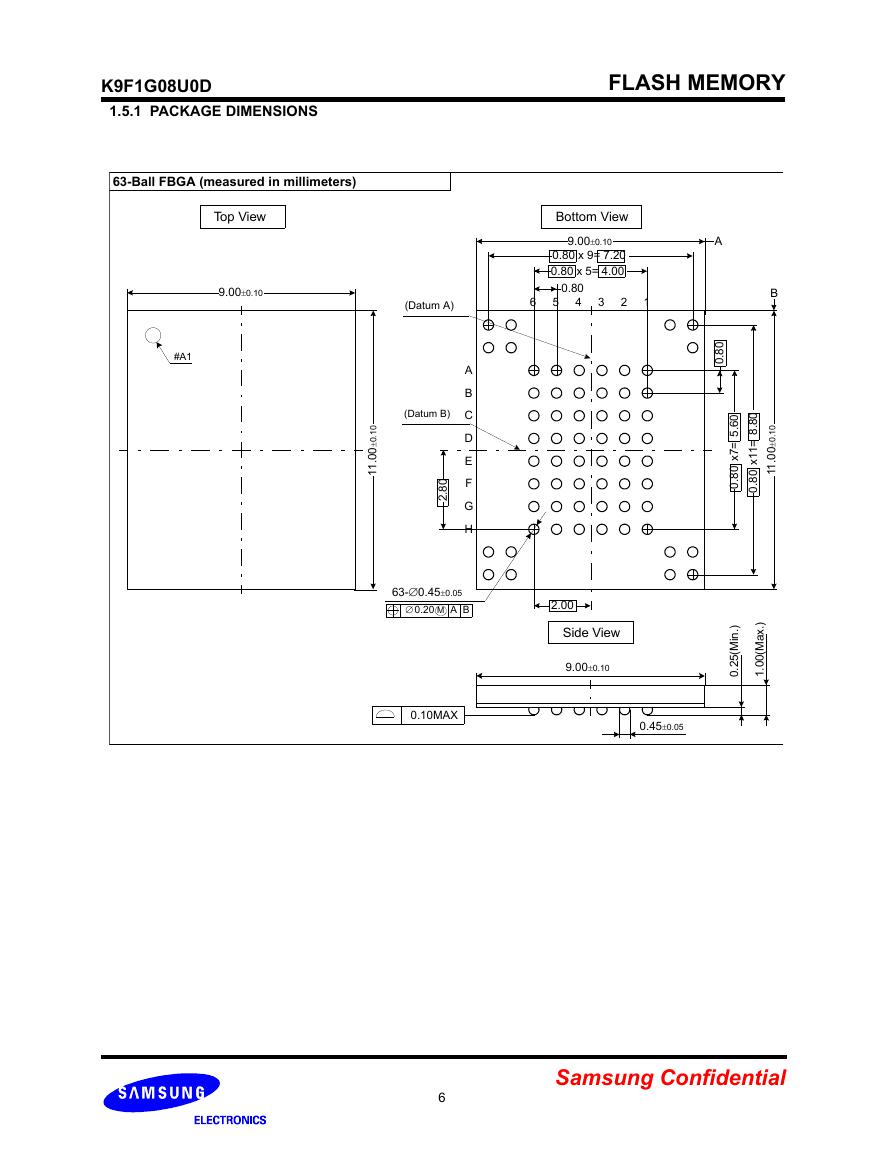

1.5.1 PACKAGE DIMENSIONS

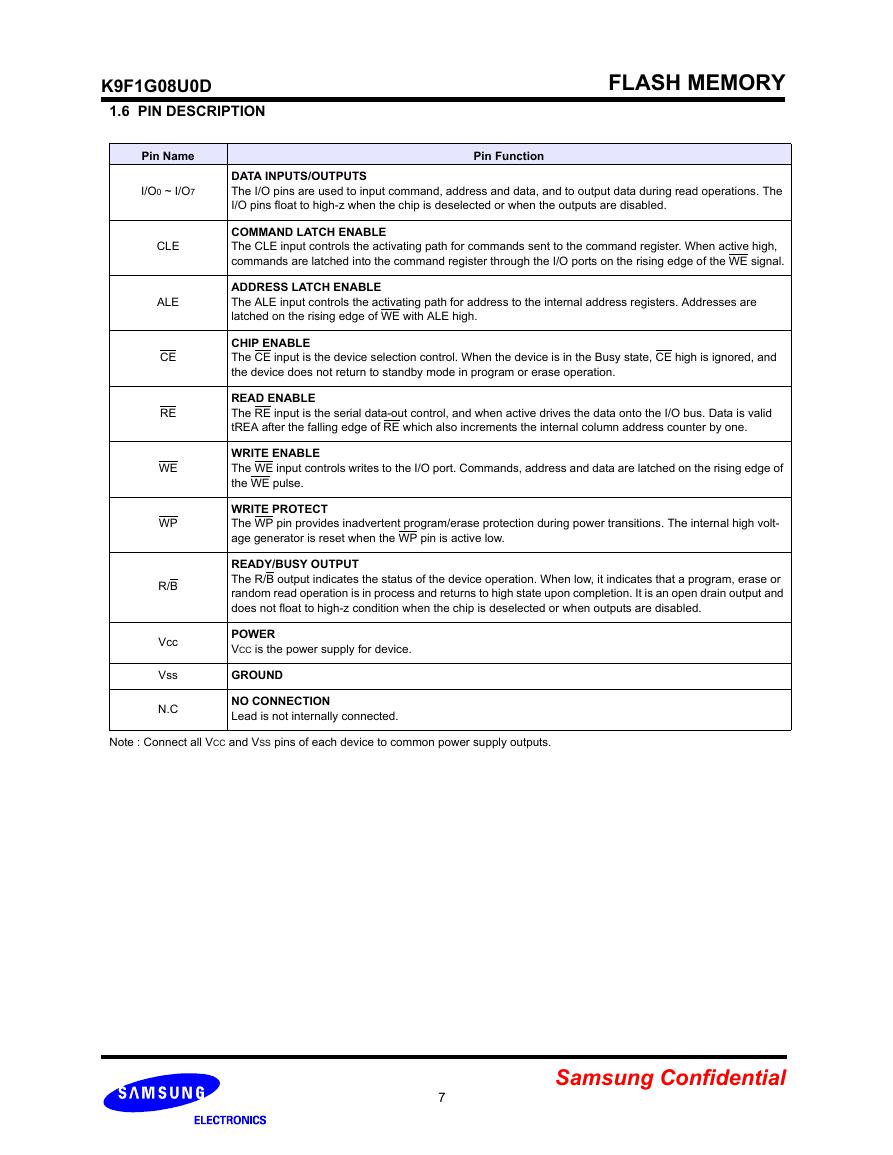

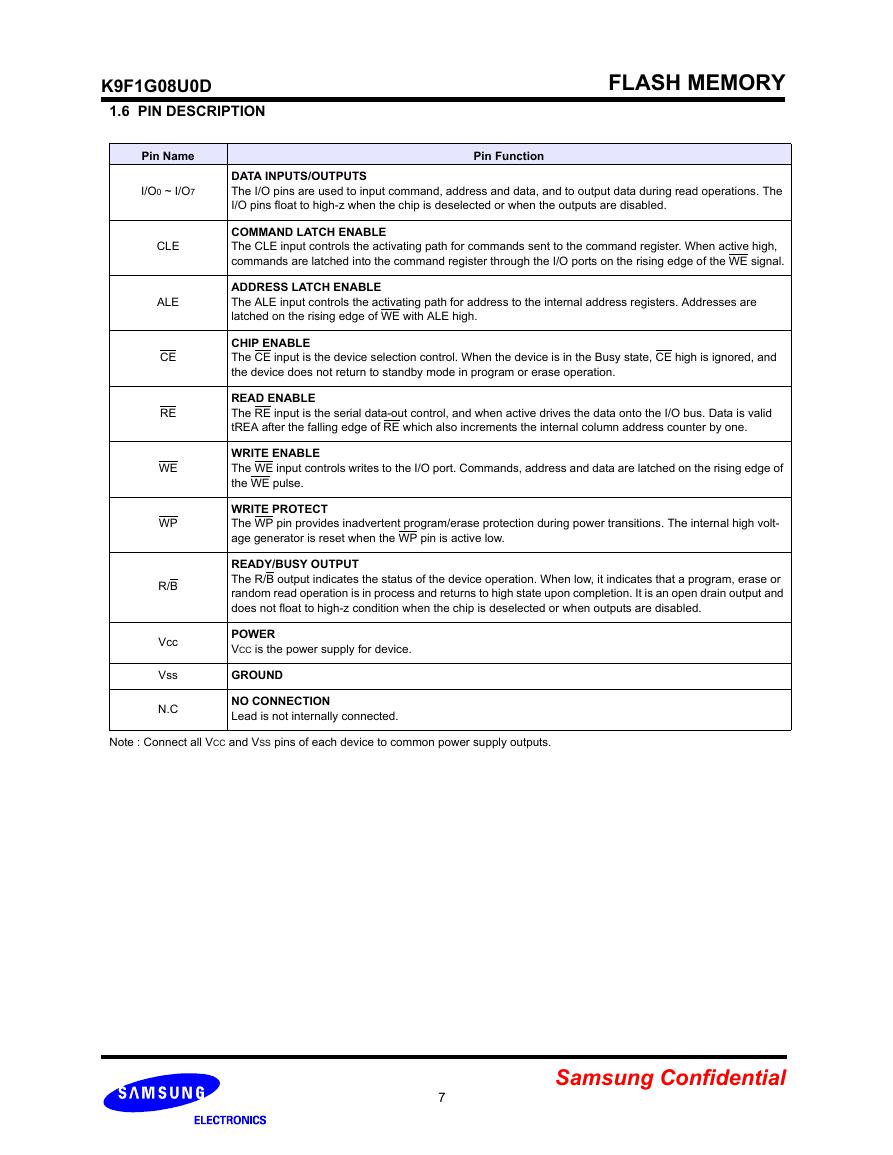

1.6 PIN DESCRIPTION

2.1 ABSOLUTE MAXIMUM RATINGS

2.2 RECOMMENDED OPERATING CONDITIONS

2.3 DC AND OPERATING CHARACTERISTICS(Recommended operating conditions otherwise noted.)

2.4 VALID BLOCK

2.5 AC TEST CONDITION

2.6 CAPACITANCE(TA=25°C, VCC=3.3V, f=1.0MHz)

2.7 MODE SELECTION

2.8 Program / Erase Characteristics

2.9 AC Timing Characteristics for Command / Address / Data Input

2.10 AC Characteristics for Operation

3.1 Initial Invalid Block(s)

3.2 Identifying Initial Invalid Block(s)

3.3 Error in write or read operation

3.4 Addressing for program operation

4.1 Command Latch Cycle

4.2 Address Latch Cycle

4.3 Input Data Latch Cycle

4.4 Status Read Cycle

4.5 Read Operation

4.6 Read Operation(Intercepted by CE)

4.7 Random Data Output In a Page

4.8 Page Program Operation

4.9 Page Program Operation with Random Data Input

4.10 Copy-Back Program Operation with Random Data Input

4.11 Block Erase Operation

4.12 Read ID Operation

5.1 PAGE READ

5.2 PAGE PROGRAM

5.3 Copy-Back Program

5.4 BLOCK ERASE

5.5 READ STATUS

5.6 Read ID

5.7 RESET

5.8 READY/BUSY

Previous Generation Product

Current Generation Device

Part ID

K9F1G08U0C

K9F1G08U0D

Features & Operations

1. tR: 25us / tPROG(200us typ, 700us Max)

tERS(1.5ms Typ, 10ms Max)

2. tRC/tWC: 25ns

3. 2 Plane Program: support

4. 2Plane Copy-back Program: Support

5. 2Plane Erase: Support

6. EDO: Support

1. tR: 35us / tPROG(250us typ, 750us Max)

tERS(2ms Typ, 10ms Max)

2. tRC/tWC: 30ns

3. 2 Plane Program: N/A

4. 2Plane Copy-back Program: N/A

5. 2Plane Erase: N/A

6. EDO: N/A

AC & DC Parameters

1. ICC1 : 15mA(typ)/ 30mA(max)

2. ICC2 : 15mA(typ)/ 30mA(max)

3. ICC3 : 15mA(typ)/ 30mA(max)

1. ICC1 : 20mA(typ)/ 35mA(max)

2. ICC2 : 20mA(typ)/ 35mA(max)

3. ICC3 : 20mA(typ)/ 35mA(max)

Technical Notes

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf