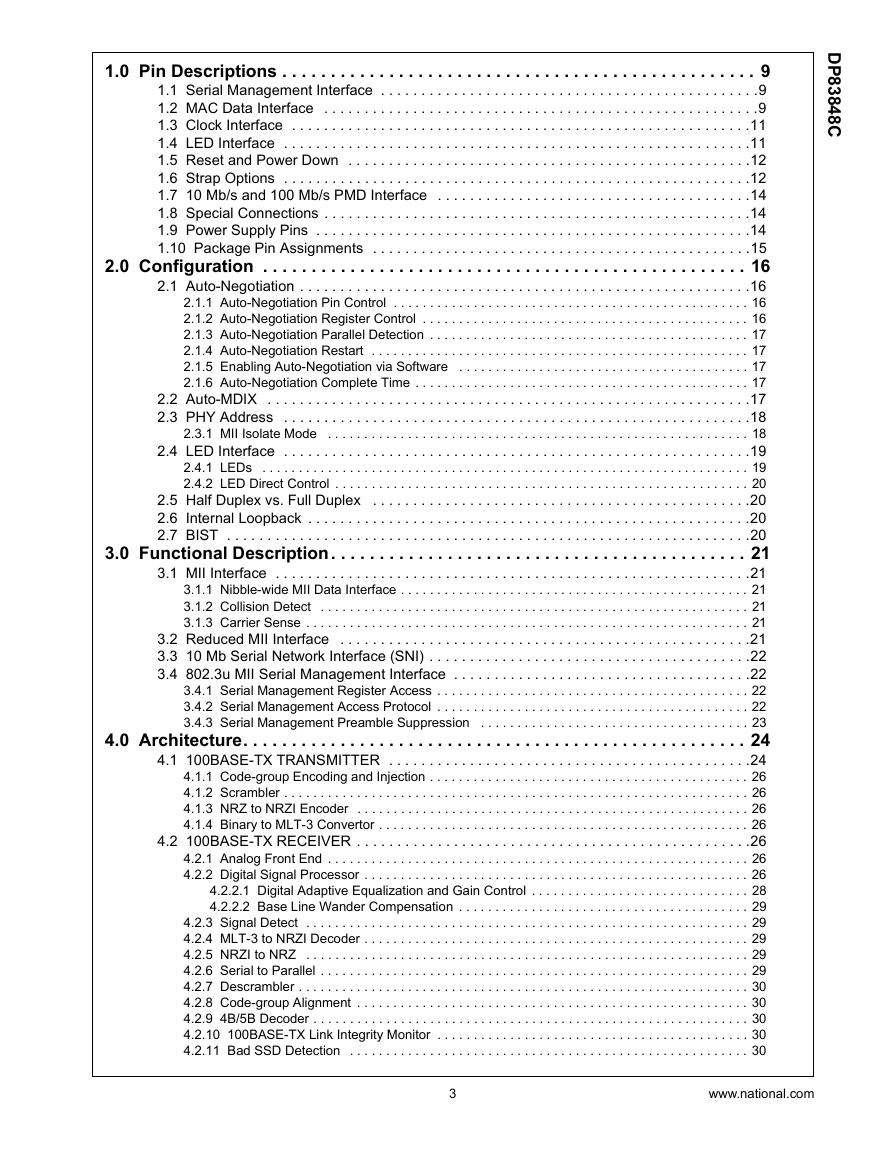

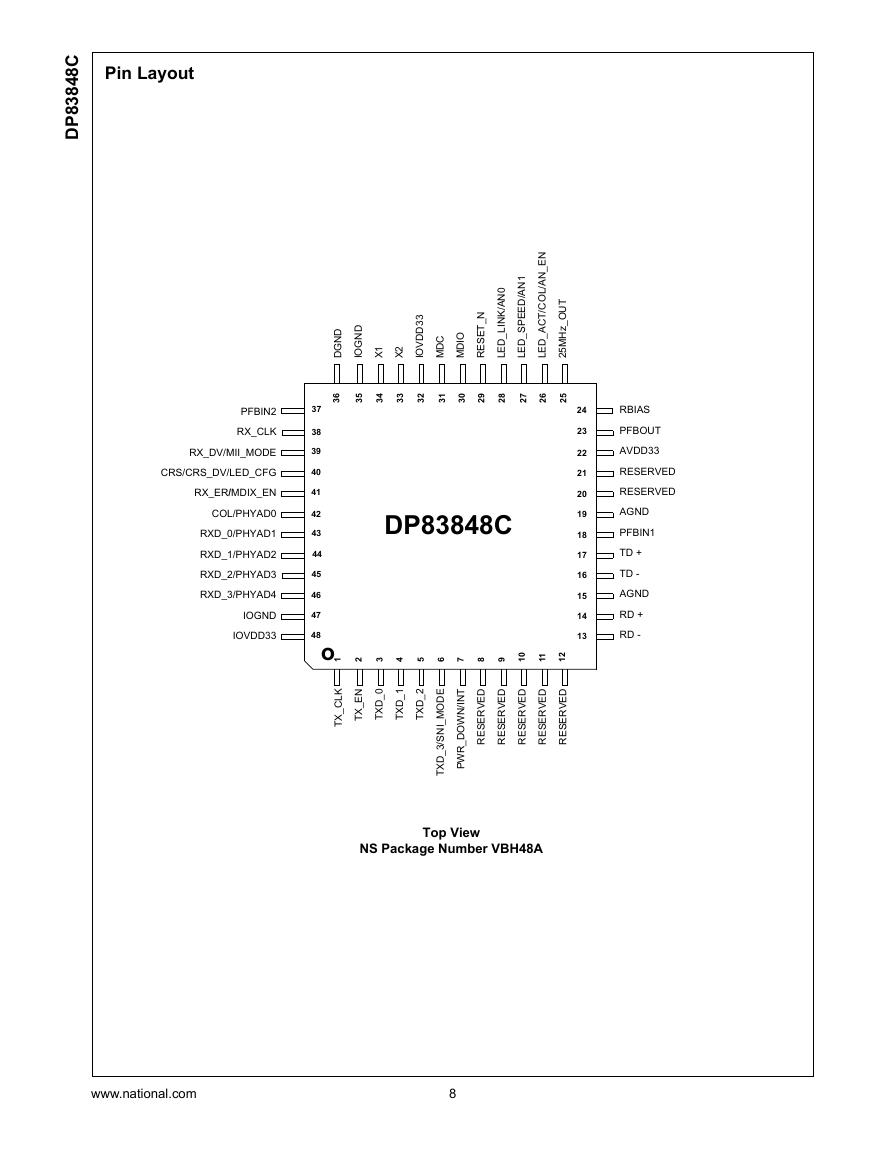

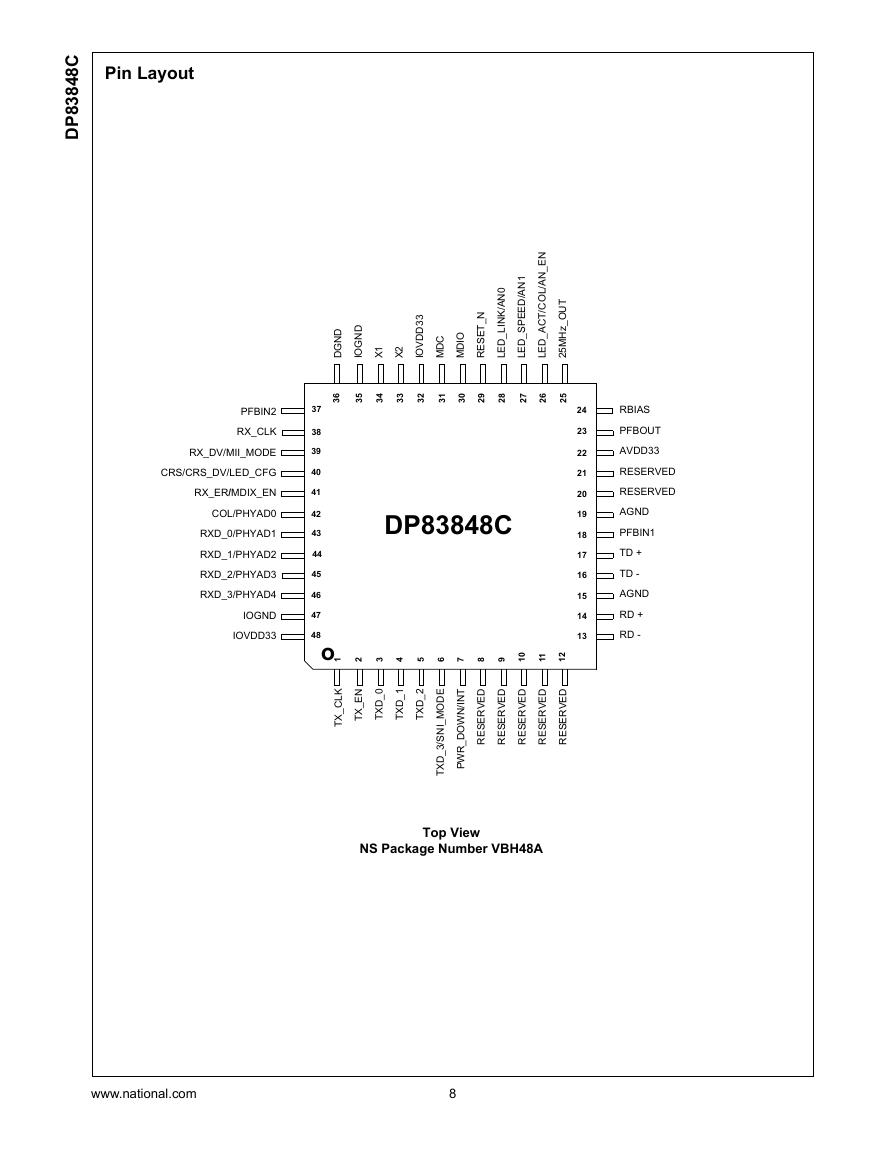

1.0 Pin Descriptions

1.1 Serial Management Interface

1.2 MAC Data Interface

1.3 Clock Interface

1.4 LED Interface

1.5 Reset and Power Down

1.6 Strap Options

1.7 10 Mb/s and 100 Mb/s PMD Interface

1.8 Special Connections

1.9 Power Supply Pins

1.10 Package Pin Assignments

2.0 Configuration

2.1 Auto-Negotiation

2.1.1 Auto-Negotiation Pin Control

2.1.2 Auto-Negotiation Register Control

2.1.3 Auto-Negotiation Parallel Detection

2.1.4 Auto-Negotiation Restart

2.1.5 Enabling Auto-Negotiation via Software

2.1.6 Auto-Negotiation Complete Time

2.2 Auto-MDIX

2.3 PHY Address

2.3.1 MII Isolate Mode

2.4 LED Interface

2.4.1 LEDs

2.4.2 LED Direct Control

2.5 Half Duplex vs. Full Duplex

2.6 Internal Loopback

2.7 BIST

3.0 Functional Description

3.1 MII Interface

3.1.1 Nibble-wide MII Data Interface

3.1.2 Collision Detect

3.1.3 Carrier Sense

3.2 Reduced MII Interface

3.3 10 Mb Serial Network Interface (SNI)

3.4 802.3u MII Serial Management Interface

3.4.1 Serial Management Register Access

3.4.2 Serial Management Access Protocol

3.4.3 Serial Management Preamble Suppression

4.0 Architecture

4.1 100BASE-TX TRANSMITTER

4.1.1 Code-group Encoding and Injection

4.1.2 Scrambler

4.1.3 NRZ to NRZI Encoder

4.1.4 Binary to MLT-3 Convertor

4.2 100BASE-TX RECEIVER

4.2.1 Analog Front End

4.2.2 Digital Signal Processor

4.2.3 Signal Detect

4.2.4 MLT-3 to NRZI Decoder

4.2.5 NRZI to NRZ

4.2.6 Serial to Parallel

4.2.7 Descrambler

4.2.8 Code-group Alignment

4.2.9 4B/5B Decoder

4.2.10 100BASE-TX Link Integrity Monitor

4.2.11 Bad SSD Detection

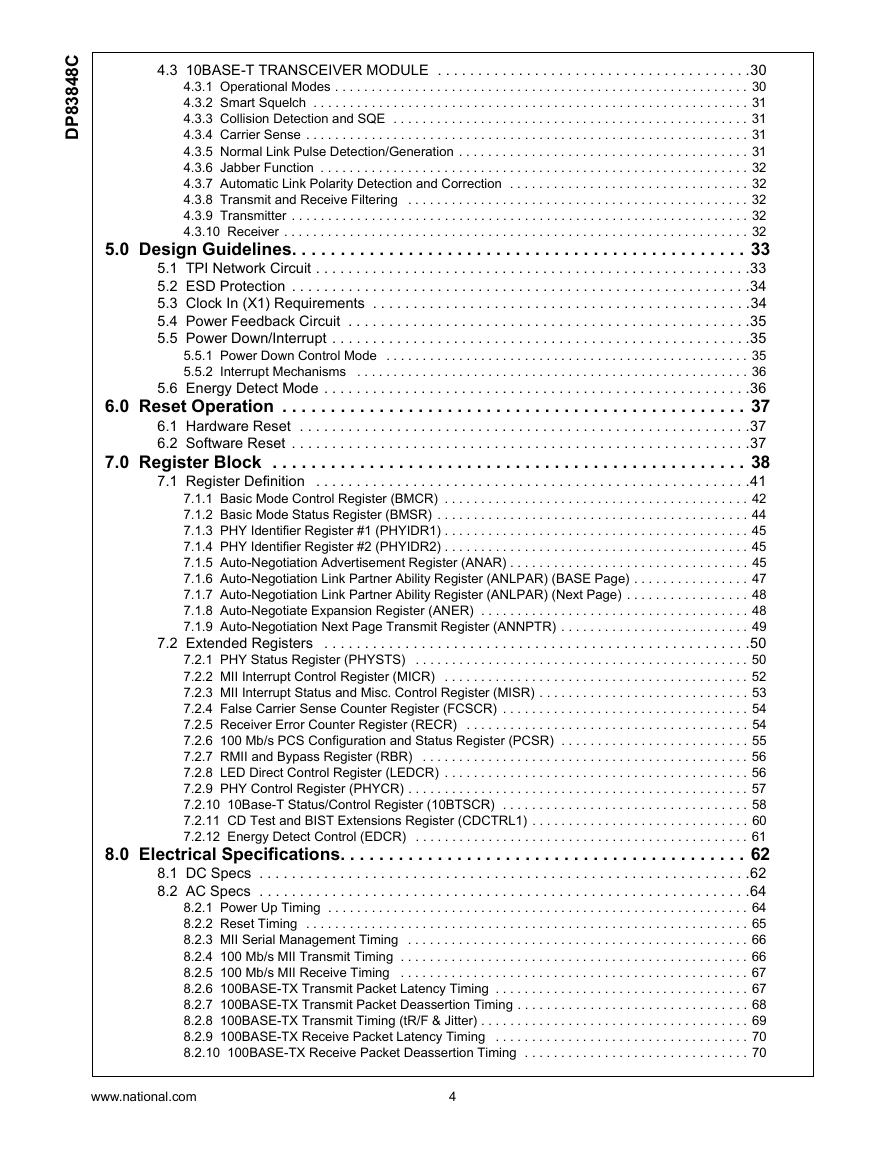

4.3 10BASE-T TRANSCEIVER MODULE

4.3.1 Operational Modes

4.3.2 Smart Squelch

4.3.3 Collision Detection and SQE

4.3.4 Carrier Sense

4.3.5 Normal Link Pulse Detection/Generation

4.3.6 Jabber Function

4.3.7 Automatic Link Polarity Detection and Correction

4.3.8 Transmit and Receive Filtering

4.3.9 Transmitter

4.3.10 Receiver

5.0 Design Guidelines

5.1 TPI Network Circuit

5.2 ESD Protection

5.3 Clock In (X1) Requirements

5.4 Power Feedback Circuit

5.5 Power Down/Interrupt

5.5.1 Power Down Control Mode

5.5.2 Interrupt Mechanisms

5.6 Energy Detect Mode

6.0 Reset Operation

6.1 Hardware Reset

6.2 Software Reset

7.0 Register Block

7.1 Register Definition

7.1.1 Basic Mode Control Register (BMCR)

7.1.2 Basic Mode Status Register (BMSR)

7.1.3 PHY Identifier Register #1 (PHYIDR1)

7.1.4 PHY Identifier Register #2 (PHYIDR2)

7.1.5 Auto-Negotiation Advertisement Register (ANAR)

7.1.6 Auto-Negotiation Link Partner Ability Register (ANLPAR) (BASE Page)

7.1.7 Auto-Negotiation Link Partner Ability Register (ANLPAR) (Next Page)

7.1.8 Auto-Negotiate Expansion Register (ANER)

7.1.9 Auto-Negotiation Next Page Transmit Register (ANNPTR)

7.2 Extended Registers

7.2.1 PHY Status Register (PHYSTS)

7.2.2 MII Interrupt Control Register (MICR)

7.2.3 MII Interrupt Status and Misc. Control Register (MISR)

7.2.4 False Carrier Sense Counter Register (FCSCR)

7.2.5 Receiver Error Counter Register (RECR)

7.2.6 100 Mb/s PCS Configuration and Status Register (PCSR)

7.2.7 RMII and Bypass Register (RBR)

7.2.8 LED Direct Control Register (LEDCR)

7.2.9 PHY Control Register (PHYCR)

7.2.10 10Base-T Status/Control Register (10BTSCR)

7.2.11 CD Test and BIST Extensions Register (CDCTRL1)

7.2.12 Energy Detect Control (EDCR)

8.0 Electrical Specifications

8.1 DC Specs

8.2 AC Specs

8.2.1 Power Up Timing

8.2.2 Reset Timing

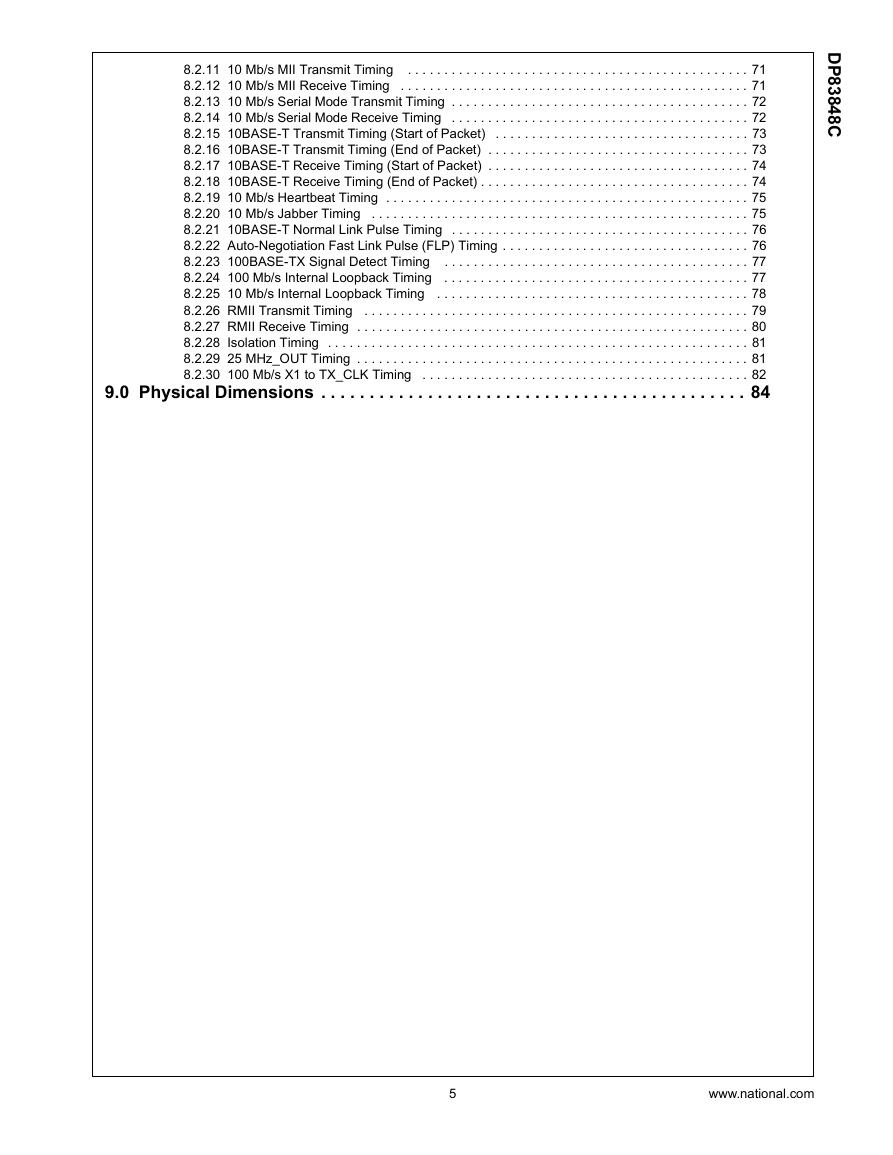

8.2.3 MII Serial Management Timing

8.2.4 100 Mb/s MII Transmit Timing

8.2.5 100 Mb/s MII Receive Timing

8.2.6 100BASE-TX Transmit Packet Latency Timing

8.2.7 100BASE-TX Transmit Packet Deassertion Timing

8.2.8 100BASE-TX Transmit Timing (tR/F & Jitter)

8.2.9 100BASE-TX Receive Packet Latency Timing

8.2.10 100BASE-TX Receive Packet Deassertion Timing

8.2.11 10 Mb/s MII Transmit Timing

8.2.12 10 Mb/s MII Receive Timing

8.2.13 10 Mb/s Serial Mode Transmit Timing

8.2.14 10 Mb/s Serial Mode Receive Timing

8.2.15 10BASE-T Transmit Timing (Start of Packet)

8.2.16 10BASE-T Transmit Timing (End of Packet)

8.2.17 10BASE-T Receive Timing (Start of Packet)

8.2.18 10BASE-T Receive Timing (End of Packet)

8.2.19 10 Mb/s Heartbeat Timing

8.2.20 10 Mb/s Jabber Timing

8.2.21 10BASE-T Normal Link Pulse Timing

8.2.22 Auto-Negotiation Fast Link Pulse (FLP) Timing

8.2.23 100BASE-TX Signal Detect Timing

8.2.24 100 Mb/s Internal Loopback Timing

8.2.25 10 Mb/s Internal Loopback Timing

8.2.26 RMII Transmit Timing

8.2.27 RMII Receive Timing

8.2.28 Isolation Timing

8.2.29 25 MHz_OUT Timing

8.2.30 100 Mb/s X1 to TX_CLK Timing

9.0 Physical Dimensions

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf