General Description

The MAX705–MAX708/MAX813L microprocessor (µP)

supervisory circuits reduce the complexity and number of

components required to monitor power-supply and battery

functions in µP systems. These devices significantly improve

system reliability and accuracy compared to separate ICs or

discrete components.

The MAX705/MAX706/MAX813L provide four functions:

1) A reset output during power-up, power-down, and

brownout conditions.

2) An independent watchdog output that goes low if

the watchdog input has not been toggled within 1.6

seconds.

3) A 1.25V threshold detector for power-fail warning, low-

battery detection, or for monitoring a power supply

other than +5V.

4) An active-low manual-reset input.

The MAX707/MAX708 are the same as the MAX705/

MAX706, except an active-high reset is substituted for

the watchdog timer. The MAX813L is the same as the

MAX705, except RESET is provided instead of RESET.

Two supply-voltage monitor levels are available: The

MAX705/MAX707/MAX813L generate a reset pulse when

the supply voltage drops below 4.65V, while the MAX706/

MAX708 generate a reset pulse below 4.40V. All four parts

are available in 8-pin DIP, SO, and µMAX® packages.

Applications

● Computers

● Controllers

● Intelligent Instruments

● Critical μP Power Monitoring

Pin Configurations appear at end of data sheet.

Benefits and Features

● Supervisory-Function Integration Significantly

Improves System Reliability While Reducing Board

Space

• μMAX Package

• Guaranteed RESET Valid at VCC = 1V

- 200ms Reset Pulse Width

- Debounced TTL/CMOS-Compatible Manual-

- Active-High Reset Output (MAX707/MAX708/

Reset Input

MAX813L)

• Precision-Supply Voltage Monitor

- 4.65V (MAX705/MAX707/MAX813L)

- 4.40V (MAX706/MAX708)

• Voltage Monitor for Power-Fail or Low-Battery

Warning

Ordering Information

PART

TEMP RANGE

0°C to +70°C

0°C to +70°C

0°C to +70°C

0°C to +70°C

PIN-PACKAGE

8 Plastic DIP

8 SO

8 μMAX

Dice*

MAX705CPA

MAX705CSA

MAX705CUA

MAX705C/D

*Dice are specified at TA = +25°C.

**Contact factory for availability and processing to MIL-STD-883.

Devices in PDIP, SO, and μMAX packages are available in both

leaded and lead(Pb)-free/RoHS-compliant packaging. Specify

lead-free by adding the + symbol at the endof the part number

when ordering.

Lead-free packaging is not available for CERDIP packages.

Ordering Information continued at end of data sheet.

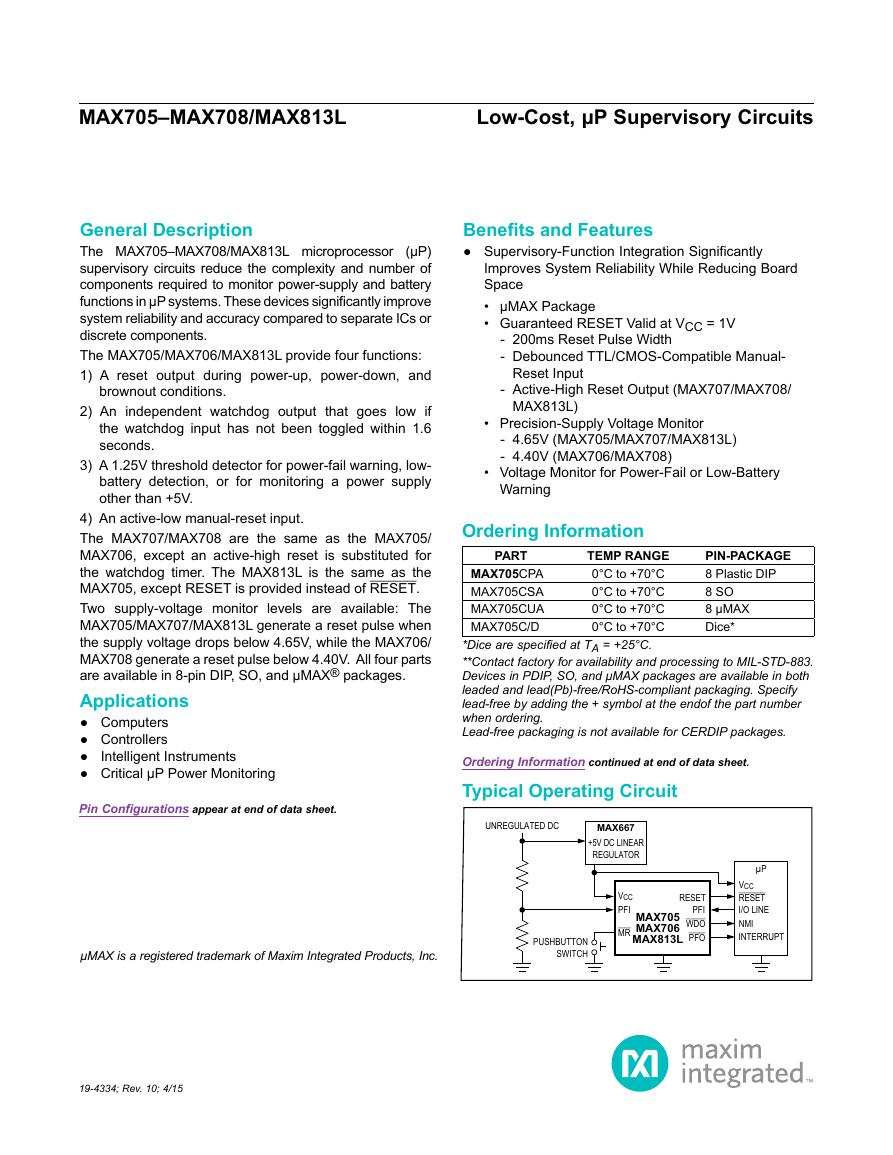

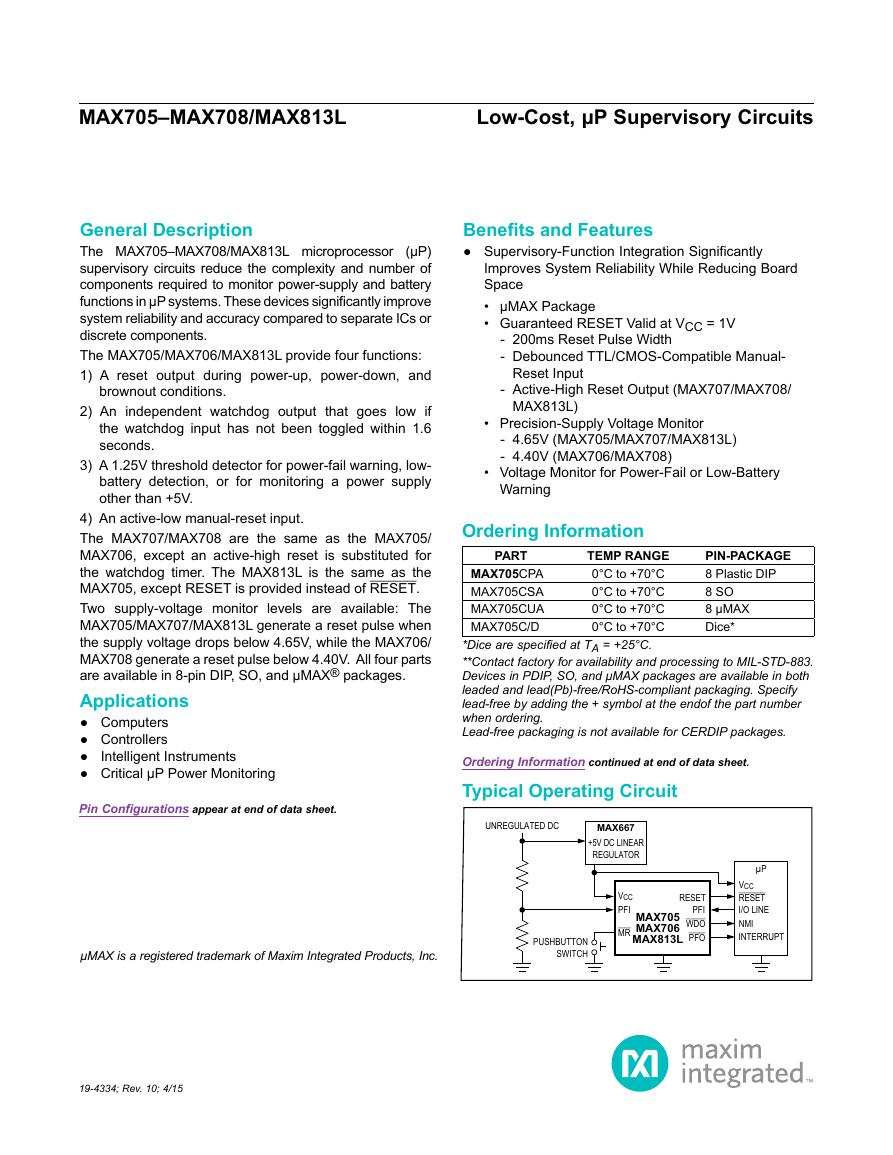

Typical Operating Circuit

UNREGULATED DC

MAX667

+5V DC LINEAR

REGULATOR

VCC

PFI

RESET

PFI

WDO

PFO

MAX705

MAX706

MAX813L

µMAX is a registered trademark of Maxim Integrated Products, Inc.

MR

PUSHBUTTON

SWITCH

19-4334; Rev. 10; 4/15

µP

VCC

RESET

I/O LINE

NMI

INTERRUPT

MAX705–MAX708/MAX813LLow-Cost, μP Supervisory Circuits�

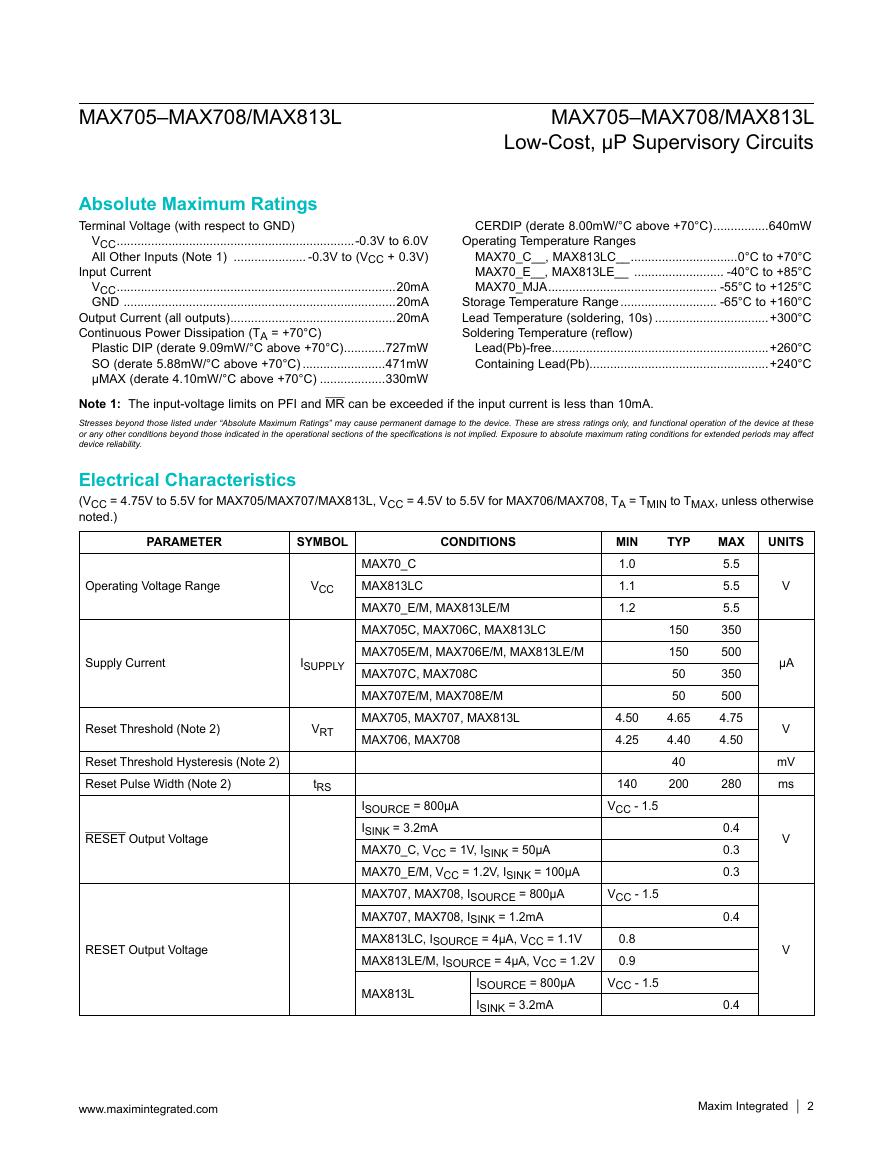

Absolute Maximum Ratings

Terminal Voltage (with respect to GND)

VCC .....................................................................-0.3V to 6.0V

All Other Inputs (Note 1) ..................... -0.3V to (VCC + 0.3V)

Input Current

VCC .................................................................................20mA

GND ...............................................................................20mA

Output Current (all outputs) ................................................20mA

Continuous Power Dissipation (TA = +70°C)

Plastic DIP (derate 9.09mW/°C above +70°C) ............727mW

SO (derate 5.88mW/°C above +70°C) ........................471mW

μMAX (derate 4.10mW/°C above +70°C) ...................330mW

Note 1: The input-voltage limits on PFI and MR can be exceeded if the input current is less than 10mA.

Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these

or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect

device reliability.

CERDIP (derate 8.00mW/°C above +70°C) ................640mW

Operating Temperature Ranges

MAX70_C__, MAX813LC__ ...............................0°C to +70°C

MAX70_E__, MAX813LE__ .......................... -40°C to +85°C

MAX70_MJA ................................................. -55°C to +125°C

Storage Temperature Range ............................ -65°C to +160°C

Lead Temperature (soldering, 10s) .................................+300°C

Soldering Temperature (reflow)

Lead(Pb)-free...............................................................+260°C

Containing Lead(Pb) ....................................................+240°C

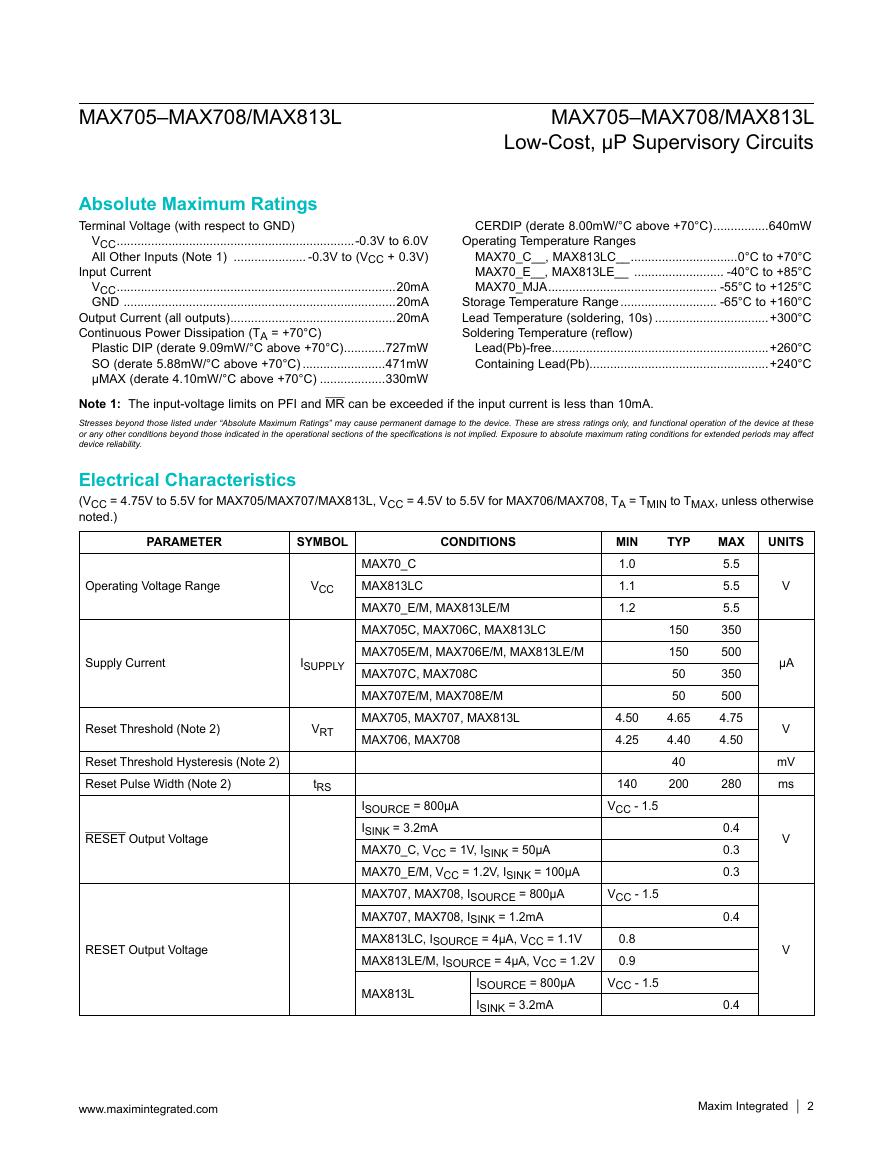

Electrical Characteristics

(VCC = 4.75V to 5.5V for MAX705/MAX707/MAX813L, VCC = 4.5V to 5.5V for MAX706/MAX708, TA = TMIN to TMAX, unless otherwise

noted.)

PARAMETER

SYMBOL

CONDITIONS

MAX70_C

MAX813LC

MAX70_E/M, MAX813LE/M

MAX705C, MAX706C, MAX813LC

MAX705E/M, MAX706E/M, MAX813LE/M

MAX707C, MAX708C

MAX707E/M, MAX708E/M

MAX705, MAX707, MAX813L

MAX706, MAX708

MIN

1.0

1.1

1.2

4.50

4.25

140

TYP

150

150

50

50

4.65

4.40

40

200

Operating Voltage Range

VCC

Supply Current

ISUPPLY

Reset Threshold (Note 2)

Reset Threshold Hysteresis (Note 2)

Reset Pulse Width (Note 2)

VRT

tRS

RESET Output Voltage

RESET Output Voltage

ISOURCE = 800μA

ISINK = 3.2mA

MAX70_C, VCC = 1V, ISINK = 50μA

MAX70_E/M, VCC = 1.2V, ISINK = 100μA

MAX707, MAX708, ISOURCE = 800μA

MAX707, MAX708, ISINK = 1.2mA

MAX813LC, ISOURCE = 4μA, VCC = 1.1V

MAX813LE/M, ISOURCE = 4μA, VCC = 1.2V

MAX813L

ISOURCE = 800μA

ISINK = 3.2mA

VCC - 1.5

VCC - 1.5

0.8

0.9

VCC - 1.5

UNITS

V

µA

V

mV

ms

V

V

MAX

5.5

5.5

5.5

350

500

350

500

4.75

4.50

280

0.4

0.3

0.3

0.4

0.4

Maxim Integrated │ 2

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

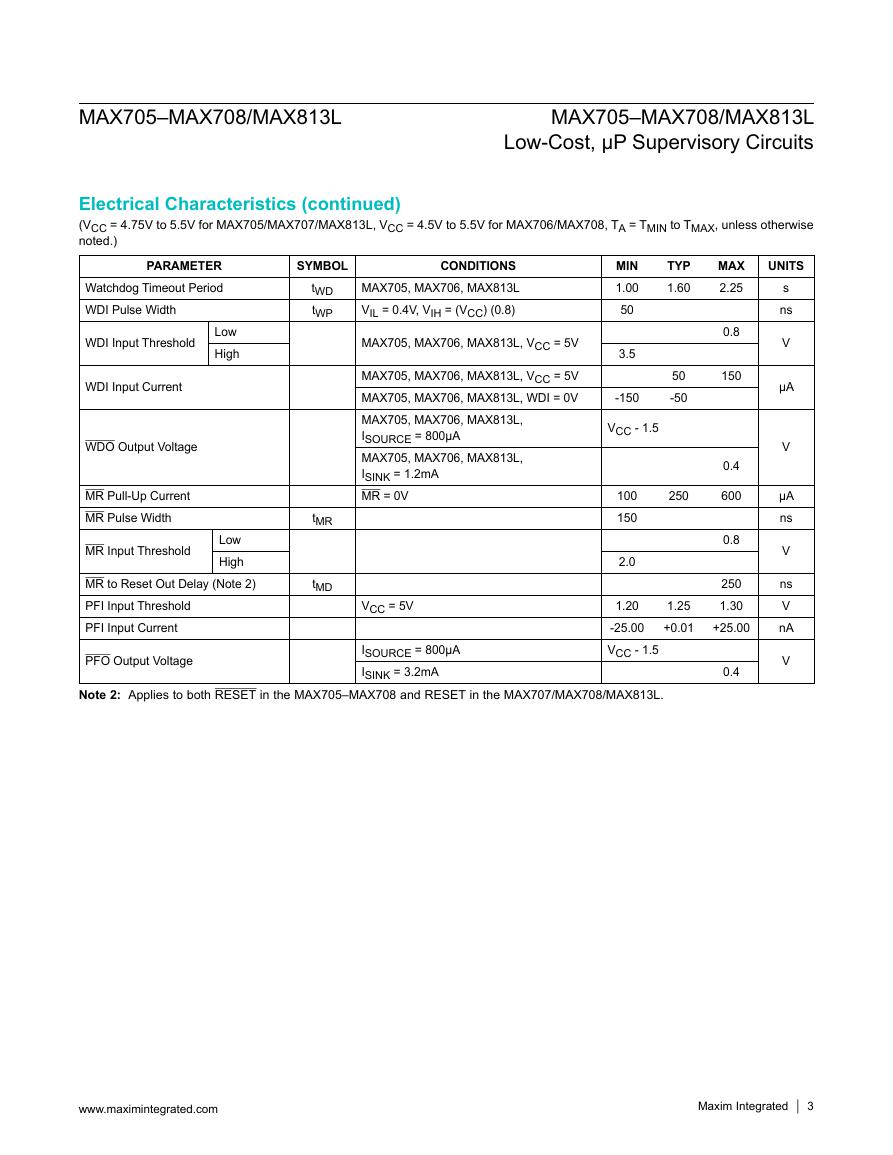

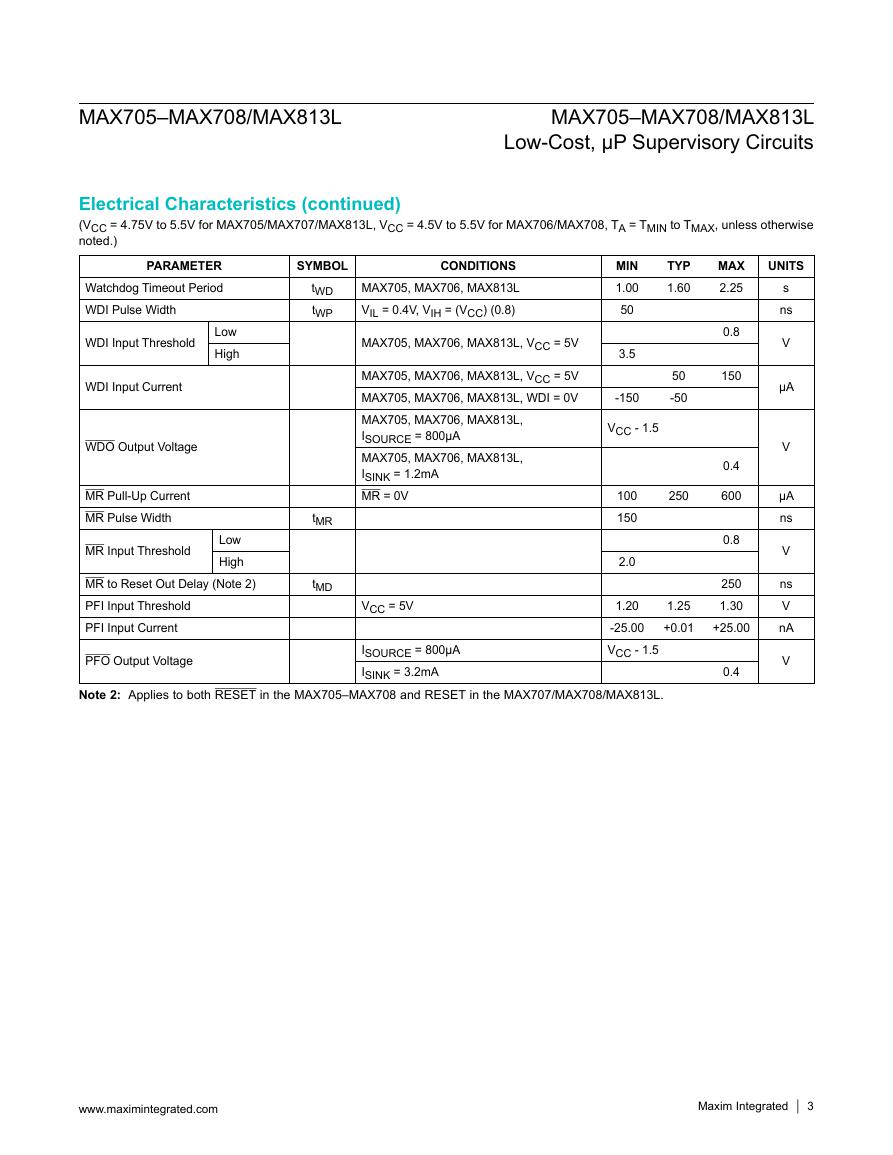

Electrical Characteristics (continued)

(VCC = 4.75V to 5.5V for MAX705/MAX707/MAX813L, VCC = 4.5V to 5.5V for MAX706/MAX708, TA = TMIN to TMAX, unless otherwise

noted.)

PARAMETER

Watchdog Timeout Period

WDI Pulse Width

WDI Input Threshold

Low

High

WDI Input Current

WDO Output Voltage

MR Pull-Up Current

MR Pulse Width

MR Input Threshold

Low

High

MR to Reset Out Delay (Note 2)

PFI Input Threshold

PFI Input Current

PFO Output Voltage

SYMBOL

tWD

tWP

CONDITIONS

MAX705, MAX706, MAX813L

VIL = 0.4V, VIH = (VCC) (0.8)

MAX705, MAX706, MAX813L, VCC = 5V

MAX705, MAX706, MAX813L, VCC = 5V

MAX705, MAX706, MAX813L, WDI = 0V

MAX705, MAX706, MAX813L,

ISOURCE = 800μA

MAX705, MAX706, MAX813L,

ISINK = 1.2mA

MR = 0V

tMR

tMD

MIN

1.00

50

3.5

-150

VCC - 1.5

100

150

2.0

50

-50

250

VCC = 5V

ISOURCE = 800μA

ISINK = 3.2mA

1.25

+0.01

1.20

-25.00

VCC - 1.5

TYP

1.60

MAX

2.25

UNITS

s

ns

V

µA

V

μA

ns

V

ns

V

nA

V

0.8

150

0.4

600

0.8

250

1.30

+25.00

0.4

Note 2: Applies to both RESET in the MAX705–MAX708 and RESET in the MAX707/MAX708/MAX813L.

Maxim Integrated │ 3

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

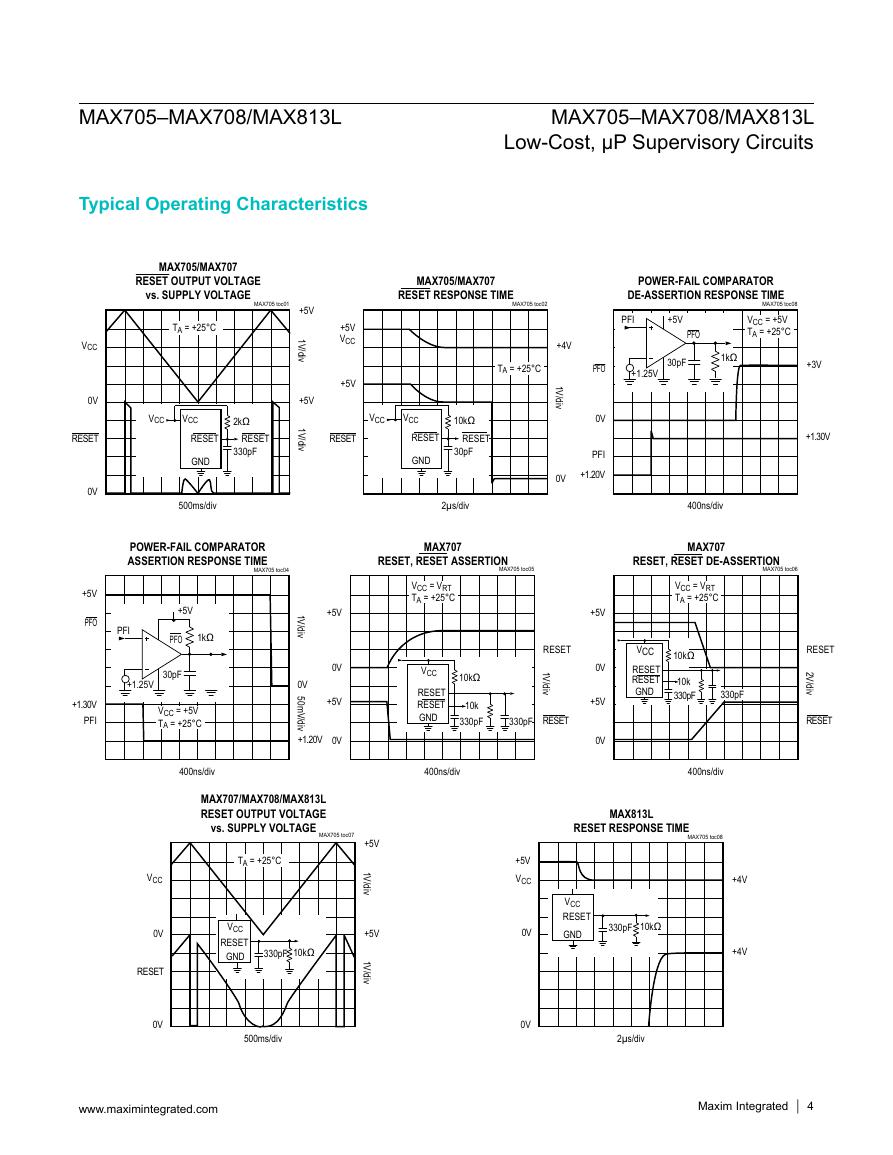

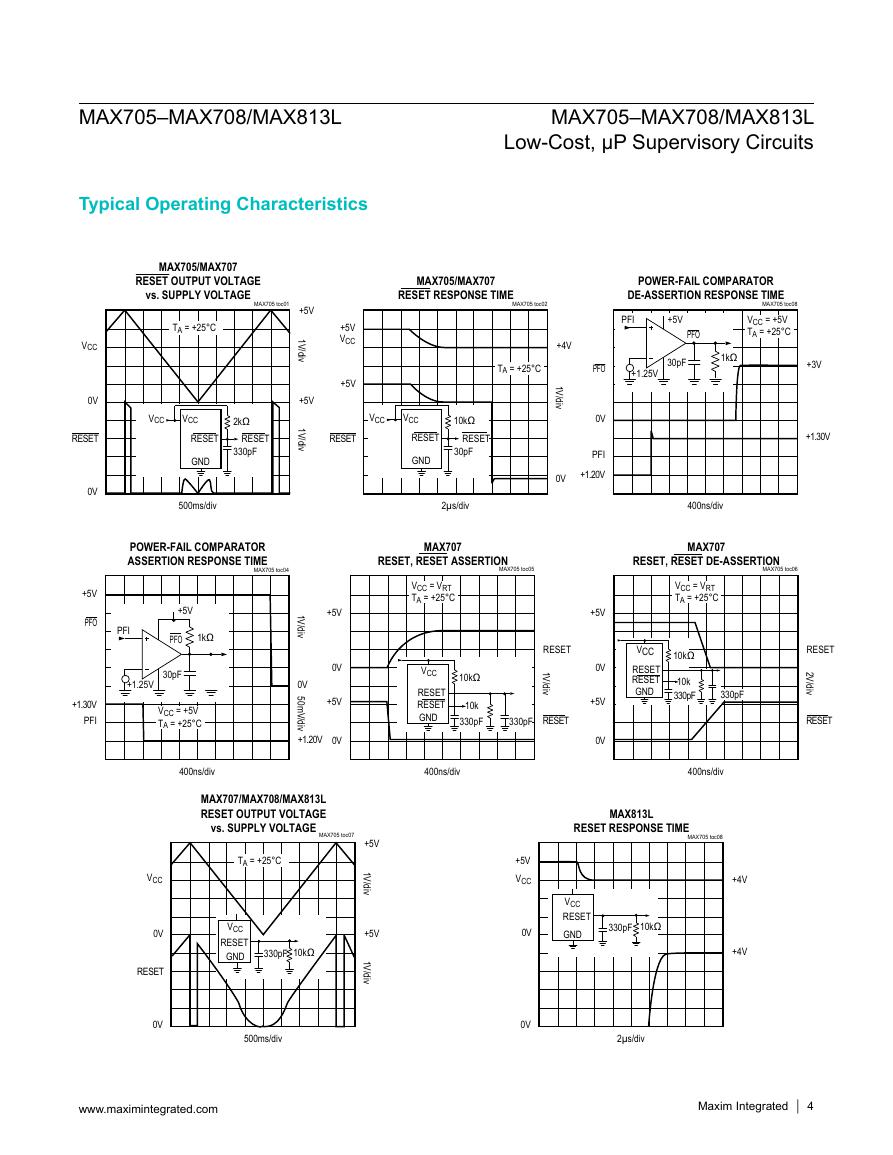

Typical Operating Characteristics

MAX705/MAX707

RESET OUTPUT VOLTAGE

vs. SUPPLY VOLTAGE

MAX705 toc01

+5V

VCC

0V

RESET

0V

TA = +25°C

2kΩ

RESET

330pF

VCC

VCC

RESET

GND

500ms/div

POWER-FAIL COMPARATOR

ASSERTION RESPONSE TIME

MAX705 toc04

+5V

PFO

PFI

+5V

PFO

1kΩ

30pF

+1.25V

VCC = +5V

TA = +25°C

+1.30V

PFI

/

1

V

d

v

i

+5V

/

1

V

d

v

i

/

1

V

d

v

i

0V

5

0

m

V

d

v

/

i

+5V

VCC

+5V

RESET

+5V

0V

+5V

+1.20V

0V

400ns/div

MAX705/MAX707

RESET RESPONSE TIME

MAX705 toc02

+4V

TA = +25°C

/

1

V

d

v

i

POWER-FAIL COMPARATOR

DE-ASSERTION RESPONSE TIME

MAX705 toc08

PFI

+5V

PFO

VCC = +5V

TA = +25°C

30pF

+1.25V

1kΩ

PFO

0V

VCC

VCC

RESET

GND

10kΩ

RESET

30pF

PFI

+1.20V

0V

2µs/div

400ns/div

MAX707

RESET, RESET ASSERTION

MAX705 toc05

MAX707

RESET, RESET DE-ASSERTION

MAX705 toc06

VCC = VRT

TA = +25°C

VCC

RESET

RESET

GND

10kΩ

10k

330pF

400ns/div

RESET

/

1

V

d

v

i

330pF

RESET

+5V

0V

+5V

0V

VCC = VRT

TA = +25°C

VCC

RESET

RESET

GND

10kΩ

10k

330pF

330pF

400ns/div

+3V

+1.30V

RESET

/

2

V

d

v

i

RESET

MAX707/MAX708/MAX813L

RESET OUTPUT VOLTAGE

vs. SUPPLY VOLTAGE

MAX705 toc07

+5V

/

1

V

d

v

i

+5V

/

1

V

d

v

i

TA = +25°C

VCC

RESET

GND

330pF 10kΩ

VCC

0V

RESET

0V

MAX813L

RESET RESPONSE TIME

MAX705 toc08

VCC

RESET

GND

330pF 10kΩ

+4V

+4V

+5V

VCC

0V

0V

500ms/div

2µs/div

Maxim Integrated │ 4

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

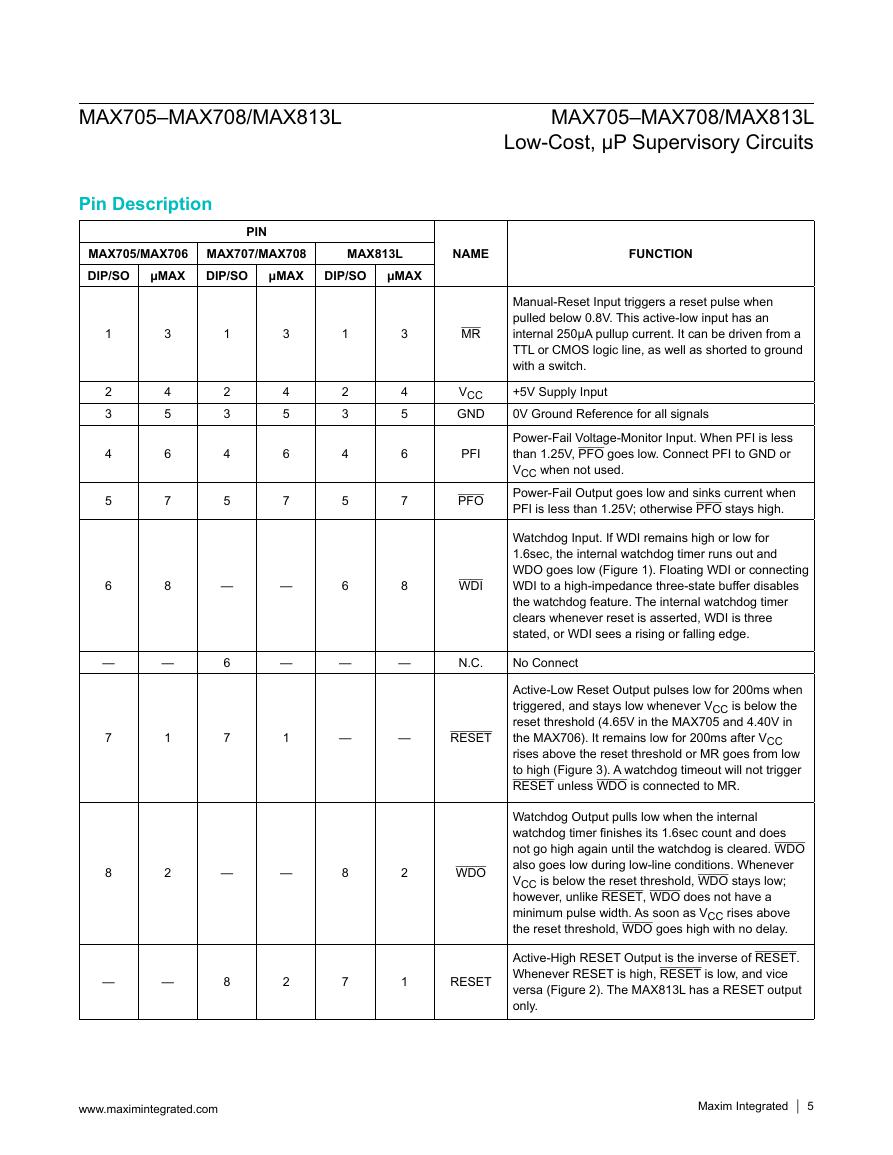

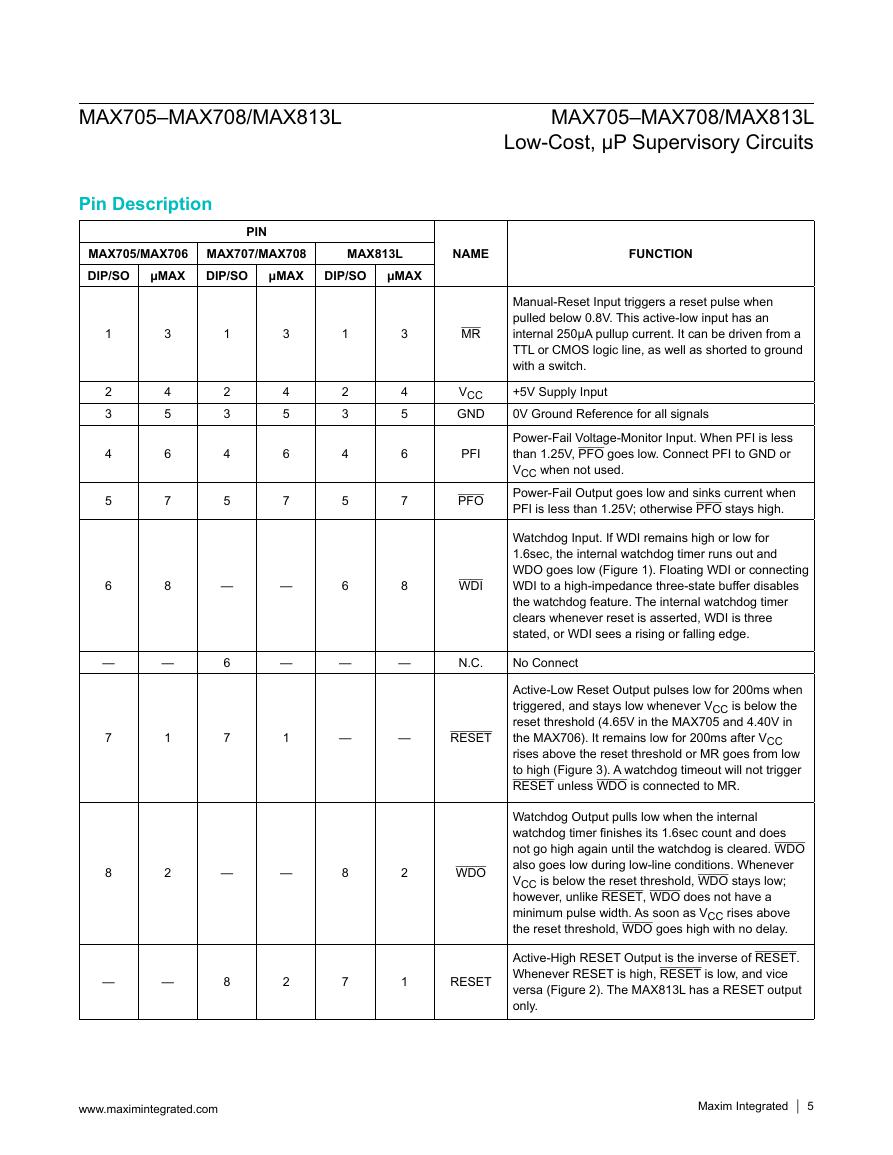

Pin Description

PIN

MAX705/MAX706 MAX707/MAX708

μMAX

DIP/SO

DIP/SO

μMAX

MAX813L

NAME

DIP/SO

μMAX

FUNCTION

1

2

3

4

5

6

3

4

5

6

7

8

—

—

7

8

1

2

1

2

3

4

5

—

6

7

3

4

5

6

7

—

—

1

—

—

—

—

8

2

1

2

3

4

5

6

—

—

8

7

3

4

5

6

7

8

MR

VCC

GND

PFI

PFO

WDI

Manual-Reset Input triggers a reset pulse when

pulled below 0.8V. This active-low input has an

internal 250μA pullup current. It can be driven from a

TTL or CMOS logic line, as well as shorted to ground

with a switch.

+5V Supply Input

0V Ground Reference for all signals

Power-Fail Voltage-Monitor Input. When PFI is less

than 1.25V, PFO goes low. Connect PFI to GND or

VCC when not used.

Power-Fail Output goes low and sinks current when

PFI is less than 1.25V; otherwise PFO stays high.

Watchdog Input. If WDI remains high or low for

1.6sec, the internal watchdog timer runs out and

WDO goes low (Figure 1). Floating WDI or connecting

WDI to a high-impedance three-state buffer disables

the watchdog feature. The internal watchdog timer

clears whenever reset is asserted, WDI is three

stated, or WDI sees a rising or falling edge.

—

N.C.

No Connect

—

RESET

WDO

2

1

Active-Low Reset Output pulses low for 200ms when

triggered, and stays low whenever VCC is below the

reset threshold (4.65V in the MAX705 and 4.40V in

the MAX706). It remains low for 200ms after VCC

rises above the reset threshold or MR goes from low

to high (Figure 3). A watchdog timeout will not trigger

RESET unless WDO is connected to MR.

Watchdog Output pulls low when the internal

watchdog timer finishes its 1.6sec count and does

not go high again until the watchdog is cleared. WDO

also goes low during low-line conditions. Whenever

VCC is below the reset threshold, WDO stays low;

however, unlike RESET, WDO does not have a

minimum pulse width. As soon as VCC rises above

the reset threshold, WDO goes high with no delay.

RESET

Active-High RESET Output is the inverse of RESET.

Whenever RESET is high, RESET is low, and vice

versa (Figure 2). The MAX813L has a RESET output

only.

Maxim Integrated │ 5

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

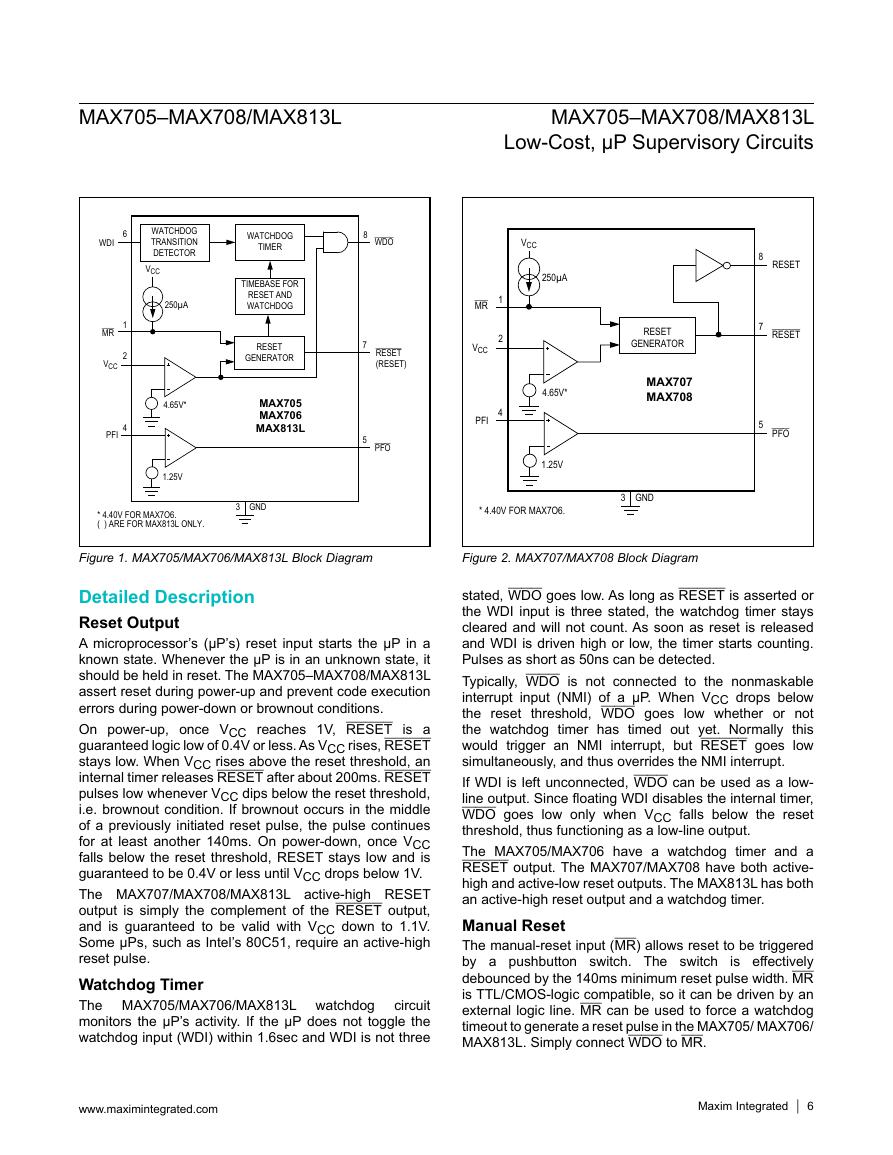

6

1

2

WDI

MR

VCC

4

PFI

WATCHDOG

TRANSITION

DETECTOR

VCC

250µA

4.65V*

1.25V

WATCHDOG

TIMER

TIMEBASE FOR

RESET AND

WATCHDOG

RESET

GENERATOR

MAX705

MAX706

MAX813L

8

WDO

7

RESET

(RESET)

5

PFO

1

2

4

MR

VCC

PFI

VCC

250µA

4.65V*

1.25V

RESET

GENERATOR

MAX707

MAX708

8

7

RESET

RESET

5

PFO

* 4.40V FOR MAX7O6.

( ) ARE FOR MAX813L ONLY.

3

GND

* 4.40V FOR MAX7O6.

3

GND

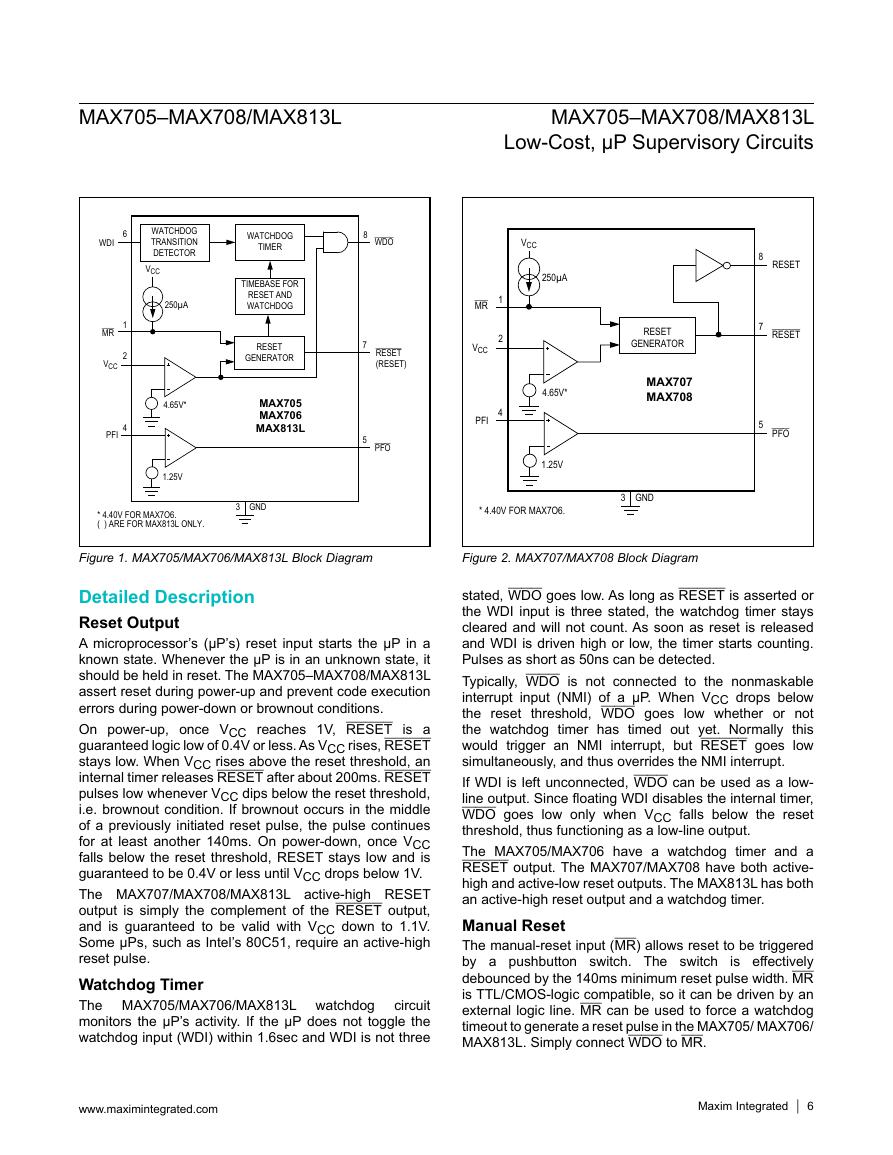

Figure 1. MAX705/MAX706/MAX813L Block Diagram

Figure 2. MAX707/MAX708 Block Diagram

Detailed Description

Reset Output

A microprocessor’s (μP’s) reset input starts the μP in a

known state. Whenever the μP is in an unknown state, it

should be held in reset. The MAX705–MAX708/MAX813L

assert reset during power-up and prevent code execution

errors during power-down or brownout conditions.

On power-up, once VCC reaches 1V, RESET is a

guaranteed logic low of 0.4V or less. As VCC rises, RESET

stays low. When VCC rises above the reset threshold, an

internal timer releases RESET after about 200ms. RESET

pulses low whenever VCC dips below the reset threshold,

i.e. brownout condition. If brownout occurs in the middle

of a previously initiated reset pulse, the pulse continues

for at least another 140ms. On power-down, once VCC

falls below the reset threshold, RESET stays low and is

guaranteed to be 0.4V or less until VCC drops below 1V.

The MAX707/MAX708/MAX813L active-high RESET

output is simply the complement of the RESET output,

and is guaranteed to be valid with VCC down to 1.1V.

Some μPs, such as Intel’s 80C51, require an active-high

reset pulse.

Watchdog Timer

The MAX705/MAX706/MAX813L watchdog

circuit

monitors the μP’s activity. If the μP does not toggle the

watchdog input (WDI) within 1.6sec and WDI is not three

stated, WDO goes low. As long as RESET is asserted or

the WDI input is three stated, the watchdog timer stays

cleared and will not count. As soon as reset is released

and WDI is driven high or low, the timer starts counting.

Pulses as short as 50ns can be detected.

Typically, WDO is not connected to the nonmaskable

interrupt input (NMI) of a μP. When VCC drops below

the reset threshold, WDO goes low whether or not

the watchdog timer has timed out yet. Normally this

would trigger an NMI interrupt, but RESET goes low

simultaneously, and thus overrides the NMI interrupt.

If WDI is left unconnected, WDO can be used as a low-

line output. Since floating WDI disables the internal timer,

WDO goes low only when VCC falls below the reset

threshold, thus functioning as a low-line output.

The MAX705/MAX706 have a watchdog timer and a

RESET output. The MAX707/MAX708 have both active-

high and active-low reset outputs. The MAX813L has both

an active-high reset output and a watchdog timer.

Manual Reset

The manual-reset input (MR) allows reset to be triggered

by a pushbutton switch. The switch

is effectively

debounced by the 140ms minimum reset pulse width. MR

is TTL/CMOS-logic compatible, so it can be driven by an

external logic line. MR can be used to force a watchdog

timeout to generate a reset pulse in the MAX705/ MAX706/

MAX813L. Simply connect WDO to MR.

Maxim Integrated │ 6

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

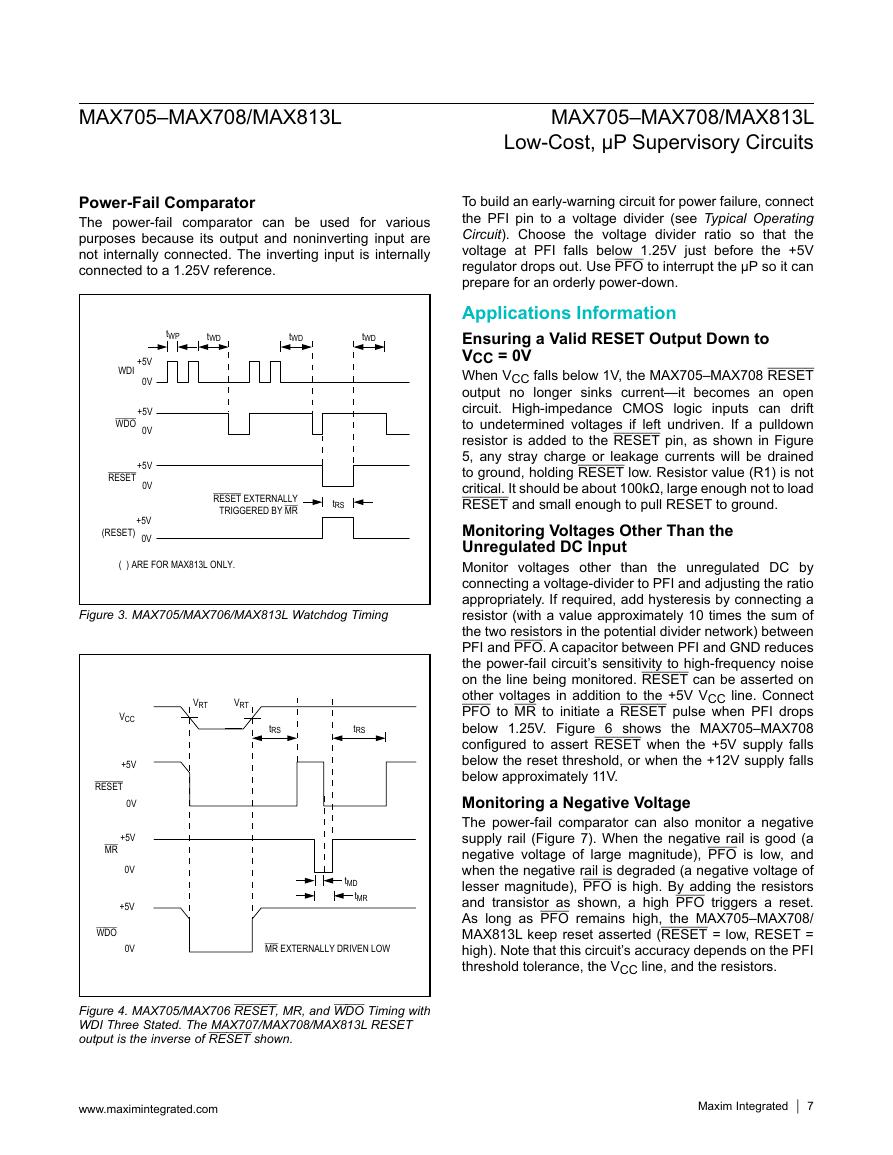

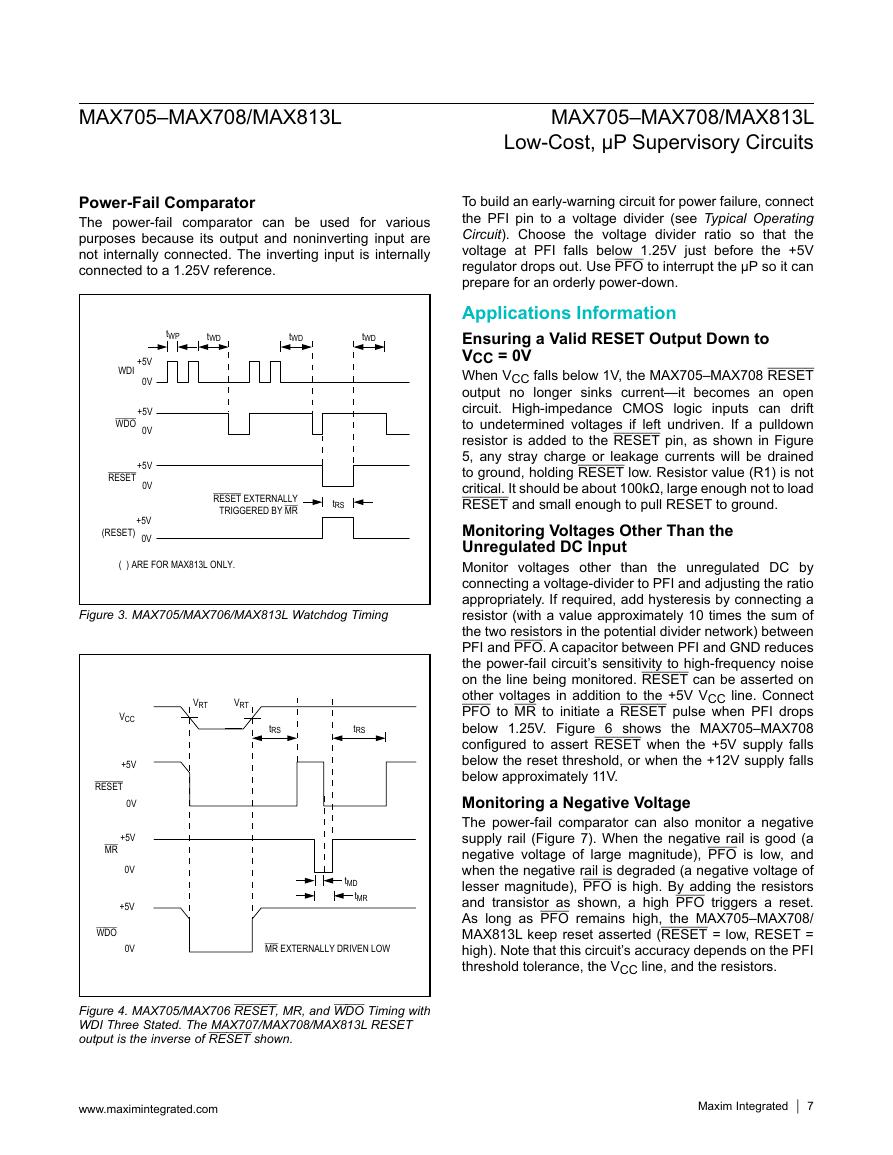

Power-Fail Comparator

The power-fail comparator can be used for various

purposes because its output and noninverting input are

not internally connected. The inverting input is internally

connected to a 1.25V reference.

tWP

tWD

tWD

tWD

WDI

WDO

RESET

(RESET)

+5V

0V

+5V

0V

+5V

0V

+5V

0V

RESET EXTERNALLY

TRIGGERED BY MR

tRS

( ) ARE FOR MAX813L ONLY.

Figure 3. MAX705/MAX706/MAX813L Watchdog Timing

VCC

+5V

RESET

0V

+5V

0V

+5V

0V

MR

WDO

VRT

VRT

tRS

tRS

tMD

tMR

MR EXTERNALLY DRIVEN LOW

Figure 4. MAX705/MAX706 RESET, MR, and WDO Timing with

WDI Three Stated. The MAX707/MAX708/MAX813L RESET

output is the inverse of RESET shown.

To build an early-warning circuit for power failure, connect

the PFI pin to a voltage divider (see Typical Operating

Circuit). Choose the voltage divider ratio so that the

voltage at PFI falls below 1.25V just before the +5V

regulator drops out. Use PFO to interrupt the μP so it can

prepare for an orderly power-down.

Applications Information

Ensuring a Valid RESET Output Down to

VCC = 0V

When VCC falls below 1V, the MAX705–MAX708 RESET

output no longer sinks current—it becomes an open

circuit. High-impedance CMOS logic inputs can drift

to undetermined voltages if left undriven. If a pulldown

resistor is added to the RESET pin, as shown in Figure

5, any stray charge or leakage currents will be drained

to ground, holding RESET low. Resistor value (R1) is not

critical. It should be about 100kΩ, large enough not to load

RESET and small enough to pull RESET to ground.

Monitoring Voltages Other Than the

Unregulated DC Input

Monitor voltages other than the unregulated DC by

connecting a voltage-divider to PFI and adjusting the ratio

appropriately. If required, add hysteresis by connecting a

resistor (with a value approximately 10 times the sum of

the two resistors in the potential divider network) between

PFI and PFO. A capacitor between PFI and GND reduces

the power-fail circuit’s sensitivity to high-frequency noise

on the line being monitored. RESET can be asserted on

other voltages in addition to the +5V VCC line. Connect

PFO to MR to initiate a RESET pulse when PFI drops

below 1.25V. Figure 6 shows the MAX705–MAX708

configured to assert RESET when the +5V supply falls

below the reset threshold, or when the +12V supply falls

below approximately 11V.

Monitoring a Negative Voltage

The power-fail comparator can also monitor a negative

supply rail (Figure 7). When the negative rail is good (a

negative voltage of large magnitude), PFO is low, and

when the negative rail is degraded (a negative voltage of

lesser magnitude), PFO is high. By adding the resistors

and transistor as shown, a high PFO triggers a reset.

As long as PFO remains high, the MAX705–MAX708/

MAX813L keep reset asserted (RESET = low, RESET =

high). Note that this circuit’s accuracy depends on the PFI

threshold tolerance, the VCC line, and the resistors.

Maxim Integrated │ 7

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

MAX70_

RESET

R1

+12V

+5V

1MΩ

1%

130kΩ

1%

PARAMETER

+12V Reset

Threshold at +25°C

VCC

RESET

TO µP

MAX70_

MR

PFO

PFI

GND

MIN TYP MAX UNIT

10.67

10.87

11.50

V

Figure 5. RESET Valid to Ground Circuit

Figure 6. Monitoring Both +5V and +12V

VCC

MR

100kΩ

MAX70_

100kΩ

PFO

2N3904

PFI

RESET

GND

TO µP

+5V

R1

R2

V-

MR

PFO

+5V

0V

+5V

0V

V-

VTRIP

0V

5 1.25

–

R1

=

1.25 VTRIP

–

R2

<

, VTRIP 0

Figure 7. Monitoring a Negative Voltage

BUFFERED RESET TO OTHER SYSTEM COMPONENTS

VCC

MAX70_

RESET

GND

4.7kΩ

VCC

µP

RESET

GND

Figure 6. Monitoring Both +5V and +12V

Interfacing to μPs with

Bidirectional Reset Pins

μPs with bidirectional reset pins, such as the Motorola

68HC11 series, can contend with the MAX705–MAX708

RESET output. If, for example, the RESET output is

driven high and the μP wants to pull it low, indeterminate

logic levels may result. To correct this, connect a 4.7kΩ

resistor between the RESET output and the μP reset I/O,

as in Figure 8. Buffer the RESET output to other system

components.

Maxim Integrated │ 8

MAX705–MAX708/MAX813LMAX705–MAX708/MAX813L Low-Cost, μP Supervisory Circuitswww.maximintegrated.com�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf