SOLOMON SYSTECH

SEMICONDUCTOR TECHNICAL DATA

SSD1351

Advance Information

128 RGB x 128 Dot Matrix

OLED/PLED Segment/Common Driver with Controller

This document contains information on a new product. Specifications and information herein are subject to change

without notice.

http://www.solomon-systech.com

SSD1351

Copyright © 2011 Solomon Systech Limited

Jan 2011

Rev 1.5

P 1/57

�

Version

0.10

1.0

1.1

1.2

1.3

1.4

1.5

Appendix: IC Revision history of SSD1351 Specification

Change Items

1. 1st release

1.

2.

3.

4.

5.

6.

1. Revised section 8.1 MCU interface

Change to Advance Info

Revise die thickness tolerance from ±25um to ±15um

Revise table 12-1 DC characteristic

Revise tables 13 AC characteristic

Revise command table

Revise VCC voltage range

1

2

Change “Gold Bump Die” to “COG” for SSD1351Z in Table 3-1 Ordering

information

Revise typo in Figure 5 1: SSD1351Z Die Drawing ( position of L, T alignment

mark)

Revise typo in P.45 : 10.1.9 Set Function selection (ABh)

3

4 Add Note 2 in application example Fig 14-1

1 Added +/- 0.05mm tolerance for Die Size (after sawing) in Section 5 – P.9

2 Added command C1h in the description of command FDh – P.37

3

4 Updated the ISLP VCI sleep mode current section of Table 12-1 (Max = 50uA when

Revised typo error on the description of command C1h – P.46

internal VDD is enabled) – P.49

Revised declaimer

5

1

2 P.51 Revise Table 13-2 : 6800-Series MCU Parallel Interface Timing

P.30 Update Power On/OFF sequence

3

Characteristics

P.52 Revise Table 13-3 : 8080-Series MCU Parallel Interface Timing

Characteristics

P.53 Revise Table 13-4 : Serial Interface Timing Characteristics (4-wire SPI)

P.54 Revise Table 13-5: Serial Interface Timing Characteristics (3-wire SPI)

4

5

1. Update the power supply on Section 2 (P.7) and Section 12 (P.48)

2. Updated the pin description of VDD and VCI on Table 7-1 (P.15)

3. Updated Section 8.9 “Power On and Off sequence” (P.30)

4. Updated Section 8.10 “VDD Regulator” and Figure 8-15 (P.31)

5. Updated Figure 8-17 (P.31)

6. Updated command ABh (Function selection) on Table 9-1 (P.33) and Section 10.1.9

7. Revise Table 11-1: Maximum Ratings (P.47)

8. Revise DC CHARACTERISTICS information in Table 12-1 (P.48)

9. Revise the information on the application example Figure 14-1 and revised the

(P.44)

diagram (P.54)

Effective Date

10-Jun-08

12-Dec-08

19-Feb-09

31-Aug-09

27-Oct-09

23-Jul-10

02-Feb-11

Solomon Systech

Jan 2011

P 2/57

Rev 1.5

SSD1351

�

CONTENTS

1

2

3

4

5

6

6.1

7

8

GENERAL DESCRIPTION ....................................................................................................7

FEATURES................................................................................................................................7

ORDERING INFORMATION ................................................................................................7

BLOCK DIAGRAM..................................................................................................................8

DIE PAD FLOOR PLAN..........................................................................................................9

PIN ARRANGEMENT...........................................................................................................12

SSD1351UR1 PIN ASSIGNMENT..........................................................................................................12

PIN DESCRIPTIONS .............................................................................................................15

FUNCTIONAL BLOCK DESCRIPTIONS..........................................................................18

8.1 MCU INTERFACE ................................................................................................................................18

8.1.1 MCU Parallel 6800-series Interface................................................................................................................18

8.1.2 MCU Parallel 8080-series Interface................................................................................................................19

8.1.3 MCU Serial Interface (4-wire SPI) .................................................................................................................20

8.1.4 MCU Serial Interface (3-wire SPI) .................................................................................................................21

8.2 RESET CIRCUIT....................................................................................................................................22

8.3 GDDRAM...........................................................................................................................................22

8.3.1 GDDRAM structure........................................................................................................................................22

8.3.2 Data bus to RAM mapping under different input mode..................................................................................23

8.4 COMMAND DECODER..........................................................................................................................24

8.5 OSCILLATOR & TIMING GENERATOR..................................................................................................24

8.5.1 Oscillator.........................................................................................................................................................24

8.6

SEG/COM DRIVING BLOCK................................................................................................................25

8.7

SEG / COM DRIVER............................................................................................................................26

8.8 GRAY SCALE DECODER ......................................................................................................................29

POWER ON AND OFF SEQUENCE ........................................................................................................30

8.9

8.10

VDD REGULATOR .............................................................................................................................31

VDD Regulator in Sleep Mode.....................................................................................................................31

8.10.1

COMMAND.............................................................................................................................32

9.1 BASIC COMMAND LIST........................................................................................................................32

10 COMMAND.............................................................................................................................38

Set Column Address (15h)..........................................................................................................................38

10.1.1

Set Row Address (75h) ...............................................................................................................................38

10.1.2

10.1.3 Write RAM Command (5Ch) .....................................................................................................................39

Read RAM Command (5Dh) ......................................................................................................................39

10.1.4

10.1.5

Set Re-map & Dual COM Line Mode (A0h)..............................................................................................39

10.1.6

Set Display Start Line (A1h).......................................................................................................................41

10.1.7

Set Display Offset (A2h) ............................................................................................................................42

Set Display Mode (A4h ~ A7h) ..................................................................................................................43

10.1.8

Set Function selection (ABh)......................................................................................................................44

10.1.9

10.1.10

Set Sleep mode ON/OFF (AEh / AFh) .......................................................................................................44

10.1.11

Set Phase Length (B1h) ..............................................................................................................................44

10.1.12 Display Enhancement (B2h) .......................................................................................................................44

Set Front Clock Divider / Oscillator Frequency (B3h) ...............................................................................44

10.1.13

10.1.14

Set GPIO (B5h)...........................................................................................................................................44

10.1.15

Set Second Pre-charge period (B6h)...........................................................................................................45

10.1.16 Look Up Table for Gray Scale Pulse width (B8h) ......................................................................................45

10.1.17 Use Built-in Linear LUT (B9h) ..................................................................................................................45

10.1.18

Set Pre-charge voltage (BBh) .....................................................................................................................45

9

SSD1351

Rev 1.5

P 3/57

Jan 2011

Solomon Systech

�

10.1.19

Set VCOMH Voltage (BEh) ...........................................................................................................................45

Set Contrast Current for Color A,B,C (C1h)...............................................................................................46

10.1.20

10.1.21 Master Contrast Current Control (C7h) ......................................................................................................46

10.1.22

Set Multiplex Ratio (CAh)..........................................................................................................................46

10.1.23

Set Command Lock (FDh)..........................................................................................................................46

11 MAXIMUM RATINGS ..........................................................................................................47

12 DC CHARACTERISTICS .....................................................................................................48

13 AC CHARACTERISTICS .....................................................................................................49

14 APPLICATION EXAMPLE..................................................................................................54

15

PACKAGE INFORMATION ................................................................................................55

SSD1351UR1 DETAIL DIMENSION ..................................................................................................55

SSD1351Z DIE TRAY INFORMATION ..............................................................................................56

15.1

15.2

Solomon Systech

Jan 2011

P 4/57

Rev 1.5

SSD1351

�

TABLES

Table 3-1 : Ordering Information .........................................................................................................................................7

Table 5-1: SSD1351Z Bump Die Pad Coordinates ............................................................................................................10

Table 6-1: SSD1351UR1 Pin Assignment Table................................................................................................................13

Table 7-1 : SSD1351 Pin Description.................................................................................................................................15

Table 7-2 : Bus Interface selection .....................................................................................................................................16

Table 8-1 : MCU interface assignment under different bus interface mode.......................................................................18

Table 8-2 : Data bus selection modes .................................................................................................................................18

Table 8-3 : Control pins of 6800 interface..........................................................................................................................18

Table 8-4 : Control pins of 8080 interface..........................................................................................................................20

Table 8-5 : Control pins of 4-wire Serial interface .............................................................................................................20

Table 8-6 : Control pins of 3-wire Serial interface .............................................................................................................21

Table 8-7 : 262k Color Depth Graphic Display Data RAM Structure................................................................................22

Table 8-8 : Write Data bus usage under different bus width and color depth mode...........................................................23

Table 8-9 : Read Data bus usage under different bus width and color depth mode............................................................23

Table 9-1 : Command table ................................................................................................................................................32

Table 9-2: SSD1351 Graphic Acceleration Command List................................................................................................37

Table 10-11: Bus interface selection...................................................................................................................................44

Table 11-1 : Maximum Ratings ..........................................................................................................................................47

Table 12-1 : DC Characteristics..........................................................................................................................................48

Table 13-1 : AC Characteristics..........................................................................................................................................49

Table 13-2 : 6800-Series MCU Parallel Interface Timing Characteristics .........................................................................50

Table 13-3 : 8080-Series MCU Parallel Interface Timing Characteristics .........................................................................51

Table 13-4 : Serial Interface Timing Characteristics (4-wire SPI) .....................................................................................52

Table 13-5 : Serial Interface Timing Characteristics (3-wire SPI) .....................................................................................53

SSD1351

Rev 1.5

P 5/57

Jan 2011

Solomon Systech

�

FIGURES

Figure 4-1 Block Diagram ....................................................................................................................................................8

Figure 5-1: SSD1351Z Die Drawing ....................................................................................................................................9

Figure 6-1: SSD1351UR1 Pin Assignment ........................................................................................................................12

Figure 8-1 : Data read back procedure - insertion of dummy read .....................................................................................19

Figure 8-2 : Example of Write procedure in 8080 parallel interface mode ........................................................................19

Figure 8-3 : Example of Read procedure in 8080 parallel interface mode .........................................................................19

Figure 8-4 : Display data read back procedure - insertion of dummy read.........................................................................20

Figure 8-5 : Write procedure in 4-wire Serial interface mode ............................................................................................21

Figure 8-6 : Write procedure in 3-wire Serial interface mode ............................................................................................21

Figure 8-7 : Oscillator Circuit.............................................................................................................................................24

Figure 8-8 : IREF Current Setting by Resistor Value............................................................................................................25

Figure 8-9 : Segment and Common Driver Block Diagram ...............................................................................................26

Figure 8-10 : Segment and Common Driver Signal Waveform..........................................................................................27

Figure 8-11: Gray Scale Control in Segment......................................................................................................................28

Figure 8-12 : Relation between GDDRAM content and Gray Scale table entry for three colors in 262K color mode

(under command B9h Use Built-in Linear LUT)........................................................................................................29

Figure 8-13 : The Power ON sequence...............................................................................................................................30

Figure 8-14 : The Power OFF sequence .............................................................................................................................30

Figure 8-15 VDD pin connection scheme.............................................................................................................................31

Figure 8-16 : Case 1 - Command sequence for just entering/ exiting sleep mode..............................................................31

Figure 8-17 : Case 2 - Command sequence for disabling internal VDD regulator during sleep mode.................................31

Figure 10-1 : Example of Column and Row Address Pointer Movement ..........................................................................38

Figure 10-2 : Address Pointer Movement of Horizontal Address Increment Mode ...........................................................39

Figure 10-3: Address Pointer Movement of Vertical Address Increment Mode ................................................................39

Figure 10-4 : COM Pins Hardware Configuration (MUX ratio: 128) ................................................................................40

Figure 10-5 : Example of Set Display Start Line with no Remap.......................................................................................41

Figure 10-6 : Example of Set Display Offset with no Remap ...........................................................................................42

Figure 10-7 : Example of Entire Display OFF....................................................................................................................43

Figure 10-8 : Example of Entire Display ON .....................................................................................................................43

Figure 10-9 : Example of Normal Display..........................................................................................................................43

Figure 10-10 : Example of Inverse Display........................................................................................................................43

Figure 13-1 : 6800-series MCU parallel interface characteristics.......................................................................................50

Figure 13-2 : 8080-series MCU parallel interface characteristics.......................................................................................51

Figure 13-3 : Serial interface characteristics (4-wire SPI)..................................................................................................52

Figure 13-4 : Serial interface characteristics (3-wire SPI)..................................................................................................53

Figure 14-1 : SSD1351Z application example for 18-bit 6800-parallel interface mode.....................................................54

Figure 15-1: SSD1351UR1 Detail Dimension....................................................................................................................55

Figure 15-2: SSD1351UR1 Die Tray Information..............................................................................................................56

Solomon Systech

Jan 2011

P 6/57

Rev 1.5

SSD1351

�

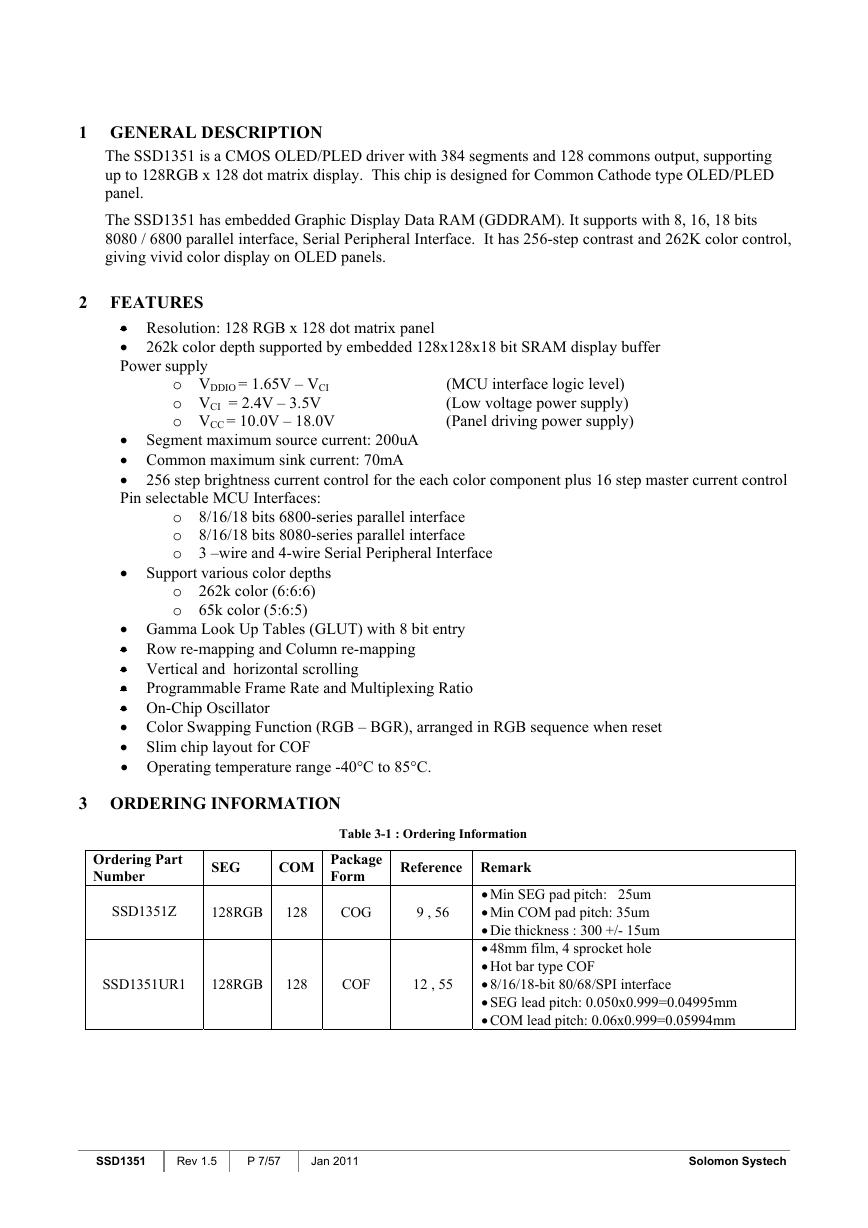

1 GENERAL DESCRIPTION

The SSD1351 is a CMOS OLED/PLED driver with 384 segments and 128 commons output, supporting

up to 128RGB x 128 dot matrix display. This chip is designed for Common Cathode type OLED/PLED

panel.

The SSD1351 has embedded Graphic Display Data RAM (GDDRAM). It supports with 8, 16, 18 bits

8080 / 6800 parallel interface, Serial Peripheral Interface. It has 256-step contrast and 262K color control,

giving vivid color display on OLED panels.

2 FEATURES

• Resolution: 128 RGB x 128 dot matrix panel

• 262k color depth supported by embedded 128x128x18 bit SRAM display buffer

Power supply

o VDDIO = 1.65V – VCI

o VCI = 2.4V – 3.5V

o VCC = 10.0V – 18.0V

(MCU interface logic level)

(Low voltage power supply)

(Panel driving power supply)

• Segment maximum source current: 200uA

• Common maximum sink current: 70mA

• 256 step brightness current control for the each color component plus 16 step master current control

Pin selectable MCU Interfaces:

o 8/16/18 bits 6800-series parallel interface

o 8/16/18 bits 8080-series parallel interface

o 3 –wire and 4-wire Serial Peripheral Interface

o 262k color (6:6:6)

o 65k color (5:6:5)

• Support various color depths

• Gamma Look Up Tables (GLUT) with 8 bit entry

• Row re-mapping and Column re-mapping

• Vertical and horizontal scrolling

• Programmable Frame Rate and Multiplexing Ratio

• On-Chip Oscillator

• Color Swapping Function (RGB – BGR), arranged in RGB sequence when reset

• Slim chip layout for COF

• Operating temperature range -40°C to 85°C.

3 ORDERING INFORMATION

Table 3-1 : Ordering Information

Ordering Part

Number

SEG

COM Package

Form

Reference Remark

SSD1351Z

128RGB

128

COG

9 , 56

SSD1351UR1

128RGB

128

COF

12 , 55

• Min SEG pad pitch: 25um

• Min COM pad pitch: 35um

• Die thickness : 300 +/- 15um

• 48mm film, 4 sprocket hole

• Hot bar type COF

• 8/16/18-bit 80/68/SPI interface

• SEG lead pitch: 0.050x0.999=0.04995mm

• COM lead pitch: 0.06x0.999=0.05994mm

SSD1351

Rev 1.5

P 7/57

Jan 2011

Solomon Systech

�

4 BLOCK DIAGRAM

Figure 4-1 Block Diagram

VDD Regulator

VCI

e

c

a

f

r

e

t

n

I

U

C

M

M

A

R

D

D

G

r

e

d

o

c

e

D

e

l

a

c

S

y

a

r

G

s

r

e

v

i

r

)

d

d

o

(

D

n

o

m

m

o

C

s

r

e

v

i

r

D

t

n

e

m

g

e

S

d

n

a

m

m

o

C

r

e

d

o

c

e

D

r

o

t

a

l

l

i

c

s

O

i

g

n

i

m

T

y

a

l

p

s

i

D

r

o

t

a

r

e

n

e

G

k

c

o

l

B

g

n

i

v

i

r

D

M

O

C

G

E

S

/

L

C

S

L

C

R

F

H

M

O

C

V

F

E

R

I

s

r

e

v

i

r

D

n

o

m

m

o

C

)

n

e

v

e

(

COM127

COM125

COM123

.

.

.

COM5

COM3

COM1

SC127

SB127

SA127

SC126

SB126

SA126

SC125

SB125

SA125

.

.

.

SC2

SB2

SA2

SC1

SB1

SA1

SC0

SB0

SA0

COM0

COM2

COM4

.

.

.

COM122

COM124

COM126

BGGND

VDD

RES#

CS#

D/C#

R/W#(W/R#)

E(RD#)

D[17:0]

BS[1:0]

VDDIO

VLSS

VCC

VCI

VSS

VSL

GPIO 0

GPIO 1

VPP

Solomon Systech

Jan 2011

P 8/57

Rev 1.5

SSD1351

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf