10. Cyclone IV器件的JTAG边界扫描测试

November 2011

CYIV-51010-1.2

CYIV-51010-1.2

本章介绍了 Cyclone® IV 器件所支持的边界扫描测试 (BST) 功能。这些 BST 功能与

Cyclone III 器件中的相类似,除非另有说明。

Cyclone IV 器件 (Cyclone IV E 器件和 Cyclone IV GX 器件 ) 支持 IEEE Std.1149.1。

Cyclone IV GX 器件也支持 IEEE Std.1149.6。IEEE Std.1149.6 (AC JTAG) 仅被

Cyclone IV GX 器件中的高速串行接口 (HSSI) 收发器支持。IEEE Std.1149.6 用于使

能 AC 耦合的发送器与接收器之间的板级连接检查。

本章节含盖以下几方面内容:

■ IEEE Std.1149.6 边界扫描寄存器 ( 第 10-2 页 )

■ BST 操作控制 ( 第 10-3 页 )

■ JTAG 链中 I/O 电压支持 ( 第 10-5 页 )

■ 边界扫描描述语言支持 ( 第 10-6 页 )

f 欲了解关于 JTAG 指令代码描述以及 IEEE Std.1149.1 BST 指南的详细信息,请参考

IEEE 1149.1 (JTAG) Boundary- Scan Testing for Cyclone III Devices章节。

f 欲了解以下方面的内容,请参考 AN 39: IEEE 1149.1 (JTAG) Boundary-Scan Testing

in Altera Devices:

■ IEEE Std. 1149.1 BST 体系结构与电路系统

■ TAP 控制器状态机

■ 指令模式

© 2011 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos

are trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as

trademarks or service marks are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its

semiconductor products to current specifications in accordance with Altera's standard warranty, but reserves the right to make changes to any products and

services at any time without notice. Altera assumes no responsibility or liability arising out of the application or use of any information, product, or service

described herein except as expressly agreed to in writing by Altera. Altera customers are advised to obtain the latest version of device specifications before relying

on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 1

2011 年 11 月

Subscribe

�

10–2

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

IEEE Std.1149.6 边界扫描寄存器

IEEE Std.1149.6 边界扫描寄存器

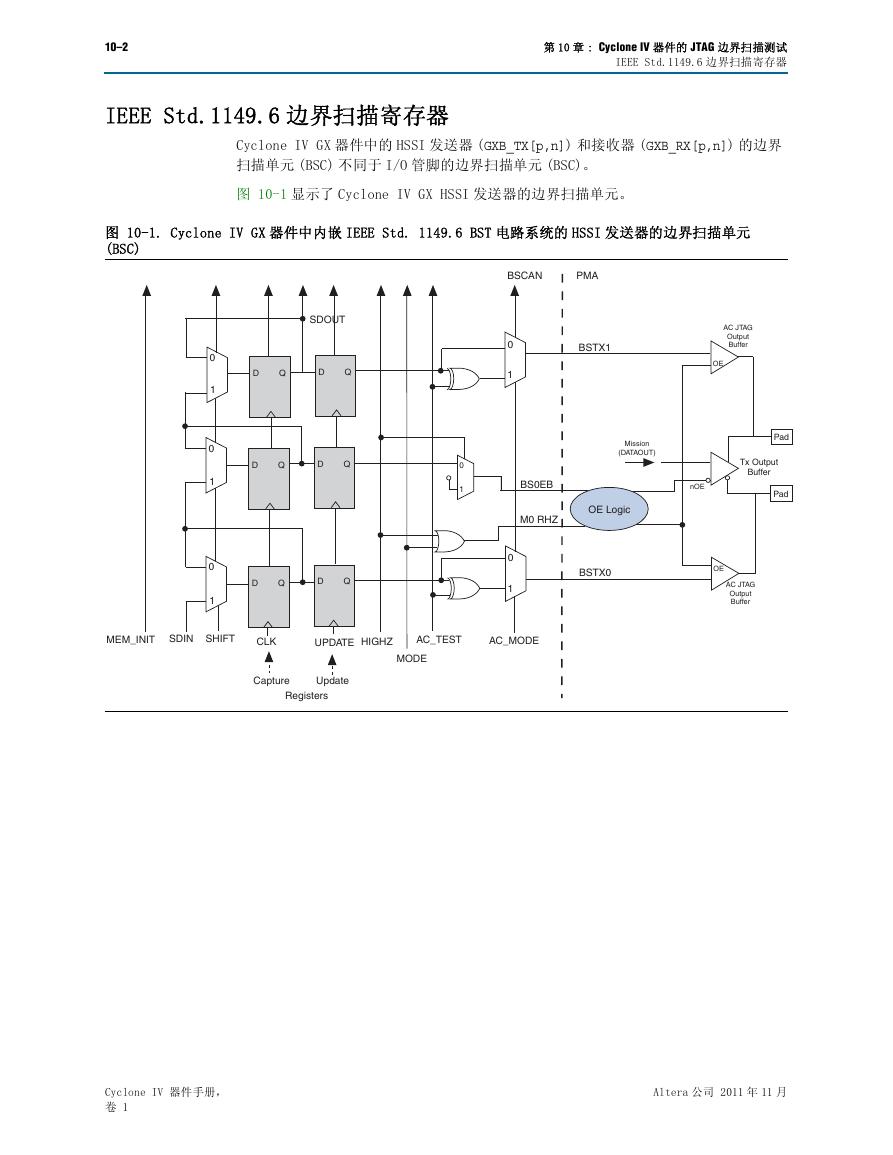

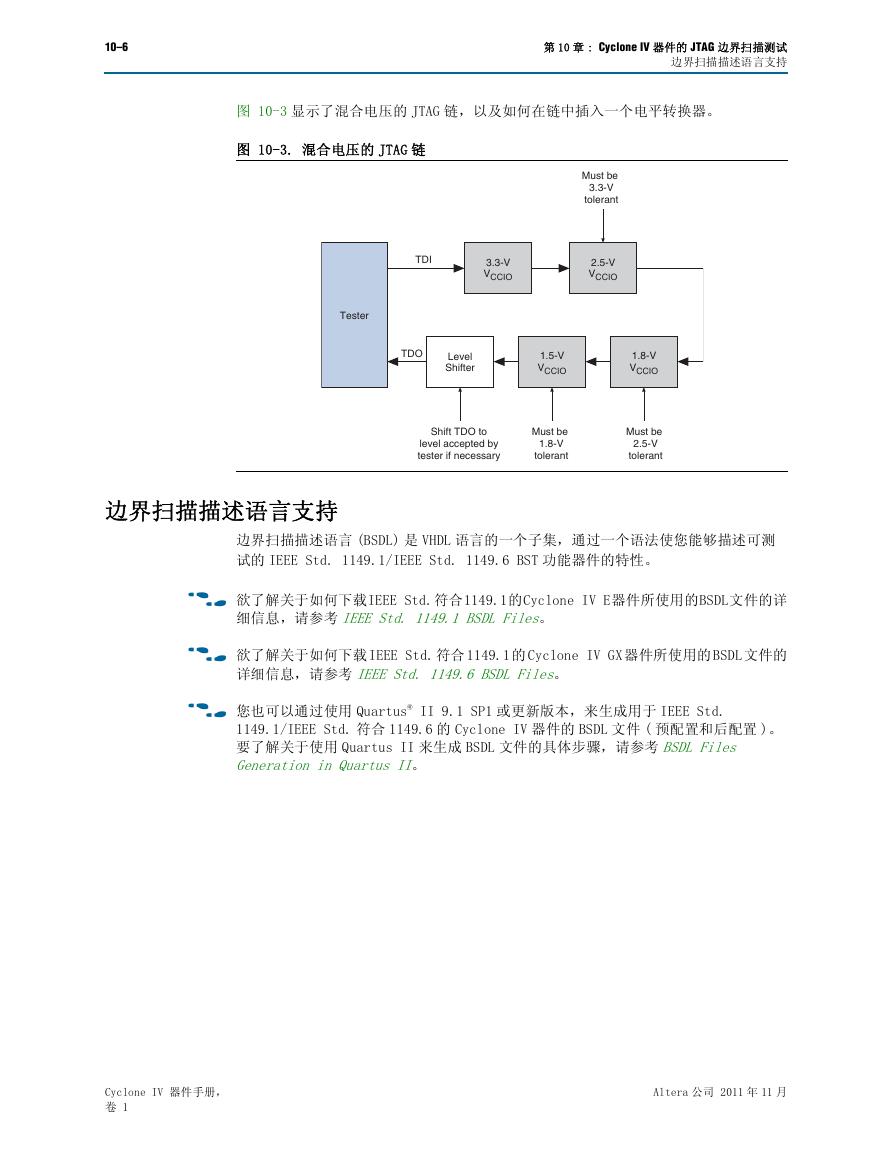

Cyclone IV GX 器件中的 HSSI 发送器 (GXB_TX[p,n]) 和接收器 (GXB_RX[p,n]) 的边界

扫描单元 (BSC) 不同于 I/O 管脚的边界扫描单元 (BSC)。

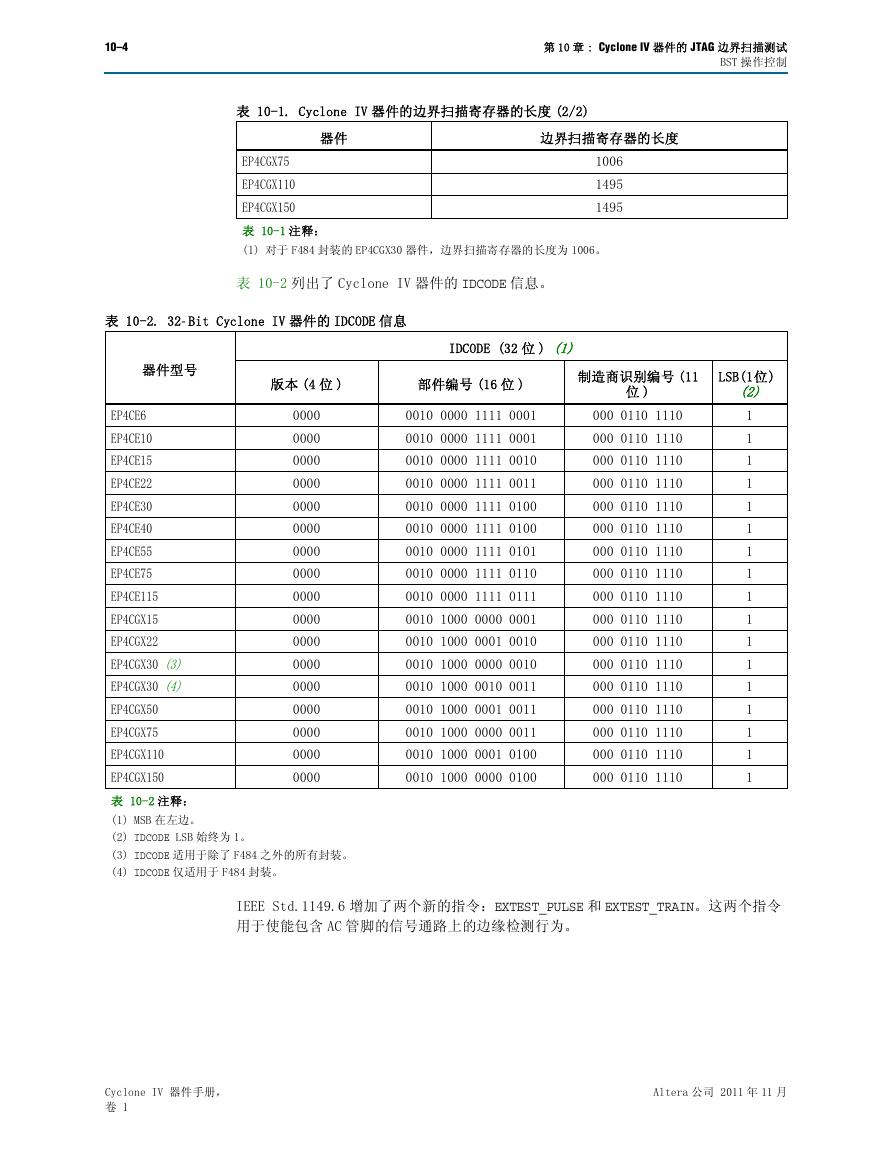

图 10-1 显示了 Cyclone IV GX HSSI 发送器的边界扫描单元。

图 10-1. Cyclone IV GX 器件中内嵌 IEEE Std. 1149.6 BST 电路系统的 HSSI 发送器的边界扫描单元

(BSC)

BSCAN

PMA

SDOUT

D

Q

D

Q

D

Q

D

Q

0

1

D

Q

D

Q

0

1

0

1

0

1

0

1

0

1

BSTX1

AC JTAG

Output

Buffer

OE

Mission

(DATAOUT)

BS0EB

M0 RHZ

OE Logic

Pad

Tx Output

Buffer

Pad

nOE

BSTX0

OE

AC JTAG

Output

Buffer

MEM_INIT

SDIN SHIFT

CLK

UPDATE

HIGHZ

AC_TEST

AC_MODE

MODE

Capture

Update

Registers

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

BST 操作控制

10–3

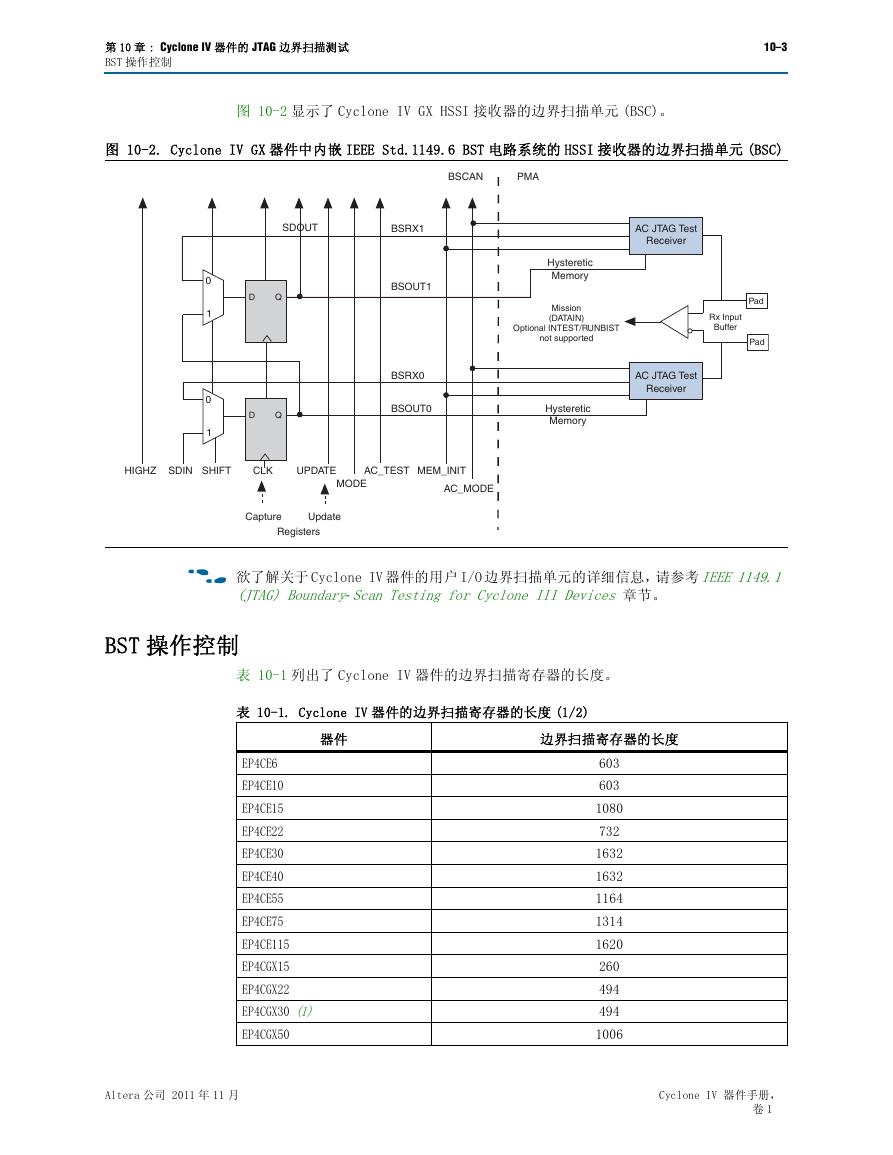

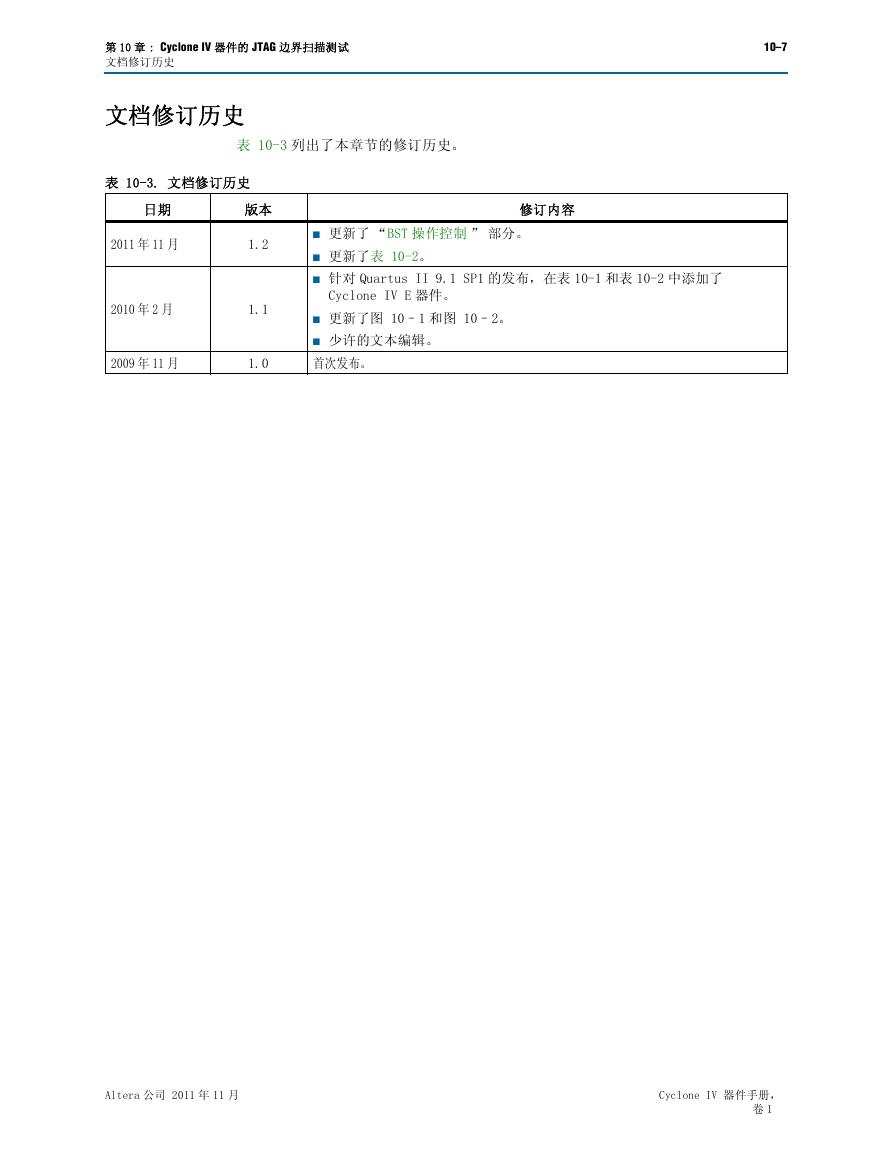

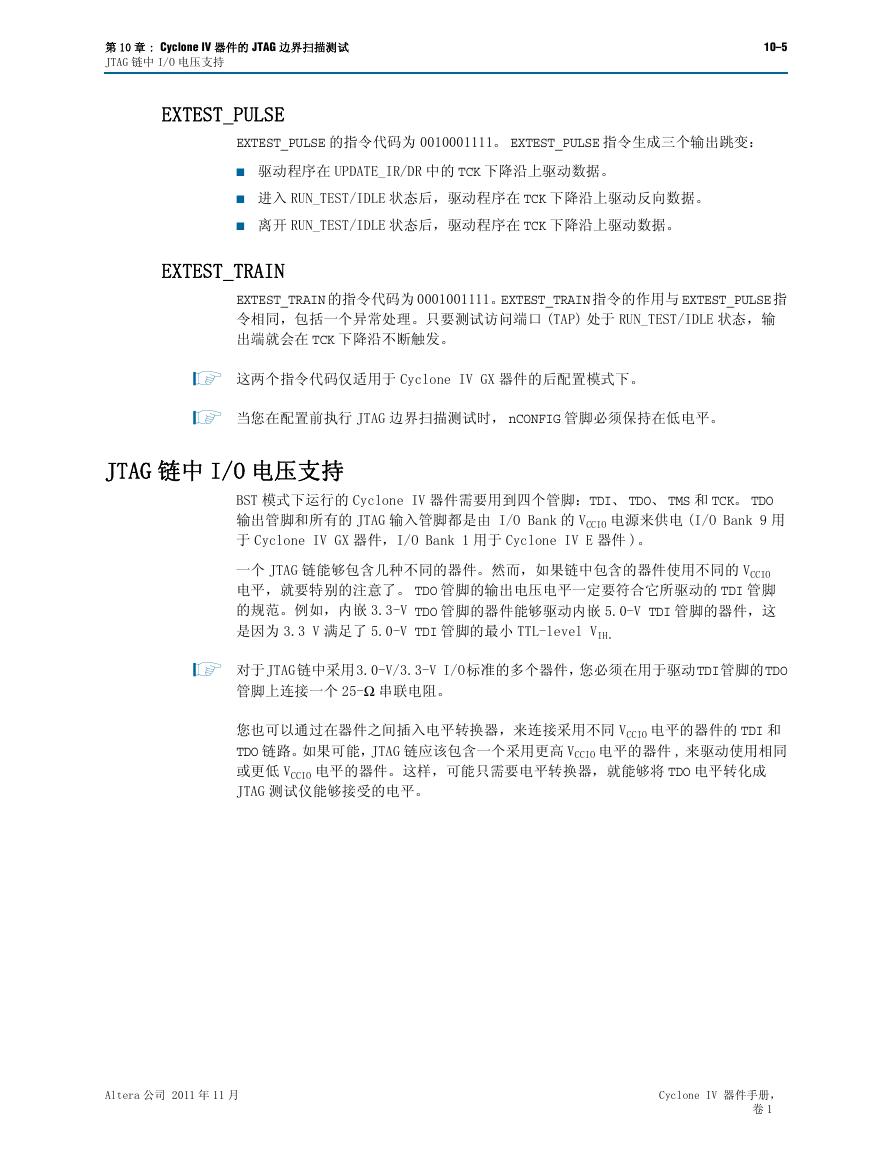

图 10-2 显示了 Cyclone IV GX HSSI 接收器的边界扫描单元 (BSC)。

图 10-2. Cyclone IV GX 器件中内嵌 IEEE Std.1149.6 BST 电路系统的 HSSI 接收器的边界扫描单元 (BSC)

BSCAN

PMA

SDOUT

BSRX1

AC JTAG Test

Receiver

BSOUT1

BSRX0

BSOUT0

Hysteretic

Memory

Mission

(DATAIN)

Optional INTEST/RUNBIST

not supported

Rx Input

Buffer

Pad

Pad

AC JTAG Test

Receiver

Hysteretic

Memory

0

1

0

1

D

Q

D

Q

HIGHZ SDIN SHIFT

CLK

UPDATE

AC_TEST

MEM_INIT

MODE

AC_MODE

Capture

Update

Registers

f 欲了解关于 Cyclone IV 器件的用户 I/O 边界扫描单元的详细信息,请参考IEEE 1149.1

(JTAG) Boundary- Scan Testing for Cyclone III Devices 章节。

BST 操作控制

表 10-1 列出了 Cyclone IV 器件的边界扫描寄存器的长度。

表 10-1. Cyclone IV 器件的边界扫描寄存器的长度 (1/2)

器件

边界扫描寄存器的长度

EP4CE6

EP4CE10

EP4CE15

EP4CE22

EP4CE30

EP4CE40

EP4CE55

EP4CE75

EP4CE115

EP4CGX15

EP4CGX22

EP4CGX30 (1)

EP4CGX50

603

603

1080

732

1632

1632

1164

1314

1620

260

494

494

1006

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

10–4

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

BST 操作控制

表 10-1. Cyclone IV 器件的边界扫描寄存器的长度 (2/2)

器件

边界扫描寄存器的长度

EP4CGX75

EP4CGX110

EP4CGX150

表 10-1 注释:

1006

1495

1495

(1) 对于 F484 封装的 EP4CGX30 器件,边界扫描寄存器的长度为 1006。

表 10-2 列出了 Cyclone IV 器件的 IDCODE 信息。

表 10-2. 32- Bit Cyclone IV 器件的 IDCODE 信息

器件型号

版本 (4 位 )

部件编号 (16 位 )

制造商识别编号 (11

LSB(1位)

位 )

(2)

IDCODE (32 位 ) (1)

EP4CE6

EP4CE10

EP4CE15

EP4CE22

EP4CE30

EP4CE40

EP4CE55

EP4CE75

EP4CE115

EP4CGX15

EP4CGX22

EP4CGX30 (3)

EP4CGX30 (4)

EP4CGX50

EP4CGX75

EP4CGX110

EP4CGX150

表 10-2 注释:

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0000

0010 0000 1111 0001

000 0110 1110

0010 0000 1111 0001

000 0110 1110

0010 0000 1111 0010

000 0110 1110

0010 0000 1111 0011

000 0110 1110

0010 0000 1111 0100

000 0110 1110

0010 0000 1111 0100

000 0110 1110

0010 0000 1111 0101

000 0110 1110

0010 0000 1111 0110

000 0110 1110

0010 0000 1111 0111

000 0110 1110

0010 1000 0000 0001

000 0110 1110

0010 1000 0001 0010

000 0110 1110

0010 1000 0000 0010

000 0110 1110

0010 1000 0010 0011

000 0110 1110

0010 1000 0001 0011

000 0110 1110

0010 1000 0000 0011

000 0110 1110

0010 1000 0001 0100

000 0110 1110

0010 1000 0000 0100

000 0110 1110

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

1

(1) MSB 在左边。

(2) IDCODE LSB 始终为 1。

(3) IDCODE 适用于除了 F484 之外的所有封装。

(4) IDCODE 仅适用于 F484 封装。

IEEE Std.1149.6 增加了两个新的指令:EXTEST_PULSE 和 EXTEST_TRAIN。这两个指令

用于使能包含 AC 管脚的信号通路上的边缘检测行为。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

JTAG 链中 I/O 电压支持

EXTEST_PULSE

10–5

EXTEST_PULSE 的指令代码为 0010001111。 EXTEST_PULSE 指令生成三个输出跳变:

■ 驱动程序在 UPDATE_IR/DR 中的 TCK 下降沿上驱动数据。

■ 进入 RUN_TEST/IDLE 状态后,驱动程序在 TCK 下降沿上驱动反向数据。

■ 离开 RUN_TEST/IDLE 状态后,驱动程序在 TCK 下降沿上驱动数据。

EXTEST_TRAIN

EXTEST_TRAIN 的指令代码为 0001001111。EXTEST_TRAIN 指令的作用与 EXTEST_PULSE指

令相同,包括一个异常处理。只要测试访问端口 (TAP) 处于 RUN_TEST/IDLE 状态,输

出端就会在 TCK 下降沿不断触发。

1 这两个指令代码仅适用于 Cyclone IV GX 器件的后配置模式下。

1 当您在配置前执行 JTAG 边界扫描测试时, nCONFIG 管脚必须保持在低电平。

JTAG 链中 I/O 电压支持

BST 模式下运行的 Cyclone IV 器件需要用到四个管脚:TDI、 TDO、 TMS 和 TCK。 TDO

输出管脚和所有的 JTAG 输入管脚都是由 I/O Bank 的 VCCIO 电源来供电 (I/O Bank 9 用

于 Cyclone IV GX 器件,I/O Bank 1 用于 Cyclone IV E 器件 )。

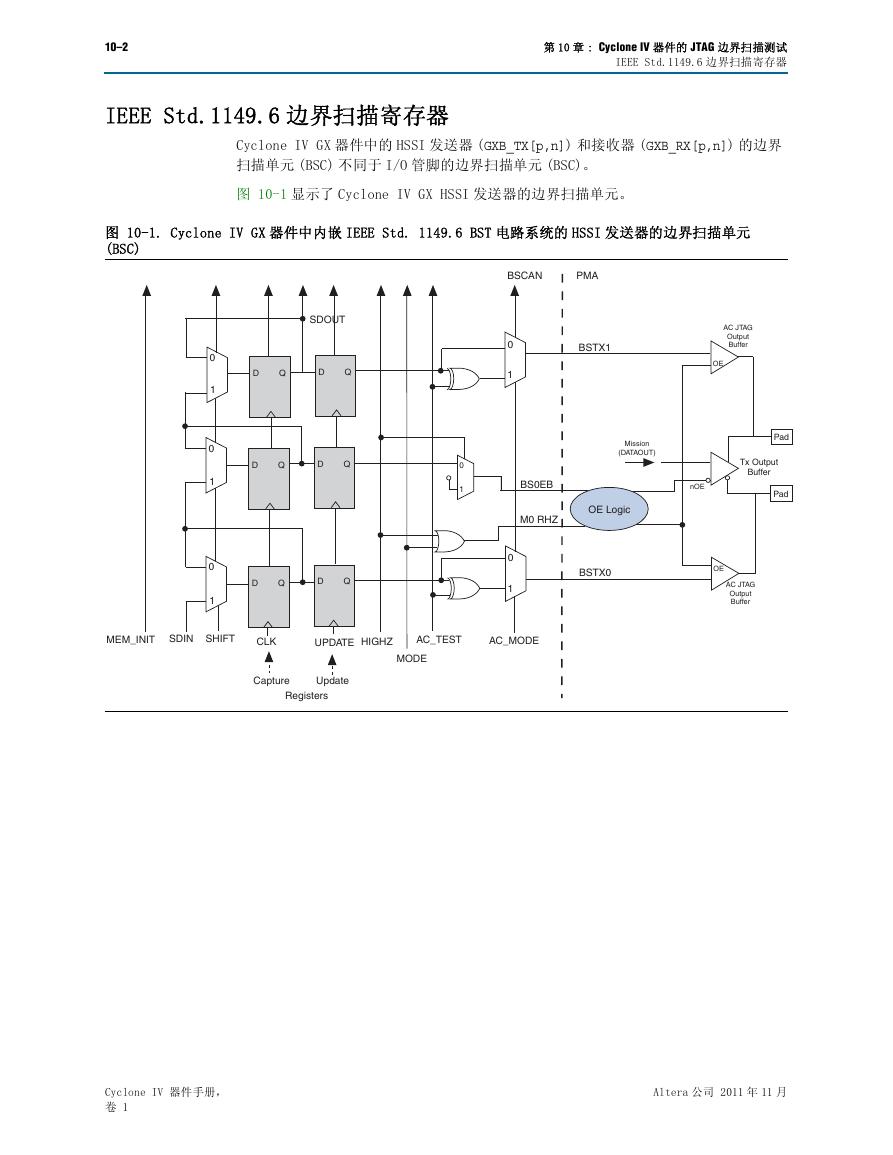

一个 JTAG 链能够包含几种不同的器件。然而,如果链中包含的器件使用不同的 VCCIO

电平,就要特别的注意了。 TDO 管脚的输出电压电平一定要符合它所驱动的 TDI 管脚

的规范。例如,内嵌 3.3-V TDO 管脚的器件能够驱动内嵌 5.0-V TDI 管脚的器件,这

是因为 3.3 V 满足了 5.0-V TDI 管脚的最小 TTL-level VIH。

1 对于 JTAG链中采用3.0-V/3.3-V I/O标准的多个器件,您必须在用于驱动TDI管脚的TDO

管脚上连接一个 25-Ω 串联电阻。

您也可以通过在器件之间插入电平转换器,来连接采用不同 VCCIO 电平的器件的 TDI 和

TDO 链路。如果可能,JTAG 链应该包含一个采用更高 VCCIO 电平的器件 , 来驱动使用相同

或更低 VCCIO 电平的器件。这样,可能只需要电平转换器,就能够将 TDO 电平转化成

JTAG 测试仪能够接受的电平。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

10–6

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

边界扫描描述语言支持

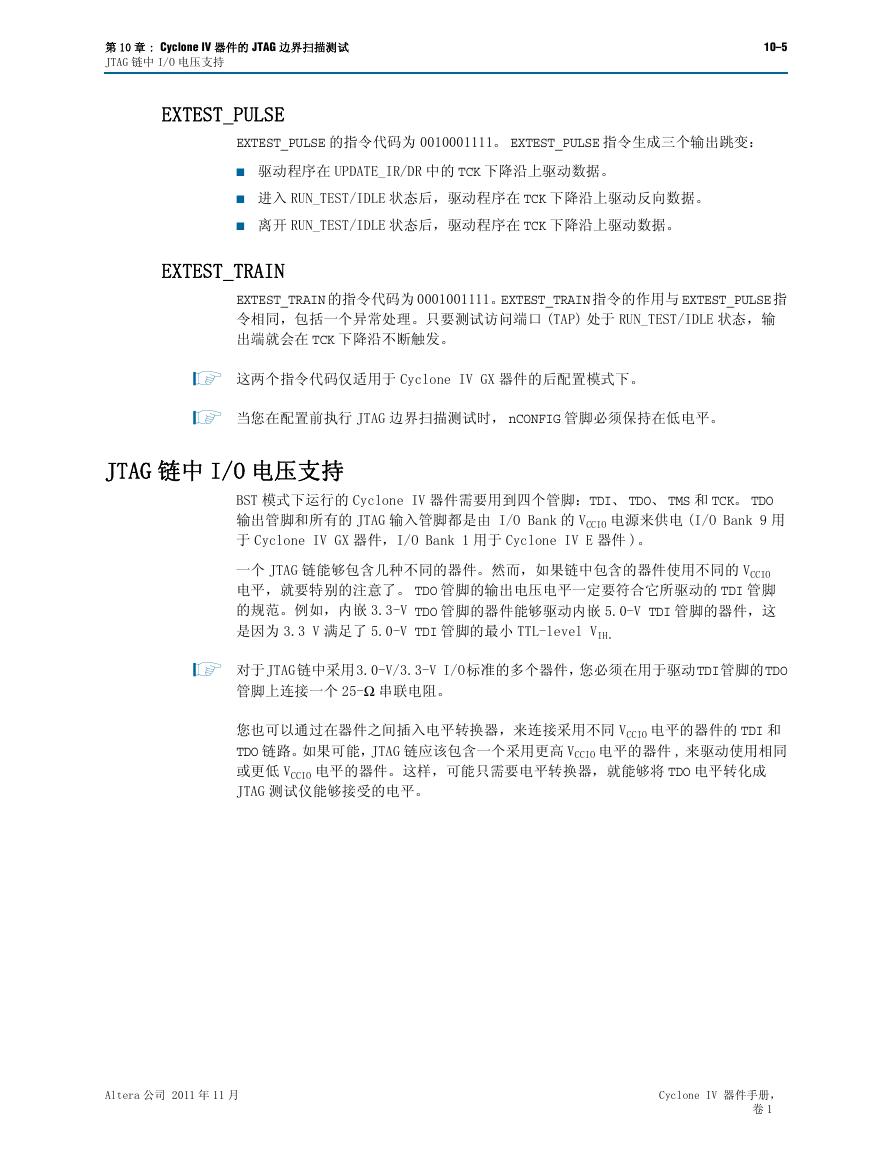

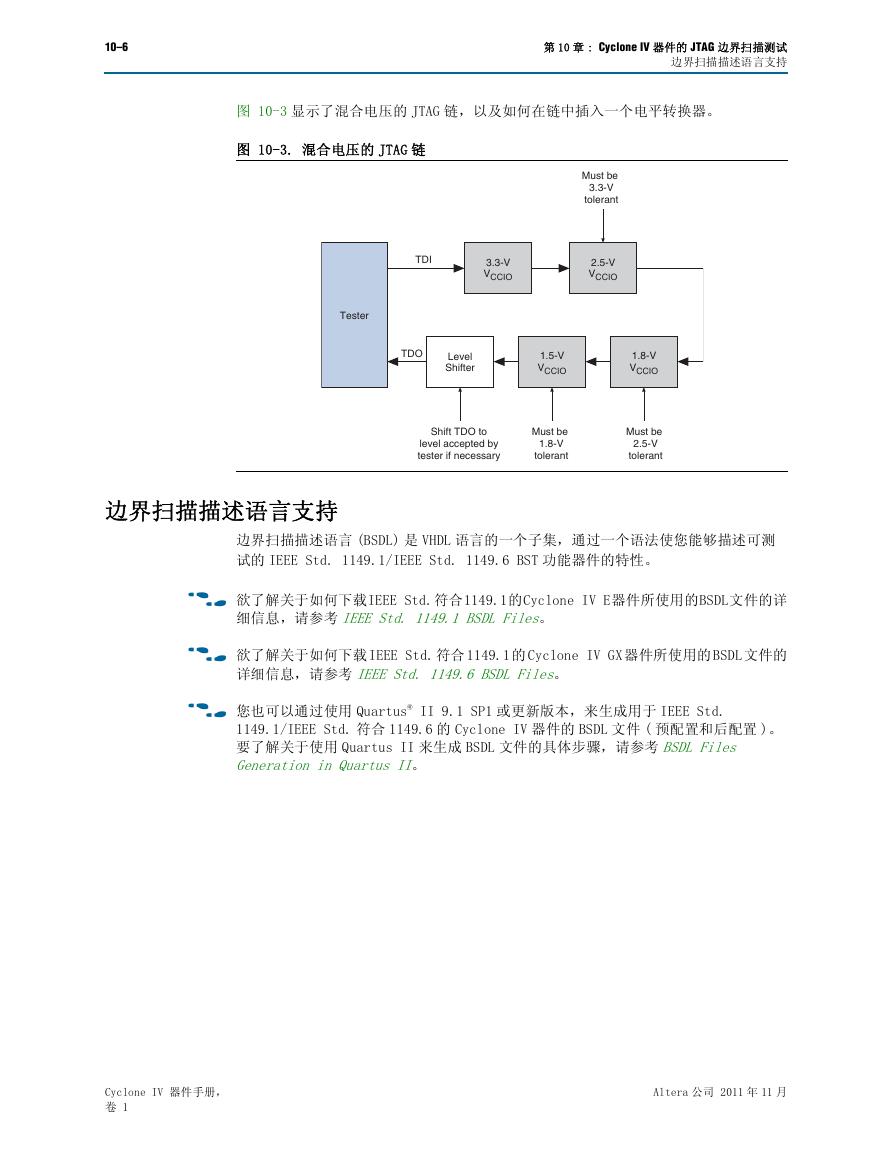

图 10-3 显示了混合电压的 JTAG 链,以及如何在链中插入一个电平转换器。

图 10-3. 混合电压的 JTAG 链

Must be

3.3-V

tolerant

TDI

3.3-V

VCCIO

2.5-V

VCCIO

Tester

TDO

Level

Shifter

1.5-V

VCCIO

1.8-V

VCCIO

Shift TDO to

level accepted by

tester if necessary

Must be

1.8-V

tolerant

Must be

2.5-V

tolerant

边界扫描描述语言支持

边界扫描描述语言 (BSDL) 是 VHDL 语言的一个子集,通过一个语法使您能够描述可测

试的 IEEE Std. 1149.1/IEEE Std. 1149.6 BST 功能器件的特性。

f 欲了解关于如何下载IEEE Std.符合1149.1的Cyclone IV E器件所使用的BSDL文件的详

细信息,请参考 IEEE Std. 1149.1 BSDL Files。

f 欲了解关于如何下载 IEEE Std. 符合 1149.1 的 Cyclone IV GX 器件所使用的 BSDL 文件的

详细信息,请参考 IEEE Std. 1149.6 BSDL Files。

f 您也可以通过使用 Quartus® II 9.1 SP1 或更新版本,来生成用于 IEEE Std.

1149.1/IEEE Std. 符合 1149.6 的 Cyclone IV 器件的 BSDL 文件 ( 预配置和后配置 )。

要了解关于使用 Quartus II 来生成 BSDL 文件的具体步骤,请参考 BSDL Files

Generation in Quartus II。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

文档修订历史

10–7

文档修订历史

表 10-3 列出了本章节的修订历史。

表 10-3. 文档修订历史

日期

2011 年 11 月

版本

1.2

2010 年 2 月

1.1

修订内容

■ 更新了 “BST 操作控制 ” 部分。

■ 更新了表 10-2。

■ 针对 Quartus II 9.1 SP1 的发布,在表 10-1 和表 10-2 中添加了

Cyclone IV E 器件。

■ 更新了图 10–1 和图 10–2。

■ 少许的文本编辑。

2009 年 11 月

1.0

首次发布。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

10–8

第 10 章 : Cyclone IV 器件的 JTAG 边界扫描测试

文档修订历史

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf