November 2009

CYIV-51002-1.0

CYIV-51002-1.0

逻辑单元

2. Cyclone IV 器件的逻辑单元和逻辑阵

列模块

这个章节包含了定义逻辑单元 (LE) 和逻辑阵列模块 (LAB) 的特性。具体信息体现在 LE

如何运作,LAB 如何容纳 LE 组,以及 LAB 接口如何与 Cyclone® IV 器件中的其他模块

连接。

逻辑单元 (LE) 在 Cyclone IV 器件结构中是最小的逻辑单位。LE 紧密且有效的提供了

高级功能的逻辑使用。每个 LE 有以下特性:

■ 一个四口输入的查找表 (LUT),以实现四种变量的任何功能

■ 一个可编程的寄存器

■ 一个进位链连接

■ 一个寄存器链连接

■ 可驱动以下的相互连接:

■ 本地

■ 行

■ 列

■ 寄存器链

■ 直联

■ 寄存器套包支持

■ 寄存器反馈支持

© 2009 Altera Corporation. All rights reserved. ALTERA, ARRIA, CYCLONE, HARDCOPY, MAX, MEGACORE, NIOS, QUARTUS and STRATIX words and logos are

trademarks of Altera Corporation and registered in the U.S. Patent and Trademark Office and in other countries. All other words and logos identified as trademarks or service marks

are the property of their respective holders as described at www.altera.com/common/legal.html. Altera warrants performance of its semiconductor products to current specifications

in accordance with Altera's standard warranty, but reserves the right to make changes to any products and services at any time without notice. Altera assumes no responsibility or

liability arising out of the application or use of any information, product, or service described herein except as expressly agreed to in writing by Altera. Altera customers are advised

to obtain the latest version of device specifications before relying on any published information and before placing orders for products or services.

ISO

9001:2008

Registered

Cyclone IV 器件手册,

卷 1

2011 年 11 月

Subscribe

�

2–2

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

逻辑单元

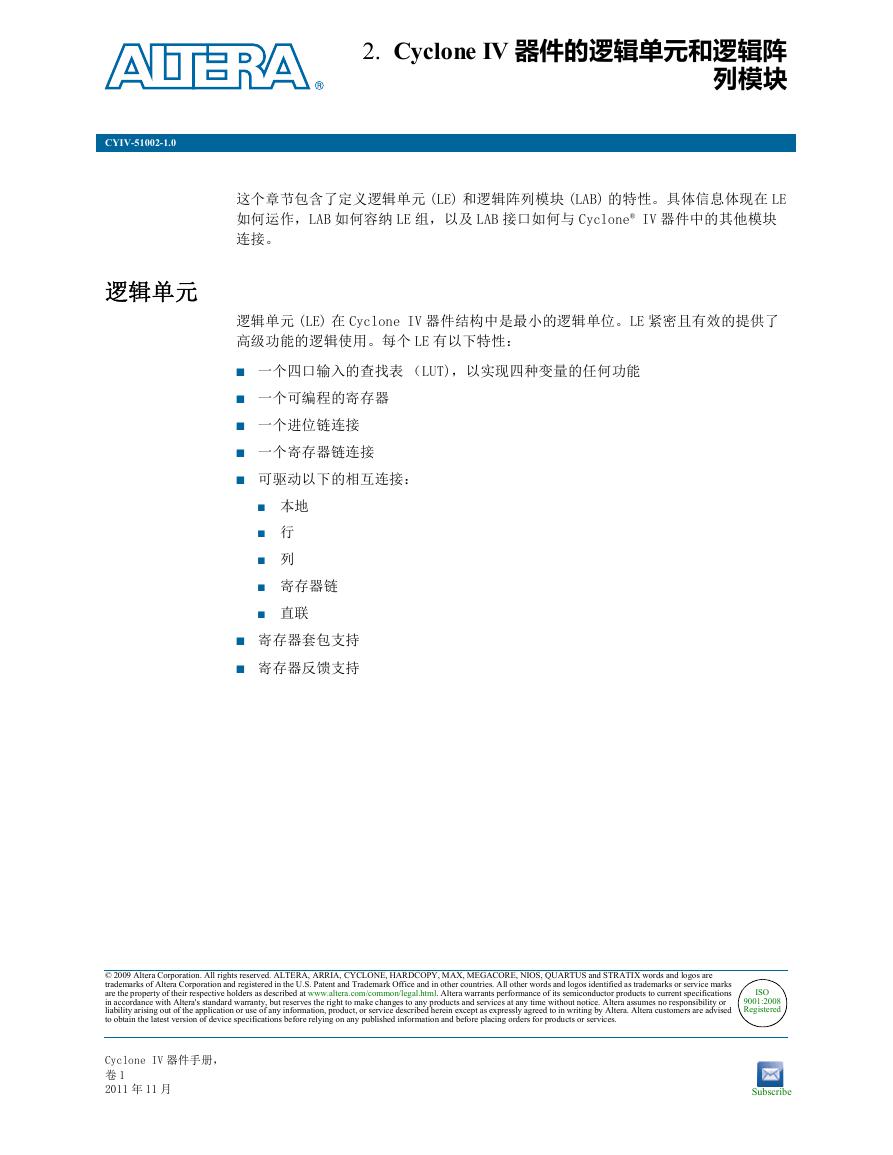

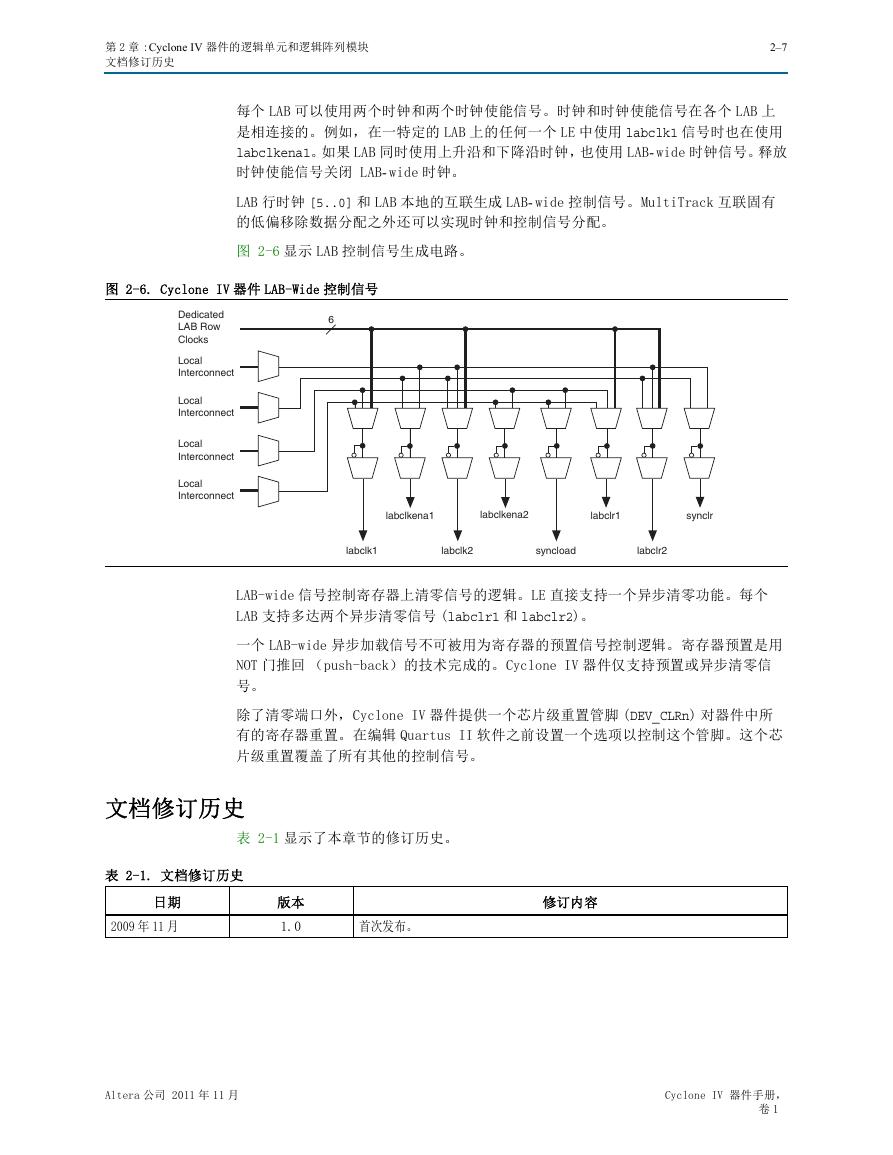

图 2-1 显示在 Cyclone IV 器件中的 LE

图 2-1. 在 Cyclone IV 器件中的 LE

Register Chain

Routing from

previous LE

LAB-Wide

Register Bypass

Synchronous

LAB-Wide

Load

Synchronous

Clear

Programmable

Register

LE Carry-In

data 1

data 2

data 3

data 4

Look-Up Table

(LUT)

Carry

Chain

Synchronous

Load and

Clear Logic

D

Q

ENA

CLRN

Register Feedback

labclr1

labclr2

Chip-Wide

Reset

(DEV_CLRn)

Asynchronous

Clear Logic

Clock &

Clock Enable

Select

LE Carry-Out

labclk1

labclk2

labclkena1

labclkena2

LE 特性

Row, Column,

And Direct Link

Routing

Row, Column,

And Direct Link

Routing

Local

Routing

Register Chain

Output

您可以对每个 LE 配置可编程的寄存器为 D、 T、 JK, 或 SR 触发器操作。每个寄存器上

有数据,时钟,时钟使能和清零输入。全局时钟网络,通用 I/O 管脚,任何内部逻辑

都可以驱动时钟和清零寄存器控制信号。通用 I/O 管脚或内部逻辑都可以驱动时钟使

能。对于组合功能,LUT 输出端旁路寄存器直接驱动到 LE 输出端。

每个 LE 有三个输出端分别驱动本地,行和列的布线资源。LUT 或寄存器输出独立地驱

动这三个输出端。两个 LE 输出端驱动列或行以及直接链接布线连接,而另一个 LE 则

驱动本地互联资源。这允许 LUT 驱动一个输出端,当寄存器驱动另一个输出端时。这

个特性称为寄存器套包,由于器件可以使用寄存器和 LUT 在不相关的功能,增加了器

件的利用率。LAB- wide 同步加载控制信号在使用寄存器套包时是不可用的。要了解更

多关于同步加载控制信号的信息,请参阅 “LAB 控制信号 ” (第 2-6 页)

寄存器反馈模式允许寄存器输出反馈到相同 LE 的 LUT 中以确保寄存器与自己的扇出一

起配套,提供另一种机制以改进布局布线。LE 也可以驱动 LUT 输出存储与未存储的版

本。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

LE 操作模式

2–3

除了三个通用布线输出之外,在一个 LAB 上的 LE 有寄存器链输出,使得同一个 LAB 中

的寄存器能够串联在一起。寄存器链输出使 LUT 能够被用于组合功能,实现寄存器被

用于一个不相关的移位寄存器。这些资源加速了 LAB 之间的连接,同时节省本地互联

资源。

LE 操作模式

Cyclone IV LE 在以下模式下操作:

■ 正常模式

■ 算术模式

The Quartus® II 软件自动为普通功能选择适用的模式,例如计数器,加法器,减法器

和算术功能,与参数化功能如参数化模块库 (LPM) 功能一起。如果需要,您也可以创

建指定的特用功能以用于 LE 操作模式的性能优化。

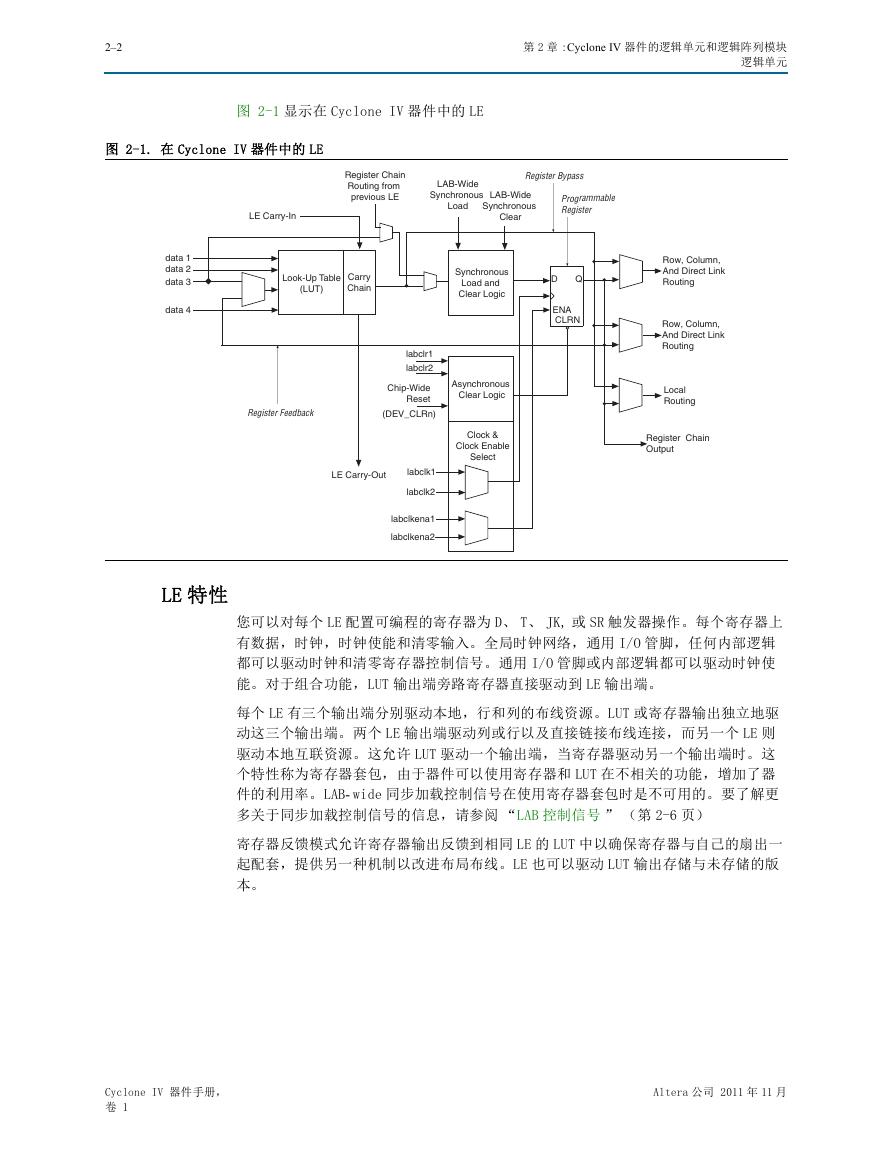

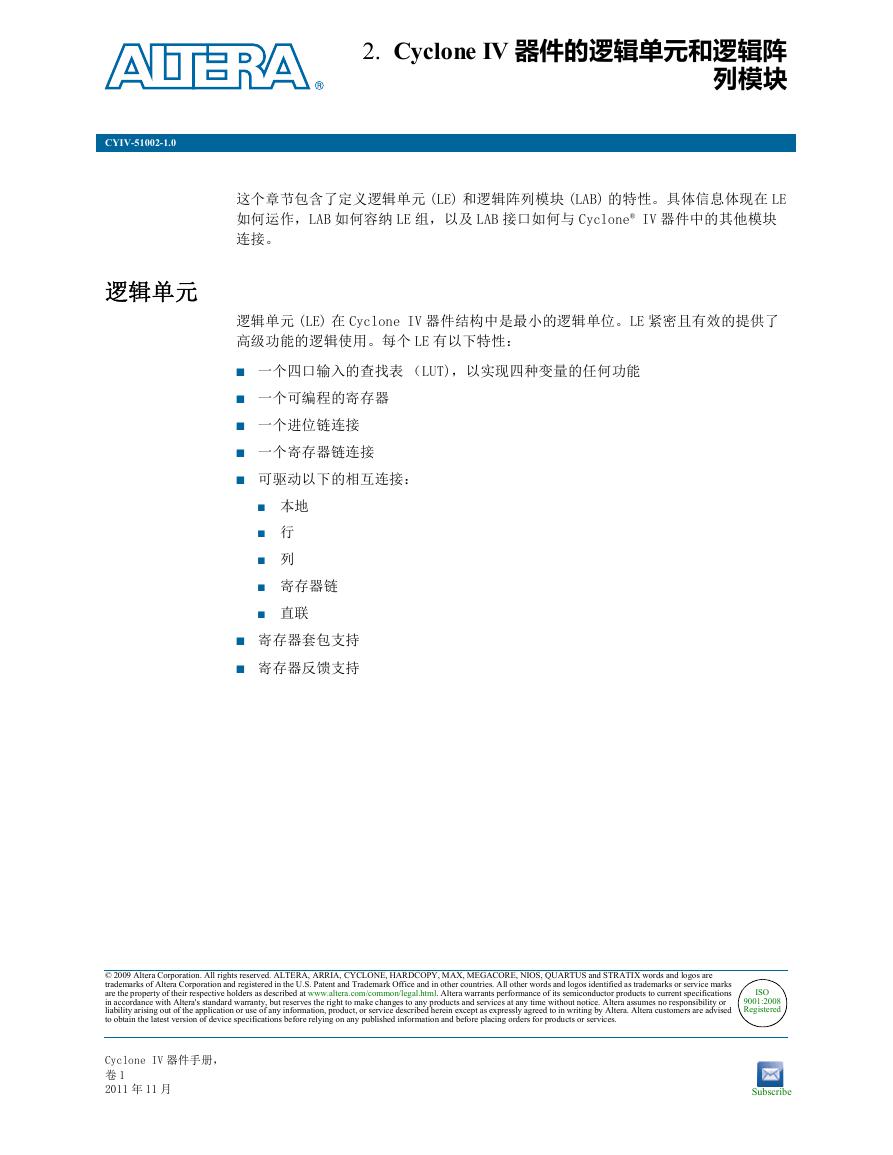

正常模式

正常模式适用于一般的逻辑运用和组合功能。在正常模式中,来自 LAB 本地互联的四

个数据输入口输入到一个四口输入的 LUT 中 ( 图 2-2)。Quartus II 编译器自动选择

carry- in (cin) 或 data3 信号作为其中一个输入到 LUT。LE 在正常模式中支持套包寄

存器和寄存器的反馈。

图 2-2 显示在正常模式中的 LE。

图 2-2. 在 Cyclone IV 器件上正常模式中的 LE

Register Chain

Connection

sload

sclear

(LAB Wide)

(LAB Wide)

Packed Register Input

data1

data2

data3

cin (from cout

of previous LE)

data4

Four-Input

LUT

clock (LAB Wide)

ena (LAB Wide)

aclr (LAB Wide)

Q

D

ENA

CLRN

Row, Column, and

Direct Link Routing

Row, Column, and

Direct Link Routing

Local Routing

Register Bypass

Register Feedback

Register

Chain Output

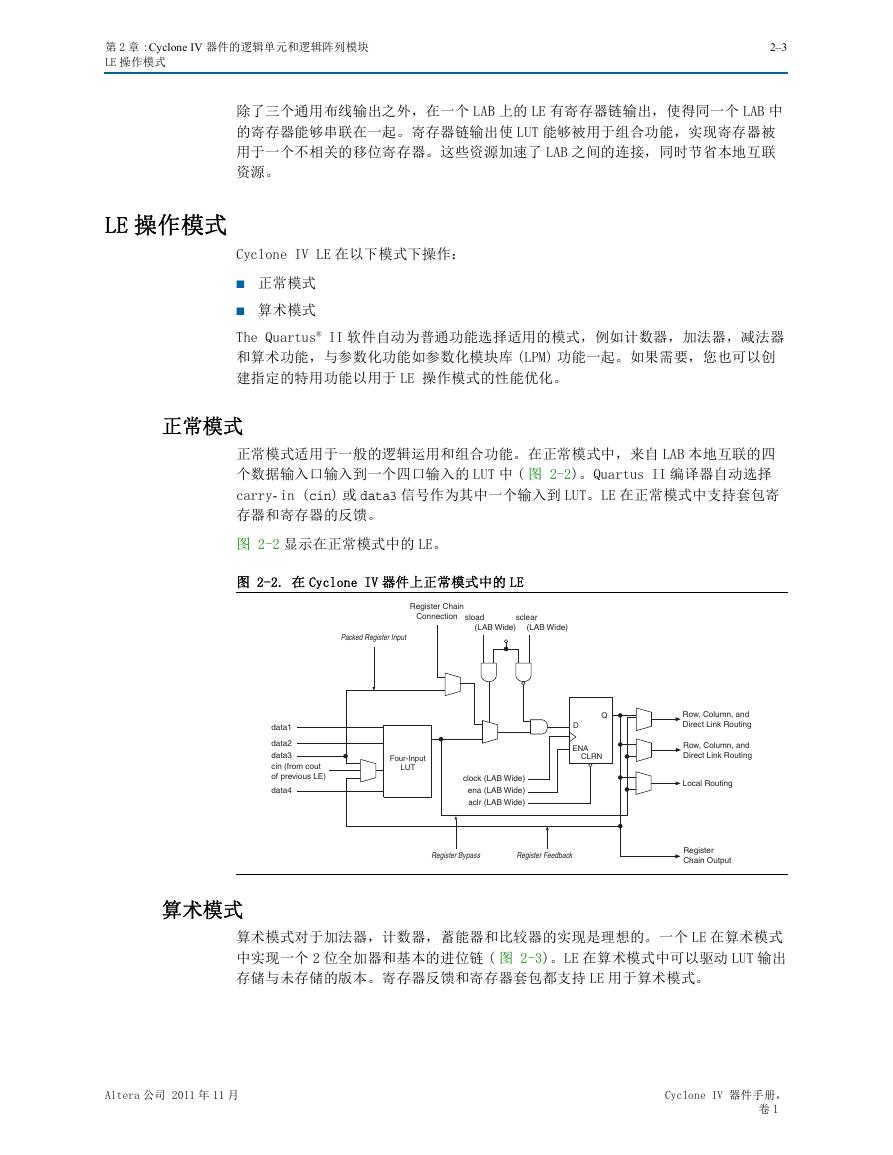

算术模式

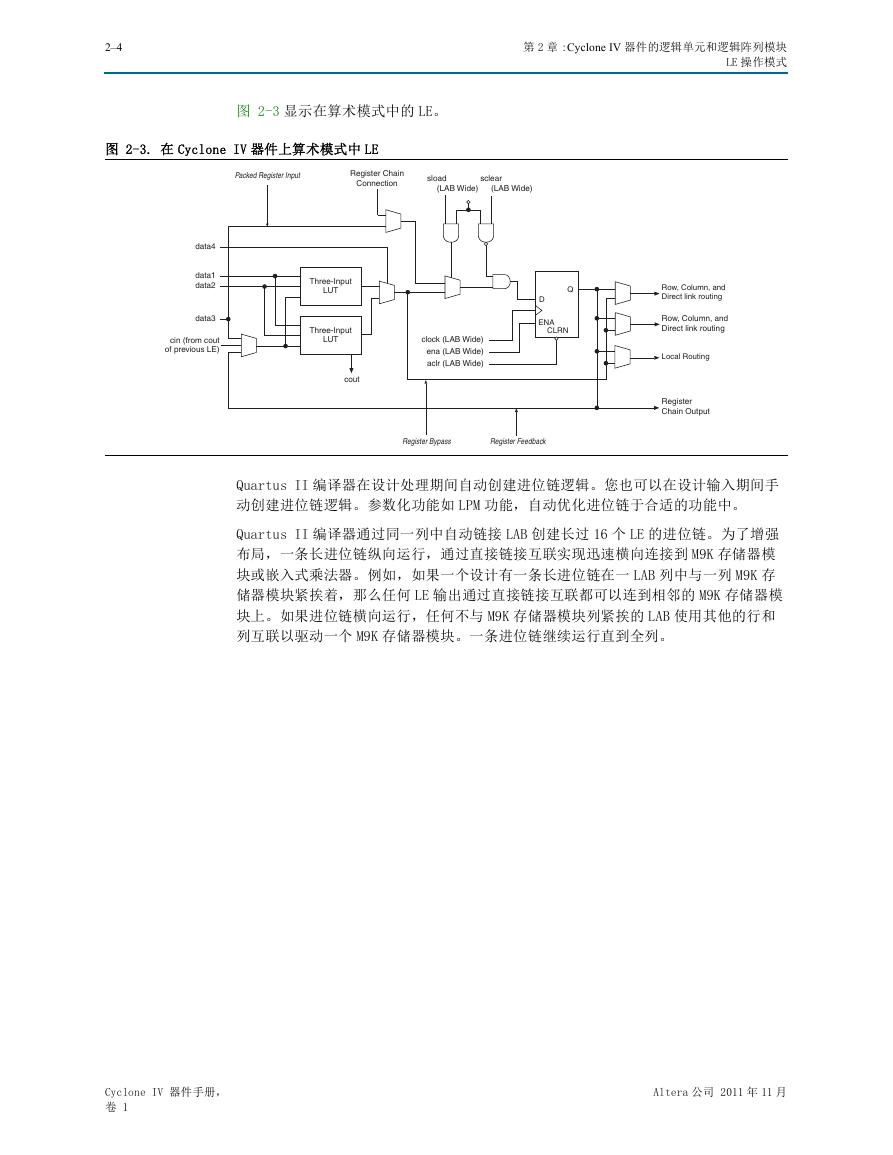

算术模式对于加法器,计数器,蓄能器和比较器的实现是理想的。一个 LE 在算术模式

中实现一个 2 位全加器和基本的进位链 ( 图 2-3)。LE 在算术模式中可以驱动 LUT 输出

存储与未存储的版本。寄存器反馈和寄存器套包都支持 LE 用于算术模式。

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

2–4

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

LE 操作模式

图 2-3 显示在算术模式中的 LE。

图 2-3. 在 Cyclone IV 器件上算术模式中 LE

Packed Register Input

Register Chain

Connection

sload

sclear

(LAB Wide)

(LAB Wide)

data4

data1

data2

data3

cin (from cout

of previous LE)

Three-Input

LUT

Three-Input

LUT

cout

Q

D

ENA

CLRN

clock (LAB Wide)

ena (LAB Wide)

aclr (LAB Wide)

Register Bypass

Register Feedback

Row, Column, and

Direct link routing

Row, Column, and

Direct link routing

Local Routing

Register

Chain Output

Quartus II 编译器在设计处理期间自动创建进位链逻辑。您也可以在设计输入期间手

动创建进位链逻辑。参数化功能如 LPM 功能,自动优化进位链于合适的功能中。

Quartus II 编译器通过同一列中自动链接 LAB 创建长过 16 个 LE 的进位链。为了增强

布局,一条长进位链纵向运行,通过直接链接互联实现迅速横向连接到 M9K 存储器模

块或嵌入式乘法器。例如,如果一个设计有一条长进位链在一 LAB 列中与一列 M9K 存

储器模块紧挨着,那么任何 LE 输出通过直接链接互联都可以连到相邻的 M9K 存储器模

块上。如果进位链横向运行,任何不与 M9K 存储器模块列紧挨的 LAB 使用其他的行和

列互联以驱动一个 M9K 存储器模块。一条进位链继续运行直到全列。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

逻辑阵列模块

2–5

逻辑阵列模块

逻辑阵列模块 (LAB) 包含 LE 组。

拓扑

每个 LAB 包括以下特性:

■ 16 LE

■ LAB 控制信号

■ LE 进位链

■ 寄存器链

■ 本地互联

本地互联在同一个 LAB 的 LE 之间传输信号。寄存器链连接把一个 LE 寄存器的输出传

输到 LAB 中相邻的 LE 寄存器上。Quartus II 编译器放置相关的逻辑在 LAB 或相邻的

LAB 中,允许使用本地和寄存器链连接以实现性能和面积效率。

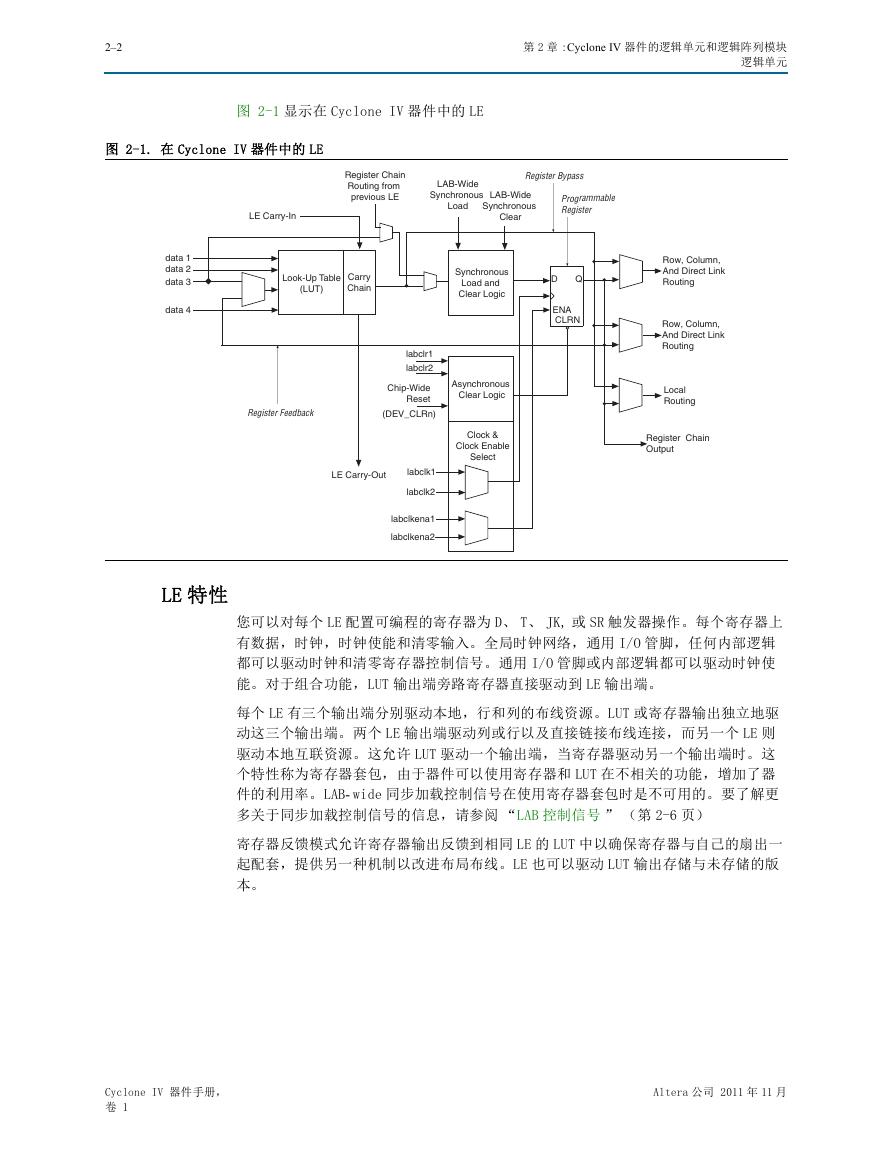

图 2-4 显示在 Cyclone IV 器件中的 LAB 结构。

图 2-4. 在 Cyclone IV 器件中的 LAB 结构

Row Interconnect

Direct link

interconnect

from adjacent

block

Direct link

interconnect

to adjacent

block

LAB

Local Interconnect

Column

Interconnect

Direct link

interconnect

from adjacent

block

Direct link

interconnect

to adjacent

block

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

2–6

LAB 互联

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

LAB 控制信号

LAB 本地互联是由列和行互联以及 LE 在相同的 LAB 中的输出端驱动的。邻近的 LAB, 锁

相环 (PLL),M9K RAM 模块和嵌入式乘法器由左到右通过直接链接连接也可以驱动 LAB

的本地互联。直接链接连接功能最小化行和列互联的使用,以提供更高的性能和灵活

性。每个 LE 通过加速本地和直接链接互联可以驱动多达 48 个的 LE。

图 2-5 显示直接链接连接。

图 2-5. 在 Cyclone IV 器件中的直连连接方式

Direct link interconnect from

left LAB, M9K memory

block, embedded multiplier,

PLL, or IOE output

Direct link interconnect from

right LAB, M9K memory

block, embedded multiplier,

PLL, or IOE output

Direct link

interconnect

to left

Local

Interconnect

Direct link

interconnect

to right

LAB

LAB 控制信号

每个 LAB 都包含专用的逻辑以驱动控制信号各自 LE。控制信号包括:

■ 两个时钟

■ 两个时钟使能

■ 两个异步清零

■ 一个同步清零

■ 一个同步加载

您可以一次使用多达 8 个的控制信号。寄存器套包和同步加载不能被同时使用。

每个 LAB 可以有多达四个的非全局控制信号。您可以使用其他的 LAB 控制信号只要这

些信号是全局信号。

同步清零和加载对于实现计数和其他功能是很有用的。同步清零和同步加载是 LAB-

wide 信号,其影响所有寄存器上的 LAB。

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

文档修订历史

2–7

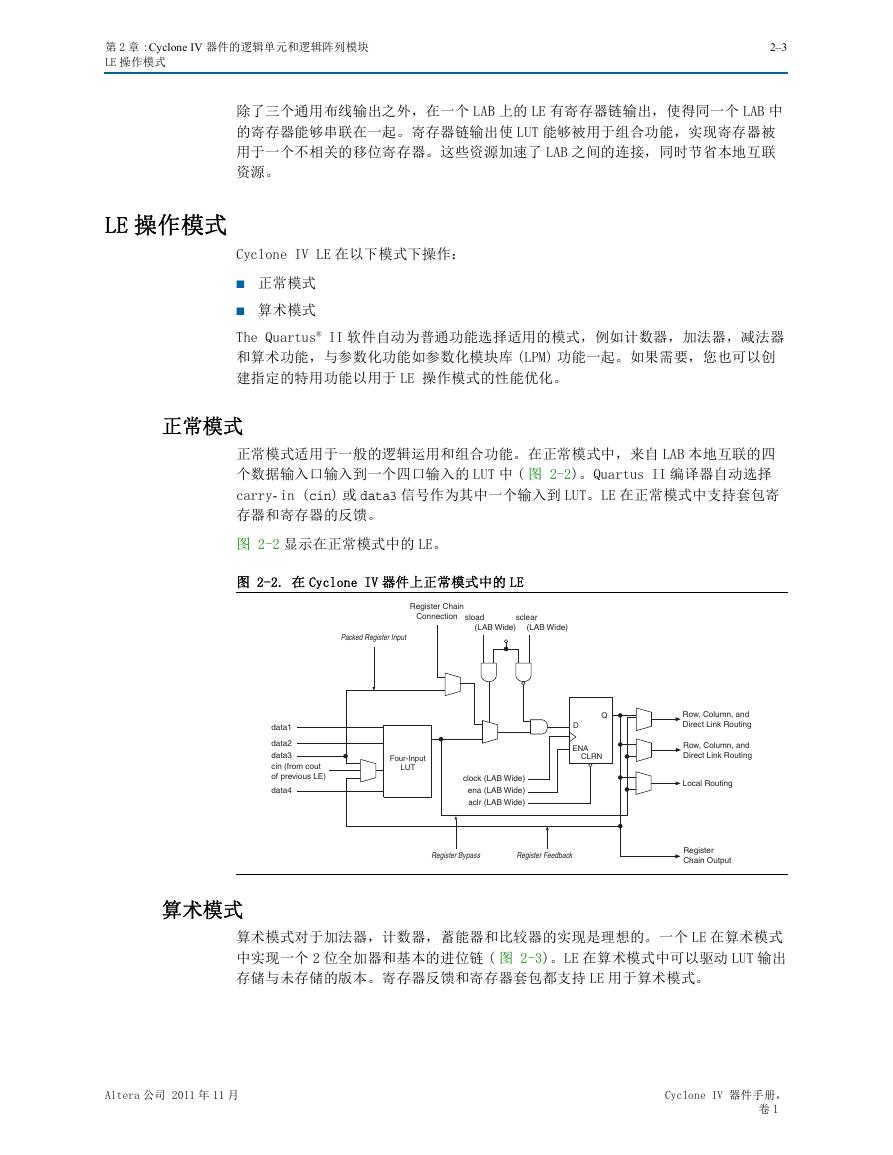

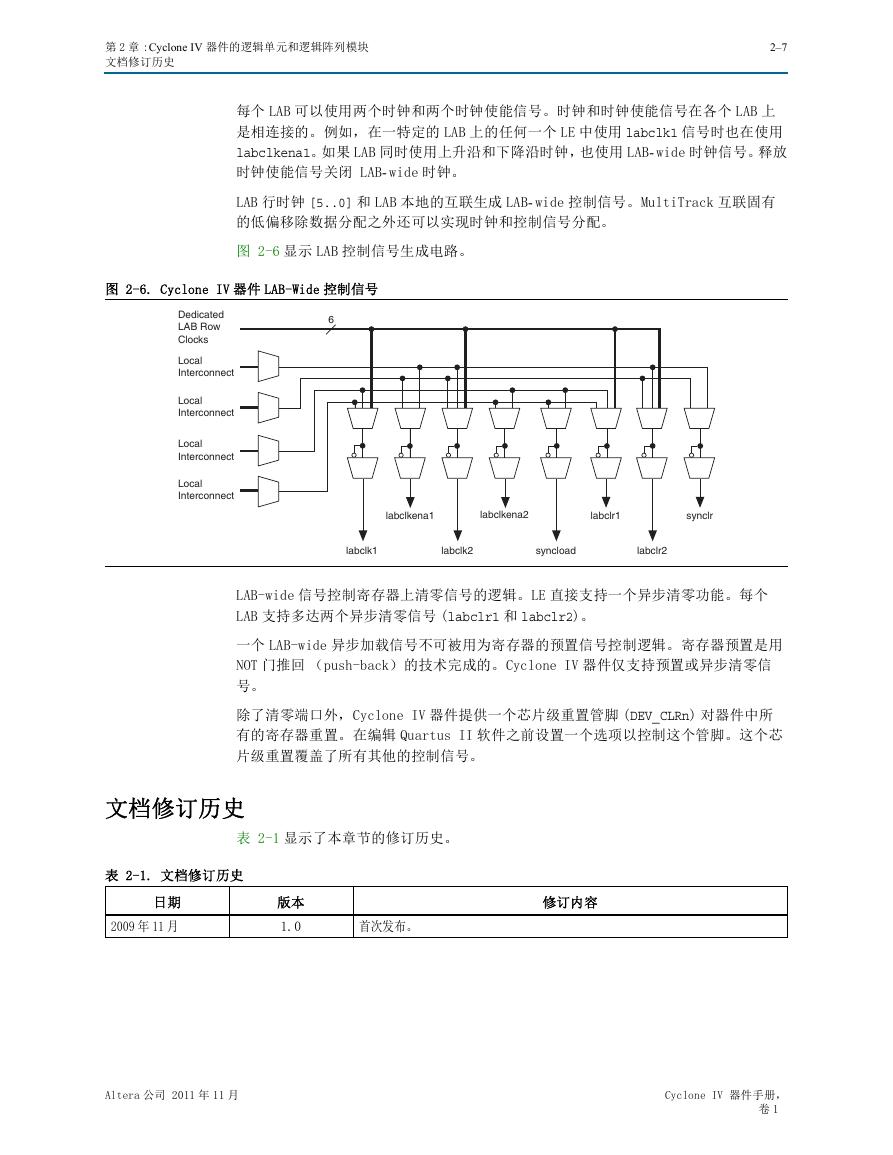

每个 LAB 可以使用两个时钟和两个时钟使能信号。时钟和时钟使能信号在各个 LAB 上

是相连接的。例如,在一特定的 LAB 上的任何一个 LE 中使用 labclk1 信号时也在使用

labclkena1。如果 LAB 同时使用上升沿和下降沿时钟,也使用 LAB- wide 时钟信号。释放

时钟使能信号关闭 LAB- wide 时钟。

LAB 行时钟 [5..0] 和 LAB 本地的互联生成 LAB- wide 控制信号。MultiTrack 互联固有

的低偏移除数据分配之外还可以实现时钟和控制信号分配。

图 2-6 显示 LAB 控制信号生成电路。

图 2-6. Cyclone IV 器件 LAB-Wide 控制信号

6

Dedicated

LAB Row

Clocks

Local

Interconnect

Local

Interconnect

Local

Interconnect

Local

Interconnect

labclkena1

labclkena2

labclr1

synclr

labclk1

labclk2

syncload

labclr2

LAB-wide 信号控制寄存器上清零信号的逻辑。LE 直接支持一个异步清零功能。每个

LAB 支持多达两个异步清零信号 (labclr1 和 labclr2)。

一个 LAB-wide 异步加载信号不可被用为寄存器的预置信号控制逻辑。寄存器预置是用

NOT 门推回 (push-back)的技术完成的。Cyclone IV 器件仅支持预置或异步清零信

号。

除了清零端口外,Cyclone IV 器件提供一个芯片级重置管脚 (DEV_CLRn) 对器件中所

有的寄存器重置。在编辑 Quartus II 软件之前设置一个选项以控制这个管脚。这个芯

片级重置覆盖了所有其他的控制信号。

文档修订历史

表 2-1 显示了本章节的修订历史。

表 2-1. 文档修订历史

日期

2009 年 11 月

版本

1.0

首次发布。

修订内容

Altera 公司 2011 年 11 月 Cyclone IV 器件手册,

卷 1

�

2–8

第 2 章 :Cyclone IV 器件的逻辑单元和逻辑阵列模块

文档修订历史

Cyclone IV 器件手册,

卷 1

Altera 公司 2011 年 11 月

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf