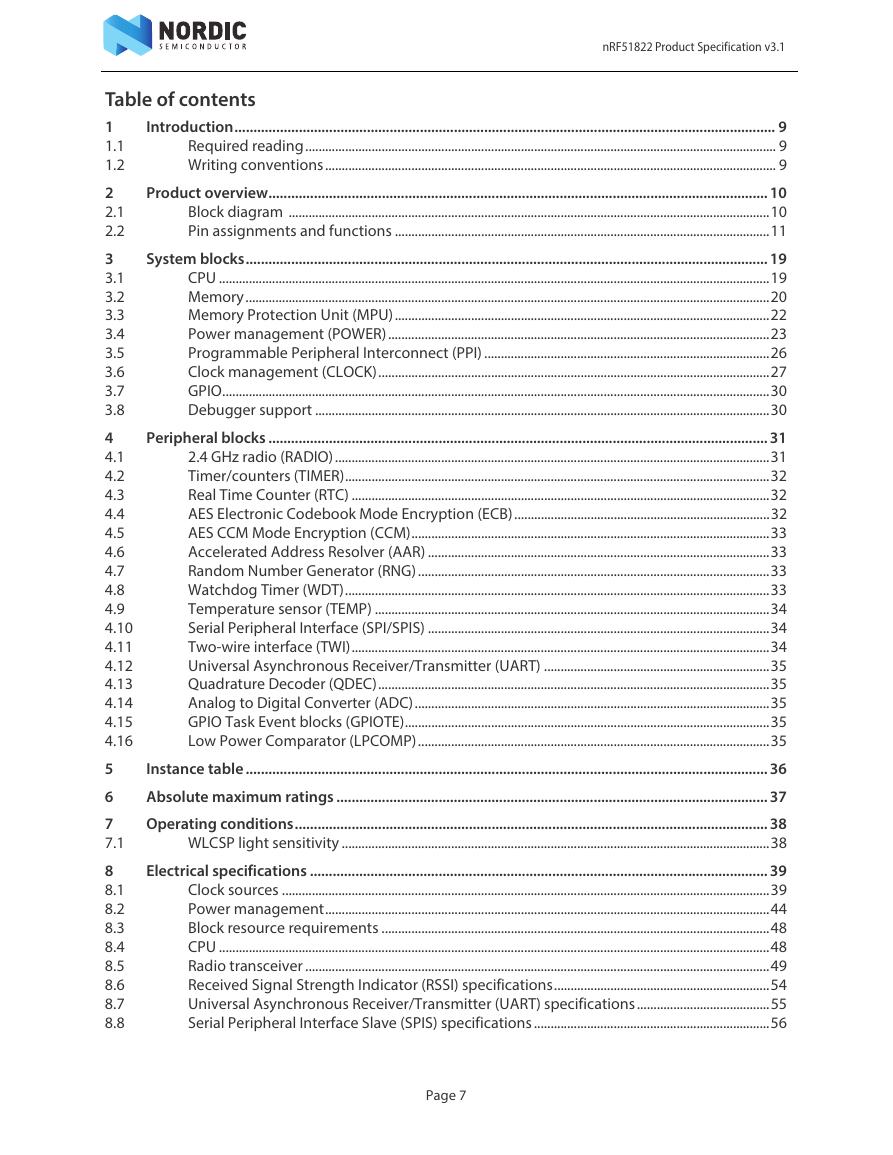

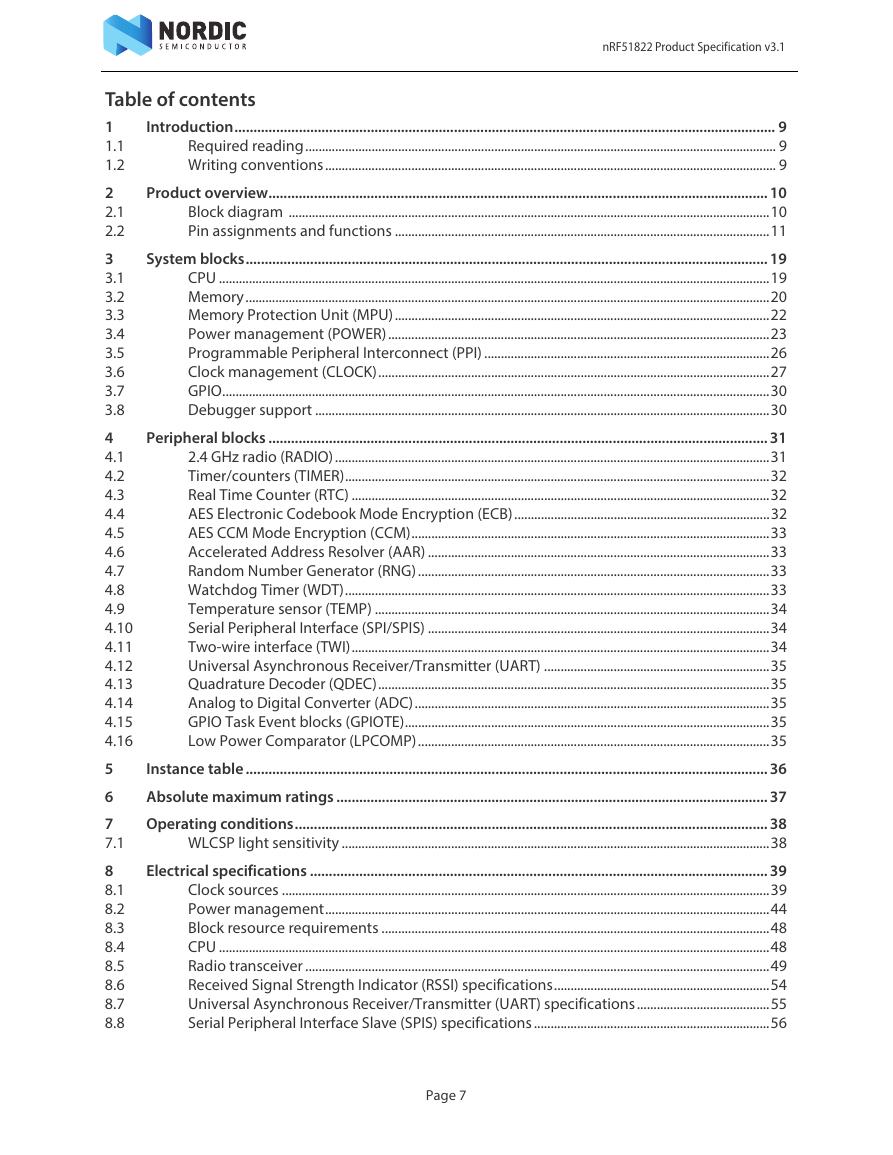

1 Introduction

1.1 Required reading

1.2 Writing conventions

2 Product overview

2.1 Block diagram

2.2 Pin assignments and functions

2.2.1 Pin assignment QFN48

2.2.2 CDAB WLCSP ball assignment and functions

2.2.3 CEAA and CFAC WLCSP ball assignment and functions

3 System blocks

3.1 CPU

3.2 Memory

3.2.1 Code organization

3.2.2 RAM organization

3.3 Memory Protection Unit (MPU)

3.4 Power management (POWER)

3.4.1 Power supply

3.4.2 Power management

3.5 Programmable Peripheral Interconnect (PPI)

3.6 Clock management (CLOCK)

3.6.1 16/32 MHz crystal oscillator

3.6.2 32.768 kHz crystal oscillator

3.6.3 32.768 kHz RC oscillator

3.6.4 Synthesized 32.768 kHz clock

3.7 GPIO

3.8 Debugger support

4 Peripheral blocks

4.1 2.4 GHz radio (RADIO)

4.2 Timer/counters (TIMER)

4.3 Real Time Counter (RTC)

4.4 AES Electronic Codebook Mode Encryption (ECB)

4.5 AES CCM Mode Encryption (CCM)

4.6 Accelerated Address Resolver (AAR)

4.7 Random Number Generator (RNG)

4.8 Watchdog Timer (WDT)

4.9 Temperature sensor (TEMP)

4.10 Serial Peripheral Interface (SPI/SPIS)

4.11 Two-wire interface (TWI)

4.12 Universal Asynchronous Receiver/Transmitter (UART)

4.13 Quadrature Decoder (QDEC)

4.14 Analog to Digital Converter (ADC)

4.15 GPIO Task Event blocks (GPIOTE)

4.16 Low Power Comparator (LPCOMP)

5 Instance table

6 Absolute maximum ratings

7 Operating conditions

7.1 WLCSP light sensitivity

8 Electrical specifications

8.1 Clock sources

8.1.1 16/32 MHz crystal startup

8.1.2 16 MHz crystal oscillator (16M XOSC)

8.1.3 32 MHz crystal oscillator (32M XOSC)

8.1.4 16 MHz RC oscillator (16M RCOSC)

8.1.5 32.768 kHz crystal oscillator (32k XOSC)

8.1.6 32.768 kHz RC oscillator (32k RCOSC)

8.1.7 32.768 kHz Synthesized oscillator (32k SYNT)

8.2 Power management

8.3 Block resource requirements

8.4 CPU

8.5 Radio transceiver

8.5.1 General radio characteristics

8.5.2 Radio current consumption with DC/DC disabled

8.5.3 Radio current consumption with DC/DC enabled

8.5.4 Transmitter specifications

8.5.5 Receiver specifications

8.5.6 Radio timing parameters

8.5.7 Antenna matching network requirements

8.6 Received Signal Strength Indicator (RSSI) specifications

8.7 Universal Asynchronous Receiver/Transmitter (UART) specifications

8.8 Serial Peripheral Interface Slave (SPIS) specifications

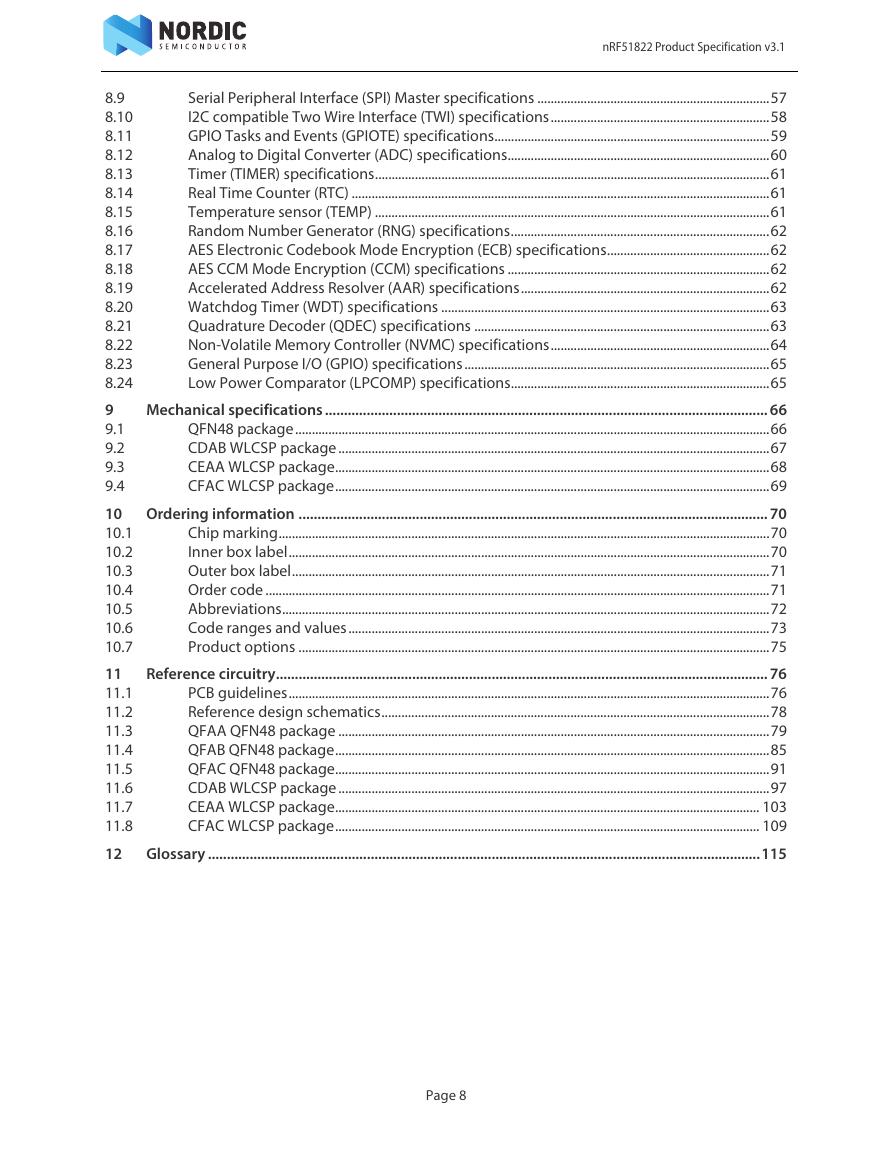

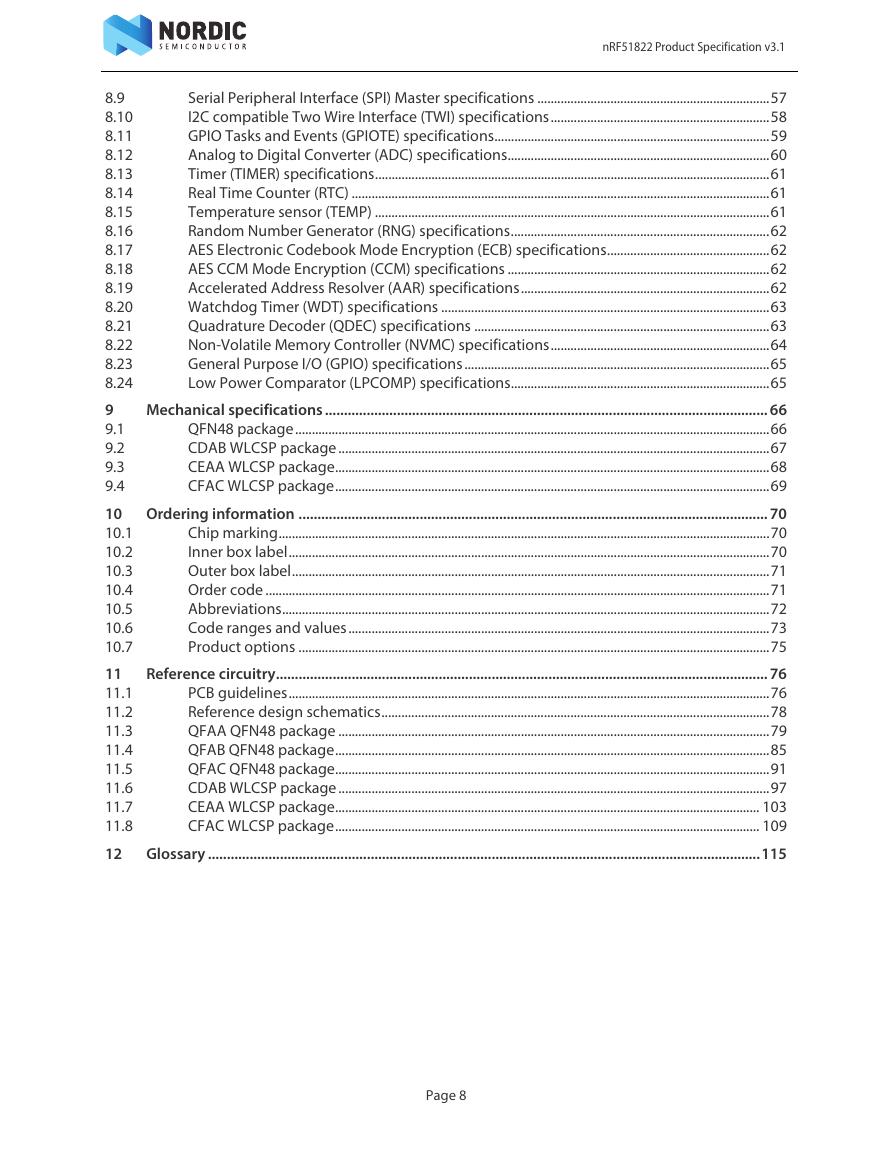

8.9 Serial Peripheral Interface (SPI) Master specifications

8.10 I2C compatible Two Wire Interface (TWI) specifications

8.11 GPIO Tasks and Events (GPIOTE) specifications

8.12 Analog to Digital Converter (ADC) specifications

8.13 Timer (TIMER) specifications

8.14 Real Time Counter (RTC)

8.15 Temperature sensor (TEMP)

8.16 Random Number Generator (RNG) specifications

8.17 AES Electronic Codebook Mode Encryption (ECB) specifications

8.18 AES CCM Mode Encryption (CCM) specifications

8.19 Accelerated Address Resolver (AAR) specifications

8.20 Watchdog Timer (WDT) specifications

8.21 Quadrature Decoder (QDEC) specifications

8.22 Non-Volatile Memory Controller (NVMC) specifications

8.23 General Purpose I/O (GPIO) specifications

8.24 Low Power Comparator (LPCOMP) specifications

9 Mechanical specifications

9.1 QFN48 package

9.2 CDAB WLCSP package

9.3 CEAA WLCSP package

9.4 CFAC WLCSP package

10 Ordering information

10.1 Chip marking

10.2 Inner box label

10.3 Outer box label

10.4 Order code

10.5 Abbreviations

10.6 Code ranges and values

10.7 Product options

10.7.1 nRF ICs

10.7.2 Development tools

11 Reference circuitry

11.1 PCB guidelines

11.1.1 PCB layout example

11.2 Reference design schematics

11.3 QFAA QFN48 package

11.3.1 QFAA QFN48 schematic with internal LDO setup

11.3.2 QFAA QFN48 schematic with low voltage mode setup

11.3.3 QFAA QFN48 schematic with DC/DC converter setup

11.4 QFAB QFN48 package

11.4.1 QFAB QFN48 schematic with internal LDO setup

11.4.2 QFAB QFN48 schematic with low voltage mode setup

11.4.3 QFAB QFN48 schematic with DC/DC converter setup

11.5 QFAC QFN48 package

11.5.1 QFAC QFN48 schematic with internal LDO setup

11.5.2 QFAC QFN48 schematic with low voltage mode setup

11.5.3 QFAC QFN48 schematic with DC/DC converter setup

11.6 CDAB WLCSP package

11.6.1 CDAB WLCSP schematic with internal LDO setup

11.6.2 CDAB WLCSP schematic with low voltage mode setup

11.6.3 CDAB WLCSP schematic with DC/DC converter setup

11.7 CEAA WLCSP package

11.7.1 CEAA WLCSP schematic with internal LDO setup

11.7.2 CEAA WLCSP schematic with low voltage mode setup

11.7.3 CEAA WLCSP schematic with DC/DC converter setup

11.8 CFAC WLCSP package

11.8.1 CFAC WLCSP schematic with internal LDO setup

11.8.2 CFAC WLCSP schematic with low voltage mode setup

11.8.3 CFAC WLCSP schematic with DC/DC converter setup

12 Glossary

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf