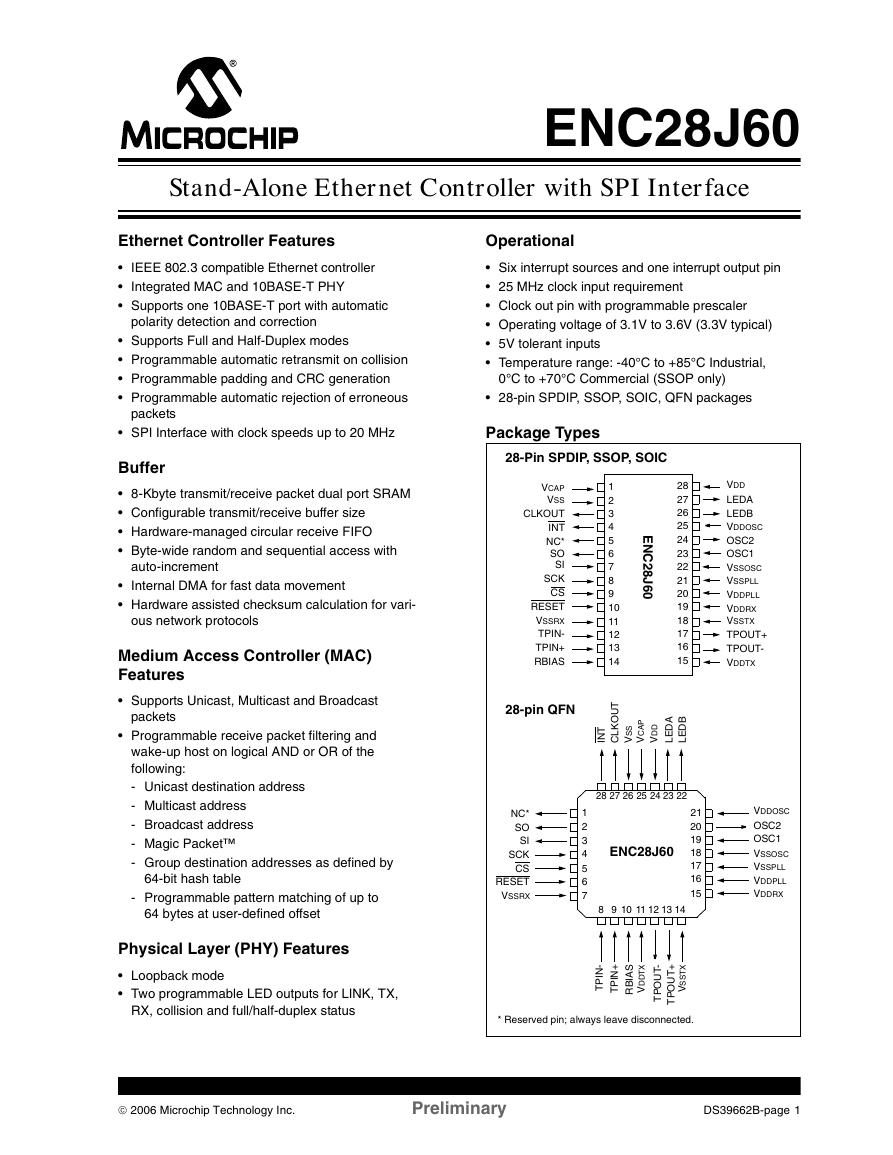

Ethernet Controller Features

Buffer

Medium Access Controller (MAC) Features

Physical Layer (PHY) Features

Operational

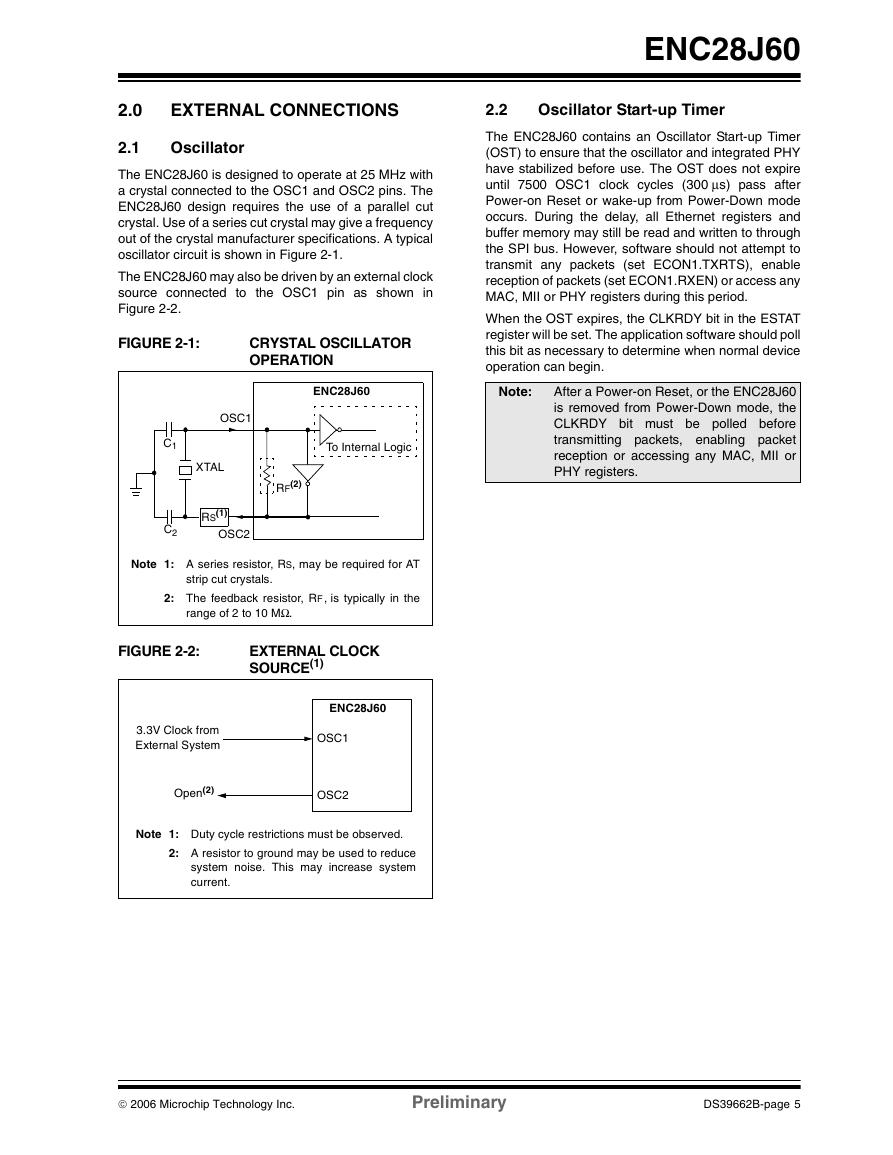

Package Types

Table of Contents

Most Current Data Sheet

Errata

Customer Notification System

1.0 Overview

FIGURE 1-1: ENC28J60 Block Diagram

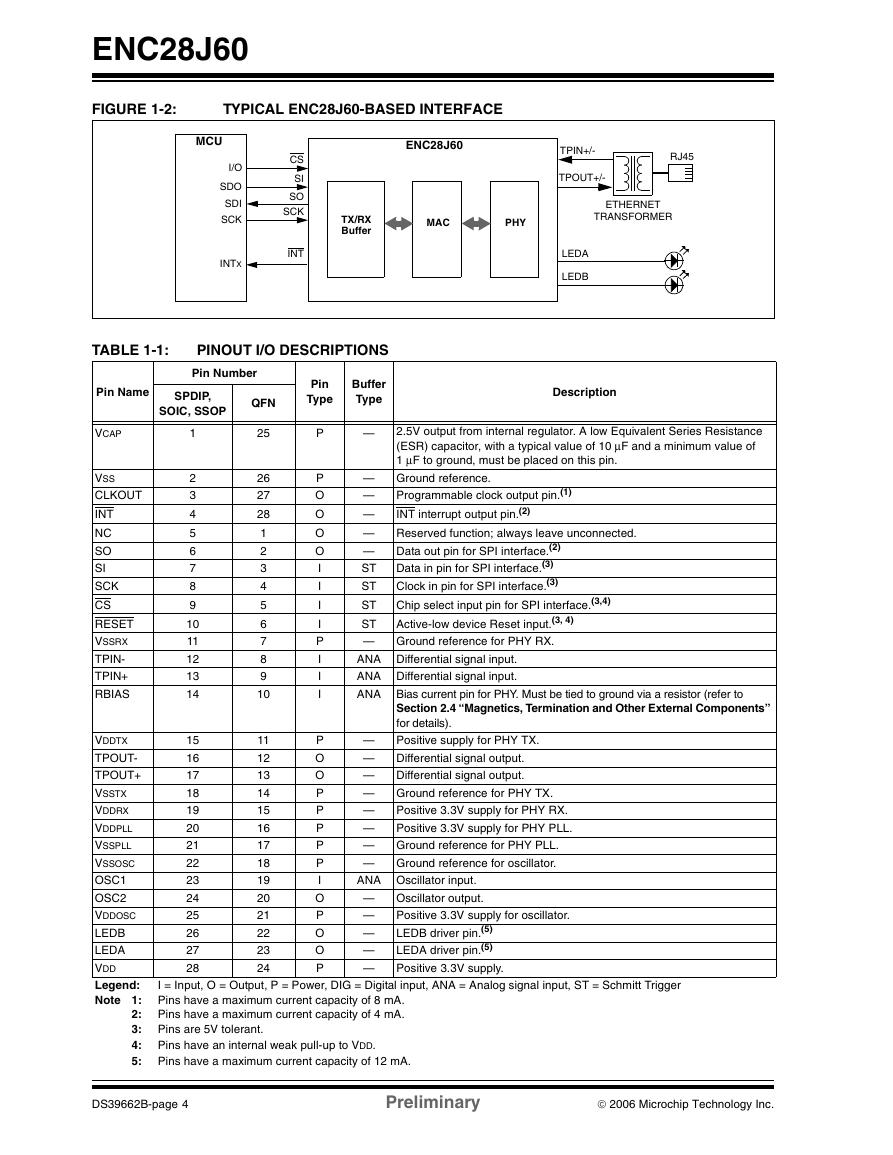

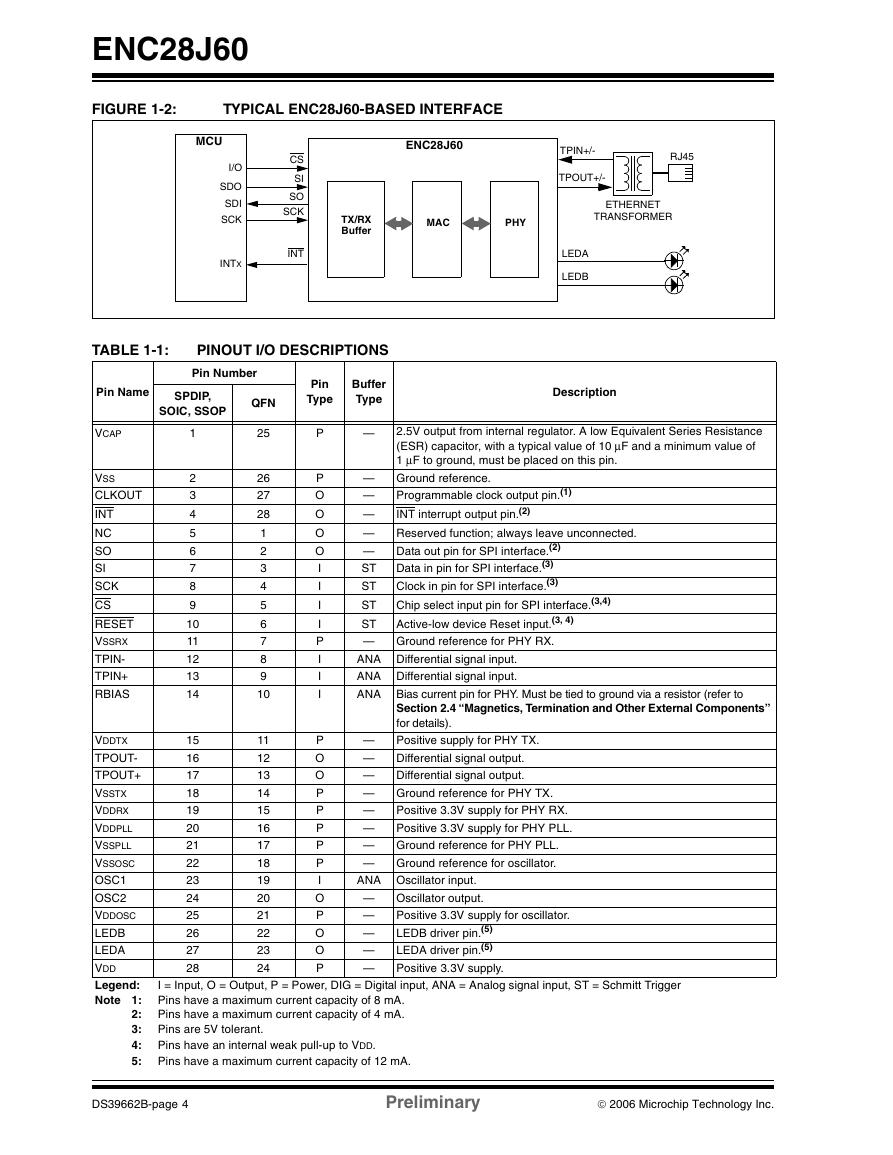

FIGURE 1-2: Typical ENC28J60-Based Interface

TABLE 1-1: Pinout I/O Descriptions

2.0 External Connections

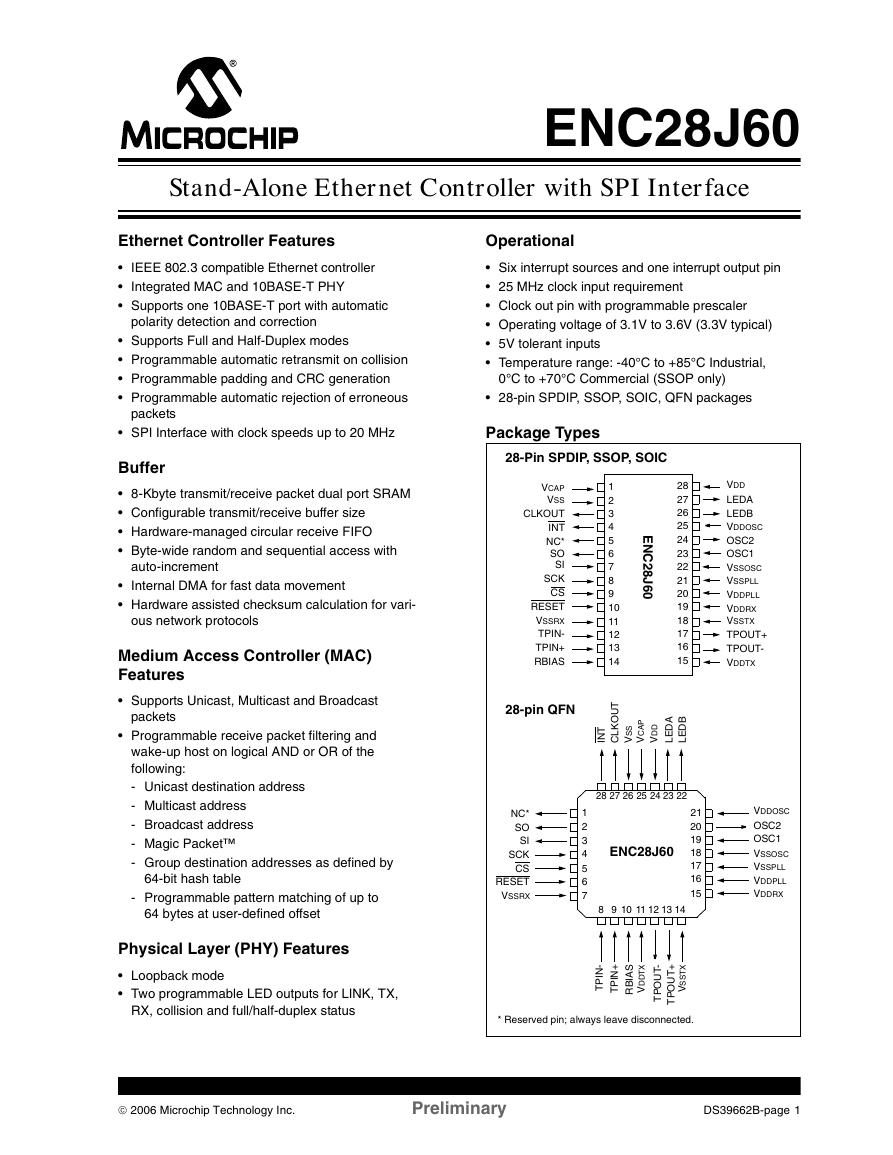

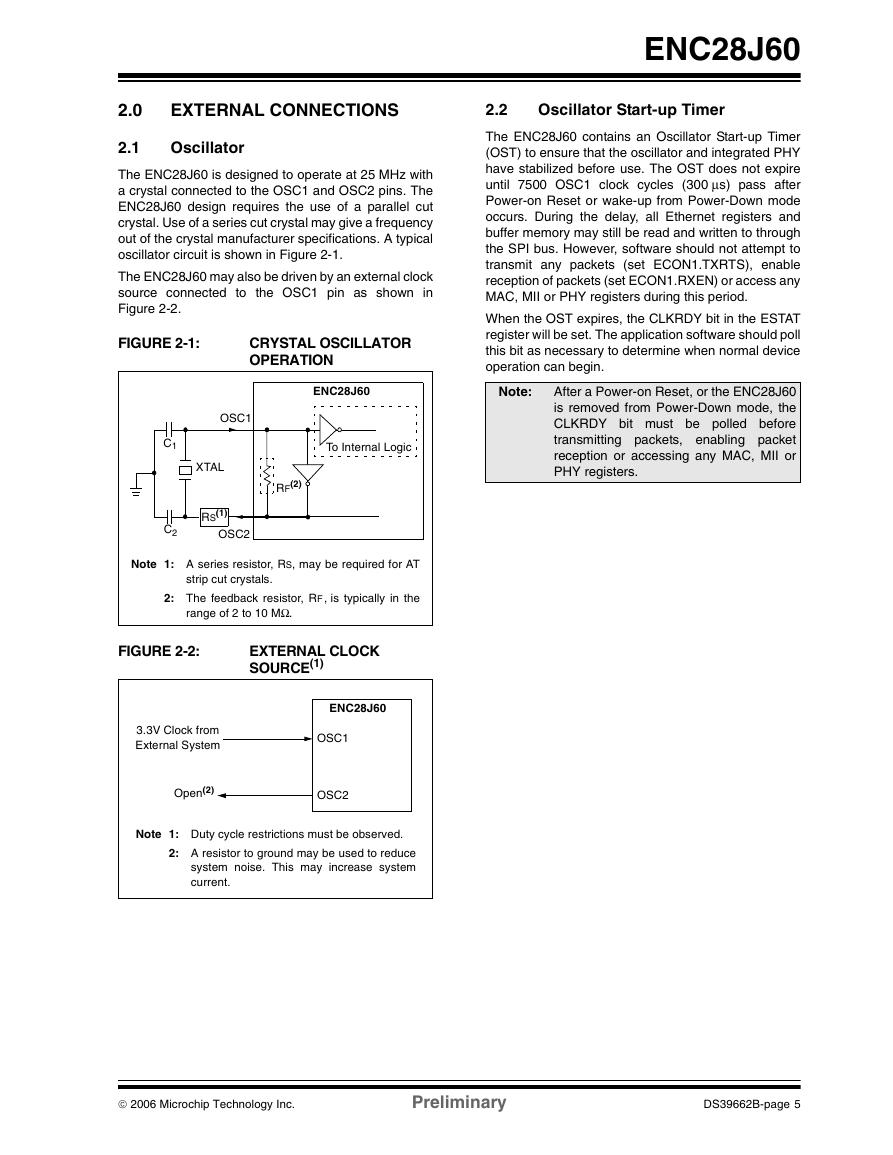

2.1 Oscillator

FIGURE 2-1: Crystal Oscillator Operation��

FIGURE 2-2: External Clock Source(1)��

2.2 Oscillator Start-up Timer

2.3 CLKOUT Pin

FIGURE 2-3: CLKOUT Transition

Register 2-1: ECOCON: Clock Output Control Register

2.4 Magnetics, Termination and Other External Components

FIGURE 2-4: ENC28J60 Ethernet Termination and External Connections

2.5 I/O Levels

FIGURE 2-5: Level Shifting Using AND Gates

FIGURE 2-6: Level Shifting Using 3-State Buffers

2.6 LED Configuration

FIGURE 2-7: LEDB Polarity and Reset Configuration Options

TABLE 2-1: LED Blink Stretch Length

Register 2-2: PHLCON: PHY Module LED Control Register��

3.0 Memory Organization

FIGURE 3-1: ENC28J60 Memory Organization

3.1 Control Registers

TABLE 3-1: ENC28J60 Control Register Map

TABLE 3-2: ENC28J60 Control Register Summary�

3.1.1 ECON1 Register

Register 3-1: ECON1: Ethernet Control Register 1�

3.1.2 ECON2 Register

Register 3-2: ECON2: Ethernet Control Register 2�

3.2 Ethernet Buffer

3.2.1 Receive Buffer

3.2.2 Transmit Buffer

3.2.3 Reading and Writing to the Buffer

3.2.4 DMA Access to the Buffer

FIGURE 3-2: Ethernet Buffer Organization

3.3 PHY Registers

3.3.1 Reading PHY Registers

3.3.2 Writing PHY Registers

3.3.3 Scanning a PHY Register

TABLE 3-3: ENC28J60 PHY Register Summary

Register 3-3: MICMD: MII Command Register�

Register 3-4: MISTAT: MII Status Register�

3.3.4 PHSTAT Registers

3.3.5 PHID1 and PHID2 Registers

Register 3-5: PHSTAT1: Physical Layer Status Register 1�

Register 3-6: PHSTAT2: Physical Layer Status Register 2�

4.0 Serial Peripheral Interface (SPI)

4.1 Overview

FIGURE 4-1: SPI Input Timing

FIGURE 4-2: SPI Output Timing

4.2 SPI Instruction Set

TABLE 4-1: SPI Instruction Set for the ENC28J60

4.2.1 Read Control Register Command

FIGURE 4-3: Read Control Register Command Sequence (ETH Registers)

FIGURE 4-4: Read Control Register Command Sequence (MAC and MII Registers)

4.2.2 Read Buffer Memory Command

4.2.3 Write Control Register Command

FIGURE 4-5: Write Control Register Command Sequence

4.2.4 Write Buffer Memory Command

4.2.5 Bit Field Set Command

4.2.6 Bit Field Clear Command

FIGURE 4-6: Write Buffer Memory Command Sequence

4.2.7 System Reset Command

FIGURE 4-7: System Reset Command Sequence

5.0 Ethernet Overview

5.1 Packet Format

5.1.1 Preamble/Start-of-Frame Delimiter

FIGURE 5-1: Ethernet Packet Format

5.1.2 Destination Address

5.1.3 Source Address

5.1.4 Type/Length

5.1.5 Data

5.1.6 Padding

5.1.7 CRC

6.0 Initialization

6.1 Receive Buffer

6.2 Transmission Buffer

6.3 Receive Filters

6.4 Waiting For OST

6.5 MAC Initialization Settings

Register 6-1: MACON1: MAC Control Register 1�

Register 6-2: MACON3: MAC Control Register 3�

Register 6-3: MACON4: MAC Control Register 4�

Register 6-4: MABBIPG: MAC Back-to-back Inter-packet GAP Register�

6.6 PHY Initialization Settings

Register 6-5: PHCON2: PHY Control Register 2

7.0 Transmitting and Receiving Packets

7.1 Transmitting Packets

FIGURE 7-1: Format for Per Packet Control Bytes

FIGURE 7-2: Sample TRansmit Packet Layout

TABLE 7-1: Transmit Status Vectors

TABLE 7-2: Summary of Registers Used for Packet Transmission�

7.2 Receiving Packets

7.2.1 Enabling Reception

7.2.2 Receive Packet Layout

FIGURE 7-3: Sample Receive Packet Layout

TABLE 7-3: Receive Status Vectors

7.2.3 Reading Received Packets

EXAMPLE 7-1: Random Access Address Calculation

7.2.4 Freeing Receive Buffer Space

7.2.5 Receive Buffer Free Space

EXAMPLE 7-2: Receive Buffer Free Space Calculation

TABLE 7-4: Summary of Registers Used for Packet Reception

8.0 Receive Filters

Register 8-1: ERXFCON: Ethernet RECEIVE FILTER CONTROL REGISTER�

FIGURE 8-1: Receive Filtering Using OR Logic

FIGURE 8-2: Receive Filtering Using AND Logic

8.1 Unicast Filter

8.2 Pattern Match Filter

FIGURE 8-3: Sample Pattern Match Format

8.3 Magic Packet™ Filter

FIGURE 8-4: SAMPLE MAGIC PACKET™ Format

8.4 Hash Table Filter

8.5 Multicast Filter

8.6 Broadcast Filter

9.0 Duplex Mode Configuration and Negotiation

9.1 Half-Duplex Operation

9.2 Full-Duplex Operation

10.0 Flow Control

10.1 Half-Duplex Mode

10.2 Full-Duplex Mode

FIGURE 10-1: Sample Full-Duplex Network

Register 10-1: EFLOCON: Ethernet Flow Control Register�

TABLE 10-1: Summary of Registers Used with Flow Control

11.0 Reset

FIGURE 11-1: On-Chip Reset Circuit

11.1 Power-on Reset (POR)

11.2 System Reset

11.3 Transmit Only Reset

11.4 Receive Only Reset

11.5 PHY Subsystem Reset

Register 11-1: PHCON1: PHY Control Register 1

12.0 Interrupts

FIGURE 12-1: ENC28J60 Interrupt Logic

12.1 INT Interrupt Enable (INTIE)

12.1.1 INT Interrupt Registers

Register 12-1: ESTAT: Ethernet Status Register�

Register 12-2: EIE: Ethernet Interrupt Enable Register�

Register 12-3: EIR: Ethernet Interrupt Request (Flag) Register�

Register 12-4: PHIE: PHY Interrupt Enable Register�

Register 12-5: PHIR: PHY Interrupt Request (Flag) Register�

12.1.2 Receive Error Interrupt Flag (RXERIF)

12.1.3 Transmit Error Interrupt Flag (TXERIF)

12.1.4 Transmit Interrupt Flag (TXIF)

12.1.5 Link Change Interrupt Flag (LINKIF)

12.1.6 DMA Interrupt Flag (DMAIF)

12.1.7 Receive Packet Pending Interrupt Flag (PKTIF)

12.2 Wake-On-LAN/Remote Wake-up

12.2.1 Setup Steps for Waking Up on a Magic Packet

13.0 Direct Memory Access Controller

13.1 Copying Memory

13.2 Checksum Calculations

TABLE 13-1: Summary of Registers Associated with the DMA Controller

14.0 Power-Down

TABLE 14-1: Summary of Registers Used with Power-Down

15.0 Built-in Self-Test Controller

Register 15-1: EBSTCON: Ethernet SELF-TEST CONTROL REGISTER�

15.1 Using the BIST

15.2 Random Data Fill Mode

15.3 Address Fill Mode

15.4 Pattern Shift Fill Mode

TABLE 15-1: Summary of Registers Associated with the Self-Test Controller

16.0 Electrical Characteristics

Absolute Maximum Ratings

16.1 DC Characteristics: ENC28J60 (Industrial and Commercial)�

TABLE 16-1: AC Characteristics: ENC28J60 (Industrial and Commercial)

TABLE 16-2: Oscillator Timing Characteristics��

TABLE 16-3: Reset AC Characteristics��

TABLE 16-4: CLKOUT Pin AC Characteristics��

TABLE 16-5: Requirements for External Magnetics��

FIGURE 16-1: SPI Input Timing�

FIGURE 16-2: SPI Output Timing�

TABLE 16-6: SPI Interface AC Characteristics��

17.0 Packaging Information

17.1 Package Marking Information

17.2 Package Details

28-Lead Skinny Plastic Dual In-line (SP) – 300 mil Body (PDIP)

28-Lead Plastic Small Outline (SO) –�Wide, 300 mil Body (SOIC)

28-Lead Plastic Shrink Small Outline (SS) – 209 mil Body, 5.30 mm (SSOP)

28-Lead Plastic Quad Flat No Lead Package (ML) 6x6 mm Body (QFN) – With 0.55 mm Contact Length (S...

INDEX

The Microchip Web Site

Customer Change Notification Service

Customer Support

Reader Response

Product Identification System

Worldwide Sales and Service

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf