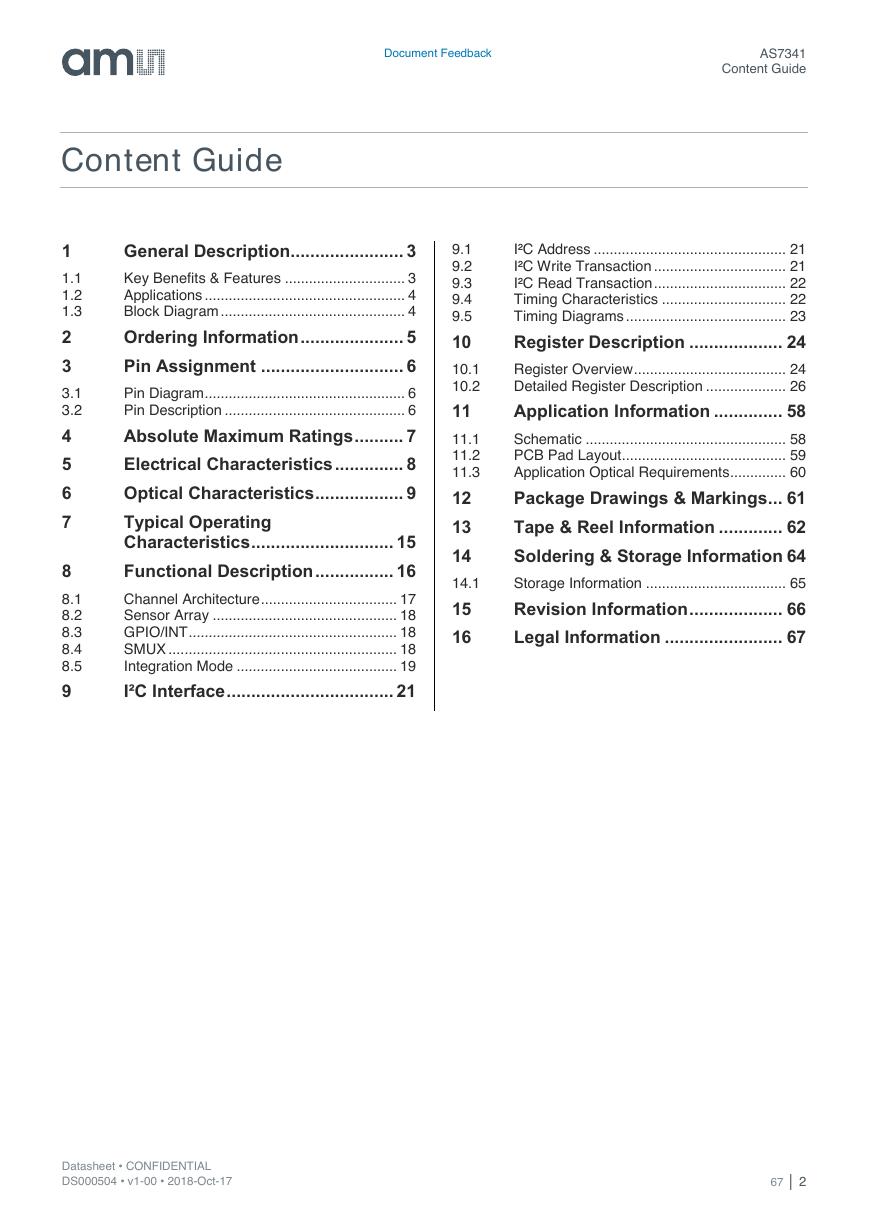

Content Guide

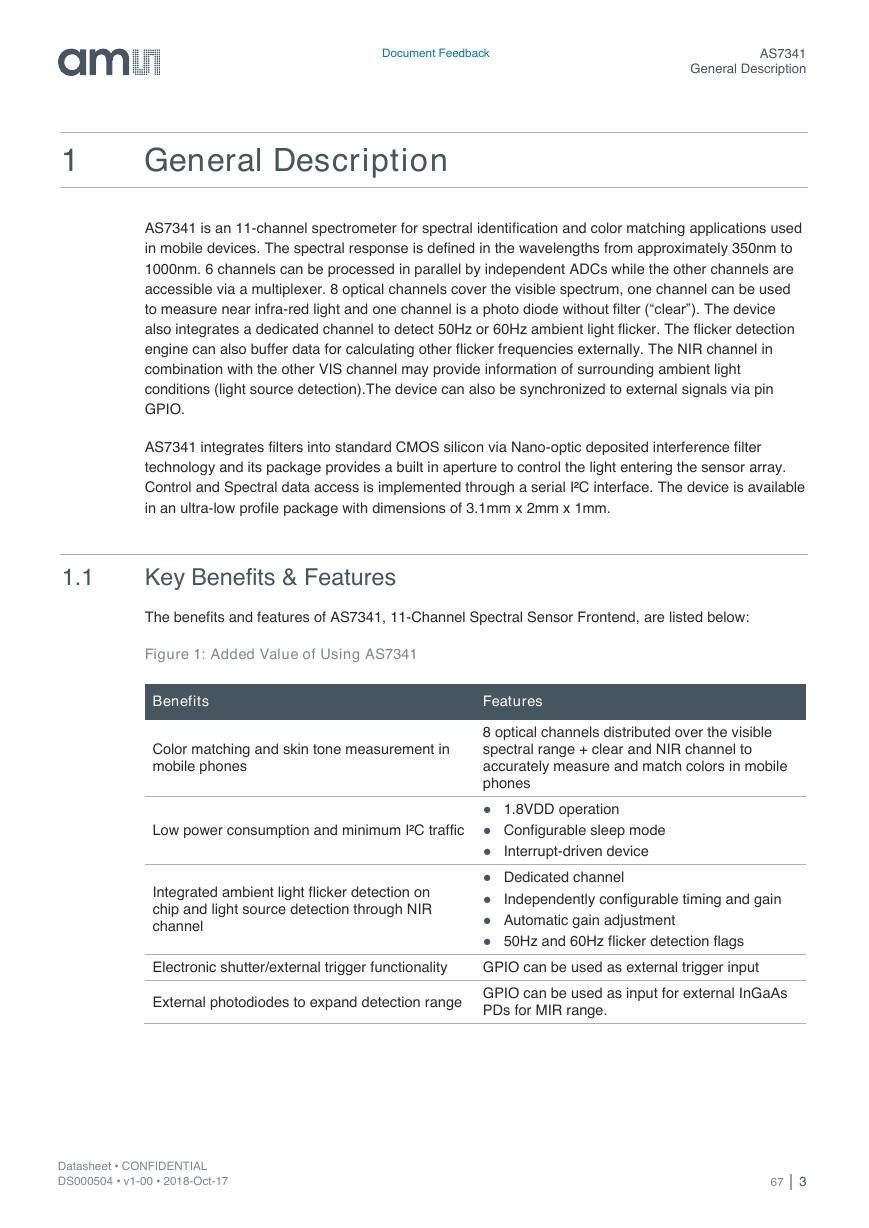

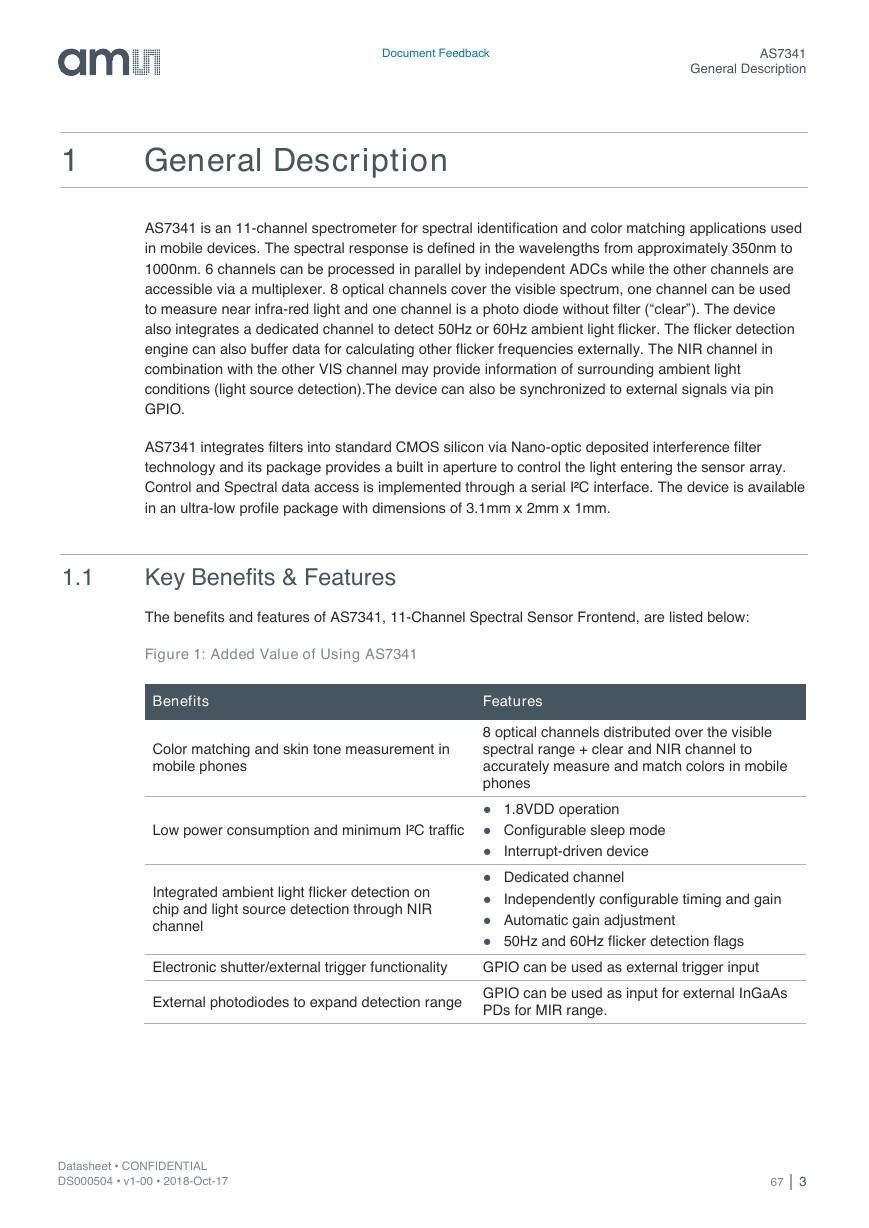

1 General Description

1.1 Key Benefits & Features

1.2 Applications

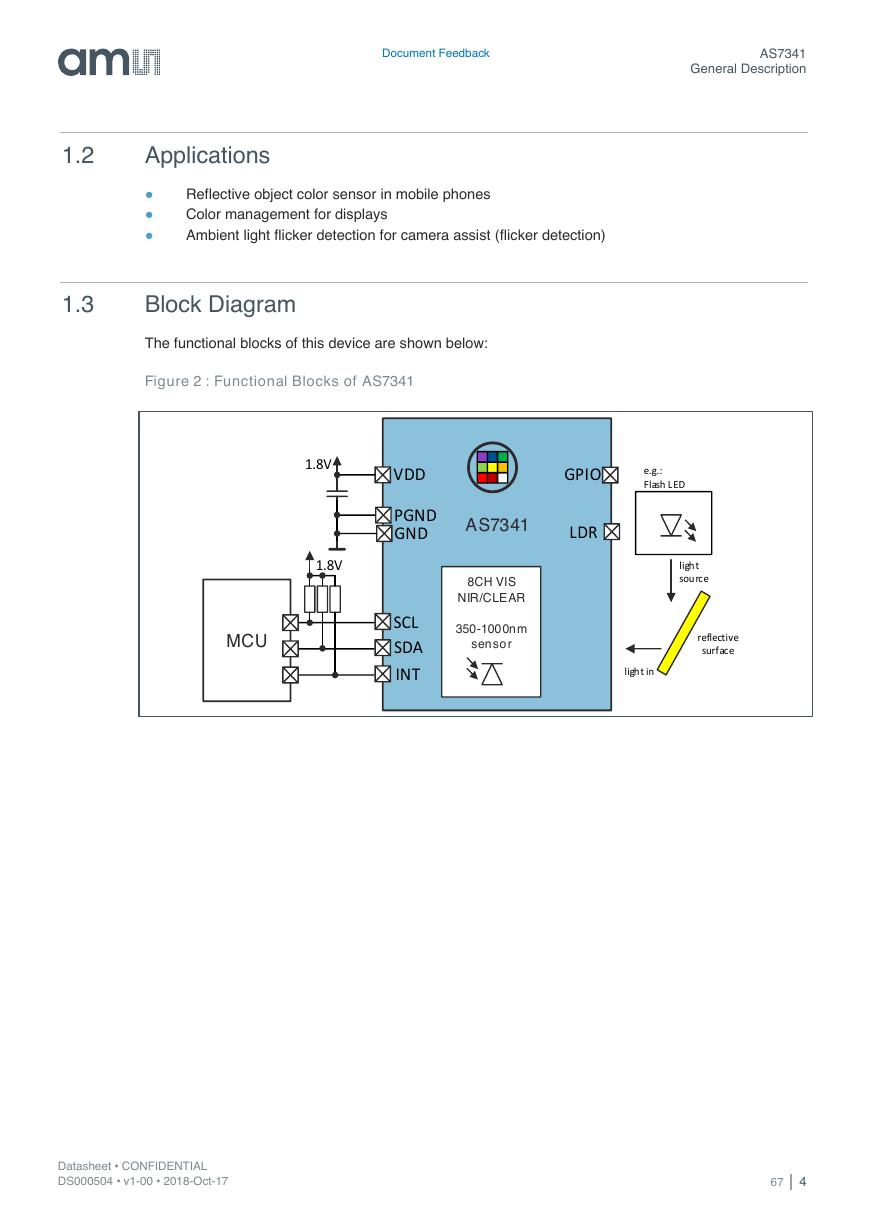

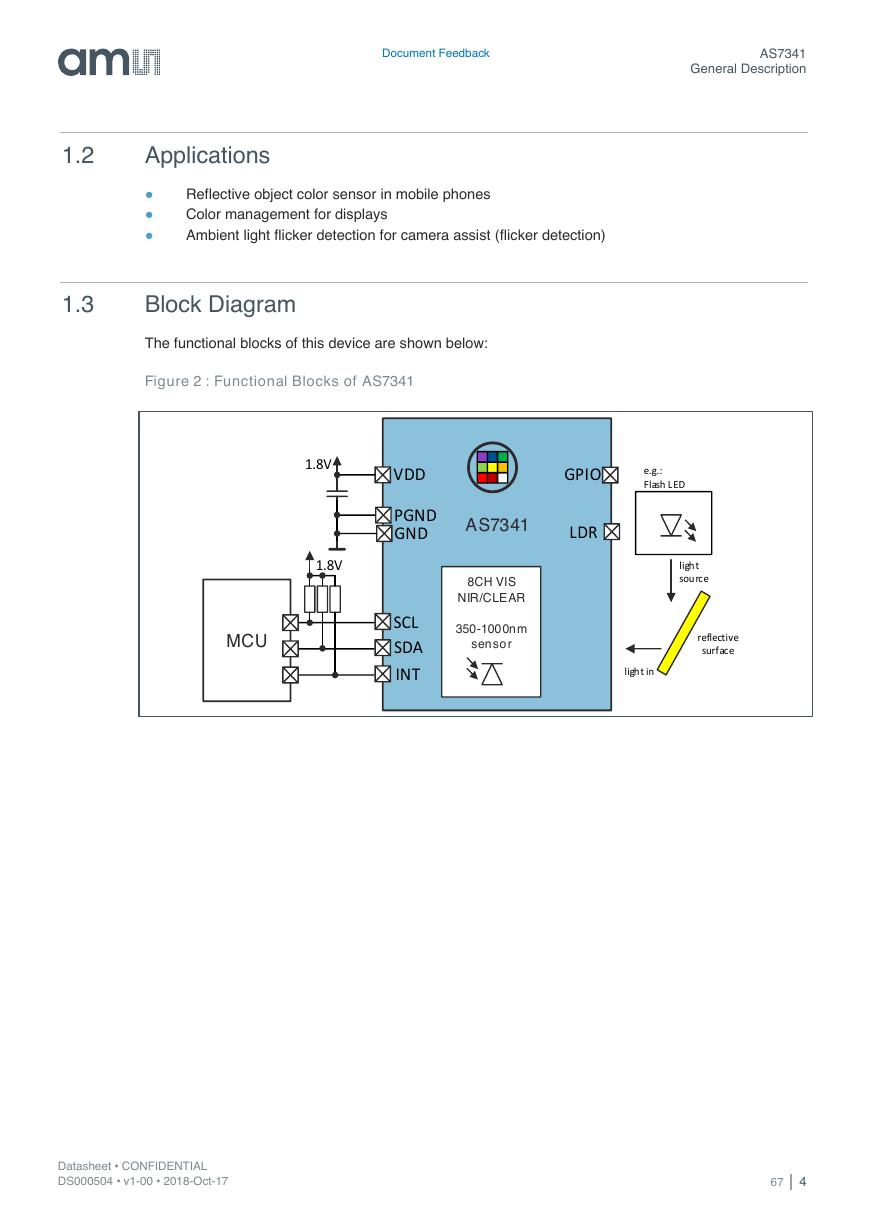

1.3 Block Diagram

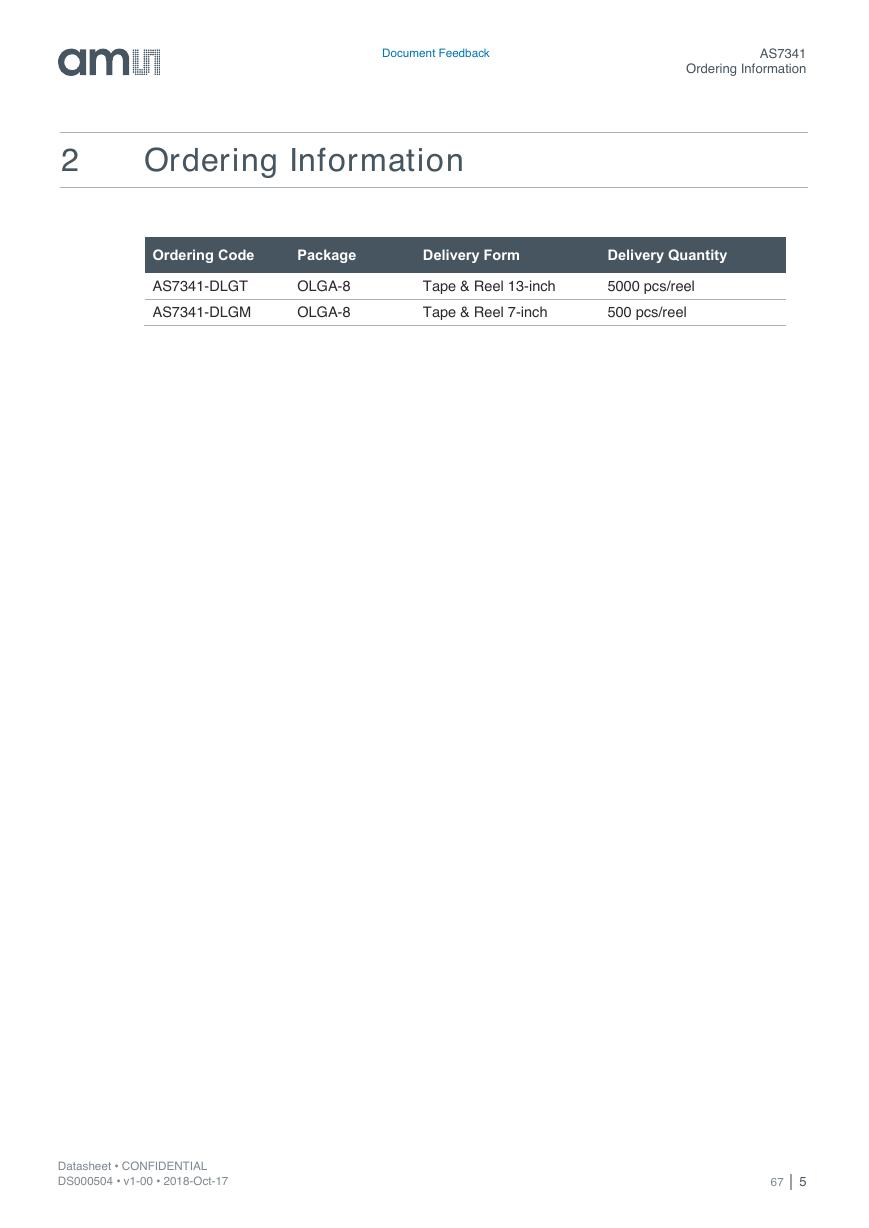

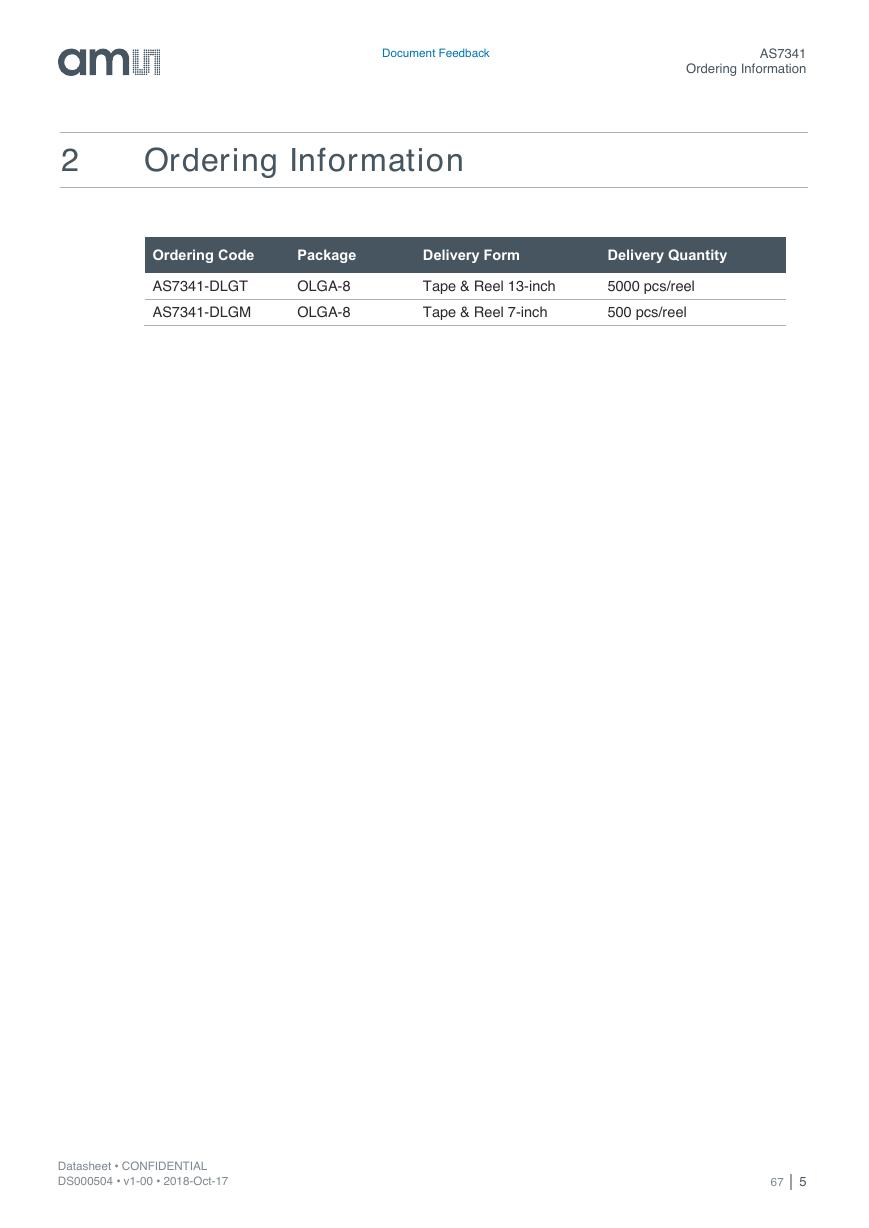

2 Ordering Information

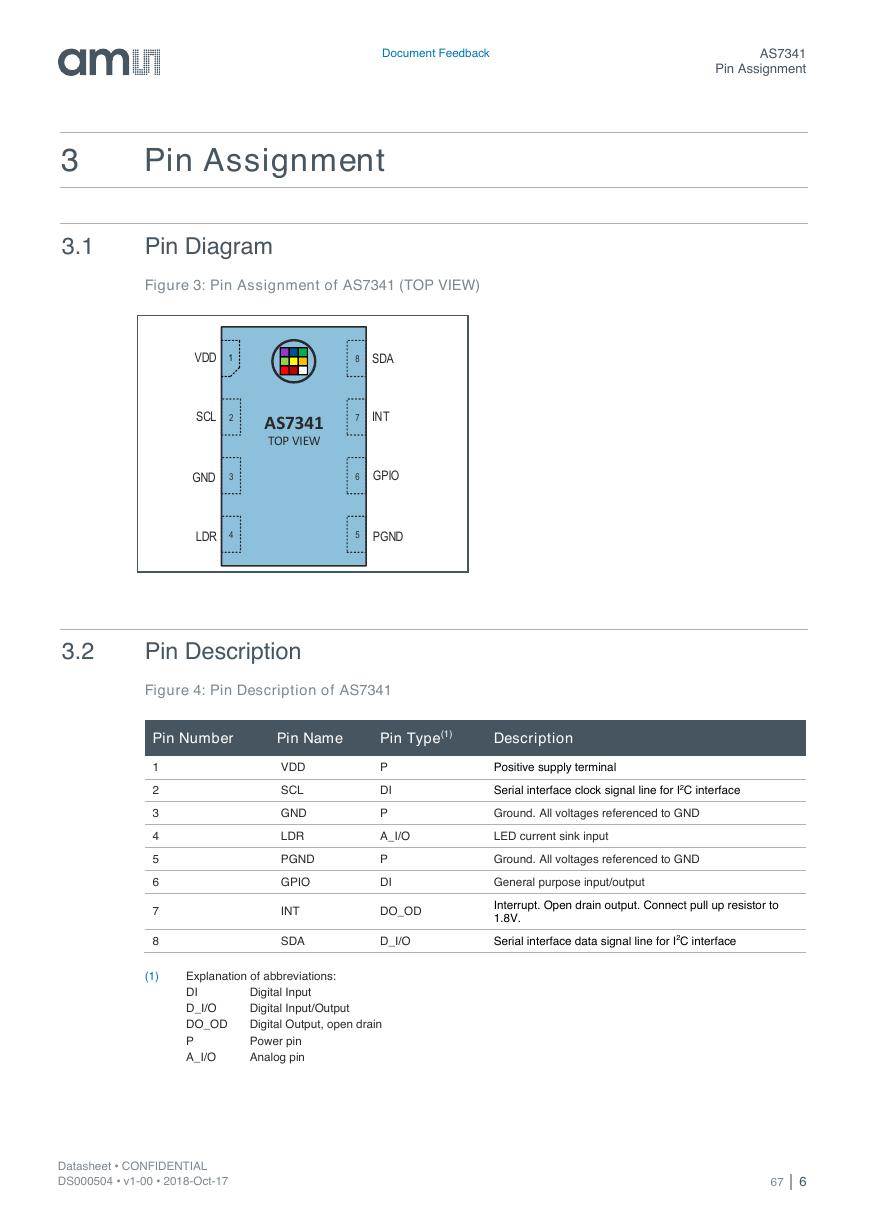

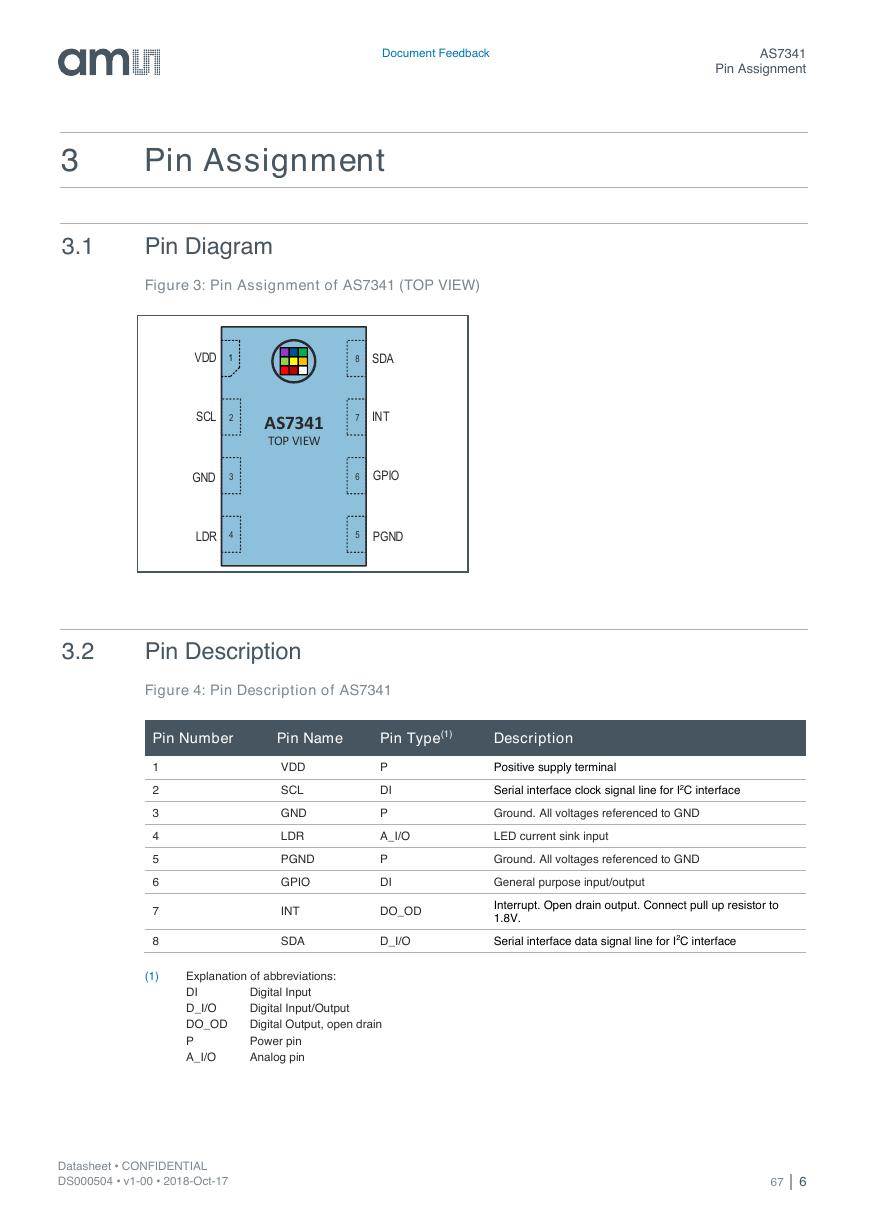

3 Pin Assignment

3.1 Pin Diagram

3.2 Pin Description

4 Absolute Maximum Ratings

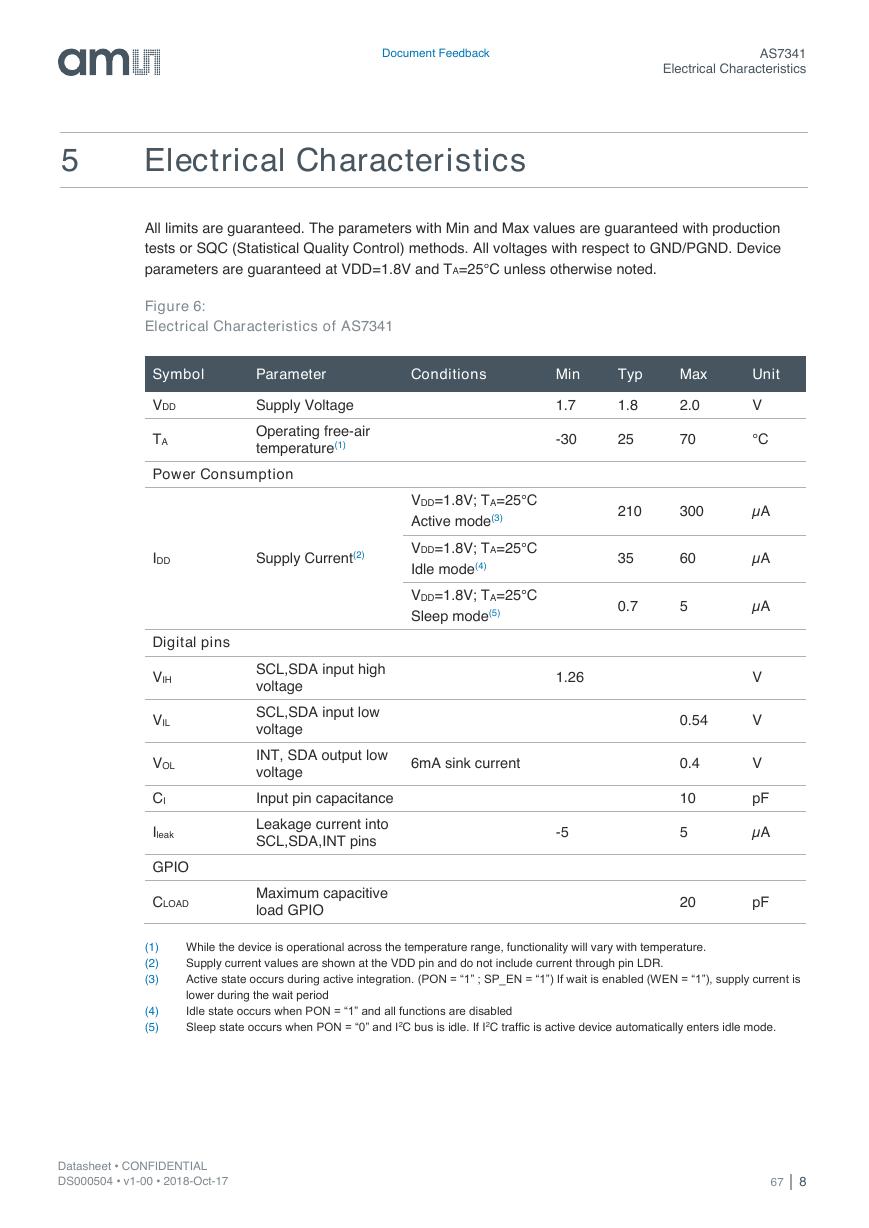

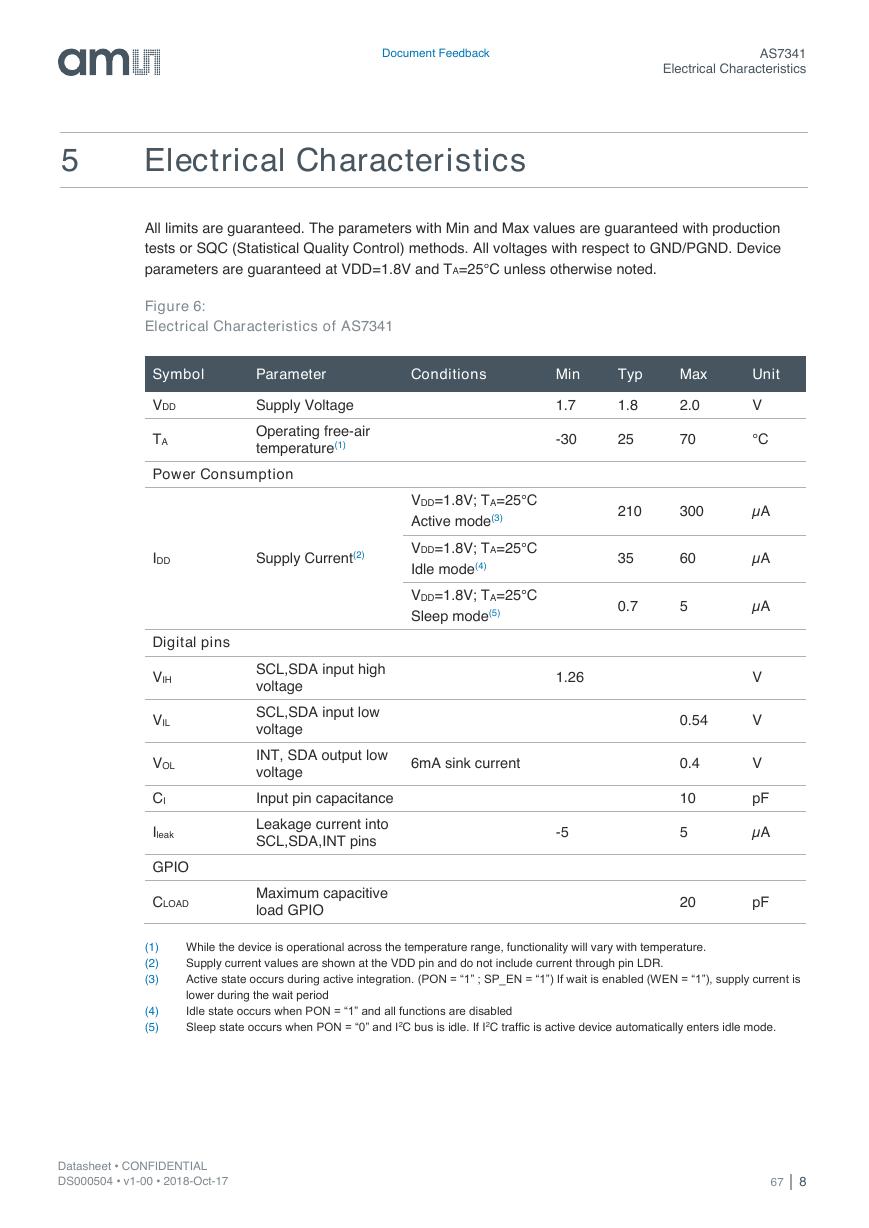

5 Electrical Characteristics

6 Optical Characteristics

7 Typical Operating Characteristics

8 Functional Description

8.1 Channel Architecture

8.2 Sensor Array

8.3 GPIO/INT

8.4 SMUX

8.5 Integration Mode

9 I²C Interface

9.1 I²C Address

9.2 I²C Write Transaction

9.3 I²C Read Transaction

9.4 Timing Characteristics

9.5 Timing Diagrams

10 Register Description

10.1 Register Overview

10.2 Detailed Register Description

10.2.1 Enable and Configuration Register

ENABLE Register (Address 0x80)

CONFIG Register (Address 0x70)

GPIO Register (Address 0x73)

GPIO 2 Register (Address 0xBE)

LED Register (Address 0x74)

INTENAB Register (Address 0xF9)

CONTROL Register (Address 0xFA)

10.2.2 ADC Timing Configuration / Integration Time

ATIME Register (Address 0x81)

ASTEP Register (Address 0xCA, 0xCB)

WTIME Register (Address 0x83)

ITIME Register (Address 0x63, 0x64, 0x65)

EDGE Register (Address 0x72)

FD_TIME Register (Address 0xD8, 0xDA)

10.2.3 ADC Configuration (gain, AGC…)

CFG1 Register (Address 0xAA)

CFG10 Register (Address 0xB3)

AZ_CONFIG Register (Address 0xD6)

AGC_GAIN_MAX Register (Address 0xCF)

CFG8 Register (Address 0xB1)

10.2.4 Device Identification

AUXID Register (Address 0x90)

REVID Register (Address 0x91)

ID Register (Address 0x92)

10.2.5 Spectral Interrupt Configuration

SP_TH_L_LSB Register (Address 0x84)

SP_TH_L_MSB Register (Address 0x85)

SP_TH_H_LSB Register (Address 0x86)

SP _TH_H_MSB Register (Address 0x87)

CFG12 Register (Address 0xB5)

10.2.6 Device Status Register

STAT Register (Address 0x71)

STATUS Register (Address 0x93)

STATUS 2 Register (Address 0xA3)

STATUS 3 Register (Address 0xA4)

STATUS 5 Register (Address 0xA6)

STATUS 6 Register (Address 0xA7)

FD_STATUS Register (Address 0xDB)

10.2.7 Spectral Data and Status

ASTATUS Register (Address 0x60 or 0x94)

CH0_DATA Register (Address 0x95/0x96)

CH1_DATA Register (Address 0x97/0x98)

CH2_DATA Register (Address 0x99/0x9A)

CH3_DATA Register (Address 0x9B/0x9C)

CH4_DATA Register (Address 0x9D/0x9E)

CH5_DATA Register (Address 0x9F/0xA0)

10.2.8 Miscellaneous Configuration

CFG0 Register (Address 0xA9)

CFG3 Register (Address 0xAC)

CFG6 Register (Address 0xAF)

CFG9 Register (Address 0xB2)

PERS Register (Address 0xBD)

10.2.9 FIFO Buffer Data and Status

FIFO_MAP Register (Address 0xFC)

FIFO_CFG0 Register (Address 0xD7)

FIFO_LVL Register (Address 0xFD)

FDATA Register (Address 0xFE and 0xFF)

11 Application Information

11.1 Schematic

11.2 PCB Pad Layout

11.3 Application Optical Requirements

12 Package Drawings & Markings

13 Tape & Reel Information

14 Soldering & Storage Information

14.1 Storage Information

14.1.1 Moisture Sensitivity

14.1.2 Shelf Life

14.1.3 Floor Life

14.1.4 Rebaking Instructions

15 Revision Information

16 Legal Information

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf