1. General Descriptions

2. Features

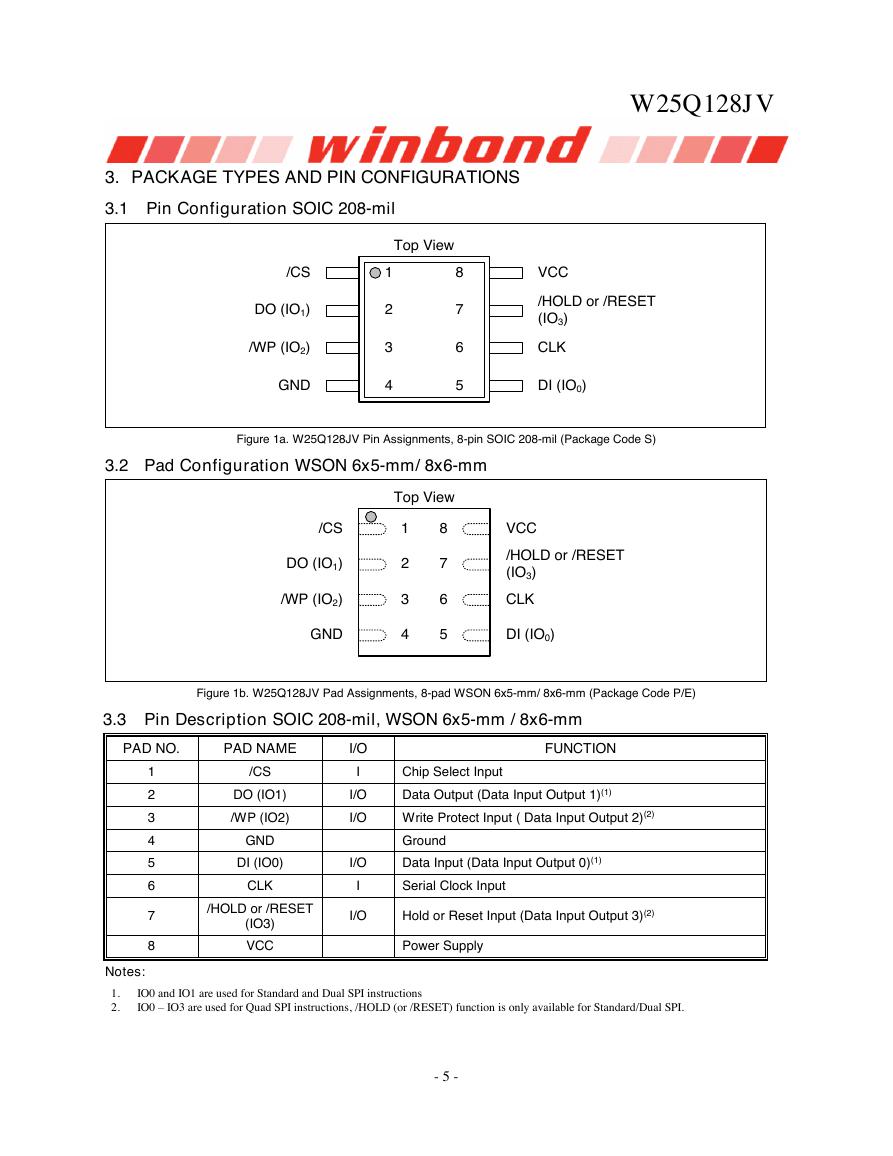

3. Package types and Pin configurations

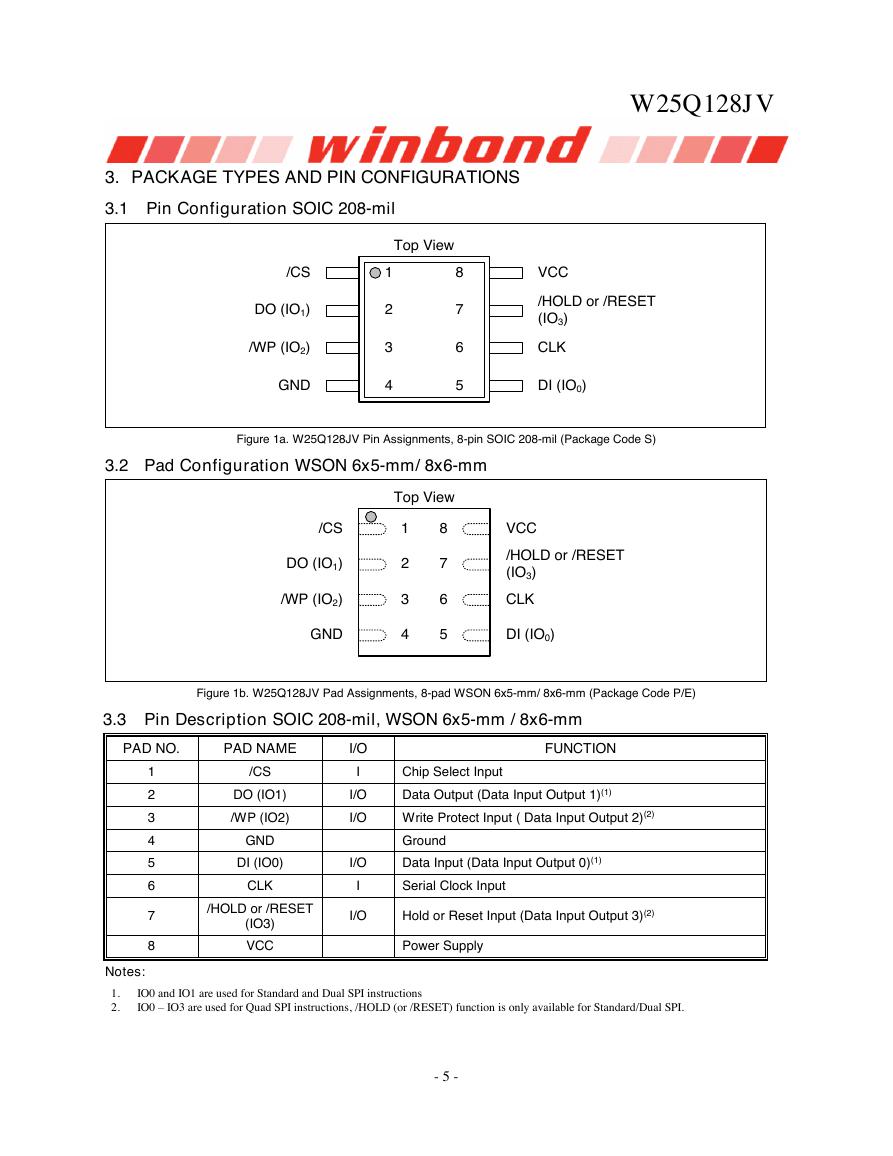

3.1 Pin Configuration SOIC 208-mil

3.2 Pad Configuration WSON 6x5-mm/ 8x6-mm

3.3 Pin Description SOIC 208-mil, WSON 6x5-mm / 8x6-mm

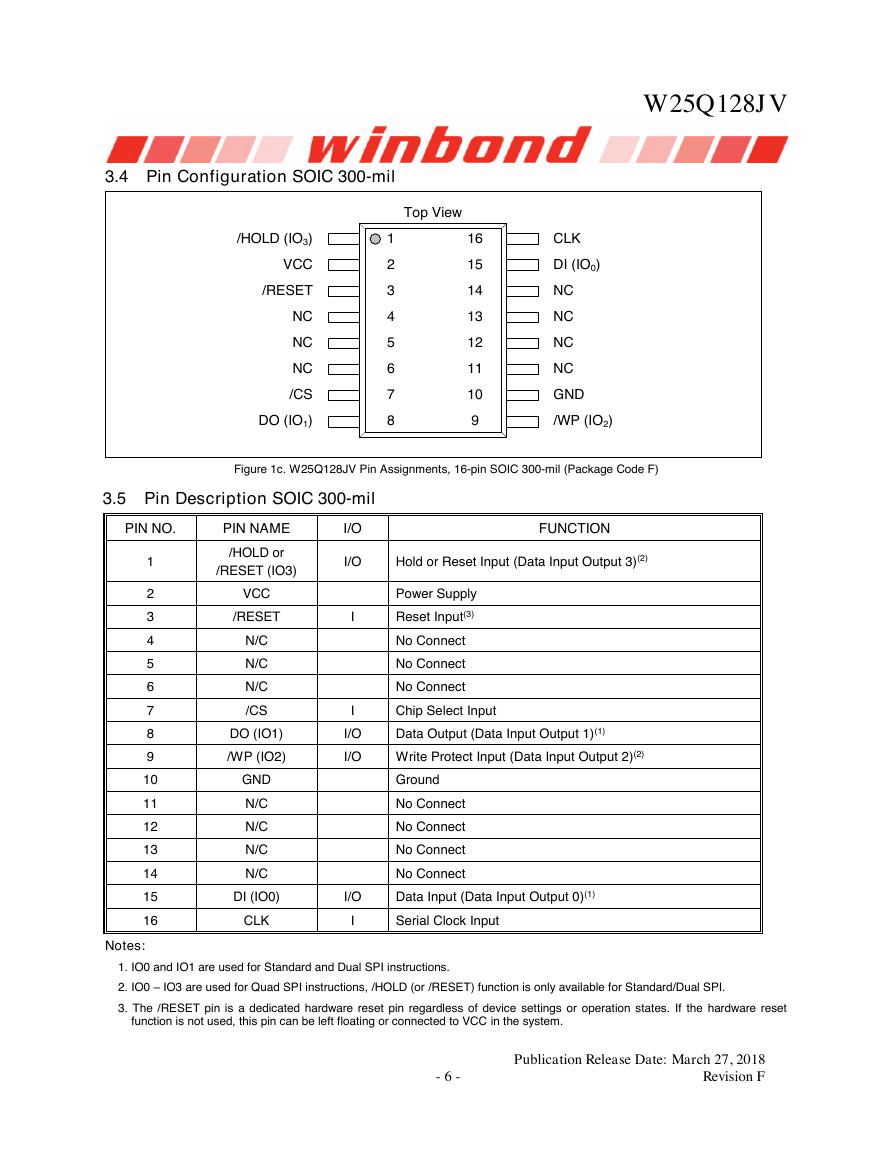

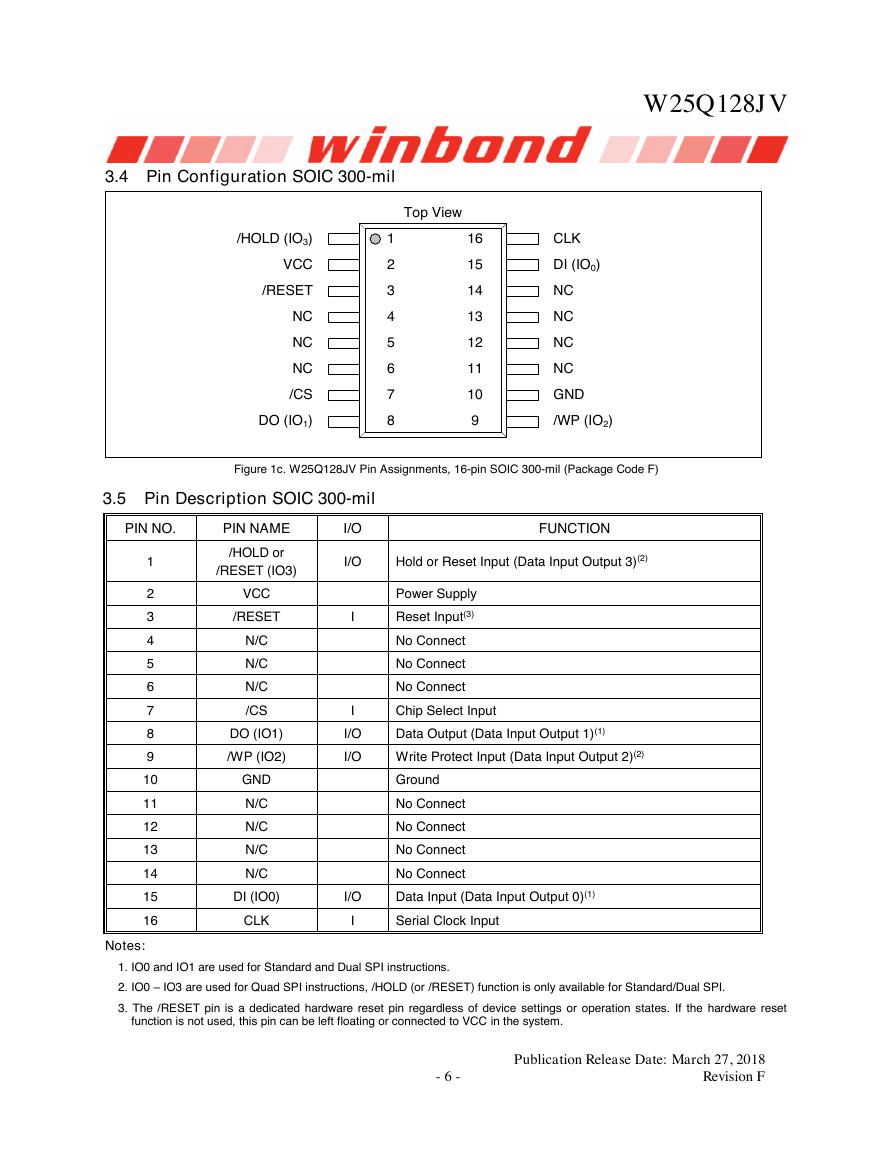

3.4 Pin Configuration SOIC 300-mil

3.5 Pin Description SOIC 300-mil

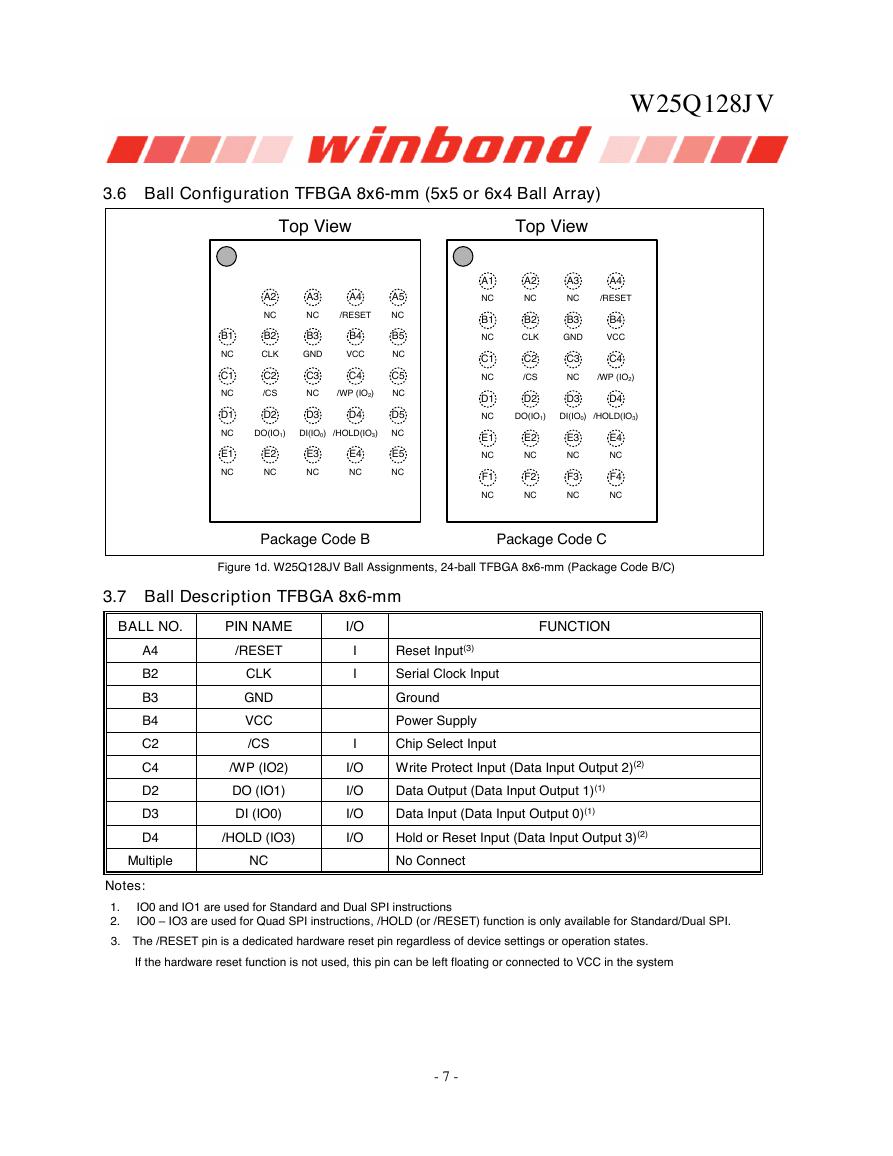

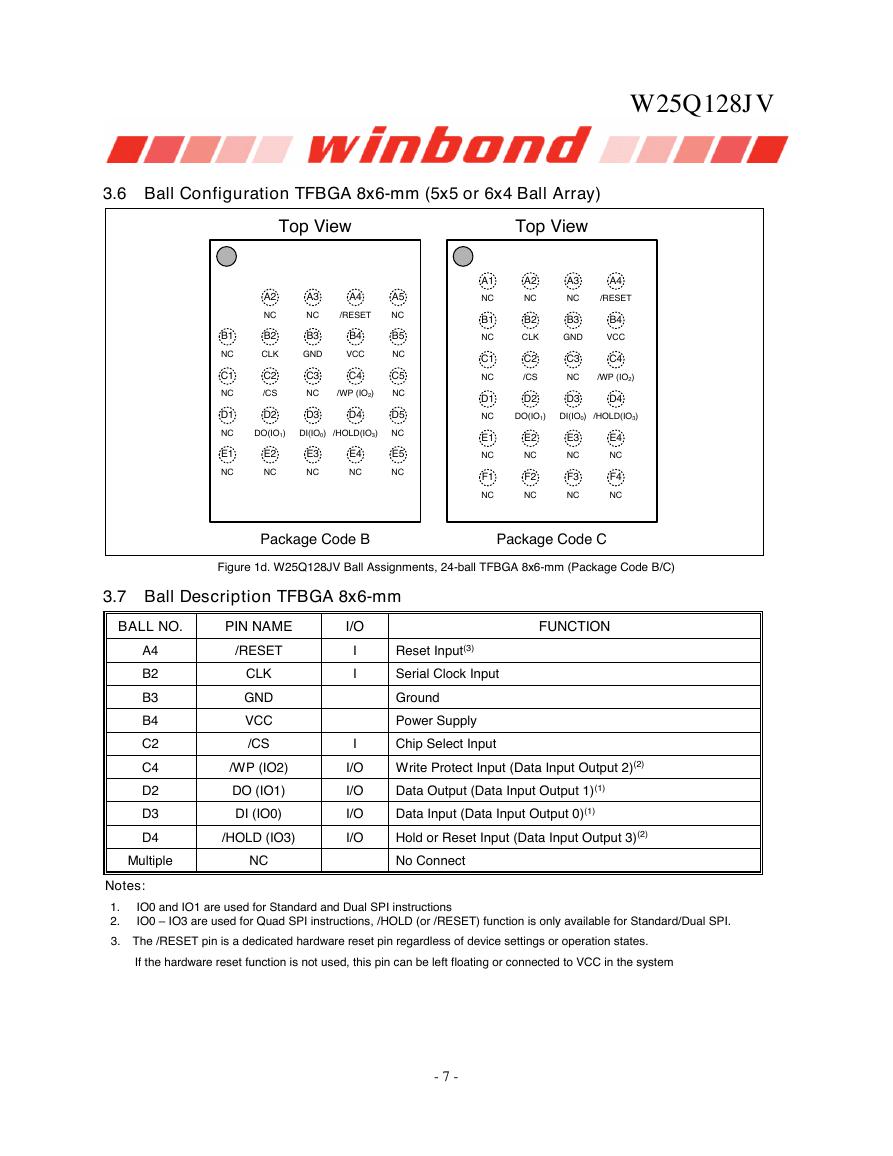

3.6 Ball Configuration TFBGA 8x6-mm (5x5 or 6x4 Ball Array)

3.7 Ball Description TFBGA 8x6-mm

3.8 Ball Configuration WLCSP

3.9 Ball Description WLCSP24

4. pin descriptions

4.1 Chip Select (/CS)

4.2 Serial Data Input, Output and IOs (DI, DO and IO0, IO1, IO2, IO3)

4.3 Write Protect (/WP)

4.4 HOLD (/HOLD)

4.5 Serial Clock (CLK)

4.6 Reset (/RESET)

5. Block Diagram

6. Functional Descriptions

6.1 Standard SPI Instructions

6.2 Dual SPI Instructions

6.3 Quad SPI Instructions

6.4 Software Reset & Hardware /RESET pin

6.5 Write Protection

6.5.1 Write Protect Features

7. Status and configuration Registers

7.1 Status Registers

7.1.1 Erase/Write In Progress (BUSY) – Status Only

7.1.2 Write Enable Latch (WEL) – Status Only

7.1.3 Block Protect Bits (BP2, BP1, BP0) – Volatile/Non-Volatile Writable

7.1.4 Top/Bottom Block Protect (TB) – Volatile/Non-Volatile Writable

7.1.5 Sector/Block Protect Bit (SEC) – Volatile/Non-Volatile Writable

7.1.6 Complement Protect (CMP) – Volatile/Non-Volatile Writable

7.1.1 Status Register Protect (SRP, SRL) – Volatile/Non-Volatile Writable

7.1.2 Erase/Program Suspend Status (SUS) – Status Only

7.1.3 Security Register Lock Bits (LB3, LB2, LB1) – Volatile/Non-Volatile OTP Writable

7.1.4 Quad Enable (QE) – Volatile/Non-Volatile Writable

7.1.5 Write Protect Selection (WPS) – Volatile/Non-Volatile Writable

7.1.6 Output Driver Strength (DRV1, DRV0) – Volatile/Non-Volatile Writable

7.1.7 Reserved Bits – Non Functional

7.1.8 W25Q128JV Status Register Memory Protection (WPS = 0, CMP = 0)

7.1.9 W25Q128JV Status Register Memory Protection (WPS = 0, CMP = 1)

7.1.10 W25Q128JV Individual Block Memory Protection (WPS=1)

8. INSTRUCTIONS

8.1 Device ID and Instruction Set Tables

8.1.1 Manufacturer and Device Identification

8.1.2 Instruction Set Table 1 (Standard SPI Instructions)(1)

8.1.3 Instruction Set Table 2 (Dual/Quad SPI Instructions)

Notes:

8.2 Instruction Descriptions

8.2.1 Write Enable (06h)

8.2.2 Write Enable for Volatile Status Register (50h)

8.2.3 Write Disable (04h)

8.2.4 Read Status Register-1 (05h), Status Register-2 (35h) & Status Register-3 (15h)

8.2.5 Write Status Register-1 (01h), Status Register-2 (31h) & Status Register-3 (11h)

8.2.6 Read Data (03h)

8.2.7 Fast Read (0Bh)

8.2.8 Fast Read Dual Output (3Bh)

8.2.9 Fast Read Quad Output (6Bh)

8.2.10 Fast Read Dual I/O (BBh)

8.2.11 Fast Read Quad I/O (EBh)

8.2.12 Set Burst with Wrap (77h)

8.2.13 Page Program (02h)

8.2.14 Quad Input Page Program (32h)

8.2.15 Sector Erase (20h)

8.2.16 32KB Block Erase (52h)

8.2.17 64KB Block Erase (D8h)

8.2.18 Chip Erase (C7h / 60h)

8.2.19 Erase / Program Suspend (75h)

8.2.20 Erase / Program Resume (7Ah)

8.2.21 Power-down (B9h)

8.2.22 Release Power-down / Device ID (ABh)

8.2.23 Read Manufacturer / Device ID (90h)

8.2.24 Read Manufacturer / Device ID Dual I/O (92h)

8.2.25 Read Manufacturer / Device ID Quad I/O (94h)

8.2.26 Read Unique ID Number (4Bh)

8.2.27 Read JEDEC ID (9Fh)

8.2.28 Read SFDP Register (5Ah)

8.2.29 Erase Security Registers (44h)

8.2.30 Program Security Registers (42h)

8.2.31 Read Security Registers (48h)

8.2.32 Individual Block/Sector Lock (36h)

8.2.33 Individual Block/Sector Unlock (39h)

8.2.34 Read Block/Sector Lock (3Dh)

8.2.35 Global Block/Sector Lock (7Eh)

8.2.36 Global Block/Sector Unlock (98h)

8.2.37 Enable Reset (66h) and Reset Device (99h)

9. Electrical CharacteristicS

9.1 Absolute Maximum Ratings (1)

9.2 Operating Ranges

9.3 Power-Up Power-Down Timing and Requirements

9.4 DC Electrical Characteristics-

9.5 AC Measurement Conditions

9.6 AC Electrical Characteristics(6)

9.7 Serial Output Timing

9.8 Serial Input Timing

9.9 /WP Timing

10. PACKAGE SPECIFICATIONs

10.1 8-Pin SOIC 208-mil (Package Code S)

10.2 16-Pin SOIC 300-mil (Package Code F)

10.3 8-Pad WSON 6x5-mm (Package Code P)

10.4 8-Pad WSON 8x6-mm (Package Code E)

10.5 24-Ball TFBGA 8x6-mm (Package Code B, 5x5-1 ball array)

10.6 24-Ball TFBGA 8x6-mm (Package Code C, 6x4 ball array)

10.7 24-Ball WLCSP (Package Code Y)

11. Ordering Information

11.1 Valid Part Numbers and Top Side Marking

12. Revision history

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf