Verilog-A

Language Reference Manual

Analog Extensions to Verilog HDL

Version 1.0

August 1, 1996

Open Verilog International

�

No part of this work covered by the copyright hereon may be reproduced or used in any form or by any means --

- graphic, electronic, or mechanical, including photocopying, recording, taping, or information storage and

retrieval systems --- without the prior written approval of Open Verilog International.

Additional copies of this manual may be purchased by contacting Open Verilog International at the address

shown below.

Notices

The information contained in this draft manual represents the definition of the Verilog-A hardware description

language as proposed by OVI (Analog TSC) as of January, 1996. Open Verilog International makes no warran-

ties whatsoever with respect to the completeness, accuracy, or applicability of the information in this draft man-

ual to a user’s requirements. This language is not yet fully defined and is subject to change. It is suitable for

learning how to do analog modeling and as a vehicle for providing feedback to the standards committee. Verilog-

A should not be used for production design and development.

Open Verilog International reserves the right to make changes to the Verilog-A hardware description language

and this manual at any time without notice.

Open Verilog International does not endorse any particular simulator or other CAE tool that is based on the Ver-

ilog-A hardware description language.

Suggestions for improvements to the Verilog hardware description language and/or to this manual are welcome.

They should be sent to the address below.

Information about Open Verilog International and membership enrollment can be obtained by inquiring at the

address below.

Published as:

Verilog-A Language Reference Manual

Version 1.0, August 1, 1996.

Published by:

Open Verilog International

15466 Los Gatos Blvd., #109071

Los Gatos, CA 95032

Phone: (408) 358-9510

Fax: (408) 358-3910

Printed in the United States of America.

Verilog® is a registered trademark of Cadence Design Systems, Inc.

�

The following people contributed to the creation, editing and review of this document.

Ramana Aisola

Kevin Cameron

Dan FitzPatrick

Vassilios Gerousis

Ian Getreu

Kim Hailey

Ken Kundert

Motorola

aisola@analog-dse.sps.mot.com

Meta-Software

kevinc@metasw.com

Apteq

Motorola

Analogy

dkf@apteq.com

gerousis@chdasic.sps.mot.com

iang@analogy.com

Meta Software

kimh@metasw.com

Cadence

kundert@cadence.com

Oskar Leuthold

GEC Plessy

leuthold@sv.gpsemi.com

S. Peter Liebmann

Meta Software

peterl@metasw.com

Ira Miller

Tom Reeder

Motorola

Viewlogic

miller@analog-dse.sps.mot.com

treeder@viewlogic.com

Steffen Rochel

Anacad/Mentor

steffen_rochel@mentorg.com

James Spoto

Richard Trihy

Yatin Trivedi

Cadence

Cadence

spoto@cadence.com

trihy@cadence.com

SEVA Technologies

trivedi@seva.com

Alex Zamfirescu

Veribest

a.zamfirescu@ieee.org

�

�

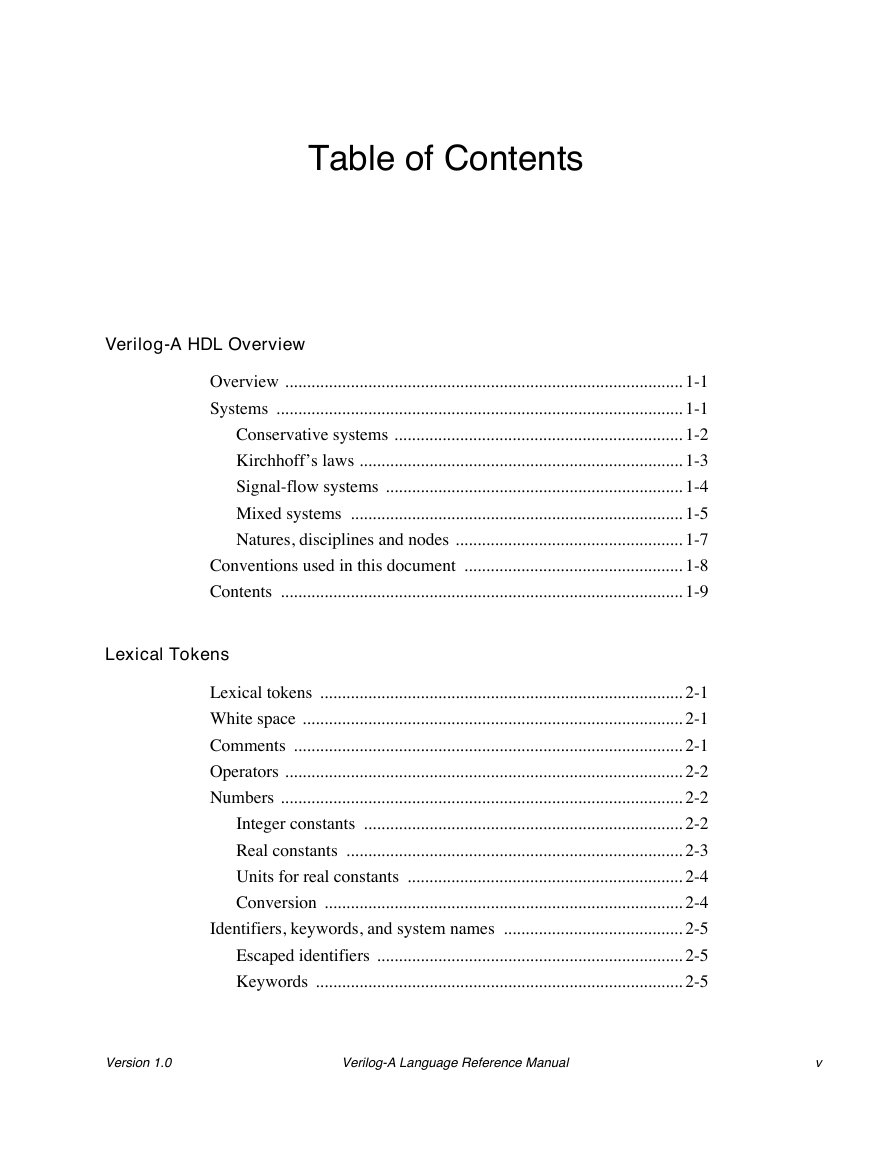

Table of Contents

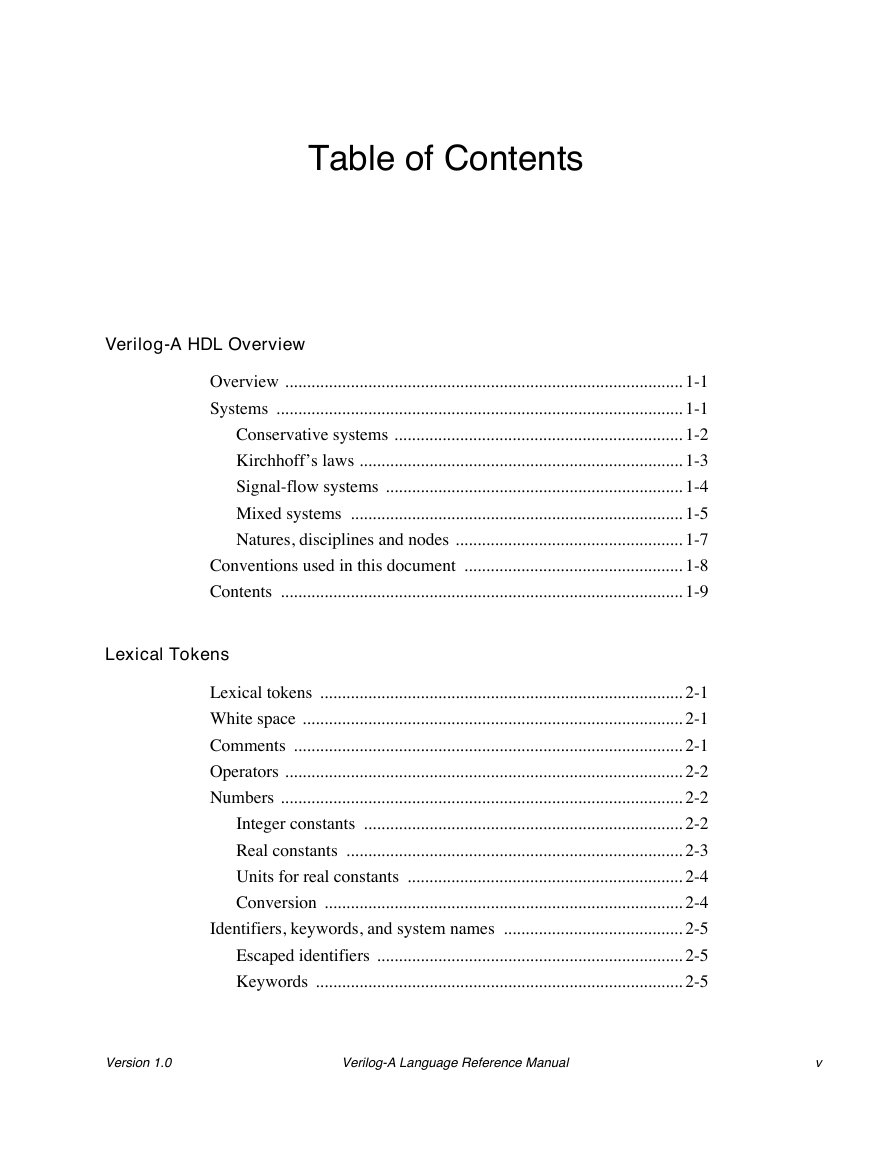

Verilog-A HDL Overview

Overview ........................................................................................... 1-1

Systems ............................................................................................. 1-1

Conservative systems .................................................................. 1-2

Kirchhoff’s laws .......................................................................... 1-3

Signal-flow systems .................................................................... 1-4

Mixed systems ............................................................................ 1-5

Natures, disciplines and nodes .................................................... 1-7

Conventions used in this document .................................................. 1-8

Contents ............................................................................................ 1-9

Lexical Tokens

Lexical tokens ................................................................................... 2-1

White space ....................................................................................... 2-1

Comments ......................................................................................... 2-1

Operators ........................................................................................... 2-2

Numbers ............................................................................................ 2-2

Integer constants ......................................................................... 2-2

Real constants ............................................................................. 2-3

Units for real constants ............................................................... 2-4

Conversion .................................................................................. 2-4

Identifiers, keywords, and system names ......................................... 2-5

Escaped identifiers ...................................................................... 2-5

Keywords .................................................................................... 2-5

Version 1.0

Verilog-A Language Reference Manual

v

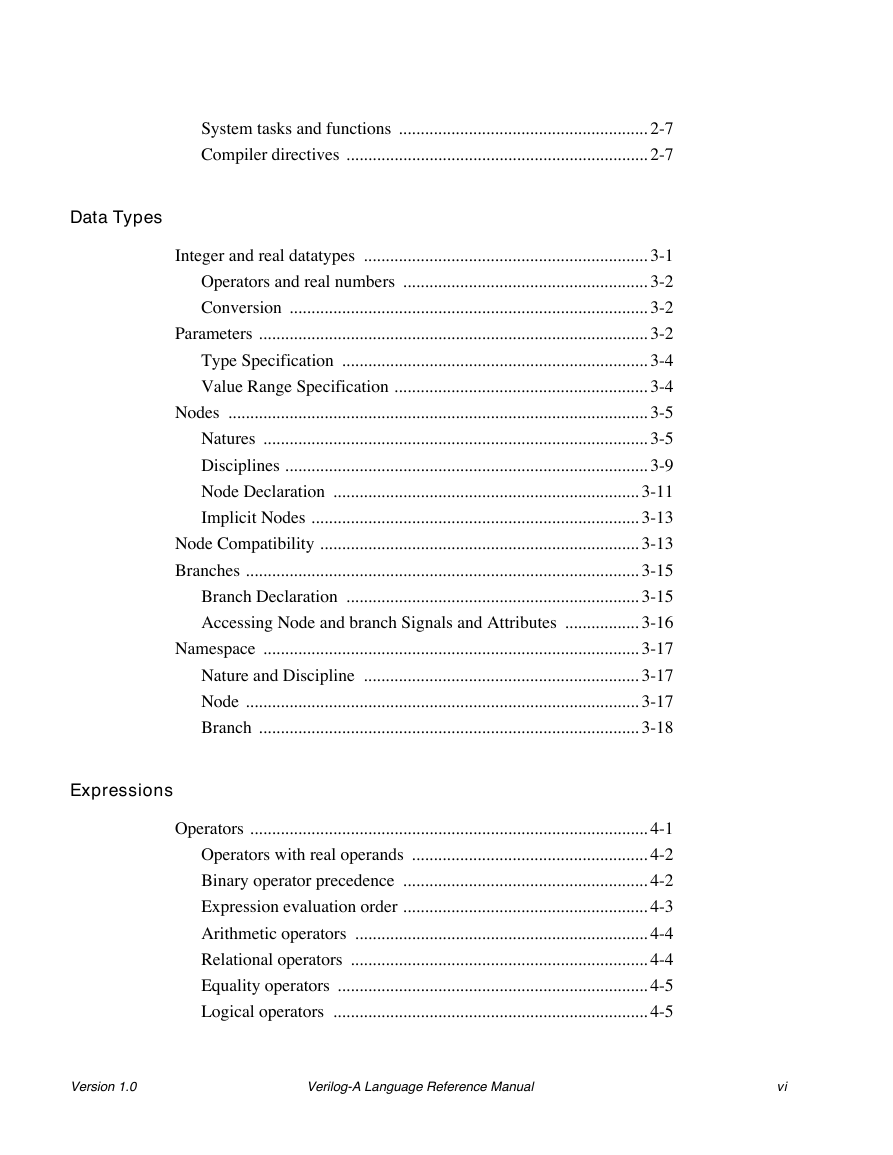

�

Data Types

Expressions

System tasks and functions ......................................................... 2-7

Compiler directives ..................................................................... 2-7

Integer and real datatypes ................................................................. 3-1

Operators and real numbers ........................................................ 3-2

Conversion .................................................................................. 3-2

Parameters ......................................................................................... 3-2

Type Specification ...................................................................... 3-4

Value Range Specification .......................................................... 3-4

Nodes ................................................................................................ 3-5

Natures ........................................................................................ 3-5

Disciplines ................................................................................... 3-9

Node Declaration ...................................................................... 3-11

Implicit Nodes ........................................................................... 3-13

Node Compatibility ......................................................................... 3-13

Branches .......................................................................................... 3-15

Branch Declaration ................................................................... 3-15

Accessing Node and branch Signals and Attributes ................. 3-16

Namespace ...................................................................................... 3-17

Nature and Discipline ............................................................... 3-17

Node .......................................................................................... 3-17

Branch ....................................................................................... 3-18

Operators ........................................................................................... 4-1

Operators with real operands ...................................................... 4-2

Binary operator precedence ........................................................ 4-2

Expression evaluation order ........................................................ 4-3

Arithmetic operators ................................................................... 4-4

Relational operators .................................................................... 4-4

Equality operators ....................................................................... 4-5

Logical operators ........................................................................ 4-5

Version 1.0

Verilog-A Language Reference Manual

vi

�

Bit-wise operators ....................................................................... 4-6

Shift operators ............................................................................. 4-7

Conditional operator ................................................................... 4-7

Event or ....................................................................................... 4-7

Built-In Mathematical Functions ...................................................... 4-7

Standard Mathematical Functions ............................................... 4-8

Transcendental Functions ........................................................... 4-8

Environment Parameters ............................................................. 4-9

Error Handling ............................................................................ 4-9

Signal Access Functions ................................................................... 4-9

Analog Operators ............................................................................ 4-10

Restrictions on analog operators ............................................... 4-11

Analog Operators and Tolerances ............................................. 4-11

Time Derivative Operator ......................................................... 4-11

Time Integral Operator ............................................................. 4-12

Delay Operator .......................................................................... 4-13

Transition Filter ........................................................................ 4-13

Slew Filter ................................................................................. 4-16

Laplace Transform Filters ......................................................... 4-17

Z-Transform Filters ................................................................... 4-19

Limited Exponential .................................................................. 4-22

Analysis Dependent Functions ....................................................... 4-22

Analysis ..................................................................................... 4-22

AC Stimulus .............................................................................. 4-23

Noise ......................................................................................... 4-24

User defined functions .................................................................... 4-25

Defining a function ................................................................... 4-25

Returning a value from a function ............................................ 4-27

Calling a function ...................................................................... 4-27

Signals

Analog Signals .................................................................................. 5-1

Access Functions ........................................................................ 5-1

Probes and Sources ..................................................................... 5-2

Version 1.0

Verilog-A Language Reference Manual

vii

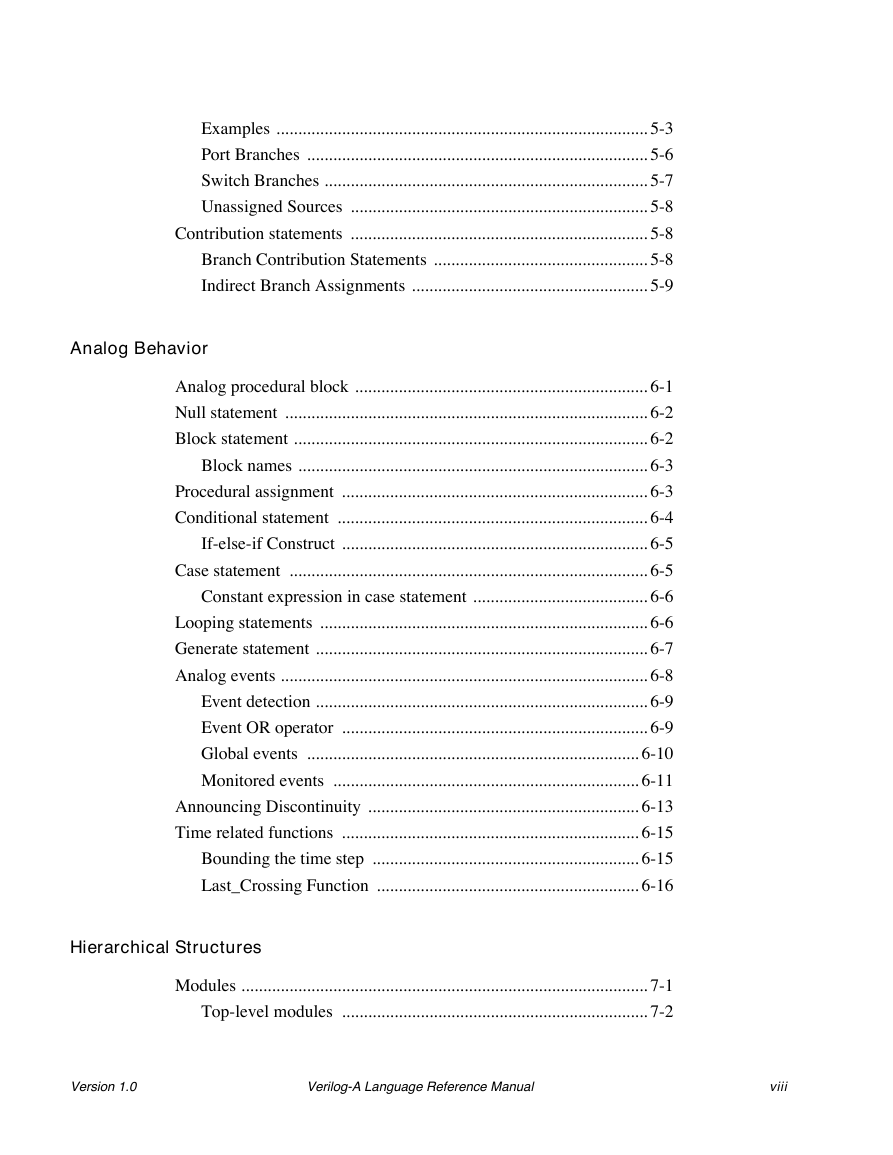

�

Examples ..................................................................................... 5-3

Port Branches .............................................................................. 5-6

Switch Branches .......................................................................... 5-7

Unassigned Sources .................................................................... 5-8

Contribution statements .................................................................... 5-8

Branch Contribution Statements ................................................. 5-8

Indirect Branch Assignments ...................................................... 5-9

Analog Behavior

Analog procedural block ................................................................... 6-1

Null statement ................................................................................... 6-2

Block statement ................................................................................. 6-2

Block names ................................................................................ 6-3

Procedural assignment ...................................................................... 6-3

Conditional statement ....................................................................... 6-4

If-else-if Construct ...................................................................... 6-5

Case statement .................................................................................. 6-5

Constant expression in case statement ........................................ 6-6

Looping statements ........................................................................... 6-6

Generate statement ............................................................................ 6-7

Analog events .................................................................................... 6-8

Event detection ............................................................................ 6-9

Event OR operator ...................................................................... 6-9

Global events ............................................................................ 6-10

Monitored events ...................................................................... 6-11

Announcing Discontinuity .............................................................. 6-13

Time related functions .................................................................... 6-15

Bounding the time step ............................................................. 6-15

Last_Crossing Function ............................................................ 6-16

Hierarchical Structures

Modules ............................................................................................. 7-1

Top-level modules ...................................................................... 7-2

Version 1.0

Verilog-A Language Reference Manual

viii

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc