技

术

创

新

嵌 入 式 与 SOC

文章编号:1008-0570(2012)10-0196-03

《微计算机信息》2012 年第 28 卷第 10 期

基于 FPGA 的实时图像中值滤波算法及实现

Real-image Median Filtering algorithm and Realization Based on FPGA

(杭州电子科技大学)

蒋 涛 李 自 勤

JIANG Tao LI Zi-qin

摘要: 在 数 字 图 像 处 理 中 , 传 统 中 值 滤 波 运 算 量 大 , 特 别 是 当 滤 波 窗 口 变 大 时 , 运 算 量 成 倍 增 加 , 难 以 满 足 实 时 性 要 求 。 本 文 提

出 一 种 5×5 窗 口 的 快 速 中 值 滤 波 算 法 , 易 于 使 用 现 场 可 编 程 门 阵 列 (FPGA) 实 现 。 相 对 于 传 统 的 算 法 , 不 但 比 较 次 数 得 到 了 大

幅 度 的 减 少 , 而 且 利 用 FPGA 并 行 处 理 的 特 点 , 处 理 速 度 也 得 到 了 提 高 。 以 分 辨 率 为 640×480 的 CMOS 摄 像 头 采 集 图 像 为 实

验 对 象 , 在 硬 件 平 台 上 验 证 算 法 的 可 行 性 , 并 且 具 有 良 好 的 滤 波 效 果 。

关键词: 实时图像处理; 中值滤波; FPGA; 并行处理

中图分类号: TP911.73

文献标识码: A

Abstract: In digital image processing, the conventional median filtering can not meet the requirements of real -time, especially, when

the filtering window is larger, the computational complexity increases more exponentially. In this paper, a kind of fast median filtering

algorithm is proposed for using FPGA to implement. There was a greatly improved in the processing speed, compared with the con-

ventional median filtering. The experimental results on filtering of 640 × 480 images show that the algorithm is viable in the hard-

ware platform of FPGA.

Key words: real-image processing; median filter; FPGA; parallel processing

1 引 言

数字图像处理中, 中值滤波因其与输入信号序列的映射关

系,在去除脉冲噪声上有比较好的效果,很多学者针对中值滤波

技术进行研究, 提出了很多改进算法。现场可编程逻辑门阵列

(Field Programmable Gate Arrays,FPGA) 技术在数字信号处理中

的应用,将逐渐成为前端信号处理的主流。本文论述了一种实时

图像中值滤波算法的基本原理以及采用 Altera 公司的 Cyclone

Ⅱ系列 FPGA 具体实现方法。

2 中 值 滤 波 原 理

2.1 传统中值滤波

传统中值滤波可以用公式表示为:

和

其中:

分别为输入和输出像素的灰度值,S 为

模板窗口。传统中值滤波要对模板窗口内的所有像素之间进行

比较排序,最后找到中值作为输出结果。对于一个 N×N 大小的

窗口,按照冒泡排序查找中值需要进行

次比较。对

于一幅 512×512 大小的图像,采用 5×5 窗口,整个滤波过程需要

7500 万次的比较。因此传统中值滤波运算量较大,很难满足实

时性要求。

2.2 快速中值滤波

针对传统中值滤波无法在图像预处理里中满足实时性要

求,文献[3]中提到的快速滤波算法,对 3×3 窗口采用不完全排序,

经过 16 次的比较找出 3×3 窗口内 9 个灰度值的中值,而且更适

合于 FPGA 硬件平台。考虑到随着图像尺寸越来越大,和更好的

滤除噪声,大窗口滤波越来越体现出它的优势,本文在此基础上,

蒋 涛: 硕士研究生

-

196

-

120 元 / 年 邮局订阅号:82-946

提出 5×5 窗口的快速中值滤波算法。

在噪声系数较高的图像中, 采用 3×3 窗口并不能很好的完

成滤波任务。表 1 是对一幅 1024×1024 大小的图像加不同程度

的噪声后,滤波结果的客观评价。峰值信噪比(PSNR)是最普遍的

图像画质的客观测量方法,可以看出,噪声系数越高,采用 5×5 窗

口滤波越有优势。实际上用视觉主观判断也很容易发现 5×5 窗

口滤波后的效果更好。

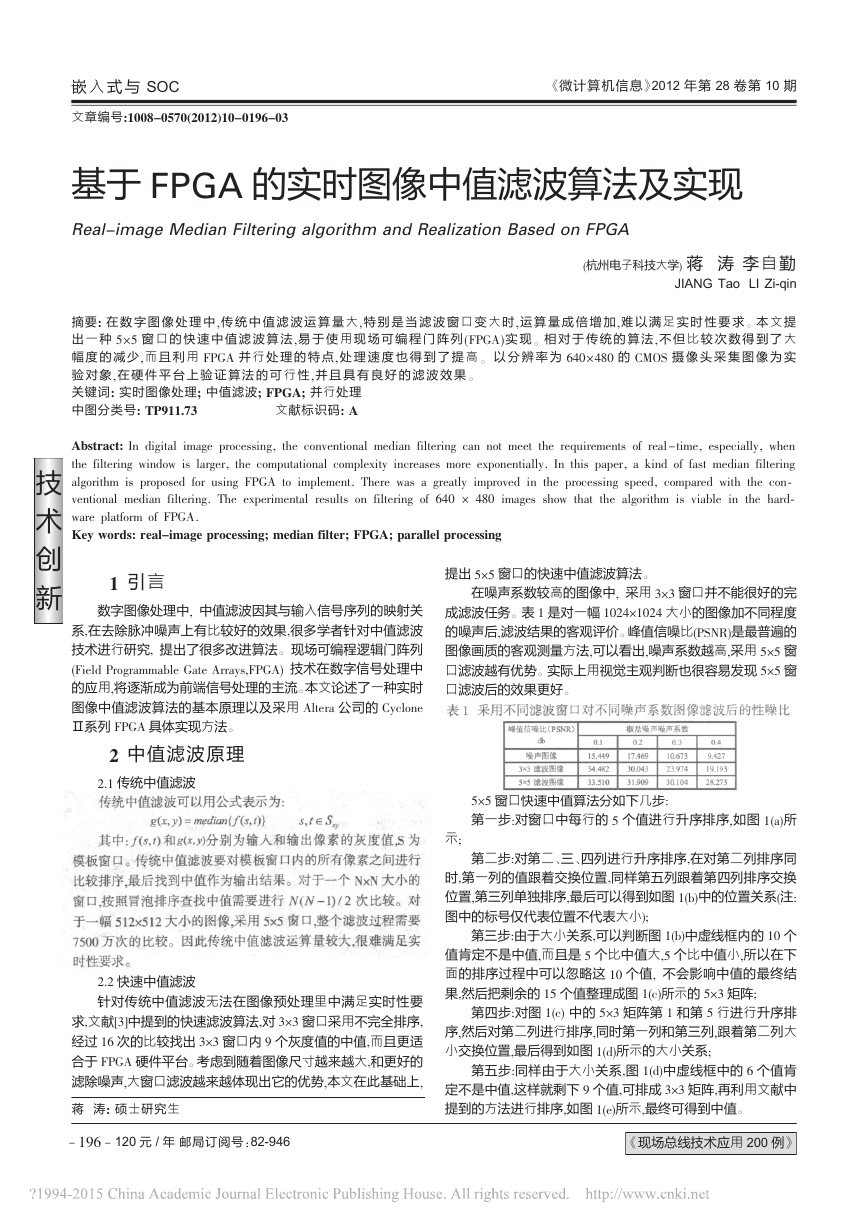

表 1 采用不同滤波窗口对不同噪声系数图像滤波后的性噪比

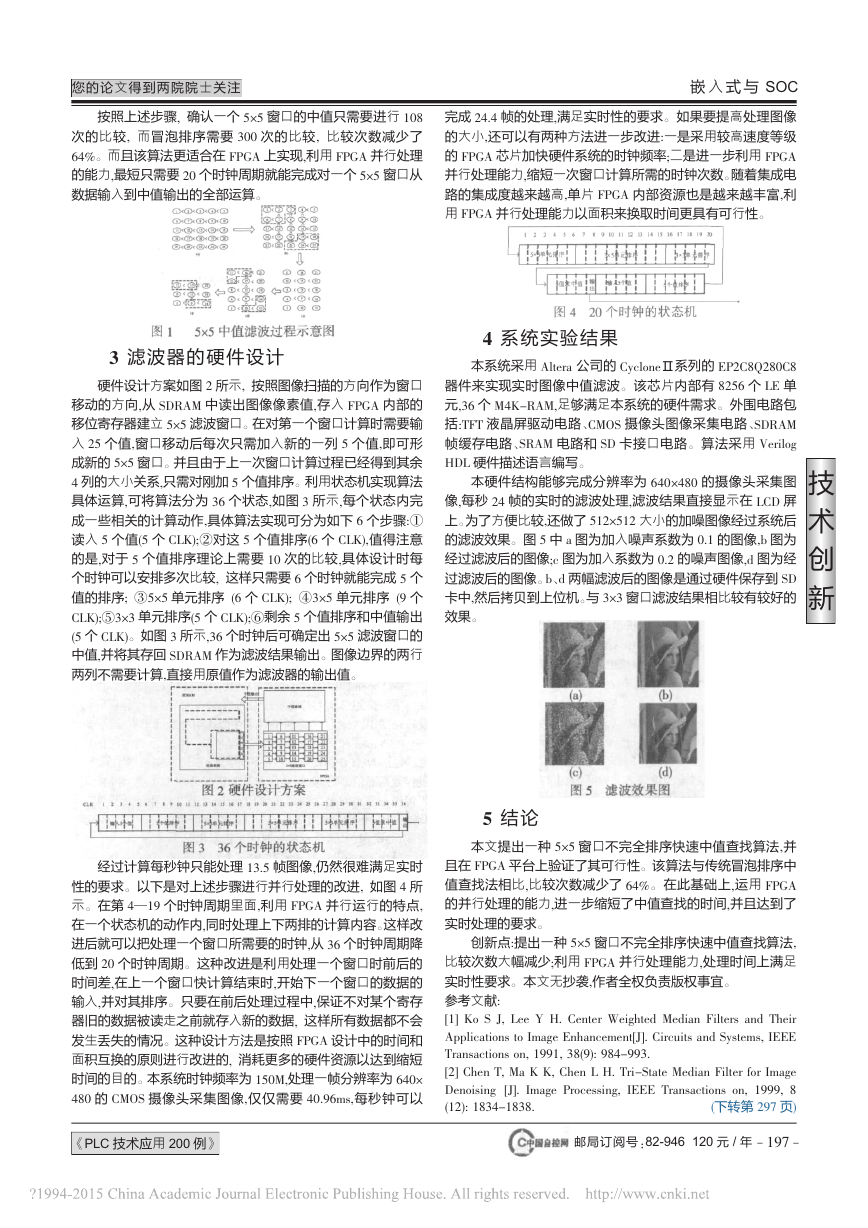

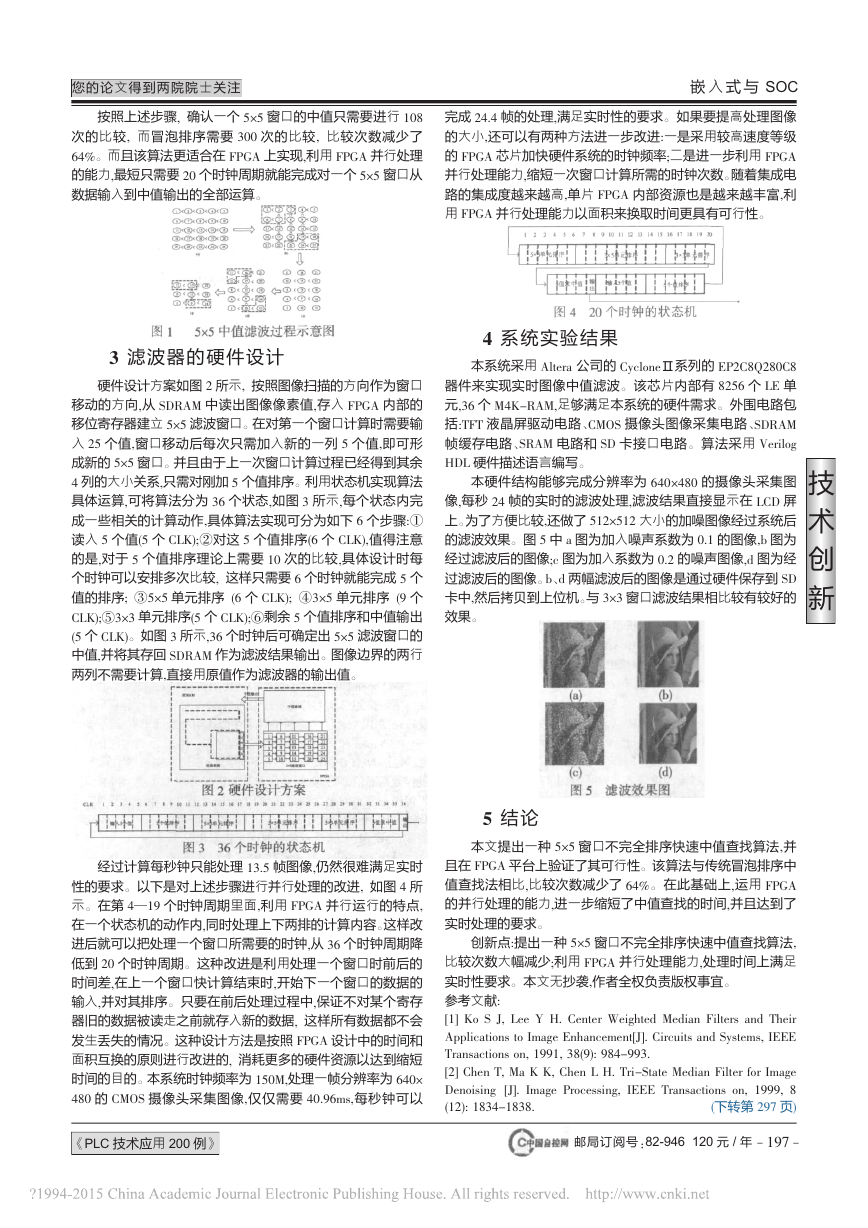

5×5 窗口快速中值算法分如下几步:

第一步:对窗口中每行的 5 个值进行升序排序,如图 1(a)所

示;

第二步:对第二、三、四列进行升序排序,在对第二列排序同

时,第一列的值跟着交换位置,同样第五列跟着第四列排序交换

位置,第三列单独排序,最后可以得到如图 1(b)中的位置关系(注:

图中的标号仅代表位置不代表大小);

第三步:由于大小关系,可以判断图 1(b)中虚线框内的 10 个

值肯定不是中值,而且是 5 个比中值大,5 个比中值小,所以在下

面的排序过程中可以忽略这 10 个值, 不会影响中值的最终结

果,然后把剩余的 15 个值整理成图 1(c)所示的 5×3 矩阵;

第四步:对图 1(c) 中的 5×3 矩阵第 1 和第 5 行进行升序排

序,然后对第二列进行排序,同时第一列和第三列,跟着第二列大

小交换位置,最后得到如图 1(d)所示的大小关系;

第五步:同样由于大小关系,图 1(d)中虚线框中的 6 个值肯

定不是中值,这样就剩下 9 个值,可排成 3×3 矩阵,再利用文献中

提到的方法进行排序,如图 1(e)所示,最终可得到中值。

《现场总线技术应用 200 例》

�

您的论文得到两院院士关注

按照上述步骤, 确认一个 5×5 窗口的中值只需要进行 108

次的比较, 而冒泡排序需要 300 次的比较, 比较次数减少了

64%。而且该算法更适合在 FPGA 上实现,利用 FPGA 并行处理

的能力,最短只需要 20 个时钟周期就能完成对一个 5×5 窗口从

数据输入到中值输出的全部运算。

嵌 入 式 与 SOC

完成 24.4 帧的处理,满足实时性的要求。如果要提高处理图像

的大小,还可以有两种方法进一步改进:一是采用较高速度等级

的 FPGA 芯片加快硬件系统的时钟频率;二是进一步利用 FPGA

并行处理能力,缩短一次窗口计算所需的时钟次数。随着集成电

路的集成度越来越高,单片 FPGA 内部资源也是越来越丰富,利

用 FPGA 并行处理能力以面积来换取时间更具有可行性。

图 1

5×5 中值滤波过程示意图

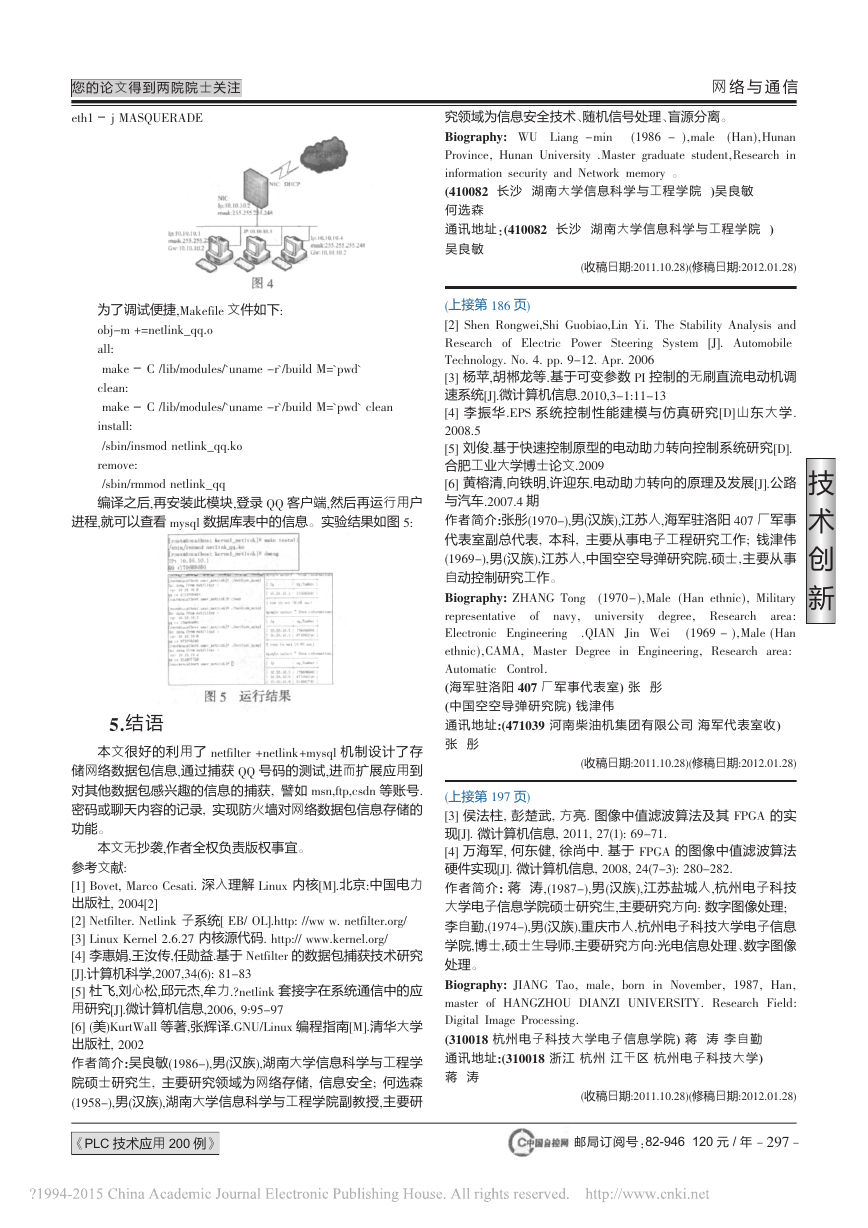

3 滤 波 器 的 硬 件 设 计

硬件设计方案如图 2 所示, 按照图像扫描的方向作为窗口

移动的方向,从 SDRAM 中读出图像像素值,存入 FPGA 内部的

移位寄存器建立 5×5 滤波窗口。在对第一个窗口计算时需要输

入 25 个值,窗口移动后每次只需加入新的一列 5 个值,即可形

成新的 5×5 窗口。并且由于上一次窗口计算过程已经得到其余

4 列的大小关系,只需对刚加 5 个值排序。利用状态机实现算法

具体运算,可将算法分为 36 个状态,如图 3 所示,每个状态内完

成一些相关的计算动作,具体算法实现可分为如下 6 个步骤:①

读入 5 个值(5 个 CLK);②对这 5 个值排序(6 个 CLK),值得注意

的是,对于 5 个值排序理论上需要 10 次的比较,具体设计时每

个时钟可以安排多次比较, 这样只需要 6 个时钟就能完成 5 个

值的排序; ③5×5 单元排序 (6 个 CLK); ④3×5 单元排序 (9 个

CLK);⑤3×3 单元排序(5 个 CLK);⑥剩余 5 个值排序和中值输出

(5 个 CLK)。如图 3 所示,36 个时钟后可确定出 5×5 滤波窗口的

中值,并将其存回 SDRAM 作为滤波结果输出。图像边界的两行

两列不需要计算,直接用原值作为滤波器的输出值。

图 2 硬件设计方案

图 3 36 个时钟的状态机

经过计算每秒钟只能处理 13.5 帧图像,仍然很难满足实时

性的要求。以下是对上述步骤进行并行处理的改进, 如图 4 所

示。在第 4—19 个时钟周期里面,利用 FPGA 并行运行的特点,

在一个状态机的动作内,同时处理上下两排的计算内容。这样改

进后就可以把处理一个窗口所需要的时钟,从 36 个时钟周期降

低到 20 个时钟周期。这种改进是利用处理一个窗口时前后的

时间差,在上一个窗口快计算结束时,开始下一个窗口的数据的

输入,并对其排序。只要在前后处理过程中,保证不对某个寄存

器旧的数据被读走之前就存入新的数据, 这样所有数据都不会

发生丢失的情况。这种设计方法是按照 FPGA 设计中的时间和

面积互换的原则进行改进的, 消耗更多的硬件资源以达到缩短

时间的目的。本系统时钟频率为 150M,处理一帧分辨率为 640×

480 的 CMOS 摄像头采集图像,仅仅需要 40.96ms,每秒钟可以

图 4 20 个时钟的状态机

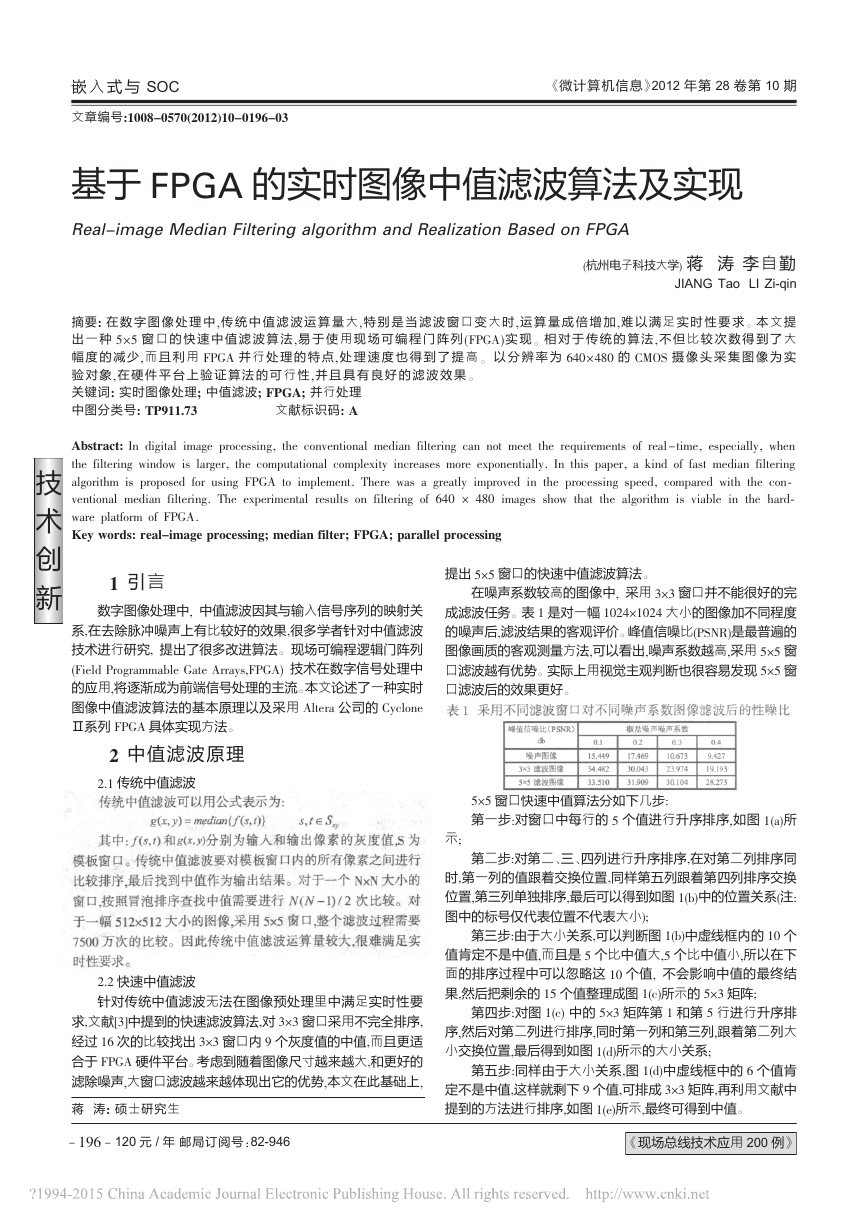

4 系 统 实 验 结 果

本系统采用 Altera 公司的 Cyclone

Ⅱ系列的 EP2C8Q280C8

器件来实现实时图像中值滤波。该芯片内部有 8256 个 LE 单

元,36 个 M4K-RAM,足够满足本系统的硬件需求。外围电路包

括:TFT 液晶屏驱动电路、CMOS 摄像头图像采集电路、SDRAM

帧缓存电路、SRAM 电路和 SD 卡接口电路。算法采用 Verilog

HDL 硬件描述语言编写。

本硬件结构能够完成分辨率为 640×480 的摄像头采集图

像,每秒 24 帧的实时的滤波处理,滤波结果直接显示在 LCD 屏

上。为了方便比较,还做了 512×512 大小的加噪图像经过系统后

的滤波效果。图 5 中 a 图为加入噪声系数为 0.1 的图像,b 图为

经过滤波后的图像;c 图为加入系数为 0.2 的噪声图像,d 图为经

过滤波后的图像。b、d 两幅滤波后的图像是通过硬件保存到 SD

卡中,然后拷贝到上位机。与 3×3 窗口滤波结果相比较有较好的

效果。

技

术

创

新

(a)

(b)

(c)

(d)

图 5 滤波效果图

5 结 论

本文提出一种 5×5 窗口不完全排序快速中值查找算法,并

且在 FPGA 平台上验证了其可行性。该算法与传统冒泡排序中

值查找法相比,比较次数减少了 64%。在此基础上,运用 FPGA

的并行处理的能力,进一步缩短了中值查找的时间,并且达到了

实时处理的要求。

创新点:提出一种 5×5 窗口不完全排序快速中值查找算法,

比较次数大幅减少;利用 FPGA 并行处理能力,处理时间上满足

实时性要求。本文无抄袭,作者全权负责版权事宜。

参考文献:

[1] Ko S J, Lee Y H. Center Weighted Median Filters and Their

Applications to Image Enhancement[J]. Circuits and Systems, IEEE

Transactions on, 1991, 38(9): 984-993.

[2] Chen T, Ma K K, Chen L H. Tri-State Median Filter for Image

Denoising [J]. Image Processing, IEEE Transactions on, 1999, 8

(下转第 297 页)

(12): 1834-1838.

《PLC 技术应用 200 例》

邮局订阅号:82-946 120 元 / 年

-

197

-

�

您的论文得到两院院士关注

eth1 –j MASQUERADE

图 4

为了调试便捷,Makefile 文件如下:

obj-m +=netlink_qq.o

all:

make –C /lib/modules/`uname -r`/build M=`pwd`

clean:

make –C /lib/modules/`uname -r`/build M=`pwd` clean

install:

/sbin/insmod netlink_qq.ko

remove:

/sbin/rmmod netlink_qq

编译之后,再安装此模块,登录 QQ 客户端,然后再运行用户

进程,就可以查看 mysql 数据库表中的信息。实验结果如图 5:

图 5 运行结果

5.结 语

本文很好的利用了 netfilter +netlink+mysql 机制设计了存

储网络数据包信息,通过捕获 QQ 号码的测试,进而扩展应用到

对其他数据包感兴趣的信息的捕获, 譬如 msn,ftp,csdn 等账号.

密码或聊天内容的记录, 实现防火墙对网络数据包信息存储的

功能。

本文无抄袭,作者全权负责版权事宜。

参考文献:

[1] Bovet, Marco Cesati. 深入理解 Linux 内核[M].北京:中国电力

出版社, 2004[2]

[2] Netfilter. Netlink 子系统[ EB/ OL].http: //ww w. netfilter.org/

[3] Linux Kernel 2.6.27 内核源代码. http:// www.kernel.org/

[4] 李惠娟,王汝传,任勋益.基于 Netfilter 的数据包捕获技术研究

[J].计算机科学,2007,34(6): 81-83

[5] 杜飞,刘心松,邱元杰,牟力.?netlink 套接字在系统通信中的应

用研究[J].微计算机信息,2006, 9:95-97

[6] (美)KurtWall 等著,张辉译.GNU/Linux 编程指南[M].清华大学

出版社, 2002

作者 简 介:吴良敏(1986-),男(汉族),湖南大学信息科学与工程学

院硕士研究生, 主要研究领域为网络存储, 信息安全; 何选森

(1958-),男(汉族),湖南大学信息科学与工程学院副教授,主要研

网 络 与 通 信

(1986 - ),male

究领域为信息安全技术、随机信号处理、盲源分离。

Biography: WU Liang -min

(Han),Hunan

Province, Hunan University .Master graduate student,Research in

information security and Network memory 。

(410082 长沙 湖南大学信息科学与工程学院 )吴良敏

何选森

通讯地址:(410082 长沙 湖南大学信息科学与工程学院 )

吴良敏

(收稿日期:2011.10.28)(修稿日期:2012.01.28)

(上接第 186 页)

[2] Shen Rongwei,Shi Guobiao,Lin Yi. The Stability Analysis and

Research of Electric Power Steering System [J]. Automobile

Technology. No. 4. pp. 9-12. Apr. 2006

[3] 杨苹,胡郴龙等.基于可变参数 PI 控制的无刷直流电动机调

速系统[J].微计算机信息.2010,3-1:11-13

[4] 李振华.EPS 系统控制性能建模与仿真研究 [D]山东大学 .

2008.5

[5] 刘俊.基于快速控制原型的电动助力转向控制系统研究[D].

合肥工业大学博士论文.2009

[6] 黄榕清,向铁明,许迎东.电动助力转向的原理及发展[J].公路

与汽车.2007.4 期

作者简介:张彤(1970-),男(汉族),江苏人,海军驻洛阳 407 厂军事

代表室副总代表, 本科, 主要从事电子工程研究工作; 钱津伟

(1969-),男(汉族),江苏人,中国空空导弹研究院,硕士,主要从事

自动控制研究工作。

Biography: ZHANG Tong

(1970- ),Male (Han ethnic), Military

representative

navy,

university

area:

Electronic Engineering

(1969 - ),Male (Han

ethnic),CAMA, Master Degree in Engineering, Research area:

Automatic Control.

(海军驻洛阳 407 厂军事代表室) 张 彤

(中国空空导弹研究院) 钱津伟

通讯地址:(471039 河南柴油机集团有限公司 海军代表室收)

张 彤

degree, Research

of

.QIAN Jin Wei

(收稿日期:2011.10.28)(修稿日期:2012.01.28)

(上接第 197 页)

[3] 侯法柱, 彭楚武, 方亮. 图像中值滤波算法及其 FPGA 的实

现[J]. 微计算机信息, 2011, 27(1): 69-71.

[4] 万海军, 何东健, 徐尚中. 基于 FPGA 的图像中值滤波算法

硬件实现[J]. 微计算机信息, 2008, 24(7-3): 280-282.

作 者 简 介: 蒋 涛,(1987-),男(汉族),江苏盐城人,杭州电子科技

大学电子信息学院硕士研究生,主要研究方向: 数字图像处理;

李自勤,(1974-),男(汉族),重庆市人,杭州电子科技大学电子信息

学院,博士,硕士生导师,主要研究方向:光电信息处理、数字图像

处理。

Biography: JIANG Tao, male, born in November, 1987, Han,

master of HANGZHOU DIANZI UNIVERSITY. Research Field:

Digital Image Processing.

(310018 杭州电子科技大学电子信息学院) 蒋 涛 李自勤

通讯地址:(310018 浙江 杭州 江干区 杭州电子科技大学)

蒋 涛

(收稿日期:2011.10.28)(修稿日期:2012.01.28)

《PLC 技术应用 200 例》

邮局订阅号:82-946 120 元 / 年

-

297

-

技

术

创

新

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc