TR6260-S1

DATASHEET

802.11b/g/n Wi-Fi Single Chip

�

Release Notes

Version

Release Notes

V1.0

V2.0

V2.1

release

Update 3.6 chapter

Update pinlist and

package information

Data

2018.10

2018.12

2019.5

�

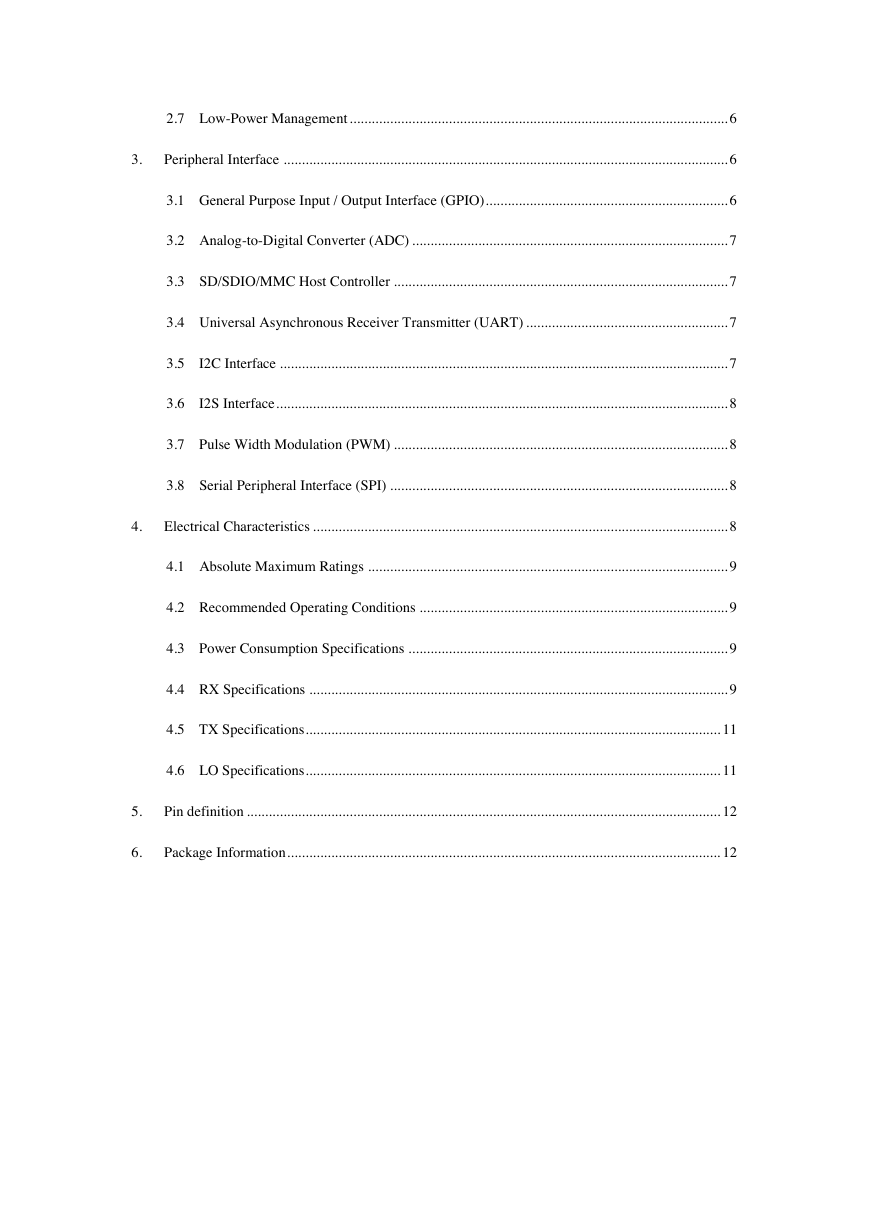

Contents

1. Overview ......................................................................................................................................... 1

1.1 Wi-Fi ...................................................................................................................................... 1

1.2 MCU and Advanced Features ................................................................................................ 1

1.2.1 CPU and Memory ...................................................................................................... 1

1.2.2 Clocks and Timers ..................................................................................................... 2

1.2.3 Advanced Peripheral Interfaces ................................................................................. 2

1.2.4 Security ...................................................................................................................... 2

1.3 Application ............................................................................................................................. 2

2. Block Diagram................................................................................................................................. 3

2.1 Function block diagram ......................................................................................................... 3

2.2 CPU and Memory .................................................................................................................. 3

2.2.1 CPU ........................................................................................................................... 3

2.2.2 Internal Memory ........................................................................................................ 4

2.2.3 External Flash and SRAM ......................................................................................... 4

2.3 Timers and Watchdogs ........................................................................................................... 4

2.3.1 Watchdog Timers ...................................................................................................... 4

2.4 System Clocks ........................................................................................................................ 4

2.4.1 CPU Clock ................................................................................................................. 4

2.4.2 RTC Clock ................................................................................................................. 4

2.5 Radio ...................................................................................................................................... 4

2.5.1 2.4 GHz Receiver ...................................................................................................... 5

2.5.2 2.4 GHz Transmitter .................................................................................................. 5

2.5.3 Clock Generator......................................................................................................... 5

2.6 Wi-Fi ...................................................................................................................................... 5

�

2.7 Low-Power Management ....................................................................................................... 6

3. Peripheral Interface ......................................................................................................................... 6

3.1 General Purpose Input / Output Interface (GPIO) .................................................................. 6

3.2 Analog-to-Digital Converter (ADC) ...................................................................................... 7

3.3 SD/SDIO/MMC Host Controller ........................................................................................... 7

3.4 Universal Asynchronous Receiver Transmitter (UART) ....................................................... 7

3.5 I2C Interface .......................................................................................................................... 7

3.6 I2S Interface ........................................................................................................................... 8

3.7 Pulse Width Modulation (PWM) ........................................................................................... 8

3.8 Serial Peripheral Interface (SPI) ............................................................................................ 8

4. Electrical Characteristics ................................................................................................................. 8

4.1 Absolute Maximum Ratings .................................................................................................. 9

4.2 Recommended Operating Conditions .................................................................................... 9

4.3 Power Consumption Specifications ....................................................................................... 9

4.4 RX Specifications .................................................................................................................. 9

4.5 TX Specifications ................................................................................................................. 11

4.6 LO Specifications ................................................................................................................. 11

5. Pin definition ................................................................................................................................. 12

6. Package Information ...................................................................................................................... 12

�

1. Overview

The SoC is a 2.4GHz IEEE 802.11b/g/n Wi-Fi single chip solution with

standard security features. With optimized power and RF performance,

robustness, versatility, reliability, various power profiles, full features and

functions, the chip is designed for a wide variety of applications, including

Smart home, Wearable devices and IoT (Internet of Things).

It integrates a 32-bit microcontroller, 802.11b/g/n Wi-Fi baseband, a 2.4GHz

RF transceiver with antenna switch, RF balun, PA (power amplifier), LNA

(low noise receive amplifier) and filters, ample memory space, a

general-purpose ADC(Analog-to-Digital Converter), 6-channel PWM(Pulse

Width Modulation),

flexible

I/O

interfaces, and multi-stage power

management module. With

the highly-integrated SoC,

few external

components and minimal PCB(Printed Circuit Board) area are needed to build

Wi-Fi applications.

The SoC has many features of the state-of-the-art low power chips, such as

good resolution clock gating, advanced management of multi-stage power

modes, and dynamic power scaling.

The chip uses CMOS for single-chip fully-integrated radio and Baseband, and

also integrates advanced calibration circuitries that allow the solution to

dynamically adjust itself to remove external circuit imperfections or adjust to

changes in external conditions.

1.1 Wi-Fi

• 802.11 b/g/n/i

• 802.11 n (2.4 GHz), up to 150 Mbps

• 802.11 e: QoS for wireless multimedia technology

• WMM-PS, UAPSD

�

• A-MPDU and A-MSDU aggregation

• Block ACK

• Wi-Fi Protected Access (WPA)/WPA2/WPA2-Enterprise/Wi-Fi Protected

Setup (WPS)

• SoftAP mode

• BT-Coexistence interface

1.2 MCU and Advanced Features

1.2.1 CPU and Memory

• 32-bit, up to 160MHz

• Instruction cache controller with 8KB cache RAM memory

• support XIP(executed in place)

• Flash, 1 Mbytes

1.2.2 Clocks and Timers

• PLL to generate a high frequency clock (typically 160 MHz)

• Internal 32kHz RC oscillator

• External 40 MHz crystal oscillator

1.2.3 Advanced Peripheral Interfaces

• Up to 16 GPIOs depending on package option

• 1 x I2C Master/Slave

• 1 x I2S Master/Slave

• 2 x SPIs Master/Slave

• 3 x UART interfaces with hardware flow control

�

• SDIO 2.0(up to 4bit) @ 50MHz

• Up to 6-channel HW PWM output

• 4-channel ADC with 14-bit ENOB

• 1 PGA

1.2.4 Security

• IEEE 802.11 standard security features all supported, including CCMP,

WPA/WPA2

• eFuse encryption

• Cryptographic hardware acceleration:

– AES

– Random Number Generator (RNG)

1.3 Application

• Generic low power IoT sensor hub

• Generic low power IoT loggers

• Video streaming from camera

• Over The Top (OTT) devices

• Wi-Fi enabled speech recognition devices

• Smart power plugs

• Home automation

• Mesh network

• Industrial wireless control

• Baby monitors

• Wearable electronic devices

�

• Wi-Fi location-aware devices

• Security ID tags

• Healthcare

– Proximity and movement monitoring trigger devices

– Temperature sensing loggers

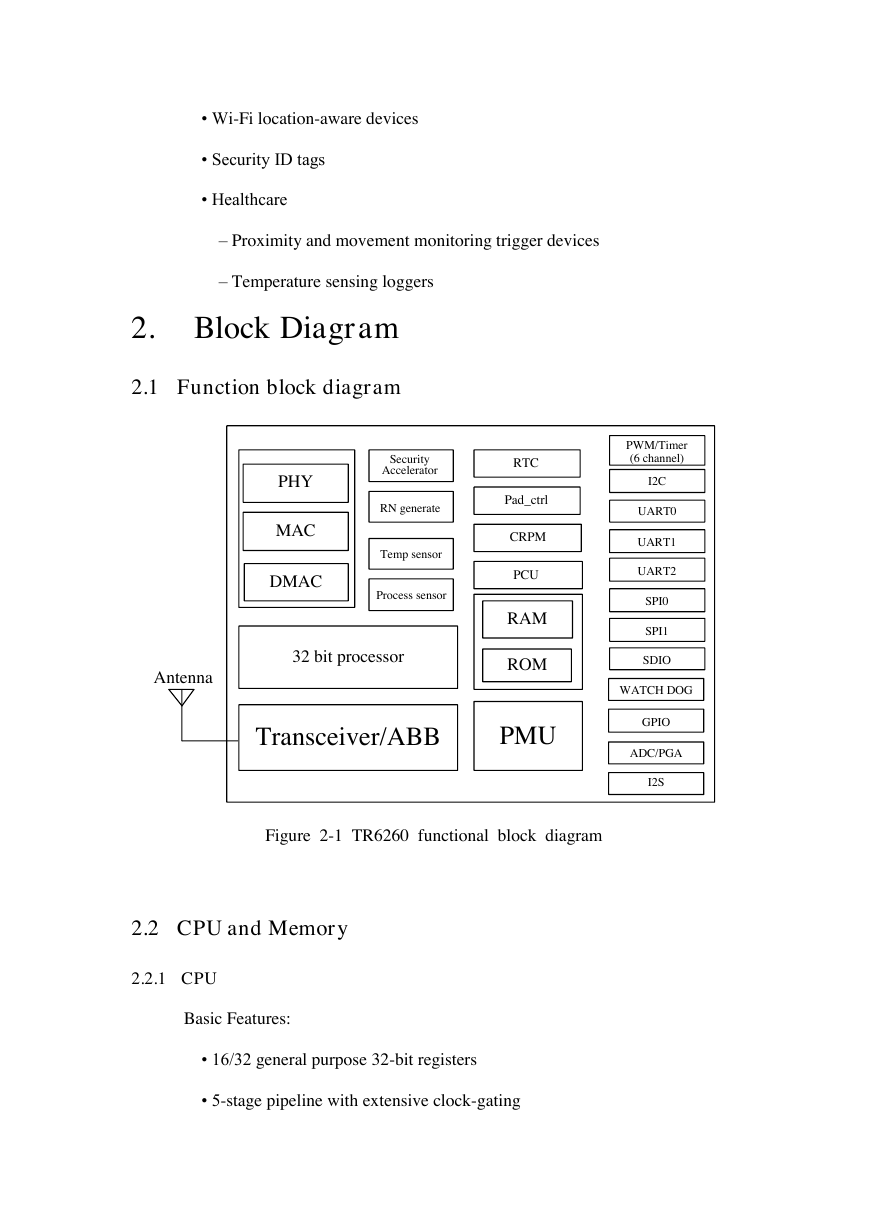

2. Block Diagram

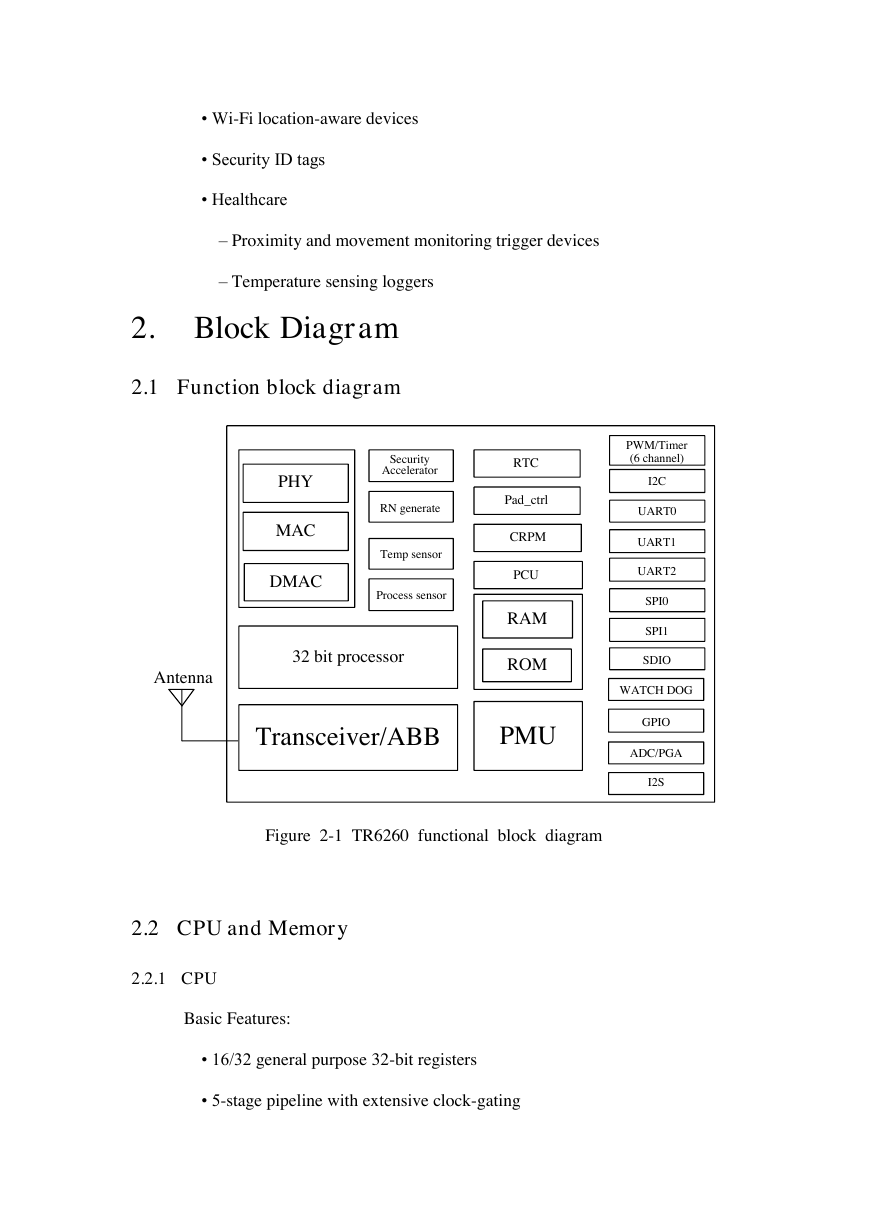

2.1 Function block diagram

Figure 2-1 TR6260 functional block diagram

2.2 CPU and Memory

2.2.1 CPU

Basic Features:

• 16/32 general purpose 32-bit registers

• 5-stage pipeline with extensive clock-gating

PCUCRPMPad_ctrlRTCPWM/Timer(6 channel)RAMROMPHYMACDMACUART0UART1UART2SPI0SPI1SDIOSecurityAcceleratorWATCH DOGGPIORN generateTemp sensorProcess sensorADC/PGATransceiver/ABBPMU 32 bit processorAntennaI2CI2S�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc