MIPS32 4K™ Processor Core Family Software User’s Manual

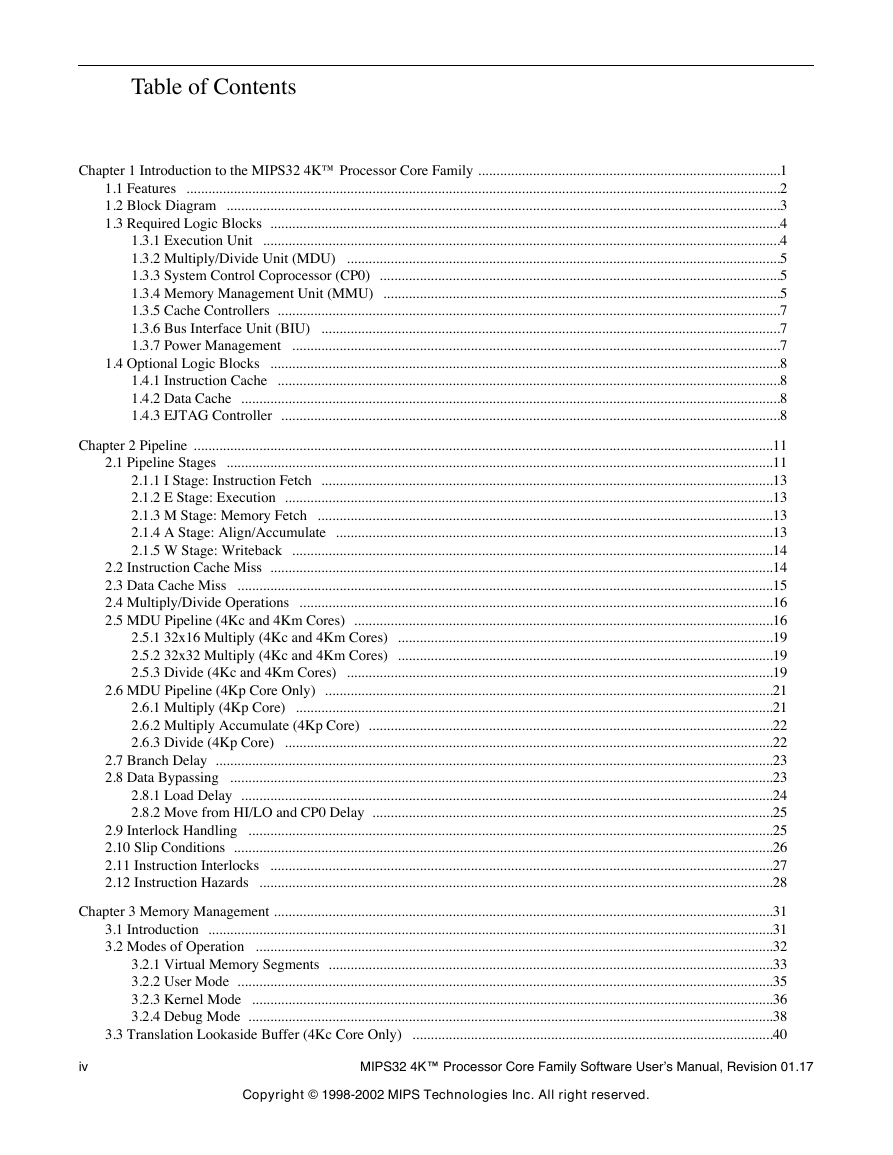

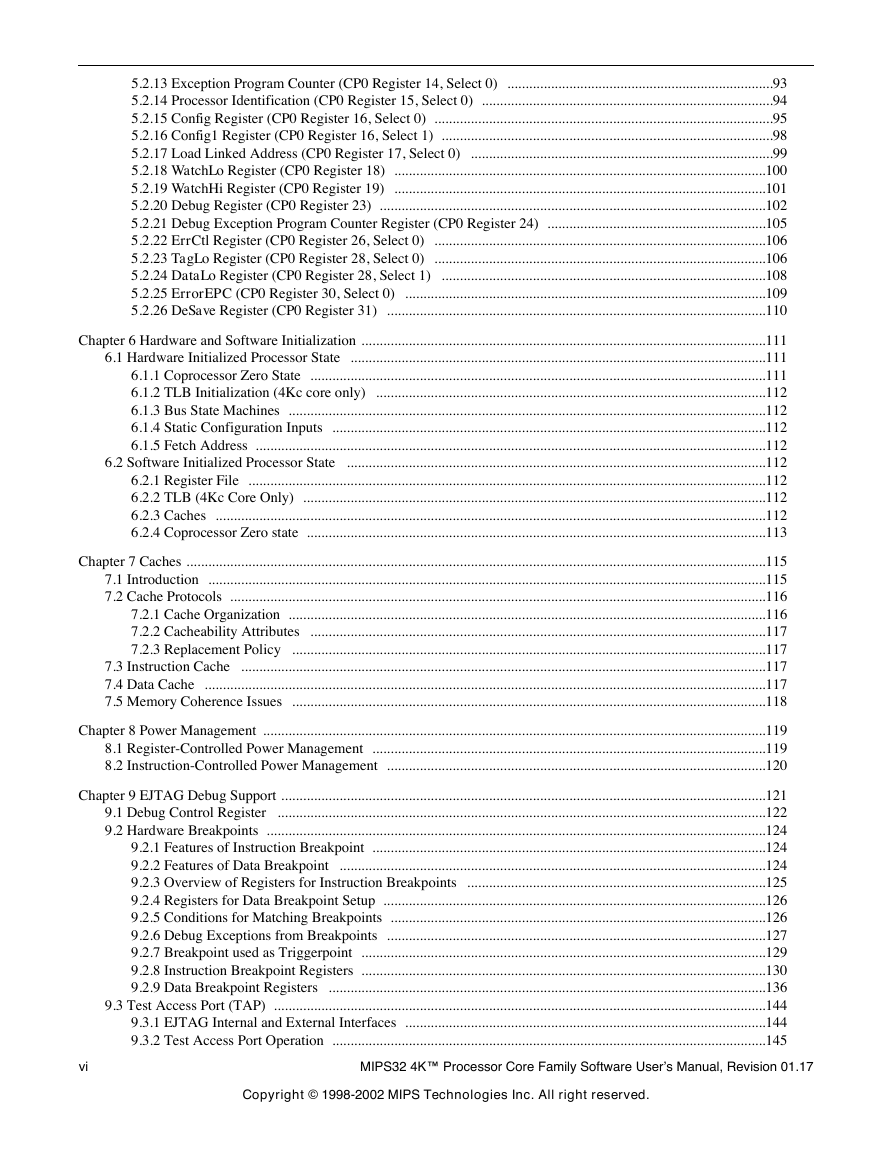

Table of Contents

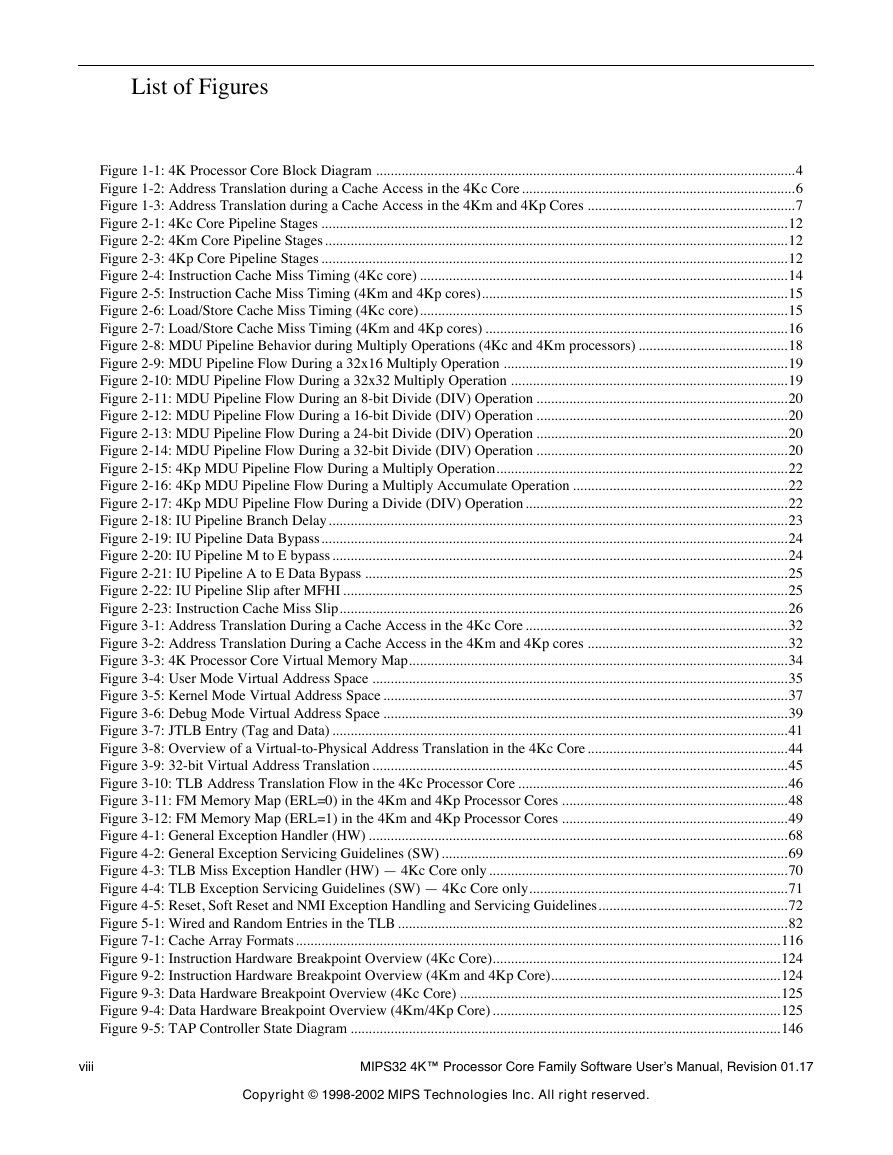

List of Figures

List of Tables

Introduction to the MIPS32 4K™ Processor Core Family

1.1� Features

1.2� Block Diagram

1.3� Required Logic Blocks

1.3.1� Execution Unit

1.3.2� Multiply/Divide Unit (MDU)

1.3.3� System Control Coprocessor (CP0)

1.3.4� Memory Management Unit (MMU)

1.3.5� Cache Controllers

1.3.6� Bus Interface Unit (BIU)

1.3.7� Power Management

1.4� Optional Logic Blocks

1.4.1� Instruction Cache

1.4.2� Data Cache

1.4.3� EJTAG Controller

Pipeline

2.1� Pipeline Stages

2.1.1� I Stage: Instruction Fetch

2.1.2� E Stage: Execution

2.1.3� M Stage: Memory Fetch

2.1.4� A Stage: Align/Accumulate

2.1.5� W Stage: Writeback

2.2� Instruction Cache Miss

2.3� Data Cache Miss

2.4� Multiply/Divide Operations

2.5� MDU Pipeline (4Kc and 4Km Cores)

2.5.1� 32x16 Multiply (4Kc and 4Km Cores)

2.5.2� 32x32 Multiply (4Kc and 4Km Cores)

2.5.3� Divide (4Kc and 4Km Cores)

2.6� MDU Pipeline (4Kp Core Only)

2.6.1� Multiply (4Kp Core)

2.6.2� Multiply Accumulate (4Kp Core)

2.6.3� Divide (4Kp Core)

2.7� Branch Delay

2.8� Data Bypassing

2.8.1� Load Delay

2.8.2� Move from HI/LO and CP0 Delay

2.9� Interlock Handling

2.10� Slip Conditions

2.11� Instruction Interlocks

2.12� Instruction Hazards

Memory Management

3.1� Introduction

3.2� Modes of Operation

3.2.1� Virtual Memory Segments

3.2.1.1� Unmapped Segments

3.2.1.2� Mapped Segments

3.2.2� User Mode

3.2.3� Kernel Mode

3.2.3.1� Kernel Mode, User Space (kuseg)

3.2.3.2� Kernel Mode, Kernel Space 0 (kseg0)

3.2.3.3� Kernel Mode, Kernel Space 1 (kseg1)

3.2.3.4� Kernel Mode, Kernel Space 2 (kseg2)

3.2.3.5� Kernel Mode, Kernel Space 3 (kseg3)

3.2.4� Debug Mode

3.2.4.1� Conditions and Behavior for Access to drseg, EJTAG Registers

3.2.4.2� Conditions and Behavior for Access to dmseg, EJTAG Memory

3.3� Translation Lookaside Buffer (4Kc Core Only)

3.3.1� Joint TLB

3.3.2� Instruction TLB

3.3.3� Data TLB

3.4� Virtual to Physical Address Translation (4Kc Core)

3.4.1� Hits, Misses, and Multiple Matches

3.4.2� Page Sizes and Replacement Algorithm

3.4.3� TLB Instructions

3.5� Fixed Mapping MMU (4Km & 4Kp Cores)

3.6� System Control Coprocessor

Exceptions

4.1� Exception Conditions

4.2� Exception Priority

4.3� Exception Vector Locations

4.4� General Exception Processing

4.5� Debug Exception Processing

4.6� Exceptions

4.6.1� Reset Exception

4.6.2� Soft Reset Exception

4.6.3� Debug Single Step Exception

4.6.4� Debug Interrupt Exception

4.6.5� Non-Maskable Interrupt (NMI) Exception

4.6.6� Machine Check Exception (4Kc core)

4.6.7� Interrupt Exception

4.6.8� Debug Instruction Break Exception

4.6.9� Watch Exception — Instruction Fetch or Data Access

4.6.10� Address Error Exception — Instruction Fetch/Data Access

4.6.11� TLB Refill Exception — Instruction Fetch or Data Access (4Kc core)

4.6.12� TLB Invalid Exception — Instruction Fetch or Data Access (4Kc core)

4.6.13� Bus Error Exception — Instruction Fetch or Data Access

4.6.14� Debug Software Breakpoint Exception

4.6.15� Execution Exception — System Call

4.6.16� Execution Exception — Breakpoint

4.6.17� Execution Exception — Reserved Instruction

4.6.18� Execution Exception — Coprocessor Unusable

4.6.19� Execution Exception — Integer Overflow

4.6.20� Execution Exception — Trap

4.6.21� Debug Data Break Exception

4.6.22� TLB Modified Exception — Data Access (4Kc core)

4.7� Exception Handling and Servicing Flowcharts

CP0 Registers

5.1� CP0 Register Summary

5.2� CP0 Registers

5.2.1� Index Register (CP0 Register 0, Select 0)

5.2.2� Random Register (CP0 Register 1, Select 0)

5.2.3� EntryLo0, EntryLo1 (CP0 Registers 2 and 3, Select 0)

5.2.4� Context Register (CP0 Register 4, Select 0)

5.2.5� PageMask Register (CP0 Register 5, Select 0)

5.2.6� Wired Register (CP0 Register 6, Select 0)

5.2.7� BadVAddr Register (CP0 Register 8, Select 0)

5.2.8� Count Register (CP0 Register 9, Select 0)

5.2.9� EntryHi Register (CP0 Register 10, Select 0)

5.2.10� Compare Register (CP0 Register 11, Select 0)

5.2.11� Status Register (CP0 Register 12, Select 0)

5.2.12� Cause Register (CP0 Register 13, Select 0)

5.2.13� Exception Program Counter (CP0 Register 14, Select 0)

5.2.14� Processor Identification (CP0 Register 15, Select 0)

5.2.15� Config Register (CP0 Register 16, Select 0)

5.2.16� Config1 Register (CP0 Register 16, Select 1)

5.2.17� Load Linked Address (CP0 Register 17, Select 0)

5.2.18� WatchLo Register (CP0 Register 18)

5.2.19� WatchHi Register (CP0 Register 19)

5.2.20� Debug Register (CP0 Register 23)

5.2.21� Debug Exception Program Counter Register (CP0 Register 24)

5.2.22� ErrCtl Register (CP0 Register 26, Select 0)

5.2.23� TagLo Register (CP0 Register 28, Select 0)

5.2.24� DataLo Register (CP0 Register 28, Select 1)

5.2.25� ErrorEPC (CP0 Register 30, Select 0)

5.2.26� DeSave Register (CP0 Register 31)

Hardware and Software Initialization

6.1� Hardware Initialized Processor State

6.1.1� Coprocessor Zero State

6.1.2� TLB Initialization (4Kc core only)

6.1.3� Bus State Machines

6.1.4� Static Configuration Inputs

6.1.5� Fetch Address

6.2� Software Initialized Processor State

6.2.1� Register File

6.2.2� TLB (4Kc Core Only)

6.2.3� Caches

6.2.4� Coprocessor Zero state

Caches

7.1� Introduction

7.2� Cache Protocols

7.2.1� Cache Organization

7.2.2� Cacheability Attributes

7.2.3� Replacement Policy

7.3� Instruction Cache

7.4� Data Cache

7.5� Memory Coherence Issues

Power Management

8.1� Register-Controlled Power Management

8.2� Instruction-Controlled Power Management

EJTAG Debug Support

9.1� Debug Control Register

9.2� Hardware Breakpoints

9.2.1� Features of Instruction Breakpoint

9.2.2� Features of Data Breakpoint

9.2.3� Overview of Registers for Instruction Breakpoints

9.2.4� Registers for Data Breakpoint Setup

9.2.5� Conditions for Matching Breakpoints

9.2.5.1� Conditions for Matching Instruction Breakpoint

9.2.5.2� Conditions for Matching Data Breakpoints

9.2.6� Debug Exceptions from Breakpoints

9.2.6.1� Debug Exception by Instruction Breakpoint

9.2.6.2� Debug Exception by Data Breakpoint

9.2.7� Breakpoint used as Triggerpoint

9.2.8� Instruction Breakpoint Registers

9.2.8.1� Instruction Breakpoint Status (IBS) Register

9.2.8.2� Instruction Breakpoint Address n (IBAn) Register

9.2.8.3� Instruction Breakpoint Address Mask n (IBMn) Register

9.2.8.4� Instruction Breakpoint ASID n (IBASIDn) Register

9.2.8.5� Instruction Breakpoint Control n (IBCn) Register

9.2.9� Data Breakpoint Registers

9.2.9.1� Data Breakpoint Status (DBS) Register

9.2.9.2� Data Breakpoint Address n (DBAn) Register

9.2.9.3� Data Breakpoint Address Mask n (DBMn) Register

9.2.9.4� Data Breakpoint ASID n (DBASIDn) Register

9.2.9.5� Data Breakpoint Control n (DBCn) Register

9.2.9.6� Data Breakpoint Value n (DBVn) Register

9.3� Test Access Port (TAP)

9.3.1� EJTAG Internal and External Interfaces

9.3.2� Test Access Port Operation

9.3.2.1� Test-Logic-Reset State

9.3.2.2� Run-Test/Idle State

9.3.2.3� Select_DR_Scan State

9.3.2.4� Select_IR_Scan State

9.3.2.5� Capture_DR State

9.3.2.6� Shift_DR State

9.3.2.7� Exit1_DR State

9.3.2.8� Pause_DR State

9.3.2.9� Exit2_DR State

9.3.2.10� Update_DR State

9.3.2.11� Capture_IR State

9.3.2.12� Shift_IR State

9.3.2.13� Exit1_IR State

9.3.2.14� Pause_IR State

9.3.2.15� Exit2_IR State

9.3.2.16� Update_IR State

9.3.3� Test Access Port (TAP) Instructions

9.3.3.1� BYPASS Instruction

9.3.3.2� IDCODE Instruction

9.3.3.3� IMPCODE Instruction

9.3.3.4� ADDRESS Instruction

9.3.3.5� DATA Instruction

9.3.3.6� CONTROL Instruction

9.3.3.7� ALL Instruction

9.3.3.8� EJTAGBOOT Instruction

9.3.3.9� NORMALBOOT Instruction

9.3.3.10� FASTDATA Instruction

9.4� EJTAG TAP Registers

9.4.1� Instruction Register

9.4.2� Data Registers Overview

9.4.2.1� Bypass Register

9.4.2.2� Device Identification (ID) Register

9.4.2.3� Implementation Register

9.4.2.4� EJTAG Control Register

9.4.3� Processor Access Address Register

9.4.3.1� Processor Access Data Register

9.4.4� Fastdata Register (TAP Instruction FASTDATA)

9.5� Processor Accesses

9.5.1� Fetch/Load and Store from/to the EJTAG Probe through dmseg

Instruction Set Overview

10.1� CPU Instruction Formats

10.2� Load and Store Instructions

10.2.1� Scheduling a Load Delay Slot

10.2.2� Defining Access Types

10.3� Computational Instructions

10.3.1� Cycle Timing for Multiply and Divide Instructions

10.4� Jump and Branch Instructions

10.4.1� Overview of Jump Instructions

10.4.2� Overview of Branch Instructions

10.5� Control Instructions

10.6� Coprocessor Instructions

10.7� Enhancements to the MIPS Architecture

10.7.1� CLO - Count Leading Ones

10.7.2� CLZ - Count Leading Zeros

10.7.3� MADD - Multiply and Add Word

10.7.4� MADDU - Multiply and Add Unsigned Word

10.7.5� MSUB - Multiply and Subtract Word

10.7.6� MSUBU - Multiply and Subtract Unsigned Word

10.7.7� MUL - Multiply Word

10.7.8� SSNOP- Superscalar Inhibit NOP

MIPS32 4K Processor Core Instructions

11.1� Understanding the Instruction Descriptions

11.2� CPU Opcode Map

11.3� Instruction Set

CACHE

LL

PREF

SC

SYNC

TLBR

TLBWI

TLBWR

WAIT

Revision History

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc