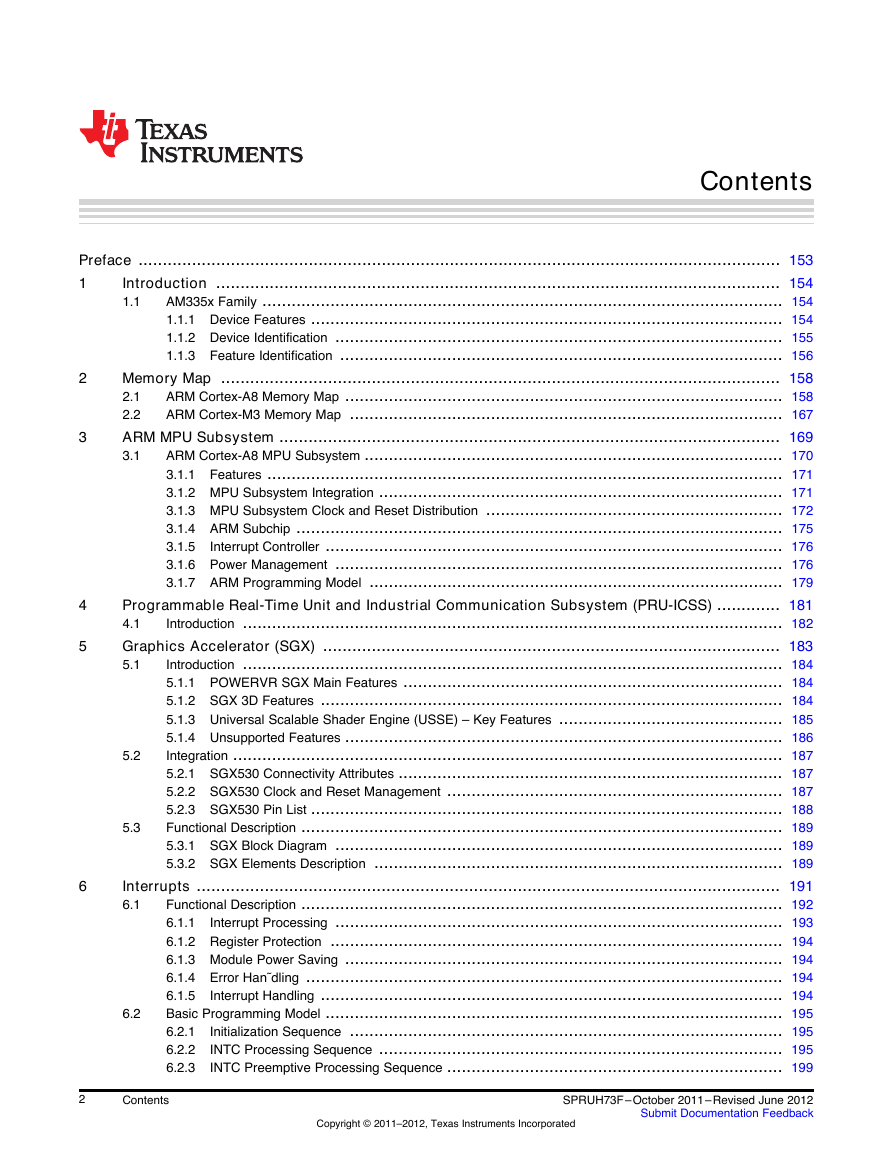

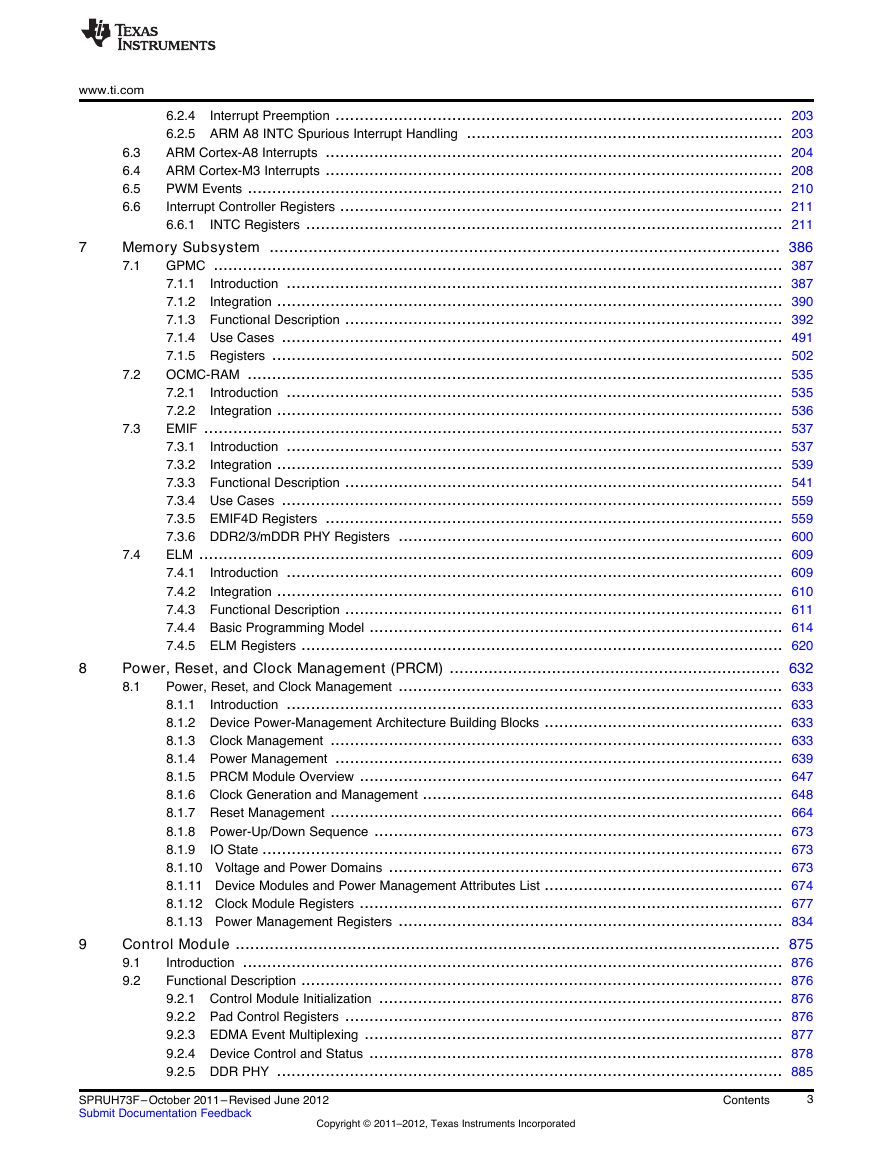

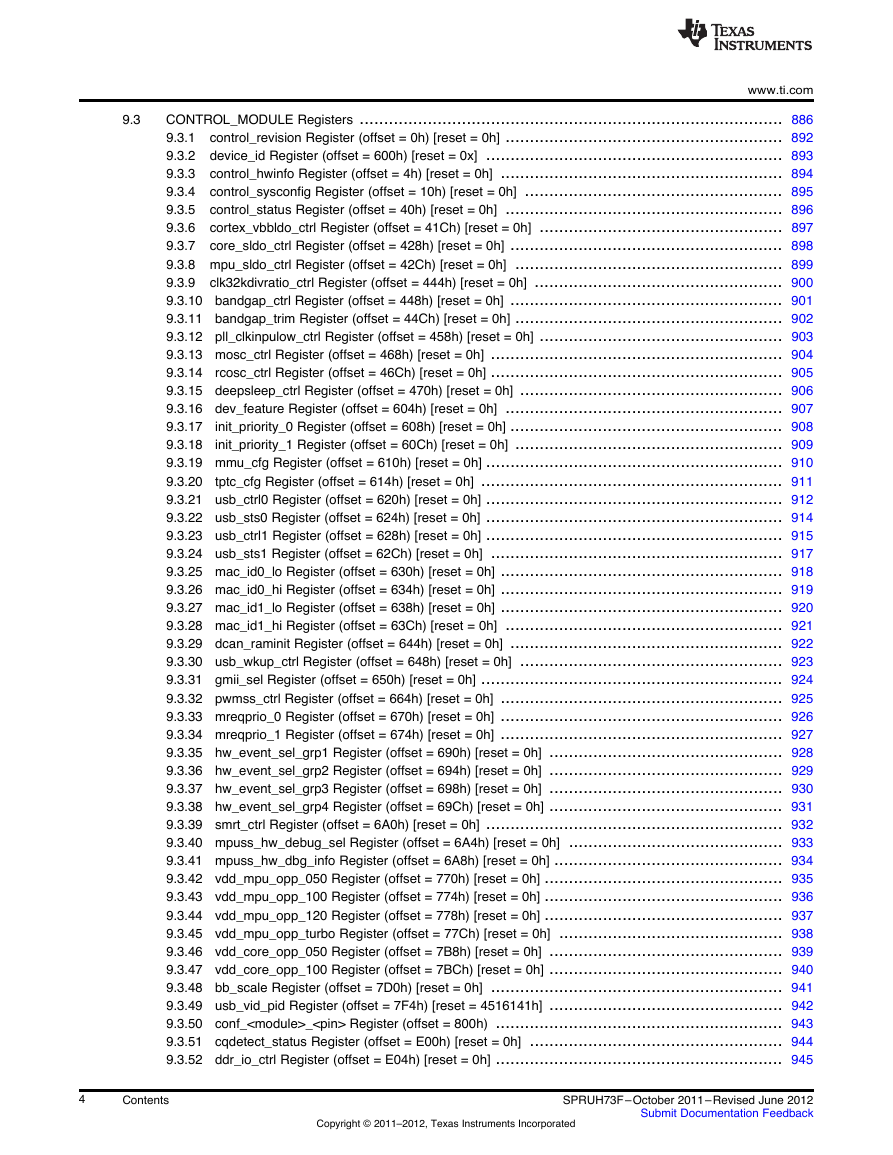

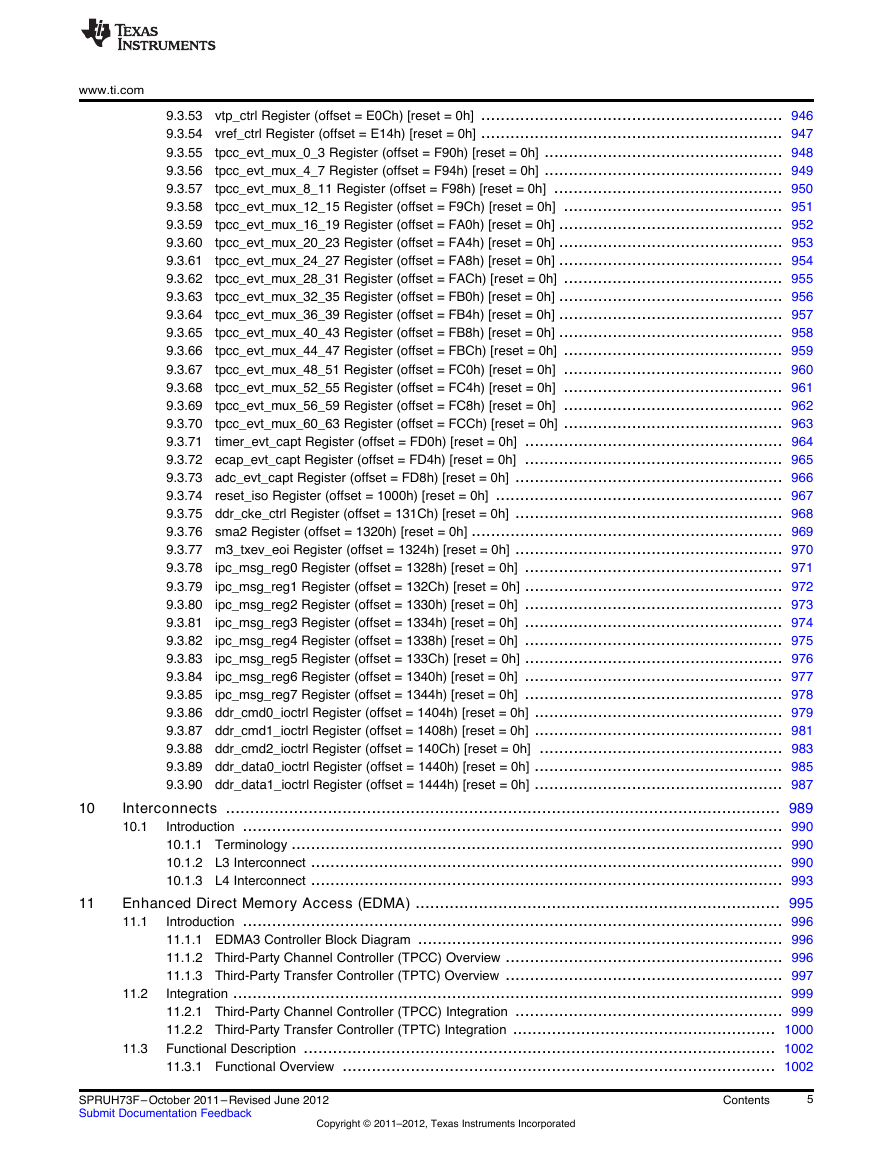

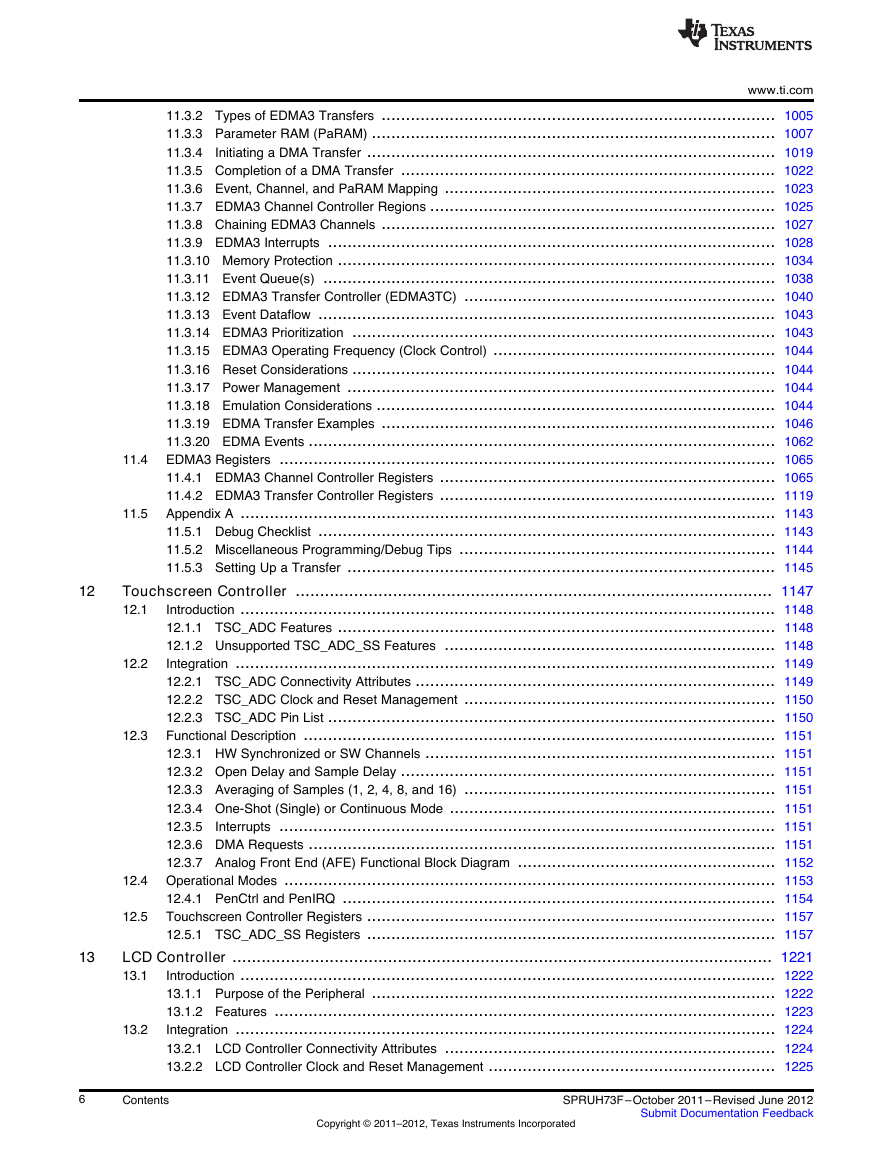

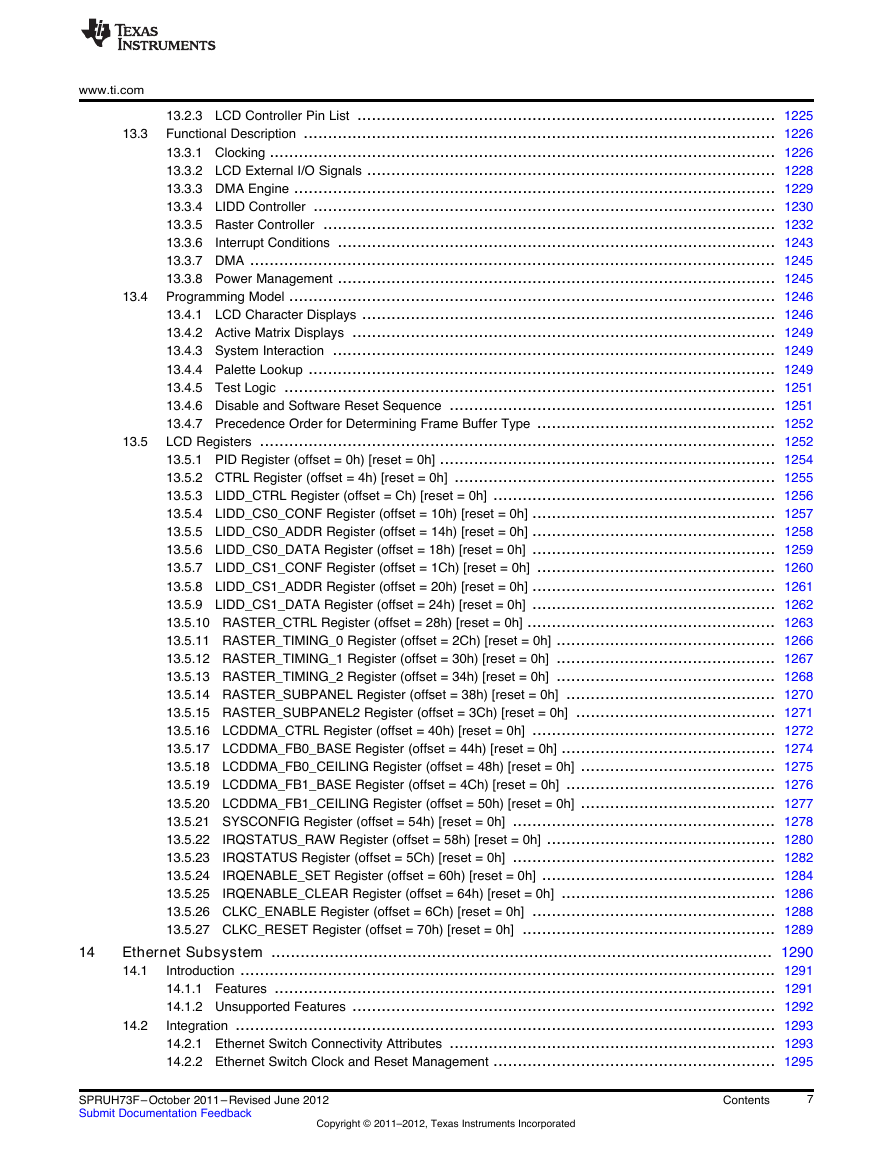

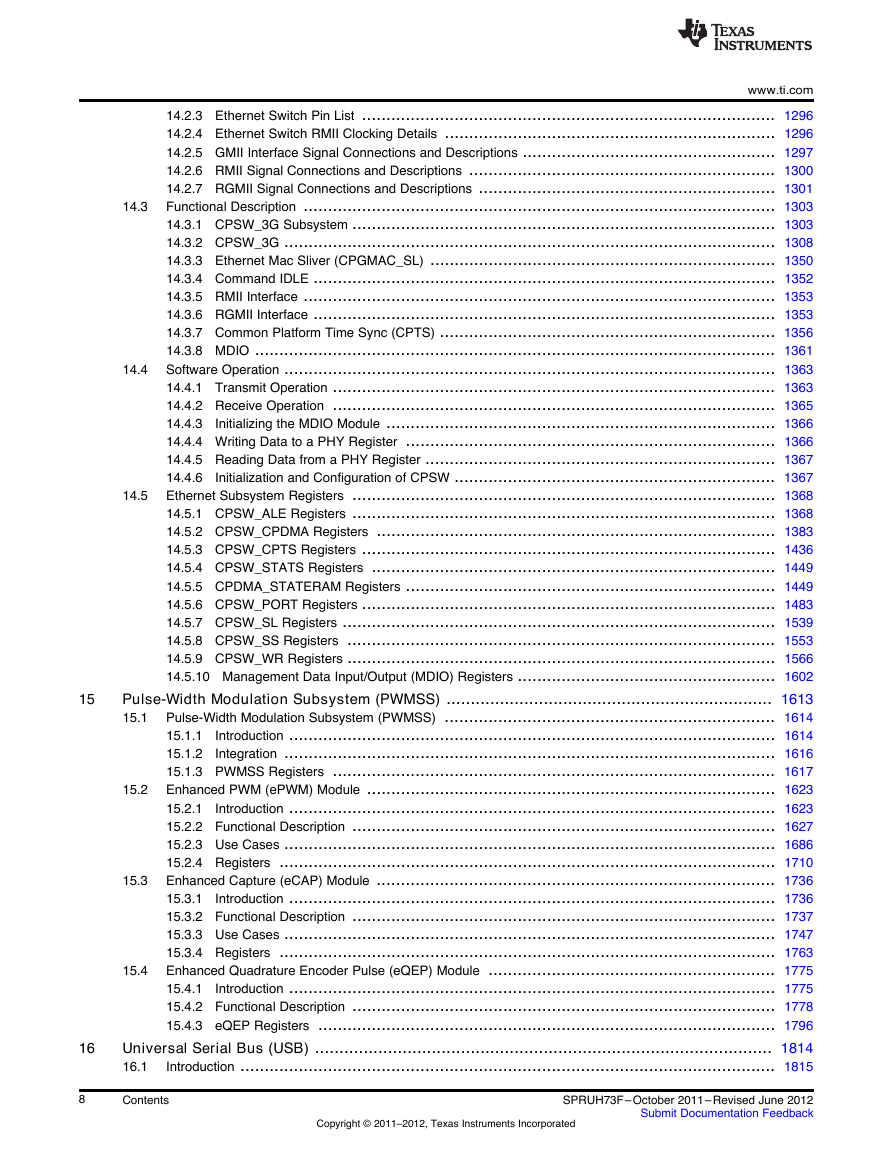

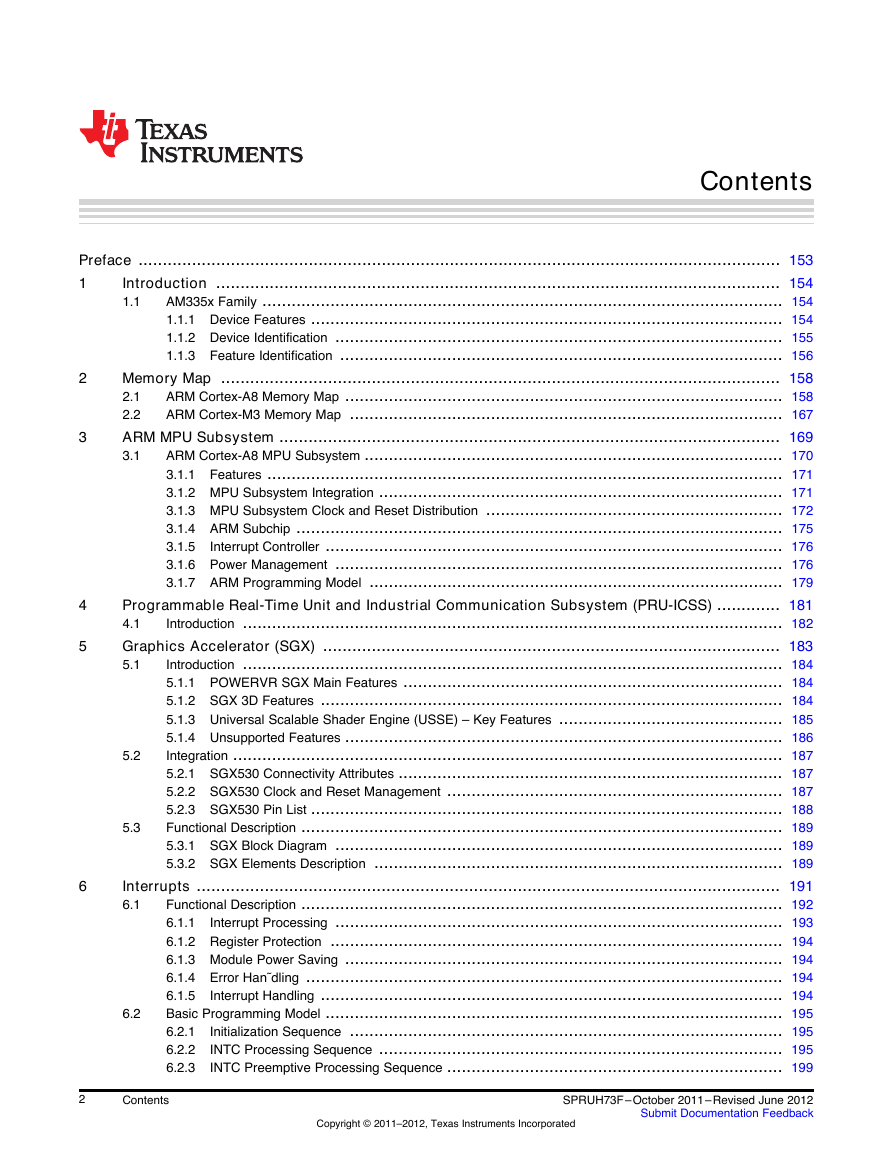

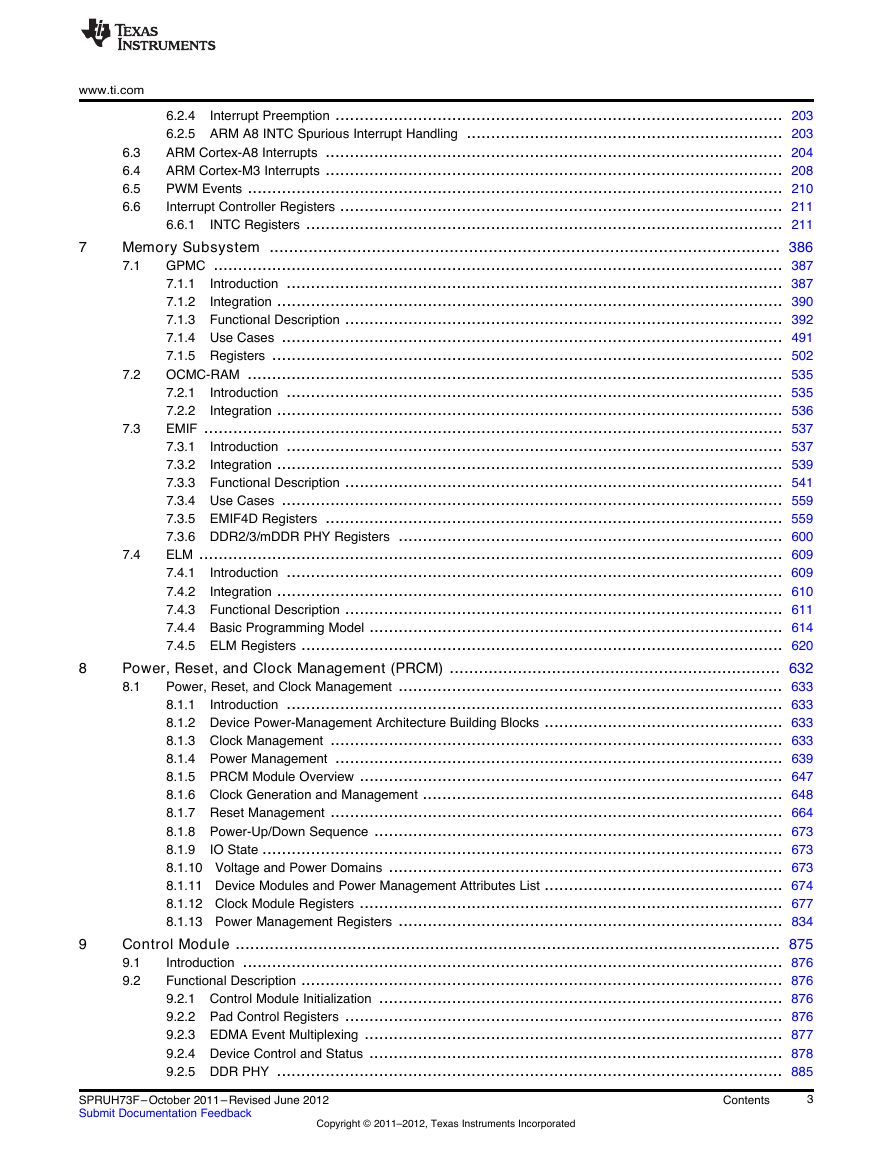

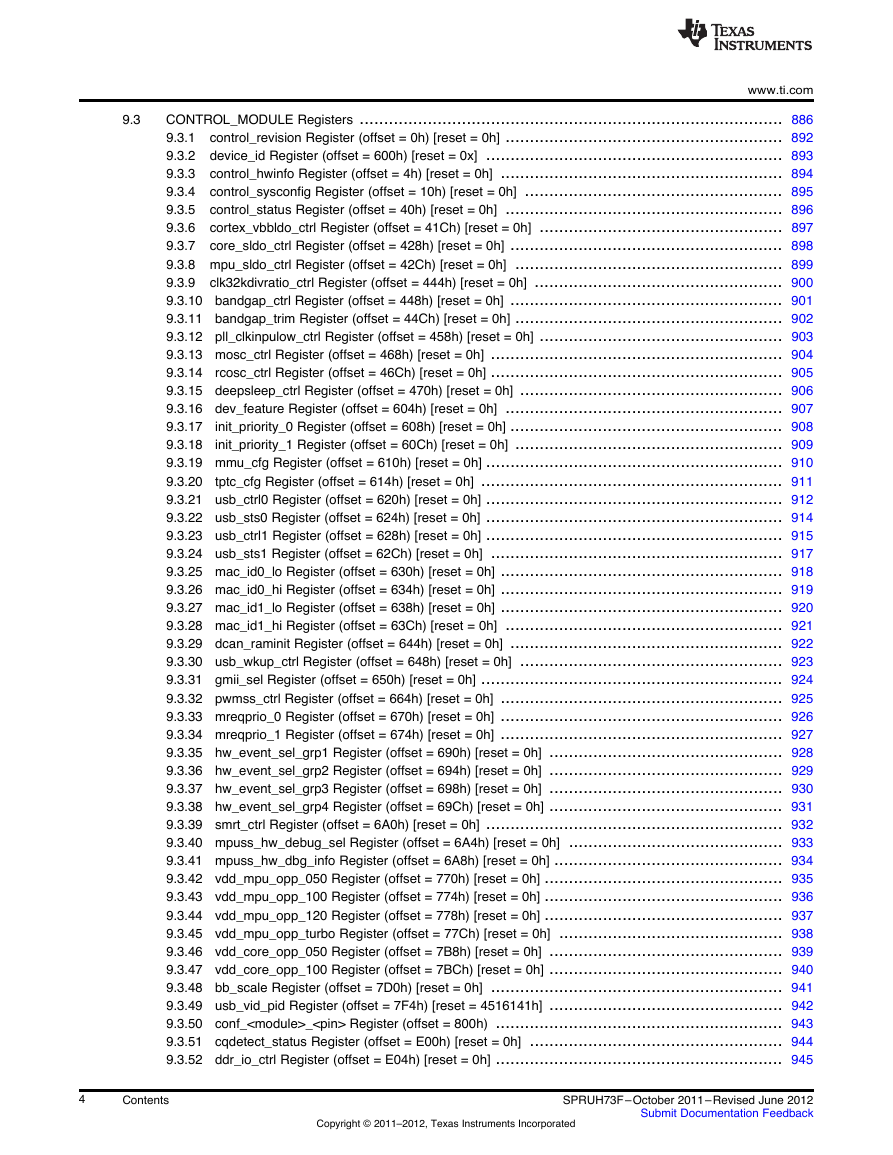

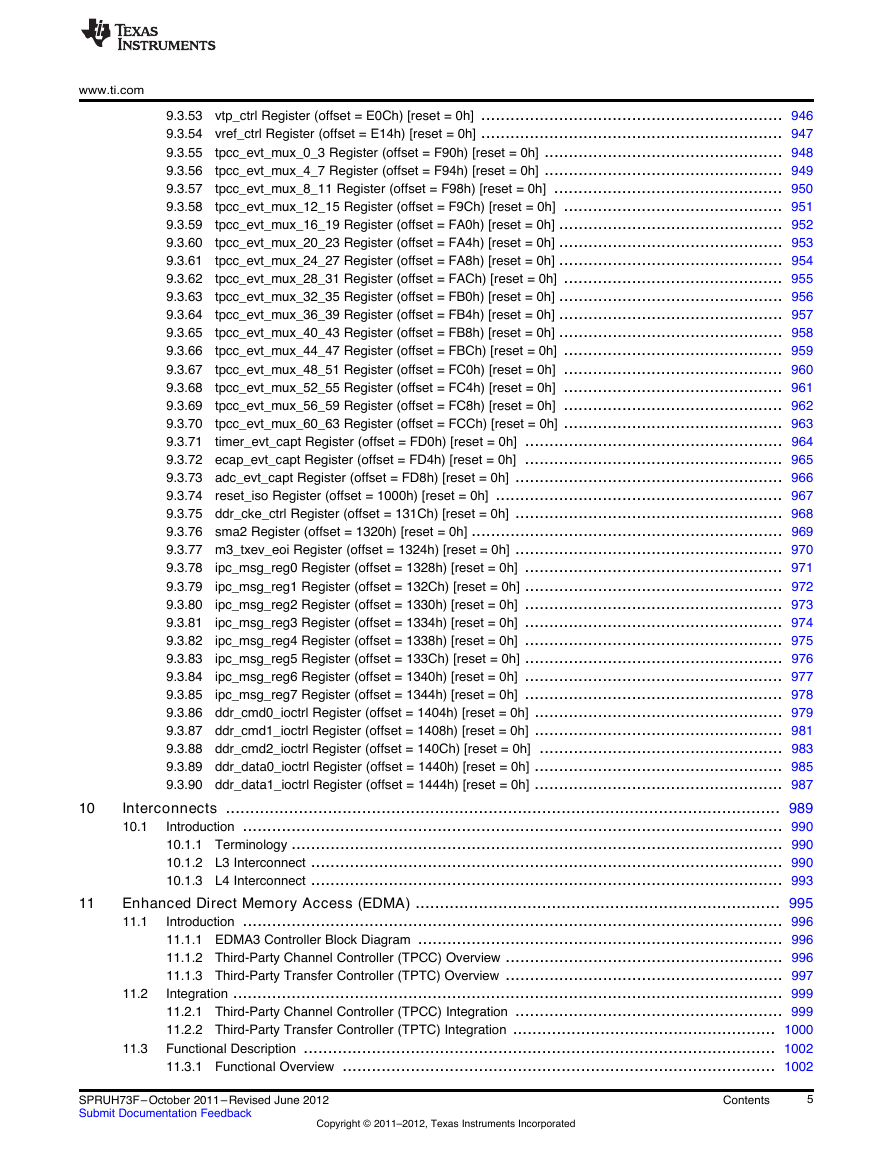

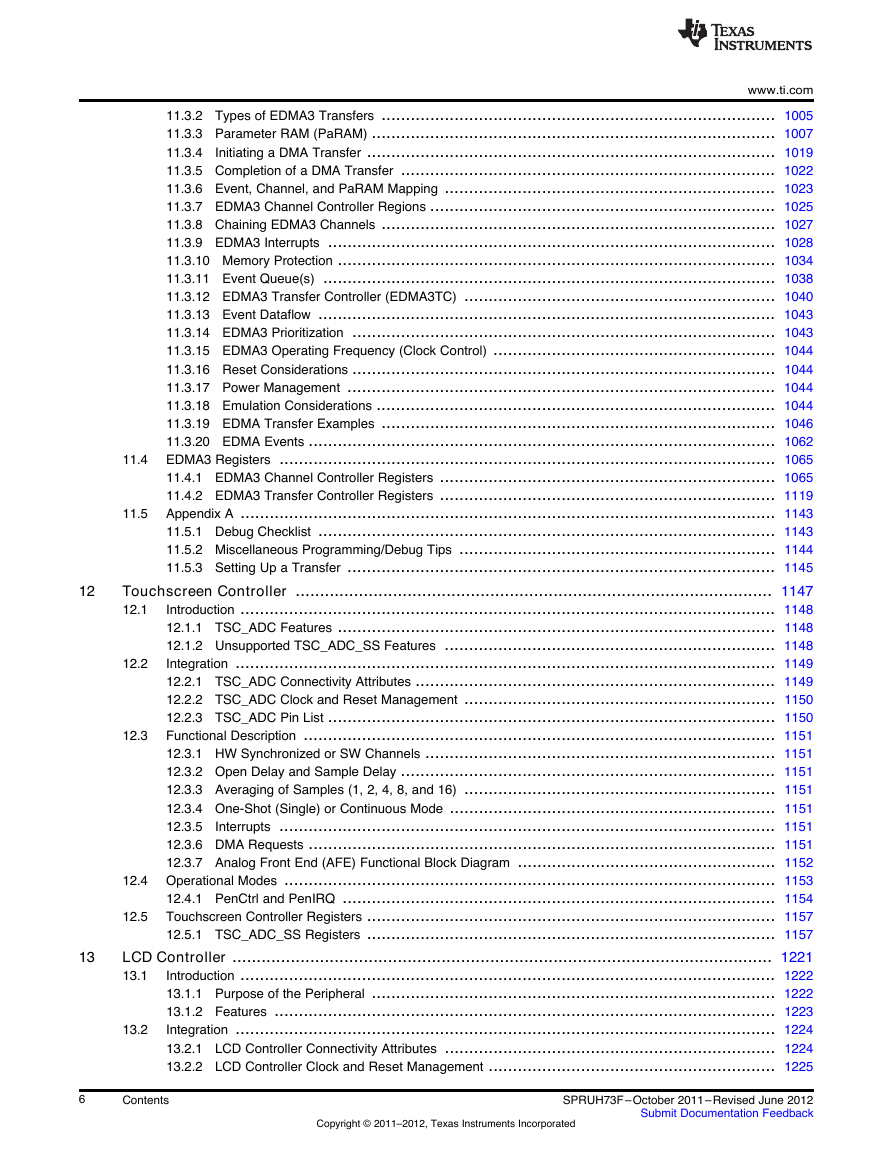

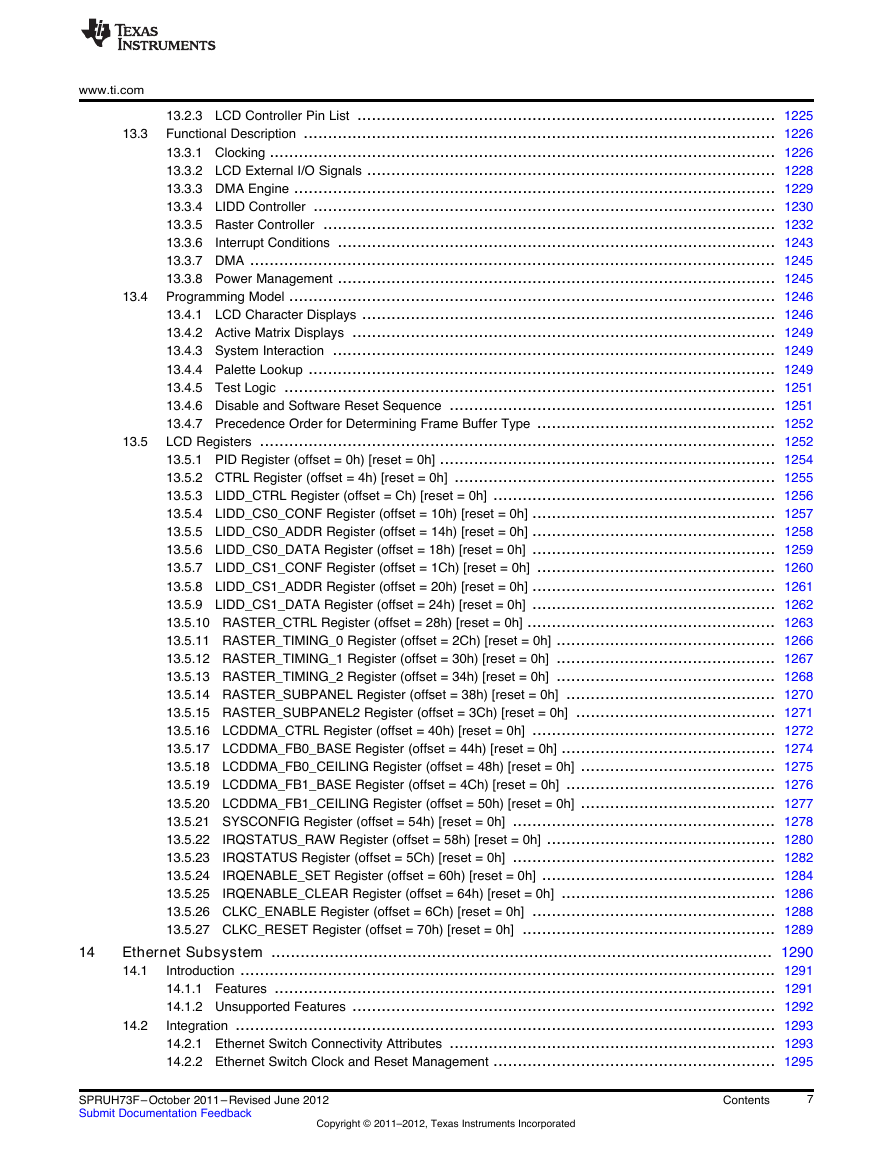

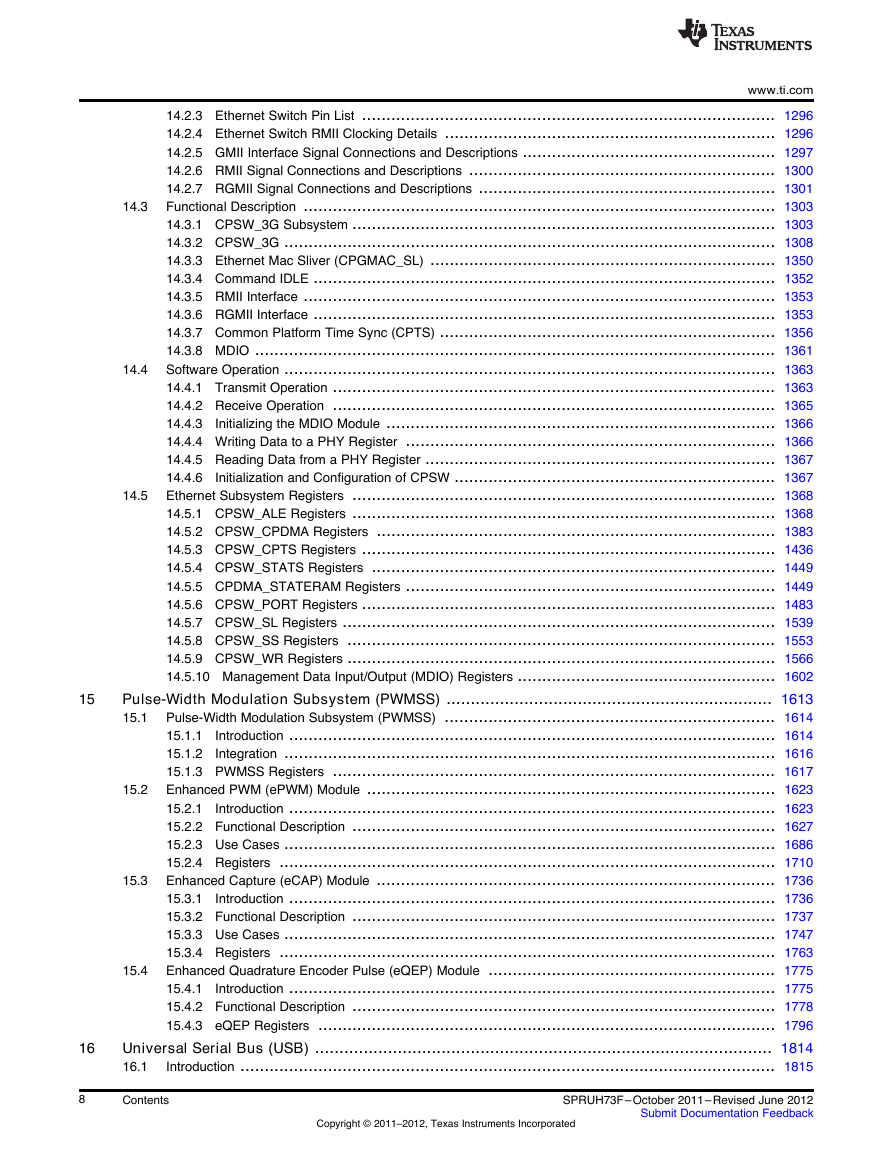

Table of Contents

Preface

1 Introduction

1.1 AM335x Family

1.1.1 Device Features

1.1.2 Device Identification

1.1.3 Feature Identification

2 Memory Map

2.1 ARM Cortex-A8 Memory Map

2.2 ARM Cortex-M3 Memory Map

3 ARM MPU Subsystem

3.1 ARM Cortex-A8 MPU Subsystem

3.1.1 Features

3.1.2 MPU Subsystem Integration

3.1.3 MPU Subsystem Clock and Reset Distribution

3.1.3.1 Clock Distribution

3.1.3.2 Reset Distribution

3.1.4 ARM Subchip

3.1.4.1 ARM Overview

3.1.4.2 ARM Description

3.1.4.2.1 ARM® Cortex™-A8 Instruction, Data, and Private Peripheral Port

3.1.4.2.2 ARM Core Supported Features

3.1.5 Interrupt Controller

3.1.6 Power Management

3.1.6.1 Power Domains

3.1.6.2 Power States

3.1.6.3 Power Modes

3.1.7 ARM Programming Model

3.1.7.1 Clock Control

3.1.7.2 MPU Power Mode Transitions

3.1.7.2.1 Basic Power-On Reset

3.1.7.2.2 MPU Into Standby Mode

3.1.7.2.3 MPU Out Of Standby Mode

3.1.7.2.4 MPU Power On From a Powered-Off State

3.1.7.3 NEON Power Mode Transition

4 Programmable Real-Time Unit and Industrial Communication Subsystem (PRU-ICSS)

4.1 Introduction

5 Graphics Accelerator (SGX)

5.1 Introduction

5.1.1 POWERVR SGX Main Features

5.1.2 SGX 3D Features

5.1.3 Universal Scalable Shader Engine (USSE) – Key Features

5.1.4 Unsupported Features

5.2 Integration

5.2.1 SGX530 Connectivity Attributes

5.2.2 SGX530 Clock and Reset Management

5.2.3 SGX530 Pin List

5.3 Functional Description

5.3.1 SGX Block Diagram

5.3.2 SGX Elements Description

6 Interrupts

6.1 Functional Description

6.1.1 Interrupt Processing

6.1.1.1 Input Selection

6.1.1.2 Masking

6.1.1.3 Individual Masking

6.1.1.4 Priority Masking

6.1.1.5 Priority Sorting

6.1.2 Register Protection

6.1.3 Module Power Saving

6.1.4 Error Han˜dling

6.1.5 Interrupt Handling

6.2 Basic Programming Model

6.2.1 Initialization Sequence

6.2.2 INTC Processing Sequence

6.2.3 INTC Preemptive Processing Sequence

6.2.4 Interrupt Preemption

6.2.5 ARM A8 INTC Spurious Interrupt Handling

6.3 ARM Cortex-A8 Interrupts

6.4 ARM Cortex-M3 Interrupts

6.5 PWM Events

6.6 Interrupt Controller Registers

6.6.1 INTC Registers

6.6.1.1 INTC_REVISION Register (offset = 0h) [reset = 50h]

6.6.1.2 INTC_SYSCONFIG Register (offset = 10h) [reset = 0h]

6.6.1.3 INTC_SYSSTATUS Register (offset = 14h) [reset = 0h]

6.6.1.4 INTC_SIR_IRQ Register (offset = 40h) [reset = FFFFFF80h]

6.6.1.5 INTC_SIR_FIQ Register (offset = 44h) [reset = FFFFFF80h]

6.6.1.6 INTC_CONTROL Register (offset = 48h) [reset = 0h]

6.6.1.7 INTC_PROTECTION Register (offset = 4Ch) [reset = 0h]

6.6.1.8 INTC_IDLE Register (offset = 50h) [reset = 0h]

6.6.1.9 INTC_IRQ_PRIORITY Register (offset = 60h) [reset = FFFFFFC0h]

6.6.1.10 INTC_FIQ_PRIORITY Register (offset = 64h) [reset = FFFFFFC0h]

6.6.1.11 INTC_THRESHOLD Register (offset = 68h) [reset = FFh]

6.6.1.12 INTC_ITR0 Register (offset = 80h) [reset = 0h]

6.6.1.13 INTC_MIR0 Register (offset = 84h) [reset = FFFFFFFFh]

6.6.1.14 INTC_MIR_CLEAR0 Register (offset = 88h) [reset = 0h]

6.6.1.15 INTC_MIR_SET0 Register (offset = 8Ch) [reset = 0h]

6.6.1.16 INTC_ISR_SET0 Register (offset = 90h) [reset = 0h]

6.6.1.17 INTC_ISR_CLEAR0 Register (offset = 94h) [reset = 0h]

6.6.1.18 INTC_PENDING_IRQ0 Register (offset = 98h) [reset = 0h]

6.6.1.19 INTC_PENDING_FIQ0 Register (offset = 9Ch) [reset = 0h]

6.6.1.20 INTC_ITR1 Register (offset = A0h) [reset = 0h]

6.6.1.21 INTC_MIR1 Register (offset = A4h) [reset = FFFFFFFFh]

6.6.1.22 INTC_MIR_CLEAR1 Register (offset = A8h) [reset = 0h]

6.6.1.23 INTC_MIR_SET1 Register (offset = ACh) [reset = 0h]

6.6.1.24 INTC_ISR_SET1 Register (offset = B0h) [reset = 0h]

6.6.1.25 INTC_ISR_CLEAR1 Register (offset = B4h) [reset = 0h]

6.6.1.26 INTC_PENDING_IRQ1 Register (offset = B8h) [reset = 0h]

6.6.1.27 INTC_PENDING_FIQ1 Register (offset = BCh) [reset = 0h]

6.6.1.28 INTC_ITR2 Register (offset = C0h) [reset = 0h]

6.6.1.29 INTC_MIR2 Register (offset = C4h) [reset = FFFFFFFFh]

6.6.1.30 INTC_MIR_CLEAR2 Register (offset = C8h) [reset = 0h]

6.6.1.31 INTC_MIR_SET2 Register (offset = CCh) [reset = 0h]

6.6.1.32 INTC_ISR_SET2 Register (offset = D0h) [reset = 0h]

6.6.1.33 INTC_ISR_CLEAR2 Register (offset = D4h) [reset = 0h]

6.6.1.34 INTC_PENDING_IRQ2 Register (offset = D8h) [reset = 0h]

6.6.1.35 INTC_PENDING_FIQ2 Register (offset = DCh) [reset = 0h]

6.6.1.36 INTC_ITR3 Register (offset = E0h) [reset = 0h]

6.6.1.37 INTC_MIR3 Register (offset = E4h) [reset = FFFFFFFFh]

6.6.1.38 INTC_MIR_CLEAR3 Register (offset = E8h) [reset = 0h]

6.6.1.39 INTC_MIR_SET3 Register (offset = ECh) [reset = 0h]

6.6.1.40 INTC_ISR_SET3 Register (offset = F0h) [reset = 0h]

6.6.1.41 INTC_ISR_CLEAR3 Register (offset = F4h) [reset = 0h]

6.6.1.42 INTC_PENDING_IRQ3 Register (offset = F8h) [reset = 0h]

6.6.1.43 INTC_PENDING_FIQ3 Register (offset = FCh) [reset = 0h]

6.6.1.44 INTC_ILR0 Register (offset = 100h) [reset = 0h]

6.6.1.45 INTC_ILR1 Register (offset = 104h) [reset = 0h]

6.6.1.46 INTC_ILR2 Register (offset = 108h) [reset = 0h]

6.6.1.47 INTC_ILR3 Register (offset = 10Ch) [reset = 0h]

6.6.1.48 INTC_ILR4 Register (offset = 110h) [reset = 0h]

6.6.1.49 INTC_ILR5 Register (offset = 114h) [reset = 0h]

6.6.1.50 INTC_ILR6 Register (offset = 118h) [reset = 0h]

6.6.1.51 INTC_ILR7 Register (offset = 11Ch) [reset = 0h]

6.6.1.52 INTC_ILR8 Register (offset = 120h) [reset = 0h]

6.6.1.53 INTC_ILR9 Register (offset = 124h) [reset = 0h]

6.6.1.54 INTC_ILR10 Register (offset = 128h) [reset = 0h]

6.6.1.55 INTC_ILR11 Register (offset = 12Ch) [reset = 0h]

6.6.1.56 INTC_ILR12 Register (offset = 130h) [reset = 0h]

6.6.1.57 INTC_ILR13 Register (offset = 134h) [reset = 0h]

6.6.1.58 INTC_ILR14 Register (offset = 138h) [reset = 0h]

6.6.1.59 INTC_ILR15 Register (offset = 13Ch) [reset = 0h]

6.6.1.60 INTC_ILR16 Register (offset = 140h) [reset = 0h]

6.6.1.61 INTC_ILR17 Register (offset = 144h) [reset = 0h]

6.6.1.62 INTC_ILR18 Register (offset = 148h) [reset = 0h]

6.6.1.63 INTC_ILR19 Register (offset = 14Ch) [reset = 0h]

6.6.1.64 INTC_ILR20 Register (offset = 150h) [reset = 0h]

6.6.1.65 INTC_ILR21 Register (offset = 154h) [reset = 0h]

6.6.1.66 INTC_ILR22 Register (offset = 158h) [reset = 0h]

6.6.1.67 INTC_ILR23 Register (offset = 15Ch) [reset = 0h]

6.6.1.68 INTC_ILR24 Register (offset = 160h) [reset = 0h]

6.6.1.69 INTC_ILR25 Register (offset = 164h) [reset = 0h]

6.6.1.70 INTC_ILR26 Register (offset = 168h) [reset = 0h]

6.6.1.71 INTC_ILR27 Register (offset = 16Ch) [reset = 0h]

6.6.1.72 INTC_ILR28 Register (offset = 170h) [reset = 0h]

6.6.1.73 INTC_ILR29 Register (offset = 174h) [reset = 0h]

6.6.1.74 INTC_ILR30 Register (offset = 178h) [reset = 0h]

6.6.1.75 INTC_ILR31 Register (offset = 17Ch) [reset = 0h]

6.6.1.76 INTC_ILR32 Register (offset = 180h) [reset = 0h]

6.6.1.77 INTC_ILR33 Register (offset = 184h) [reset = 0h]

6.6.1.78 INTC_ILR34 Register (offset = 188h) [reset = 0h]

6.6.1.79 INTC_ILR35 Register (offset = 18Ch) [reset = 0h]

6.6.1.80 INTC_ILR36 Register (offset = 190h) [reset = 0h]

6.6.1.81 INTC_ILR37 Register (offset = 194h) [reset = 0h]

6.6.1.82 INTC_ILR38 Register (offset = 198h) [reset = 0h]

6.6.1.83 INTC_ILR39 Register (offset = 19Ch) [reset = 0h]

6.6.1.84 INTC_ILR40 Register (offset = 1A0h) [reset = 0h]

6.6.1.85 INTC_ILR41 Register (offset = 1A4h) [reset = 0h]

6.6.1.86 INTC_ILR42 Register (offset = 1A8h) [reset = 0h]

6.6.1.87 INTC_ILR43 Register (offset = 1ACh) [reset = 0h]

6.6.1.88 INTC_ILR44 Register (offset = 1B0h) [reset = 0h]

6.6.1.89 INTC_ILR45 Register (offset = 1B4h) [reset = 0h]

6.6.1.90 INTC_ILR46 Register (offset = 1B8h) [reset = 0h]

6.6.1.91 INTC_ILR47 Register (offset = 1BCh) [reset = 0h]

6.6.1.92 INTC_ILR48 Register (offset = 1C0h) [reset = 0h]

6.6.1.93 INTC_ILR49 Register (offset = 1C4h) [reset = 0h]

6.6.1.94 INTC_ILR50 Register (offset = 1C8h) [reset = 0h]

6.6.1.95 INTC_ILR51 Register (offset = 1CCh) [reset = 0h]

6.6.1.96 INTC_ILR52 Register (offset = 1D0h) [reset = 0h]

6.6.1.97 INTC_ILR53 Register (offset = 1D4h) [reset = 0h]

6.6.1.98 INTC_ILR54 Register (offset = 1D8h) [reset = 0h]

6.6.1.99 INTC_ILR55 Register (offset = 1DCh) [reset = 0h]

6.6.1.100 INTC_ILR56 Register (offset = 1E0h) [reset = 0h]

6.6.1.101 INTC_ILR57 Register (offset = 1E4h) [reset = 0h]

6.6.1.102 INTC_ILR58 Register (offset = 1E8h) [reset = 0h]

6.6.1.103 INTC_ILR59 Register (offset = 1ECh) [reset = 0h]

6.6.1.104 INTC_ILR60 Register (offset = 1F0h) [reset = 0h]

6.6.1.105 INTC_ILR61 Register (offset = 1F4h) [reset = 0h]

6.6.1.106 INTC_ILR62 Register (offset = 1F8h) [reset = 0h]

6.6.1.107 INTC_ILR63 Register (offset = 1FCh) [reset = 0h]

6.6.1.108 INTC_ILR64 Register (offset = 200h) [reset = 0h]

6.6.1.109 INTC_ILR65 Register (offset = 204h) [reset = 0h]

6.6.1.110 INTC_ILR66 Register (offset = 208h) [reset = 0h]

6.6.1.111 INTC_ILR67 Register (offset = 20Ch) [reset = 0h]

6.6.1.112 INTC_ILR68 Register (offset = 210h) [reset = 0h]

6.6.1.113 INTC_ILR69 Register (offset = 214h) [reset = 0h]

6.6.1.114 INTC_ILR70 Register (offset = 218h) [reset = 0h]

6.6.1.115 INTC_ILR71 Register (offset = 21Ch) [reset = 0h]

6.6.1.116 INTC_ILR72 Register (offset = 220h) [reset = 0h]

6.6.1.117 INTC_ILR73 Register (offset = 224h) [reset = 0h]

6.6.1.118 INTC_ILR74 Register (offset = 228h) [reset = 0h]

6.6.1.119 INTC_ILR75 Register (offset = 22Ch) [reset = 0h]

6.6.1.120 INTC_ILR76 Register (offset = 230h) [reset = 0h]

6.6.1.121 INTC_ILR77 Register (offset = 234h) [reset = 0h]

6.6.1.122 INTC_ILR78 Register (offset = 238h) [reset = 0h]

6.6.1.123 INTC_ILR79 Register (offset = 23Ch) [reset = 0h]

6.6.1.124 INTC_ILR80 Register (offset = 240h) [reset = 0h]

6.6.1.125 INTC_ILR81 Register (offset = 244h) [reset = 0h]

6.6.1.126 INTC_ILR82 Register (offset = 248h) [reset = 0h]

6.6.1.127 INTC_ILR83 Register (offset = 24Ch) [reset = 0h]

6.6.1.128 INTC_ILR84 Register (offset = 250h) [reset = 0h]

6.6.1.129 INTC_ILR85 Register (offset = 254h) [reset = 0h]

6.6.1.130 INTC_ILR86 Register (offset = 258h) [reset = 0h]

6.6.1.131 INTC_ILR87 Register (offset = 25Ch) [reset = 0h]

6.6.1.132 INTC_ILR88 Register (offset = 260h) [reset = 0h]

6.6.1.133 INTC_ILR89 Register (offset = 264h) [reset = 0h]

6.6.1.134 INTC_ILR90 Register (offset = 268h) [reset = 0h]

6.6.1.135 INTC_ILR91 Register (offset = 26Ch) [reset = 0h]

6.6.1.136 INTC_ILR92 Register (offset = 270h) [reset = 0h]

6.6.1.137 INTC_ILR93 Register (offset = 274h) [reset = 0h]

6.6.1.138 INTC_ILR94 Register (offset = 278h) [reset = 0h]

6.6.1.139 INTC_ILR95 Register (offset = 27Ch) [reset = 0h]

6.6.1.140 INTC_ILR96 Register (offset = 280h) [reset = 0h]

6.6.1.141 INTC_ILR97 Register (offset = 284h) [reset = 0h]

6.6.1.142 INTC_ILR98 Register (offset = 288h) [reset = 0h]

6.6.1.143 INTC_ILR99 Register (offset = 28Ch) [reset = 0h]

6.6.1.144 INTC_ILR100 Register (offset = 290h) [reset = 0h]

6.6.1.145 INTC_ILR101 Register (offset = 294h) [reset = 0h]

6.6.1.146 INTC_ILR102 Register (offset = 298h) [reset = 0h]

6.6.1.147 INTC_ILR103 Register (offset = 29Ch) [reset = 0h]

6.6.1.148 INTC_ILR104 Register (offset = 2A0h) [reset = 0h]

6.6.1.149 INTC_ILR105 Register (offset = 2A4h) [reset = 0h]

6.6.1.150 INTC_ILR106 Register (offset = 2A8h) [reset = 0h]

6.6.1.151 INTC_ILR107 Register (offset = 2ACh) [reset = 0h]

6.6.1.152 INTC_ILR108 Register (offset = 2B0h) [reset = 0h]

6.6.1.153 INTC_ILR109 Register (offset = 2B4h) [reset = 0h]

6.6.1.154 INTC_ILR110 Register (offset = 2B8h) [reset = 0h]

6.6.1.155 INTC_ILR111 Register (offset = 2BCh) [reset = 0h]

6.6.1.156 INTC_ILR112 Register (offset = 2C0h) [reset = 0h]

6.6.1.157 INTC_ILR113 Register (offset = 2C4h) [reset = 0h]

6.6.1.158 INTC_ILR114 Register (offset = 2C8h) [reset = 0h]

6.6.1.159 INTC_ILR115 Register (offset = 2CCh) [reset = 0h]

6.6.1.160 INTC_ILR116 Register (offset = 2D0h) [reset = 0h]

6.6.1.161 INTC_ILR117 Register (offset = 2D4h) [reset = 0h]

6.6.1.162 INTC_ILR118 Register (offset = 2D8h) [reset = 0h]

6.6.1.163 INTC_ILR119 Register (offset = 2DCh) [reset = 0h]

6.6.1.164 INTC_ILR120 Register (offset = 2E0h) [reset = 0h]

6.6.1.165 INTC_ILR121 Register (offset = 2E4h) [reset = 0h]

6.6.1.166 INTC_ILR122 Register (offset = 2E8h) [reset = 0h]

6.6.1.167 INTC_ILR123 Register (offset = 2ECh) [reset = 0h]

6.6.1.168 INTC_ILR124 Register (offset = 2F0h) [reset = 0h]

6.6.1.169 INTC_ILR125 Register (offset = 2F4h) [reset = 0h]

6.6.1.170 INTC_ILR126 Register (offset = 2F8h) [reset = 0h]

6.6.1.171 INTC_ILR127 Register (offset = 2FCh) [reset = 0h]

7 Memory Subsystem

7.1 GPMC

7.1.1 Introduction

7.1.1.1 GPMC Features

7.1.1.2 Block Diagram

7.1.1.3 Unsupported GPMC Features

7.1.2 Integration

7.1.2.1 GPMC Connectivity Attributes

7.1.2.2 GPMC Clock and Reset Management

7.1.2.3 GPMC Signal List

7.1.3 Functional Description

7.1.3.1 GPMC Signals

7.1.3.2 GPMC Modes

7.1.3.3 GPMC Functional Description

7.1.3.3.1 GPMC Clock Configuration

7.1.3.3.2 GPMC Software Reset

7.1.3.3.3 GPMC Power Management

7.1.3.3.4 GPMC Interrupt Requests

7.1.3.3.5 GPMC DMA Requests

7.1.3.3.6 L3 Slow Interconnect Interface

7.1.3.3.7 GPMC Address and Data Bus

7.1.3.3.8 Address Decoder and Chip-Select Configuration

7.1.3.3.9 Timing Setting

7.1.3.3.10 NOR Access Description

7.1.3.3.11 pSRAM Access Specificities

7.1.3.3.12 NAND Access Description

7.1.3.4 GPMC High-Level Programming Model Overview

7.1.3.5 GPMC Initialization

7.1.3.6 GPMC Configuration in NOR Mode

7.1.3.7 GPMC Configuration in NAND Mode

7.1.3.8 Set Memory Access

7.1.3.9 GPMC Timing Parameters

7.1.3.9.1 GPMC Timing Parameters Formulas

7.1.4 Use Cases

7.1.4.1 How to Set GPMC Timing Parameters for Typical Accesses

7.1.4.1.1 External Memory Attached to the GPMC Module

7.1.4.1.2 Typical GPMC Setup

7.1.4.1.3 GPMC Configuration for Synchronous Burst Read Access

7.1.4.1.4 GPMC Configuration for Asynchronous Read Access

7.1.4.1.5 GPMC Configuration for Asynchronous Single Write Access

7.1.4.2 How to Choose a Suitable Memory to Use With the GPMC

7.1.4.2.1 Supported Memories or Devices

7.1.4.2.2 NAND Interface Protocol

7.1.4.2.3 NOR Interface Protocol

7.1.4.2.4 Other Technologies

7.1.4.2.5 Supported Protocols

7.1.4.2.6 GPMC Features and Settings

7.1.5 Registers

7.1.5.1 GPMC_REVISION

7.1.5.2 GPMC_SYSCONFIG

7.1.5.3 GPMC_SYSSTATUS

7.1.5.4 GPMC_IRQSTATUS

7.1.5.5 GPMC_IRQENABLE

7.1.5.6 GPMC_TIMEOUT_CONTROL

7.1.5.7 GPMC_ERR_ADDRESS

7.1.5.8 GPMC_ERR_TYPE

7.1.5.9 GPMC_CONFIG

7.1.5.10 GPMC_STATUS

7.1.5.11 GPMC_CONFIG1_i

7.1.5.12 GPMC_CONFIG2_i

7.1.5.13 GPMC_CONFIG3_i

7.1.5.14 GPMC_CONFIG4_i

7.1.5.15 GPMC_CONFIG5_i

7.1.5.16 GPMC_CONFIG6_i

7.1.5.17 GPMC_CONFIG7_i

7.1.5.18 GPMC_NAND_COMMAND_i

7.1.5.19 GPMC_NAND_ADDRESS_i

7.1.5.20 GPMC_NAND_DATA_i

7.1.5.21 GPMC_PREFETCH_CONFIG1

7.1.5.22 GPMC_PREFETCH_CONFIG2

7.1.5.23 GPMC_PREFETCH_CONTROL

7.1.5.24 GPMC_PREFETCH_STATUS

7.1.5.25 GPMC_ECC_CONFIG

7.1.5.26 GPMC_ECC_CONTROL

7.1.5.27 GPMC_ECC_SIZE_CONFIG

7.1.5.28 GPMC_ECCj_RESULT

7.1.5.29 GPMC_BCH_RESULT0_i

7.1.5.30 GPMC_BCH_RESULT1_i

7.1.5.31 GPMC_BCH_RESULT2_i

7.1.5.32 GPMC_BCH_RESULT3_i

7.1.5.33 GPMC_BCH_SWDATA

7.1.5.34 GPMC_BCH_RESULT4_i

7.1.5.35 GPMC_BCH_RESULT5_i

7.1.5.36 GPMC_BCH_RESULT6_i

7.2 OCMC-RAM

7.2.1 Introduction

7.2.1.1 OCMC RAM Features

7.2.1.2 Unsupported OCMC RAM Features

7.2.2 Integration

7.2.2.1 OCMC RAM Connectivity Attributes

7.2.2.2 OCMC RAM Clock and Reset Management

7.2.2.3 OCMC RAM Pin List

7.3 EMIF

7.3.1 Introduction

7.3.1.1 Features

7.3.1.2 Unsupported EMIF Features

7.3.2 Integration

7.3.2.1 EMIF Connectivity Attributes

7.3.2.2 EMIF Clock Management

7.3.2.3 EMIF Pin List

7.3.3 Functional Description

7.3.3.1 Signal Descriptions

7.3.3.2 Clock Control

7.3.3.3 DDR2/3/mDDR Memory Controller Subsytem Overview

7.3.3.3.1 DDR2/3/mDDR Memory Controller Interface

7.3.3.3.2 Data Macro

7.3.3.3.3 Command Macro

7.3.3.3.4 VTP Controller Macro

7.3.3.3.5 DQS-Gate IOs

7.3.3.4 Address Mapping

7.3.3.4.1 Address Mapping when REG_IBANK_POS=0 and REG_EBANK_POS=0

7.3.3.4.2 Address Mapping when REG_IBANK_POS = 1 and REG_EBANK_POS = 0

7.3.3.4.3 Address Mapping when REG_IBANK_POS=2 and REG_EBANK_POS = 0

7.3.3.4.4 Address Mapping when REG_IBANK_POS= 3 and REG_EBANK_POS = 0

7.3.3.4.5 Address Mapping when REG_IBANK_POS = 0 and REG_EBANK_POS = 1

7.3.3.4.6 Address Mapping when REG_IBANK_POS = 1 and REG_EBANK_POS = 1

7.3.3.4.7 Address Mapping when REG_IBANK_POS = 2 and REG_EBANK_POS = 1

7.3.3.4.8 Address Mapping when REG_IBANK_POS = 3 and REG_EBANK_POS = 1

7.3.3.5 Performance Management

7.3.3.5.1 Command Ordering and Scheduling

7.3.3.5.2 Command Starvation

7.3.3.5.3 Possible Race Condition

7.3.3.5.4 Class of Service (COS)

7.3.3.5.5 Refresh Scheduling

7.3.3.6 DDR3 Read-Write Leveling

7.3.3.7 PRCM Sequence for DDR2/3/mDDR Memory controller

7.3.3.8 Interrupt Support

7.3.3.9 EDMA Event Support

7.3.3.10 Emulation Considerations

7.3.3.11 Power Management

7.3.3.11.1 Clock Stop Mode

7.3.3.11.2 Self-Refresh Mode

7.3.3.11.3 Power Down Mode

7.3.3.11.4 Deep Power-Down Mode

7.3.3.11.5 Save and Restore Mode

7.3.3.11.6 EMIF PHY Clock Gating

7.3.4 Use Cases

7.3.5 EMIF4D Registers

7.3.5.1 EMIF_MOD_ID_REV Register (offset = 0h) [reset = 40440C03h]

7.3.5.2 STATUS Register (offset = 4h) [reset = 0h]

7.3.5.3 SDRAM_CONFIG Register (offset = 8h) [reset = 0h]

7.3.5.4 SDRAM_CONFIG_2 Register (offset = Ch) [reset = 0h]

7.3.5.5 SDRAM_REF_CTRL Register (offset = 10h) [reset = 0h]

7.3.5.6 SDRAM_REF_CTRL_SHDW Register (offset = 14h) [reset = 0h]

7.3.5.7 SDRAM_TIM_1 Register (offset = 18h) [reset = 0h]

7.3.5.8 SDRAM_TIM_1_SHDW Register (offset = 1Ch) [reset = 0h]

7.3.5.9 SDRAM_TIM_2 Register (offset = 20h) [reset = 0h]

7.3.5.10 SDRAM_TIM_2_SHDW Register (offset = 24h) [reset = 0h]

7.3.5.11 SDRAM_TIM_3 Register (offset = 28h) [reset = 0h]

7.3.5.12 SDRAM_TIM_3_SHDW Register (offset = 2Ch) [reset = 0h]

7.3.5.13 PWR_MGMT_CTRL Register (offset = 38h) [reset = 0h]

7.3.5.14 PWR_MGMT_CTRL_SHDW Register (offset = 3Ch) [reset = 0h]

7.3.5.15 PERF_CNT_1 Register (offset = 80h) [reset = 0h]

7.3.5.16 PERF_CNT_2 Register (offset = 84h) [reset = 0h]

7.3.5.17 PERF_CNT_CFG Register (offset = 88h) [reset = 10000h]

7.3.5.18 PERF_CNT_SEL Register (offset = 8Ch) [reset = 0h]

7.3.5.19 PERF_CNT_TIM Register (offset = 90h) [reset = 0h]

7.3.5.20 READ_IDLE_CTRL Register (offset = 98h) [reset = 50000h]

7.3.5.21 READ_IDLE_CTRL_SHDW Register (offset = 9Ch) [reset = 50000h]

7.3.5.22 IRQSTATUS_RAW_SYS Register (offset = A4h) [reset = 0h]

7.3.5.23 IRQSTATUS_SYS Register (offset = ACh) [reset = 0h]

7.3.5.24 IRQENABLE_SET_SYS Register (offset = B4h) [reset = 0h]

7.3.5.25 IRQENABLE_CLR_SYS Register (offset = BCh) [reset = 0h]

7.3.5.26 ZQ_CONFIG Register (offset = C8h) [reset = 0h]

7.3.5.27 RDWR_LVL_RMP_WIN Register (offset = D4h) [reset = 0h]

7.3.5.28 RDWR_LVL_RMP_CTRL Register (offset = D8h) [reset = 0h]

7.3.5.29 RDWR_LVL_CTRL Register (offset = DCh) [reset = 0h]

7.3.5.30 DDR_PHY_CTRL_1 Register (offset = E4h) [reset = 0h]

7.3.5.31 DDR_PHY_CTRL_1_SHDW Register (offset = E8h) [reset = 0h]

7.3.5.32 PRI_COS_MAP Register (offset = 100h) [reset = 0h]

7.3.5.33 CONNID_COS_1_MAP Register (offset = 104h) [reset = 0h]

7.3.5.34 CONNID_COS_2_MAP Register (offset = 108h) [reset = 0h]

7.3.5.35 RD_WR_EXEC_THRSH Register (offset = 120h) [reset = 0h]

7.3.6 DDR2/3/mDDR PHY Registers

7.3.6.1 DDR PHY Command 0/1/2 Address/Command Slave Ratio Register (CMD0/1/2_REG_PHY_CTRL_SLAVE_RATIO_0)

7.3.6.2 DDR PHY Command 0/1/2 Address/Command DLL Lock Difference Register( CMD0/1/2_REG_PHY_DLL_LOCK_DIFF_0)

7.3.6.3 DDR PHY Command 0/1/2 Invert Clockout Selection Register( CMD0/1/2_REG_PHY_INVERT_CLKOUT_0)

7.3.6.4 DDR PHY Data Macro 0/1 Read DQS Slave Ratio Register (DATA0/1_REG_PHY_RD_DQS_SLAVE_RATIO_0)

7.3.6.5 DDR PHY Data Macro 0/1 Write DQS Slave Ratio Register (DATA0/1_REG_PHY_WR_DQS_SLAVE_RATIO_0)

7.3.6.6 DDR PHY Data Macro 0/1 Write Leveling Init Ratio Register ( DATA0/1_REG_PHY_WRLVL_INIT_RATIO_0)

7.3.6.7 DDR PHY Data Macro 0 Write Leveling Init Mode Ratio Selection Register (DATA0/1_REG_PHY_WRLVL_INIT_MODE_0)

7.3.6.8 DDR PHY Data Macro 0 DQS Gate Training Init Ratio Register (DATA0_REG_PHY_GATELVL_INIT_RATIO_0)

7.3.6.9 DDR PHY Data Macro 0/1 DQS Gate Training Init Mode Ratio Selection Register (DATA0/1_REG_PHY_GATELVL_INIT_MODE_0)

7.3.6.10 DDR PHY Data Macro 0/1 DQS Gate Slave Ratio Register (DATA0/1_REG_PHY_FIFO_WE_SLAVE_RATIO_0)

7.3.6.11 DDR PHY Data Macro 0/1 Write Data Slave Ratio Register (DATA0/1_REG_PHY_WR_DATA_SLAVE_RATIO_0)

7.3.6.12 DDR PHY Data Macro 0/1 Delay Selection Register (DATA0/1_REG_PHY_USE_RANK0_DELAYS)

7.4 ELM

7.4.1 Introduction

7.4.1.1 ELM Features

7.4.1.2 Unsupported ELM Features

7.4.2 Integration

7.4.2.1 ELM Connectivity Attributes

7.4.2.2 ELM Clock and Reset Management

7.4.2.3 ELM Pin List

7.4.3 Functional Description

7.4.3.1 ELM Software Reset

7.4.3.2 ELM Power Management

7.4.3.3 ELM Interrupt Requests

7.4.3.4 Processing Initialization

7.4.3.5 Processing Sequence

7.4.3.6 Processing Completion

7.4.4 Basic Programming Model

7.4.4.1 ELM Low Level Programming Model

7.4.4.1.1 Processing Initialization

7.4.4.1.2 Read Results

7.4.4.2 Use Case: ELM Used in Continuous Mode

7.4.4.3 Use Case: ELM Used in Page Mode

7.4.5 ELM Registers

7.4.5.1 ELM Revision Register (ELM_REVISION)

7.4.5.2 ELM System Configuration Register (ELM_SYSCONFIG)

7.4.5.3 ELM System Status Register (ELM_SYSSTATUS)

7.4.5.4 ELM Interrupt Status Register (ELM_IRQSTATUS)

7.4.5.5 ELM Interrupt Enable Register (ELM_IRQENABLE)

7.4.5.6 ELM Location Configuration Register (ELM_LOCATION_CONFIG)

7.4.5.7 ELM Page Definition Register (ELM_PAGE_CTRL)

7.4.5.8 ELM_SYNDROME_FRAGMENT_0_i Register

7.4.5.9 ELM_SYNDROME_FRAGMENT_1_i Register

7.4.5.10 ELM_SYNDROME_FRAGMENT_2_i Register

7.4.5.11 ELM_SYNDROME_FRAGMENT_3_i Register

7.4.5.12 ELM_SYNDROME_FRAGMENT_4_i Register

7.4.5.13 ELM_SYNDROME_FRAGMENT_5_i Register

7.4.5.14 ELM_SYNDROME_FRAGMENT_6_i Register

7.4.5.15 ELM_LOCATION_STATUS_i Register

7.4.5.16 ELM_ERROR_LOCATION_0-15_i Registers

8 Power, Reset, and Clock Management (PRCM)

8.1 Power, Reset, and Clock Management

8.1.1 Introduction

8.1.2 Device Power-Management Architecture Building Blocks

8.1.3 Clock Management

8.1.3.1 Module Interface and Functional Clocks

8.1.3.2 Module-Level Clock Management

8.1.3.2.1 Master Standby Protocol

8.1.3.2.2 Slave Idle Protocol

8.1.3.3 Clock Domain

8.1.3.3.1 Clock Domain-Level Clock Management

8.1.4 Power Management

8.1.4.1 Power Domain

8.1.4.2 Power Domain Management

8.1.4.2.1 Power-Management Techniques

8.1.4.3 Power Modes

8.1.4.3.1 Active

8.1.4.3.2 Standby

8.1.4.3.3 Deepsleep0

8.1.4.3.4 Deepsleep1

8.1.4.3.5 Deepsleep2

8.1.4.3.6 RTC-Only

8.1.4.4 Main Oscillator Control During Deep Sleep

8.1.4.5 Wakeup Sources/Events

8.1.4.6 Functional Sequencing for Power Management with Cortex M3

8.1.4.6.1 Periodic Idling of Cortex A8 MPU

8.1.4.6.2 Sleep Sequencing

8.1.4.6.3 Wakeup Sequencing

8.1.5 PRCM Module Overview

8.1.5.1 Interface Descriptions

8.1.5.1.1 OCP Interfaces

8.1.5.1.2 OCP Slave Interfaces

8.1.5.1.3 Power Control Interface

8.1.5.1.4 Device Control Interface

8.1.5.1.5 Clocks Interface

8.1.5.1.6 Resets Interface

8.1.5.1.7 Modules Power Management Control Interface

8.1.5.1.8 Initiator Modules Interface

8.1.5.1.9 Targets Modules Interface

8.1.6 Clock Generation and Management

8.1.6.1 Terminology

8.1.6.2 Clock Structure

8.1.6.3 ADPLLS

8.1.6.3.1 Clock Functions

8.1.6.4 ADPLLLJ (Low Jitter DPLL)

8.1.6.4.1 Clock Functions

8.1.6.5 M2 and N2 Change On-the-Fly

8.1.6.6 Core PLL Description

8.1.6.6.1 Core PLL Configuration

8.1.6.7 Peripheral PLL Description

8.1.6.7.1 Configuring the Peripheral PLL

8.1.6.8 MPU PLL Description

8.1.6.8.1 Configuring the MPU PLL

8.1.6.9 Display PLL Description

8.1.6.9.1 Configuring the Display PLL

8.1.6.10 DDR PLL Description

8.1.6.10.1 Configuring the DDR PLL

8.1.6.11 CLKOUT Signals

8.1.6.12 Timer Clock Structure

8.1.7 Reset Management

8.1.7.1 Overview

8.1.7.2 Reset Concepts and Definitions

8.1.7.3 Global Power On Reset (Cold Reset)

8.1.7.3.1 Power On Reset (PORz)

8.1.7.3.2 PORz Sequence

8.1.7.3.3 Bad Device Reset

8.1.7.3.4 Global Cold Software Reset (GLOBAL_COLD_SW_RST)

8.1.7.4 Global Warm Reset

8.1.7.4.1 External Warm Reset

8.1.7.4.2 Watchdog Timer

8.1.7.4.3 Global Warm Software Reset (GLOBAL_SW_WARM_RST)

8.1.7.4.4 Test Reset (TRSTz)

8.1.7.5 Reset Characteristics

8.1.7.6 EMAC Switch Reset Isolation

8.1.7.7 Reset Priority

8.1.7.8 Trace Functionality Across Reset

8.1.7.9 RTC PORz

8.1.8 Power-Up/Down Sequence

8.1.9 IO State

8.1.10 Voltage and Power Domains

8.1.10.1 Voltage Domains

8.1.10.2 Power Domains

8.1.11 Device Modules and Power Management Attributes List

8.1.11.1 Power Domain Power Down Sequence

8.1.11.2 Power Domain Power-Up Sequence

8.1.12 Clock Module Registers

8.1.12.1 CM_PER Registers

8.1.12.1.1 CM_PER_L4LS_CLKSTCTRL Register (offset = 0h) [reset = C0102h]

8.1.12.1.2 CM_PER_L3S_CLKSTCTRL Register (offset = 4h) [reset = Ah]

8.1.12.1.3 CM_PER_L3_CLKSTCTRL Register (offset = Ch) [reset = 12h]

8.1.12.1.4 CM_PER_CPGMAC0_CLKCTRL Register (offset = 14h) [reset = 70000h]

8.1.12.1.5 CM_PER_LCDC_CLKCTRL Register (offset = 18h) [reset = 70000h]

8.1.12.1.6 CM_PER_USB0_CLKCTRL Register (offset = 1Ch) [reset = 70000h]

8.1.12.1.7 CM_PER_TPTC0_CLKCTRL Register (offset = 24h) [reset = 70000h]

8.1.12.1.8 CM_PER_EMIF_CLKCTRL Register (offset = 28h) [reset = 30000h]

8.1.12.1.9 CM_PER_OCMCRAM_CLKCTRL Register (offset = 2Ch) [reset = 30000h]

8.1.12.1.10 CM_PER_GPMC_CLKCTRL Register (offset = 30h) [reset = 30002h]

8.1.12.1.11 CM_PER_MCASP0_CLKCTRL Register (offset = 34h) [reset = 30000h]

8.1.12.1.12 CM_PER_UART5_CLKCTRL Register (offset = 38h) [reset = 30000h]

8.1.12.1.13 CM_PER_MMC0_CLKCTRL Register (offset = 3Ch) [reset = 30000h]

8.1.12.1.14 CM_PER_ELM_CLKCTRL Register (offset = 40h) [reset = 30000h]

8.1.12.1.15 CM_PER_I2C2_CLKCTRL Register (offset = 44h) [reset = 30000h]

8.1.12.1.16 CM_PER_I2C1_CLKCTRL Register (offset = 48h) [reset = 30000h]

8.1.12.1.17 CM_PER_SPI0_CLKCTRL Register (offset = 4Ch) [reset = 30000h]

8.1.12.1.18 CM_PER_SPI1_CLKCTRL Register (offset = 50h) [reset = 30000h]

8.1.12.1.19 CM_PER_L4LS_CLKCTRL Register (offset = 60h) [reset = 2h]

8.1.12.1.20 CM_PER_L4FW_CLKCTRL Register (offset = 64h) [reset = 2h]

8.1.12.1.21 CM_PER_MCASP1_CLKCTRL Register (offset = 68h) [reset = 30000h]

8.1.12.1.22 CM_PER_UART1_CLKCTRL Register (offset = 6Ch) [reset = 30000h]

8.1.12.1.23 CM_PER_UART2_CLKCTRL Register (offset = 70h) [reset = 30000h]

8.1.12.1.24 CM_PER_UART3_CLKCTRL Register (offset = 74h) [reset = 30000h]

8.1.12.1.25 CM_PER_UART4_CLKCTRL Register (offset = 78h) [reset = 30000h]

8.1.12.1.26 CM_PER_TIMER7_CLKCTRL Register (offset = 7Ch) [reset = 30000h]

8.1.12.1.27 CM_PER_TIMER2_CLKCTRL Register (offset = 80h) [reset = 30000h]

8.1.12.1.28 CM_PER_TIMER3_CLKCTRL Register (offset = 84h) [reset = 30000h]

8.1.12.1.29 CM_PER_TIMER4_CLKCTRL Register (offset = 88h) [reset = 30000h]

8.1.12.1.30 CM_PER_GPIO1_CLKCTRL Register (offset = ACh) [reset = 30000h]

8.1.12.1.31 CM_PER_GPIO2_CLKCTRL Register (offset = B0h) [reset = 30000h]

8.1.12.1.32 CM_PER_GPIO3_CLKCTRL Register (offset = B4h) [reset = 30000h]

8.1.12.1.33 CM_PER_TPCC_CLKCTRL Register (offset = BCh) [reset = 30000h]

8.1.12.1.34 CM_PER_DCAN0_CLKCTRL Register (offset = C0h) [reset = 30000h]

8.1.12.1.35 CM_PER_DCAN1_CLKCTRL Register (offset = C4h) [reset = 30000h]

8.1.12.1.36 CM_PER_EPWMSS1_CLKCTRL Register (offset = CCh) [reset = 30000h]

8.1.12.1.37 CM_PER_EPWMSS0_CLKCTRL Register (offset = D4h) [reset = 30000h]

8.1.12.1.38 CM_PER_EPWMSS2_CLKCTRL Register (offset = D8h) [reset = 30000h]

8.1.12.1.39 CM_PER_L3_INSTR_CLKCTRL Register (offset = DCh) [reset = 2h]

8.1.12.1.40 CM_PER_L3_CLKCTRL Register (offset = E0h) [reset = 2h]

8.1.12.1.41 CM_PER_IEEE5000_CLKCTRL Register (offset = E4h) [reset = 70002h]

8.1.12.1.42 CM_PER_PRU_ICSS_CLKCTRL Register (offset = E8h) [reset = 70000h]

8.1.12.1.43 CM_PER_TIMER5_CLKCTRL Register (offset = ECh) [reset = 30000h]

8.1.12.1.44 CM_PER_TIMER6_CLKCTRL Register (offset = F0h) [reset = 30000h]

8.1.12.1.45 CM_PER_MMC1_CLKCTRL Register (offset = F4h) [reset = 30000h]

8.1.12.1.46 CM_PER_MMC2_CLKCTRL Register (offset = F8h) [reset = 30000h]

8.1.12.1.47 CM_PER_TPTC1_CLKCTRL Register (offset = FCh) [reset = 70000h]

8.1.12.1.48 CM_PER_TPTC2_CLKCTRL Register (offset = 100h) [reset = 70000h]

8.1.12.1.49 CM_PER_SPINLOCK_CLKCTRL Register (offset = 10Ch) [reset = 30000h]

8.1.12.1.50 CM_PER_MAILBOX0_CLKCTRL Register (offset = 110h) [reset = 30000h]

8.1.12.1.51 CM_PER_L4HS_CLKSTCTRL Register (offset = 11Ch) [reset = 7Ah]

8.1.12.1.52 CM_PER_L4HS_CLKCTRL Register (offset = 120h) [reset = 2h]

8.1.12.1.53 CM_PER_OCPWP_L3_CLKSTCTRL Register (offset = 12Ch) [reset = 2h]

8.1.12.1.54 CM_PER_OCPWP_CLKCTRL Register (offset = 130h) [reset = 70002h]

8.1.12.1.55 CM_PER_PRU_ICSS_CLKSTCTRL Register (offset = 140h) [reset = 2h]

8.1.12.1.56 CM_PER_CPSW_CLKSTCTRL Register (offset = 144h) [reset = 2h]

8.1.12.1.57 CM_PER_LCDC_CLKSTCTRL Register (offset = 148h) [reset = 2h]

8.1.12.1.58 CM_PER_CLKDIV32K_CLKCTRL Register (offset = 14Ch) [reset = 30000h]

8.1.12.1.59 CM_PER_CLK_24MHZ_CLKSTCTRL Register (offset = 150h) [reset = 2h]

8.1.12.2 CM_WKUP Registers

8.1.12.2.1 CM_WKUP_CLKSTCTRL Register (offset = 0h) [reset = 6h]

8.1.12.2.2 CM_WKUP_CONTROL_CLKCTRL Register (offset = 4h) [reset = 30000h]

8.1.12.2.3 CM_WKUP_GPIO0_CLKCTRL Register (offset = 8h) [reset = 30000h]

8.1.12.2.4 CM_WKUP_L4WKUP_CLKCTRL Register (offset = Ch) [reset = 2h]

8.1.12.2.5 CM_WKUP_TIMER0_CLKCTRL Register (offset = 10h) [reset = 30002h]

8.1.12.2.6 CM_WKUP_DEBUGSS_CLKCTRL Register (offset = 14h) [reset = 52580002h]

8.1.12.2.7 CM_L3_AON_CLKSTCTRL Register (offset = 18h) [reset = 1Ah]

8.1.12.2.8 CM_AUTOIDLE_DPLL_MPU Register (offset = 1Ch) [reset = 0h]

8.1.12.2.9 CM_IDLEST_DPLL_MPU Register (offset = 20h) [reset = 0h]

8.1.12.2.10 CM_SSC_DELTAMSTEP_DPLL_MPU Register (offset = 24h) [reset = 0h]

8.1.12.2.11 CM_SSC_MODFREQDIV_DPLL_MPU Register (offset = 28h) [reset = 0h]

8.1.12.2.12 CM_CLKSEL_DPLL_MPU Register (offset = 2Ch) [reset = 0h]

8.1.12.2.13 CM_AUTOIDLE_DPLL_DDR Register (offset = 30h) [reset = 0h]

8.1.12.2.14 CM_IDLEST_DPLL_DDR Register (offset = 34h) [reset = 0h]

8.1.12.2.15 CM_SSC_DELTAMSTEP_DPLL_DDR Register (offset = 38h) [reset = 0h]

8.1.12.2.16 CM_SSC_MODFREQDIV_DPLL_DDR Register (offset = 3Ch) [reset = 0h]

8.1.12.2.17 CM_CLKSEL_DPLL_DDR Register (offset = 40h) [reset = 0h]

8.1.12.2.18 CM_AUTOIDLE_DPLL_DISP Register (offset = 44h) [reset = 0h]

8.1.12.2.19 CM_IDLEST_DPLL_DISP Register (offset = 48h) [reset = 0h]

8.1.12.2.20 CM_SSC_DELTAMSTEP_DPLL_DISP Register (offset = 4Ch) [reset = 0h]

8.1.12.2.21 CM_SSC_MODFREQDIV_DPLL_DISP Register (offset = 50h) [reset = 0h]

8.1.12.2.22 CM_CLKSEL_DPLL_DISP Register (offset = 54h) [reset = 0h]

8.1.12.2.23 CM_AUTOIDLE_DPLL_CORE Register (offset = 58h) [reset = 0h]

8.1.12.2.24 CM_IDLEST_DPLL_CORE Register (offset = 5Ch) [reset = 0h]

8.1.12.2.25 CM_SSC_DELTAMSTEP_DPLL_CORE Register (offset = 60h) [reset = 0h]

8.1.12.2.26 CM_SSC_MODFREQDIV_DPLL_CORE Register (offset = 64h) [reset = 0h]

8.1.12.2.27 CM_CLKSEL_DPLL_CORE Register (offset = 68h) [reset = 0h]

8.1.12.2.28 CM_AUTOIDLE_DPLL_PER Register (offset = 6Ch) [reset = 0h]

8.1.12.2.29 CM_IDLEST_DPLL_PER Register (offset = 70h) [reset = 0h]

8.1.12.2.30 CM_SSC_DELTAMSTEP_DPLL_PER Register (offset = 74h) [reset = 0h]

8.1.12.2.31 CM_SSC_MODFREQDIV_DPLL_PER Register (offset = 78h) [reset = 0h]

8.1.12.2.32 CM_CLKDCOLDO_DPLL_PER Register (offset = 7Ch) [reset = 0h]

8.1.12.2.33 CM_DIV_M4_DPLL_CORE Register (offset = 80h) [reset = 4h]

8.1.12.2.34 CM_DIV_M5_DPLL_CORE Register (offset = 84h) [reset = 4h]

8.1.12.2.35 CM_CLKMODE_DPLL_MPU Register (offset = 88h) [reset = 4h]

8.1.12.2.36 CM_CLKMODE_DPLL_PER Register (offset = 8Ch) [reset = 4h]

8.1.12.2.37 CM_CLKMODE_DPLL_CORE Register (offset = 90h) [reset = 4h]

8.1.12.2.38 CM_CLKMODE_DPLL_DDR Register (offset = 94h) [reset = 4h]

8.1.12.2.39 CM_CLKMODE_DPLL_DISP Register (offset = 98h) [reset = 4h]

8.1.12.2.40 CM_CLKSEL_DPLL_PERIPH Register (offset = 9Ch) [reset = 0h]

8.1.12.2.41 CM_DIV_M2_DPLL_DDR Register (offset = A0h) [reset = 1h]

8.1.12.2.42 CM_DIV_M2_DPLL_DISP Register (offset = A4h) [reset = 1h]

8.1.12.2.43 CM_DIV_M2_DPLL_MPU Register (offset = A8h) [reset = 1h]

8.1.12.2.44 CM_DIV_M2_DPLL_PER Register (offset = ACh) [reset = 1h]

8.1.12.2.45 CM_WKUP_WKUP_M3_CLKCTRL Register (offset = B0h) [reset = 2h]

8.1.12.2.46 CM_WKUP_UART0_CLKCTRL Register (offset = B4h) [reset = 30000h]

8.1.12.2.47 CM_WKUP_I2C0_CLKCTRL Register (offset = B8h) [reset = 30000h]

8.1.12.2.48 CM_WKUP_ADC_TSC_CLKCTRL Register (offset = BCh) [reset = 30000h]

8.1.12.2.49 CM_WKUP_SMARTREFLEX0_CLKCTRL Register (offset = C0h) [reset = 30000h]

8.1.12.2.50 CM_WKUP_TIMER1_CLKCTRL Register (offset = C4h) [reset = 30000h]

8.1.12.2.51 CM_WKUP_SMARTREFLEX1_CLKCTRL Register (offset = C8h) [reset = 30000h]

8.1.12.2.52 CM_L4_WKUP_AON_CLKSTCTRL Register (offset = CCh) [reset = 6h]

8.1.12.2.53 CM_WKUP_WDT1_CLKCTRL Register (offset = D4h) [reset = 30002h]

8.1.12.2.54 CM_DIV_M6_DPLL_CORE Register (offset = D8h) [reset = 4h]

8.1.12.3 CM_DPLL Registers

8.1.12.3.1 CLKSEL_TIMER7_CLK Register (offset = 4h) [reset = 1h]

8.1.12.3.2 CLKSEL_TIMER2_CLK Register (offset = 8h) [reset = 1h]

8.1.12.3.3 CLKSEL_TIMER3_CLK Register (offset = Ch) [reset = 1h]

8.1.12.3.4 CLKSEL_TIMER4_CLK Register (offset = 10h) [reset = 1h]

8.1.12.3.5 CM_MAC_CLKSEL Register (offset = 14h) [reset = 4h]

8.1.12.3.6 CLKSEL_TIMER5_CLK Register (offset = 18h) [reset = 1h]

8.1.12.3.7 CLKSEL_TIMER6_CLK Register (offset = 1Ch) [reset = 1h]

8.1.12.3.8 CM_CPTS_RFT_CLKSEL Register (offset = 20h) [reset = 0h]

8.1.12.3.9 CLKSEL_TIMER1MS_CLK Register (offset = 28h) [reset = 0h]

8.1.12.3.10 CLKSEL_GFX_FCLK Register (offset = 2Ch) [reset = 0h]

8.1.12.3.11 CLKSEL_PRU_ICSS_OCP_CLK Register (offset = 30h) [reset = 0h]

8.1.12.3.12 CLKSEL_LCDC_PIXEL_CLK Register (offset = 34h) [reset = 0h]

8.1.12.3.13 CLKSEL_WDT1_CLK Register (offset = 38h) [reset = 1h]

8.1.12.3.14 CLKSEL_GPIO0_DBCLK Register (offset = 3Ch) [reset = 0h]

8.1.12.4 CM_MPU Registers

8.1.12.4.1 CM_MPU_CLKSTCTRL Register (offset = 0h) [reset = 6h]

8.1.12.4.2 CM_MPU_MPU_CLKCTRL Register (offset = 4h) [reset = 2h]

8.1.12.5 CM_DEVICE Registers

8.1.12.5.1 CM_CLKOUT_CTRL Register (offset = 0h) [reset = 0h]

8.1.12.6 CM_RTC Registers

8.1.12.6.1 CM_RTC_RTC_CLKCTRL Register (offset = 0h) [reset = 30002h]

8.1.12.6.2 CM_RTC_CLKSTCTRL Register (offset = 4h) [reset = 102h]

8.1.12.7 CM_GFX Registers

8.1.12.7.1 CM_GFX_L3_CLKSTCTRL Register (offset = 0h) [reset = 2h]

8.1.12.7.2 CM_GFX_GFX_CLKCTRL Register (offset = 4h) [reset = 70000h]

8.1.12.7.3 CM_GFX_L4LS_GFX_CLKSTCTRL Register (offset = Ch) [reset = 102h]

8.1.12.7.4 CM_GFX_MMUCFG_CLKCTRL Register (offset = 10h) [reset = 30000h]

8.1.12.7.5 CM_GFX_MMUDATA_CLKCTRL Register (offset = 14h) [reset = 30000h]

8.1.12.8 CM_CEFUSE Registers

8.1.12.8.1 CM_CEFUSE_CLKSTCTRL Register (offset = 0h) [reset = 2h]

8.1.12.8.2 CM_CEFUSE_CEFUSE_CLKCTRL Register (offset = 20h) [reset = 30000h]

8.1.13 Power Management Registers

8.1.13.1 PRM_IRQ Registers

8.1.13.1.1 REVISION_PRM Register (offset = 0h) [reset = 0h]

8.1.13.1.2 PRM_IRQSTATUS_MPU Register (offset = 4h) [reset = 0h]

8.1.13.1.3 PRM_IRQENABLE_MPU Register (offset = 8h) [reset = 0h]

8.1.13.1.4 PRM_IRQSTATUS_M3 Register (offset = Ch) [reset = 0h]

8.1.13.1.5 PRM_IRQENABLE_M3 Register (offset = 10h) [reset = 0h]

8.1.13.2 PRM_PER Registers

8.1.13.2.1 RM_PER_RSTCTRL Register (offset = 0h) [reset = 2h]

8.1.13.2.2 PM_PER_PWRSTST Register (offset = 8h) [reset = 1E60007h]

8.1.13.2.3 PM_PER_PWRSTCTRL Register (offset = Ch) [reset = EE0000EBh]

8.1.13.3 PRM_WKUP Registers

8.1.13.3.1 RM_WKUP_RSTCTRL Register (offset = 0h) [reset = 8h]

8.1.13.3.2 PM_WKUP_PWRSTCTRL Register (offset = 4h) [reset = 8h]

8.1.13.3.3 PM_WKUP_PWRSTST Register (offset = 8h) [reset = 60004h]

8.1.13.3.4 RM_WKUP_RSTST Register (offset = Ch) [reset = 0h]

8.1.13.4 PRM_MPU Registers

8.1.13.4.1 PM_MPU_PWRSTCTRL Register (offset = 0h) [reset = 1FF0007h]

8.1.13.4.2 PM_MPU_PWRSTST Register (offset = 4h) [reset = 157h]

8.1.13.4.3 RM_MPU_RSTST Register (offset = 8h) [reset = 0h]

8.1.13.5 PRM_DEVICE Registers

8.1.13.5.1 PRM_RSTCTRL Register (offset = 0h) [reset = 0h]

8.1.13.5.2 PRM_RSTTIME Register (offset = 4h) [reset = 1006h]

8.1.13.5.3 PRM_RSTST Register (offset = 8h) [reset = 1h]

8.1.13.5.4 PRM_SRAM_COUNT Register (offset = Ch) [reset = 78000017h]

8.1.13.5.5 PRM_LDO_SRAM_CORE_SETUP Register (offset = 10h) [reset = 0h]

8.1.13.5.6 PRM_LDO_SRAM_CORE_CTRL Register (offset = 14h) [reset = 0h]

8.1.13.5.7 PRM_LDO_SRAM_MPU_SETUP Register (offset = 18h) [reset = 0h]

8.1.13.5.8 PRM_LDO_SRAM_MPU_CTRL Register (offset = 1Ch) [reset = 0h]

8.1.13.6 PRM_RTC Registers

8.1.13.6.1 PM_RTC_PWRSTCTRL Register (offset = 0h) [reset = 4h]

8.1.13.6.2 PM_RTC_PWRSTST Register (offset = 4h) [reset = 4h]

8.1.13.7 PRM_GFX Registers

8.1.13.7.1 PM_GFX_PWRSTCTRL Register (offset = 0h) [reset = 60044h]

8.1.13.7.2 RM_GFX_RSTCTRL Register (offset = 4h) [reset = 1h]

8.1.13.7.3 PM_GFX_PWRSTST Register (offset = 10h) [reset = 17h]

8.1.13.7.4 RM_GFX_RSTST Register (offset = 14h) [reset = 0h]

8.1.13.8 PRM_CEFUSE Registers

8.1.13.8.1 PM_CEFUSE_PWRSTCTRL Register (offset = 0h) [reset = 0h]

8.1.13.8.2 PM_CEFUSE_PWRSTST Register (offset = 4h) [reset = 7h]

9 Control Module

9.1 Introduction

9.2 Functional Description

9.2.1 Control Module Initialization

9.2.2 Pad Control Registers

9.2.2.1 Mode Selection

9.2.2.2 Pull Selection

9.2.3 EDMA Event Multiplexing

9.2.4 Device Control and Status

9.2.4.1 Control and Boot Status

9.2.4.2 Interprocessor Communication

9.2.4.3 Initiator Priority Control

9.2.4.3.1 Initiator Priority Control for Interconnect

9.2.4.3.2 Initiator Priority at EMIF

9.2.4.4 Peripheral Control and Status

9.2.4.4.1 USB Control and Status

9.2.4.4.2 USB Charger Detect

9.2.4.4.3 Ethernet MII Mode Selection

9.2.4.4.4 Ethernet Module Reset Isolation Control

9.2.4.4.5 Timer/eCAP Event Capture Control

9.2.4.4.6 ADC Capture Control

9.2.5 DDR PHY

9.2.5.1 DDR PHY to IO Pin Mapping

9.3 CONTROL_MODULE Registers

9.3.1 control_revision Register (offset = 0h) [reset = 0h]

9.3.2 device_id Register (offset = 600h) [reset = 0x]

9.3.3 control_hwinfo Register (offset = 4h) [reset = 0h]

9.3.4 control_sysconfig Register (offset = 10h) [reset = 0h]

9.3.5 control_status Register (offset = 40h) [reset = 0h]

9.3.6 cortex_vbbldo_ctrl Register (offset = 41Ch) [reset = 0h]

9.3.7 core_sldo_ctrl Register (offset = 428h) [reset = 0h]

9.3.8 mpu_sldo_ctrl Register (offset = 42Ch) [reset = 0h]

9.3.9 clk32kdivratio_ctrl Register (offset = 444h) [reset = 0h]

9.3.10 bandgap_ctrl Register (offset = 448h) [reset = 0h]

9.3.11 bandgap_trim Register (offset = 44Ch) [reset = 0h]

9.3.12 pll_clkinpulow_ctrl Register (offset = 458h) [reset = 0h]

9.3.13 mosc_ctrl Register (offset = 468h) [reset = 0h]

9.3.14 rcosc_ctrl Register (offset = 46Ch) [reset = 0h]

9.3.15 deepsleep_ctrl Register (offset = 470h) [reset = 0h]

9.3.16 dev_feature Register (offset = 604h) [reset = 0h]

9.3.17 init_priority_0 Register (offset = 608h) [reset = 0h]

9.3.18 init_priority_1 Register (offset = 60Ch) [reset = 0h]

9.3.19 mmu_cfg Register (offset = 610h) [reset = 0h]

9.3.20 tptc_cfg Register (offset = 614h) [reset = 0h]

9.3.21 usb_ctrl0 Register (offset = 620h) [reset = 0h]

9.3.22 usb_sts0 Register (offset = 624h) [reset = 0h]

9.3.23 usb_ctrl1 Register (offset = 628h) [reset = 0h]

9.3.24 usb_sts1 Register (offset = 62Ch) [reset = 0h]

9.3.25 mac_id0_lo Register (offset = 630h) [reset = 0h]

9.3.26 mac_id0_hi Register (offset = 634h) [reset = 0h]

9.3.27 mac_id1_lo Register (offset = 638h) [reset = 0h]

9.3.28 mac_id1_hi Register (offset = 63Ch) [reset = 0h]

9.3.29 dcan_raminit Register (offset = 644h) [reset = 0h]

9.3.30 usb_wkup_ctrl Register (offset = 648h) [reset = 0h]

9.3.31 gmii_sel Register (offset = 650h) [reset = 0h]

9.3.32 pwmss_ctrl Register (offset = 664h) [reset = 0h]

9.3.33 mreqprio_0 Register (offset = 670h) [reset = 0h]

9.3.34 mreqprio_1 Register (offset = 674h) [reset = 0h]

9.3.35 hw_event_sel_grp1 Register (offset = 690h) [reset = 0h]

9.3.36 hw_event_sel_grp2 Register (offset = 694h) [reset = 0h]

9.3.37 hw_event_sel_grp3 Register (offset = 698h) [reset = 0h]

9.3.38 hw_event_sel_grp4 Register (offset = 69Ch) [reset = 0h]

9.3.39 smrt_ctrl Register (offset = 6A0h) [reset = 0h]

9.3.40 mpuss_hw_debug_sel Register (offset = 6A4h) [reset = 0h]

9.3.41 mpuss_hw_dbg_info Register (offset = 6A8h) [reset = 0h]

9.3.42 vdd_mpu_opp_050 Register (offset = 770h) [reset = 0h]

9.3.43 vdd_mpu_opp_100 Register (offset = 774h) [reset = 0h]

9.3.44 vdd_mpu_opp_120 Register (offset = 778h) [reset = 0h]

9.3.45 vdd_mpu_opp_turbo Register (offset = 77Ch) [reset = 0h]

9.3.46 vdd_core_opp_050 Register (offset = 7B8h) [reset = 0h]

9.3.47 vdd_core_opp_100 Register (offset = 7BCh) [reset = 0h]

9.3.48 bb_scale Register (offset = 7D0h) [reset = 0h]

9.3.49 usb_vid_pid Register (offset = 7F4h) [reset = 4516141h]

9.3.50 conf__ Register (offset = 800h) 9.3.51 cqdetect_status Register (offset = E00h) [reset = 0h]

9.3.52 ddr_io_ctrl Register (offset = E04h) [reset = 0h]

9.3.53 vtp_ctrl Register (offset = E0Ch) [reset = 0h]

9.3.54 vref_ctrl Register (offset = E14h) [reset = 0h]

9.3.55 tpcc_evt_mux_0_3 Register (offset = F90h) [reset = 0h]

9.3.56 tpcc_evt_mux_4_7 Register (offset = F94h) [reset = 0h]

9.3.57 tpcc_evt_mux_8_11 Register (offset = F98h) [reset = 0h]

9.3.58 tpcc_evt_mux_12_15 Register (offset = F9Ch) [reset = 0h]

9.3.59 tpcc_evt_mux_16_19 Register (offset = FA0h) [reset = 0h]

9.3.60 tpcc_evt_mux_20_23 Register (offset = FA4h) [reset = 0h]

9.3.61 tpcc_evt_mux_24_27 Register (offset = FA8h) [reset = 0h]

9.3.62 tpcc_evt_mux_28_31 Register (offset = FACh) [reset = 0h]

9.3.63 tpcc_evt_mux_32_35 Register (offset = FB0h) [reset = 0h]

9.3.64 tpcc_evt_mux_36_39 Register (offset = FB4h) [reset = 0h]

9.3.65 tpcc_evt_mux_40_43 Register (offset = FB8h) [reset = 0h]

9.3.66 tpcc_evt_mux_44_47 Register (offset = FBCh) [reset = 0h]

9.3.67 tpcc_evt_mux_48_51 Register (offset = FC0h) [reset = 0h]

9.3.68 tpcc_evt_mux_52_55 Register (offset = FC4h) [reset = 0h]

9.3.69 tpcc_evt_mux_56_59 Register (offset = FC8h) [reset = 0h]

9.3.70 tpcc_evt_mux_60_63 Register (offset = FCCh) [reset = 0h]

9.3.71 timer_evt_capt Register (offset = FD0h) [reset = 0h]

9.3.72 ecap_evt_capt Register (offset = FD4h) [reset = 0h]

9.3.73 adc_evt_capt Register (offset = FD8h) [reset = 0h]

9.3.74 reset_iso Register (offset = 1000h) [reset = 0h]

9.3.75 ddr_cke_ctrl Register (offset = 131Ch) [reset = 0h]

9.3.76 sma2 Register (offset = 1320h) [reset = 0h]

9.3.77 m3_txev_eoi Register (offset = 1324h) [reset = 0h]

9.3.78 ipc_msg_reg0 Register (offset = 1328h) [reset = 0h]

9.3.79 ipc_msg_reg1 Register (offset = 132Ch) [reset = 0h]

9.3.80 ipc_msg_reg2 Register (offset = 1330h) [reset = 0h]

9.3.81 ipc_msg_reg3 Register (offset = 1334h) [reset = 0h]

9.3.82 ipc_msg_reg4 Register (offset = 1338h) [reset = 0h]

9.3.83 ipc_msg_reg5 Register (offset = 133Ch) [reset = 0h]

9.3.84 ipc_msg_reg6 Register (offset = 1340h) [reset = 0h]

9.3.85 ipc_msg_reg7 Register (offset = 1344h) [reset = 0h]

9.3.86 ddr_cmd0_ioctrl Register (offset = 1404h) [reset = 0h]

9.3.87 ddr_cmd1_ioctrl Register (offset = 1408h) [reset = 0h]

9.3.88 ddr_cmd2_ioctrl Register (offset = 140Ch) [reset = 0h]

9.3.89 ddr_data0_ioctrl Register (offset = 1440h) [reset = 0h]

9.3.90 ddr_data1_ioctrl Register (offset = 1444h) [reset = 0h]

10 Interconnects

10.1 Introduction

10.1.1 Terminology

10.1.2 L3 Interconnect

10.1.2.1 L3 Topology

10.1.2.2 L3 Port Mapping

10.1.2.3 Interconnect Requirements

10.1.2.4 ConnID Assignment

10.1.3 L4 Interconnect

11 Enhanced Direct Memory Access (EDMA)

11.1 Introduction

11.1.1 EDMA3 Controller Block Diagram

11.1.2 Third-Party Channel Controller (TPCC) Overview

11.1.2.1 TPCC Features

11.1.2.2 Unsupported TPCC Features

11.1.3 Third-Party Transfer Controller (TPTC) Overview

11.1.3.1 TPTC Features

11.1.3.2 Unsupported TPTC Features

11.2 Integration

11.2.1 Third-Party Channel Controller (TPCC) Integration

11.2.1.1 TPCC Connectivity Attributes

11.2.1.2 TPCC Clock and Reset Management

11.2.1.3 TPCC Pin List

11.2.2 Third-Party Transfer Controller (TPTC) Integration

11.2.2.1 TPTC Connectivity Attributes

11.2.2.2 TPTC Clock and Reset Management

11.2.2.3 TPTC Pin List

11.3 Functional Description

11.3.1 Functional Overview

11.3.1.1 EDMA3 Channel Controller (EDMA3CC)

11.3.1.2 EDMA3 Transfer Controller (EDMA3TC)

11.3.2 Types of EDMA3 Transfers

11.3.2.1 A-Synchronized Transfers

11.3.2.2 AB-Synchronized Transfers

11.3.3 Parameter RAM (PaRAM)

11.3.3.1 PaRAM

11.3.3.2 EDMA3 Channel PaRAM Set Entry Fields

11.3.3.2.1 Channel Options Parameter (OPT)

11.3.3.2.2 Channel Source Address (SRC)

11.3.3.2.3 Channel Destination Address (DST)

11.3.3.2.4 Count for 1st Dimension (ACNT)

11.3.3.2.5 Count for 2nd Dimension (BCNT)

11.3.3.2.6 Count for 3rd Dimension (CCNT)

11.3.3.2.7 BCNT Reload (BCNTRLD)

11.3.3.2.8 Source B Index (SRCBIDX)

11.3.3.2.9 Destination B Index (DSTBIDX)

11.3.3.2.10 Source C Index (SRCCIDX)

11.3.3.2.11 Destination C Index (DSTCIDX)

11.3.3.2.12 Link Address (LINK)

11.3.3.3 Null PaRAM Set

11.3.3.4 Dummy PaRAM Set

11.3.3.5 Dummy Versus Null Transfer Comparison

11.3.3.6 Parameter Set Updates

11.3.3.7 Linking Transfers

11.3.3.8 Constant Addressing Mode Transfers/Alignment Issues

11.3.3.9 Element Size

11.3.4 Initiating a DMA Transfer

11.3.4.1 DMA Channel

11.3.4.1.1 Event-Triggered Transfer Request

11.3.4.1.2 Manually Triggered Transfer Request

11.3.4.1.3 Chain-Triggered Transfer Request

11.3.4.2 QDMA Channels

11.3.4.2.1 Auto-triggered and Link-Triggered Transfer Request

11.3.4.3 Comparison Between DMA and QDMA Channels

11.3.5 Completion of a DMA Transfer

11.3.5.1 Normal Completion

11.3.5.2 Early Completion

11.3.5.3 Dummy or Null Completion

11.3.6 Event, Channel, and PaRAM Mapping

11.3.6.1 DMA Channel to PaRAM Mapping

11.3.6.2 QDMA Channel to PaRAM Mapping

11.3.7 EDMA3 Channel Controller Regions

11.3.7.1 Region Overview

11.3.7.2 Channel Controller Regions

11.3.7.3 Region Interrupts

11.3.8 Chaining EDMA3 Channels

11.3.9 EDMA3 Interrupts

11.3.9.1 Transfer Completion Interrupts

11.3.9.1.1 Enabling Transfer Completion Interrupts

11.3.9.1.2 Clearing Transfer Completion Interrupts

11.3.9.2 EDMA3 Interrupt Servicing

11.3.9.3 Interrupt Evaluation Operations

11.3.9.4 Error Interrupts

11.3.10 Memory Protection

11.3.10.1 Active Memory Protection

11.3.10.2 Proxy Memory Protection

11.3.11 Event Queue(s)

11.3.11.1 DMA/QDMA Channel to Event Queue Mapping

11.3.11.2 Queue RAM Debug Visibility

11.3.11.3 Queue Resource Tracking

11.3.11.4 Performance Considerations

11.3.12 EDMA3 Transfer Controller (EDMA3TC)

11.3.12.1 Architecture Details

11.3.12.1.1 Command Fragmentation

11.3.12.1.2 TR Pipelining

11.3.12.1.3 Performance Tuning

11.3.12.2 Memory Protection

11.3.12.3 Error Generation

11.3.12.4 Debug Features

11.3.12.4.1 Destination FIFO Register Pointer

11.3.12.5 EDMA3TC Configuration

11.3.13 Event Dataflow

11.3.14 EDMA3 Prioritization

11.3.14.1 Channel Priority

11.3.14.2 Trigger Source Priority

11.3.14.3 Dequeue Priority

11.3.14.4 System (Transfer Controller) Priority

11.3.15 EDMA3 Operating Frequency (Clock Control)

11.3.16 Reset Considerations

11.3.17 Power Management

11.3.18 Emulation Considerations

11.3.19 EDMA Transfer Examples

11.3.19.1 Block Move Example

11.3.19.2 Subframe Extraction Example

11.3.19.3 Data Sorting Example

11.3.19.4 Peripheral Servicing Example

11.3.19.4.1 Non-bursting Peripherals

11.3.19.4.2 Bursting Peripherals

11.3.19.4.3 Continuous Operation

11.3.19.4.4 Ping-Pong Buffering

11.3.19.4.5 Transfer Chaining Examples

11.3.20 EDMA Events

11.4 EDMA3 Registers

11.4.1 EDMA3 Channel Controller Registers

11.4.1.1 Global Registers

11.4.1.1.1 Peripheral Identification Register (PID)

11.4.1.1.2 EDMA3CC Configuration Register (CCCFG)

11.4.1.1.3 EDMA3CC System Configuration Register (SYSCONFIG)

11.4.1.1.4 DMA Channel Map n Registers (DCHMAPn)

11.4.1.1.5 QDMA Channel Map n Registers (QCHMAPn)

11.4.1.1.6 DMA Channel Queue n Number Registers (DMAQNUMn)

11.4.1.1.7 QDMA Channel Queue Number Register (QDMAQNUM)

11.4.1.1.8 Queue Priority Register (QUEPRI)

11.4.1.2 Error Registers

11.4.1.2.1 Event Missed Registers (EMR/EMRH)

11.4.1.2.2 Event Missed Clear Registers (EMCR/EMCRH)

11.4.1.2.3 QDMA Event Missed Register (QEMR)

11.4.1.2.4 QDMA Event Missed Clear Register (QEMCR)

11.4.1.2.5 EDMA3CC Error Register (CCERR)

11.4.1.2.6 EDMA3CC Error Clear Register (CCERRCLR)

11.4.1.2.7 Error Evaluation Register (EEVAL)

11.4.1.3 Region Access Enable Registers

11.4.1.3.1 DMA Region Access Enable for Region m (DRAEm)

11.4.1.3.2 QDMA Region Access Enable Registers (QRAEm)

11.4.1.4 Status/Debug Visibility Registers

11.4.1.4.1 Event Queue Entry Registers (QxEy)

11.4.1.4.2 Queue Status Registers (QSTATn)

11.4.1.4.3 Queue Watermark Threshold A Register (QWMTHRA)

11.4.1.4.4 EDMA3CC Status Register (CCSTAT)

11.4.1.5 Memory Protection Address Space

11.4.1.5.1 Memory Protection Fault Address Register (MPFAR)

11.4.1.5.2 Memory Protection Fault Status Register (MPFSR)

11.4.1.5.3 Memory Protection Fault Command Register (MPFCR)

11.4.1.5.4 Memory Protection Page Attribute Register (MPPAn)

11.4.1.6 DMA Channel Registers

11.4.1.6.1 Event Registers (ER, ERH)

11.4.1.6.2 Event Clear Registers (ECR, ECRH)

11.4.1.6.3 Event Set Registers (ESR, ESRH)

11.4.1.6.4 Chained Event Registers (CER, CERH)

11.4.1.6.5 Event Enable Registers (EER, EERH)

11.4.1.6.6 Event Enable Clear Register (EECR, EECRH)

11.4.1.6.7 Event Enable Set Registers (EESR, EESRH)

11.4.1.6.8 Secondary Event Registers (SER, SERH)

11.4.1.6.9 Secondary Event Clear Registers (SECR, SECRH)

11.4.1.7 Interrupt Registers

11.4.1.7.1 Interrupt Enable Registers (IER, IERH)

11.4.1.7.2 Interrupt Enable Clear Register (IECR, IECRH)

11.4.1.7.3 Interrupt Enable Set Registers (IESR, IESRH)

11.4.1.7.4 Interrupt Pending Register (IPR, IPRH)

11.4.1.7.5 Interrupt Clear Registers (ICR, ICRH)

11.4.1.7.6 Interrupt Evaluate Register (IEVAL)

11.4.1.8 QDMA Registers

11.4.1.8.1 QDMA Event Register (QER)

11.4.1.8.2 QDMA Event Enable Register (QEER)

11.4.1.8.3 QDMA Event Enable Clear Register (QEECR)

11.4.1.8.4 QDMA Event Enable Set Register (QEESR)

11.4.1.8.5 QDMA Secondary Event Register (QSER)

11.4.1.8.6 QDMA Secondary Event Clear Register (QSECR)

11.4.2 EDMA3 Transfer Controller Registers

11.4.2.1 Peripheral Identification Register (PID)

11.4.2.2 EDMA3TC Configuration Register (TCCFG)

11.4.2.3 EDMA3TC Channel Status Register (TCSTAT)

11.4.2.4 Error Registers

11.4.2.4.1 Error Register (ERRSTAT)

11.4.2.4.2 Error Enable Register (ERREN)

11.4.2.4.3 Error Clear Register (ERRCLR)

11.4.2.4.4 Error Details Register (ERRDET)

11.4.2.4.5 Error Interrupt Command Register (ERRCMD)

11.4.2.5 Read Rate Register (RDRATE)

11.4.2.6 EDMA3TC Channel Registers

11.4.2.6.1 Source Active Options Register (SAOPT)

11.4.2.6.2 Source Active Source Address Register (SASRC)

11.4.2.6.3 Source Active Count Register (SACNT)

11.4.2.6.4 Source Active Destination Address Register (SADST)

11.4.2.6.5 Source Active Source B-Dimension Index Register (SABIDX)

11.4.2.6.6 Source Active Memory Protection Proxy Register (SAMPPRXY)

11.4.2.6.7 Source Active Count Reload Register (SACNTRLD)

11.4.2.6.8 Source Active Source Address B-Reference Register (SASRCBREF)

11.4.2.6.9 Source Active Destination Address B-Reference Register (SADSTBREF)

11.4.2.6.10 Destination FIFO Options Register (DFOPTn)

11.4.2.6.11 Destination FIFO Source Address Register (DFSRCn)

11.4.2.6.12 Destination FIFO Count Register (DFCNTn)

11.4.2.6.13 Destination FIFO Destination Address Register (DFDSTn)

11.4.2.6.14 Destination FIFO B-Index Register (DFBIDXn)

11.4.2.6.15 Destination FIFO Memory Protection Proxy Register (DFMPPRXYn)

11.4.2.6.16 Destination FIFO Count Reload Register (DFCNTRLDn)

11.4.2.6.17 Destination FIFO Source Address B-Reference Register (DFSRCBREFn)

11.4.2.6.18 Destination FIFO Destination Address B-Reference (DFDSTBREFn)

11.5 Appendix A

11.5.1 Debug Checklist

11.5.2 Miscellaneous Programming/Debug Tips

11.5.3 Setting Up a Transfer

12 Touchscreen Controller

12.1 Introduction

12.1.1 TSC_ADC Features

12.1.2 Unsupported TSC_ADC_SS Features

12.2 Integration

12.2.1 TSC_ADC Connectivity Attributes

12.2.2 TSC_ADC Clock and Reset Management

12.2.3 TSC_ADC Pin List

12.3 Functional Description

12.3.1 HW Synchronized or SW Channels

12.3.2 Open Delay and Sample Delay

12.3.3 Averaging of Samples (1, 2, 4, 8, and 16)

12.3.4 One-Shot (Single) or Continuous Mode

12.3.5 Interrupts

12.3.6 DMA Requests

12.3.7 Analog Front End (AFE) Functional Block Diagram

12.4 Operational Modes

12.4.1 PenCtrl and PenIRQ

12.5 Touchscreen Controller Registers

12.5.1 TSC_ADC_SS Registers

12.5.1.1 REVISION Register (offset = 0h) [reset = 47300001h]

12.5.1.2 SYSCONFIG Register (offset = 10h) [reset = 0h]

12.5.1.3 IRQSTATUS_RAW Register (offset = 24h) [reset = 0h]

12.5.1.4 IRQSTATUS Register (offset = 28h) [reset = 0h]

12.5.1.5 IRQENABLE_SET Register (offset = 2Ch) [reset = 0h]

12.5.1.6 IRQENABLE_CLR Register (offset = 30h) [reset = 0h]

12.5.1.7 IRQWAKEUP Register (offset = 34h) [reset = 0h]

12.5.1.8 DMAENABLE_SET Register (offset = 38h) [reset = 0h]

12.5.1.9 DMAENABLE_CLR Register (offset = 3Ch) [reset = 0h]

12.5.1.10 CTRL Register (offset = 40h) [reset = 0h]

12.5.1.11 ADCSTAT Register (offset = 44h) [reset = 10h]

12.5.1.12 ADCRANGE Register (offset = 48h) [reset = 0h]

12.5.1.13 ADC_CLKDIV Register (offset = 4Ch) [reset = 0h]

12.5.1.14 ADC_MISC Register (offset = 50h) [reset = 0h]

12.5.1.15 STEPENABLE Register (offset = 54h) [reset = 0h]

12.5.1.16 IDLECONFIG Register (offset = 58h) [reset = 0h]

12.5.1.17 TS_CHARGE_STEPCONFIG Register (offset = 5Ch) [reset = 0h]

12.5.1.18 TS_CHARGE_DELAY Register (offset = 60h) [reset = 1h]

12.5.1.19 STEPCONFIG1 Register (offset = 64h) [reset = 0h]

12.5.1.20 STEPDELAY1 Register (offset = 68h) [reset = 0h]

12.5.1.21 STEPCONFIG2 Register (offset = 6Ch) [reset = 0h]

12.5.1.22 STEPDELAY2 Register (offset = 70h) [reset = 0h]

12.5.1.23 STEPCONFIG3 Register (offset = 74h) [reset = 0h]

12.5.1.24 STEPDELAY3 Register (offset = 78h) [reset = 0h]

12.5.1.25 STEPCONFIG4 Register (offset = 7Ch) [reset = 0h]

12.5.1.26 STEPDELAY4 Register (offset = 80h) [reset = 0h]

12.5.1.27 STEPCONFIG5 Register (offset = 84h) [reset = 0h]

12.5.1.28 STEPDELAY5 Register (offset = 88h) [reset = 0h]

12.5.1.29 STEPCONFIG6 Register (offset = 8Ch) [reset = 0h]

12.5.1.30 STEPDELAY6 Register (offset = 90h) [reset = 0h]

12.5.1.31 STEPCONFIG7 Register (offset = 94h) [reset = 0h]

12.5.1.32 STEPDELAY7 Register (offset = 98h) [reset = 0h]

12.5.1.33 STEPCONFIG8 Register (offset = 9Ch) [reset = 0h]

12.5.1.34 STEPDELAY8 Register (offset = A0h) [reset = 0h]

12.5.1.35 STEPCONFIG9 Register (offset = A4h) [reset = 0h]

12.5.1.36 STEPDELAY9 Register (offset = A8h) [reset = 0h]

12.5.1.37 STEPCONFIG10 Register (offset = ACh) [reset = 0h]

12.5.1.38 STEPDELAY10 Register (offset = B0h) [reset = 0h]

12.5.1.39 STEPCONFIG11 Register (offset = B4h) [reset = 0h]

12.5.1.40 STEPDELAY11 Register (offset = B8h) [reset = 0h]

12.5.1.41 STEPCONFIG12 Register (offset = BCh) [reset = 0h]

12.5.1.42 STEPDELAY12 Register (offset = C0h) [reset = 0h]

12.5.1.43 STEPCONFIG13 Register (offset = C4h) [reset = 0h]

12.5.1.44 STEPDELAY13 Register (offset = C8h) [reset = 0h]

12.5.1.45 STEPCONFIG14 Register (offset = CCh) [reset = 0h]

12.5.1.46 STEPDELAY14 Register (offset = D0h) [reset = 0h]

12.5.1.47 STEPCONFIG15 Register (offset = D4h) [reset = 0h]

12.5.1.48 STEPDELAY15 Register (offset = D8h) [reset = 0h]

12.5.1.49 STEPCONFIG16 Register (offset = DCh) [reset = 0h]

12.5.1.50 STEPDELAY16 Register (offset = E0h) [reset = 0h]

12.5.1.51 FIFO0COUNT Register (offset = E4h) [reset = 0h]

12.5.1.52 FIFO0THRESHOLD Register (offset = E8h) [reset = 0h]

12.5.1.53 DMA0REQ Register (offset = ECh) [reset = 0h]

12.5.1.54 FIFO1COUNT Register (offset = F0h) [reset = 0h]

12.5.1.55 FIFO1THRESHOLD Register (offset = F4h) [reset = 0h]

12.5.1.56 DMA1REQ Register (offset = F8h) [reset = 0h]

12.5.1.57 FIFO0DATA Register (offset = 100h) [reset = 0h]

12.5.1.58 FIFO1DATA Register (offset = 200h) [reset = 0h]

13 LCD Controller

13.1 Introduction

13.1.1 Purpose of the Peripheral

13.1.2 Features

13.2 Integration

13.2.1 LCD Controller Connectivity Attributes

13.2.2 LCD Controller Clock and Reset Management

13.2.3 LCD Controller Pin List

13.3 Functional Description

13.3.1 Clocking

13.3.1.1 Pixel Clock (LCD_PCLK)

13.3.1.2 Horizontal Clock (LCD_HSYNC)

13.3.1.3 Vertical Clock (LCD_VSYNC)

13.3.1.4 LCD_AC_BIAS_EN

13.3.2 LCD External I/O Signals

13.3.3 DMA Engine

13.3.3.1 Interrupts

13.3.3.1.1 LIDD Mode

13.3.3.1.2 Raster Mode

13.3.3.1.3 Interrupt Handling

13.3.4 LIDD Controller

13.3.5 Raster Controller

13.3.5.1 Logical Data Path

13.3.5.2 Frame Buffer

13.3.5.3 Palette

13.3.5.4 Gray-Scaler/Serializer

13.3.5.4.1 Passive (STN) Mode

13.3.5.4.2 Active (TFT) Mode

13.3.5.4.3 Summary of Color Depth

13.3.5.5 Output Format

13.3.5.5.1 Passive (STN) Mode

13.3.5.5.2 Active (TFT) Mode

13.3.5.6 Subpicture Feature

13.3.6 Interrupt Conditions

13.3.6.1 Highlander 0.8 Interrupts

13.3.6.1.1 Highlander Interrupt Basics

13.3.6.1.2 Raw Status Register

13.3.6.1.3 Masked Status Register

13.3.6.1.4 Interrupt Enable Set Register

13.3.6.1.5 Interrupt Enable Clear Register

13.3.6.1.6 End of Interrupt Register

13.3.6.2 Interrupt Sources

13.3.6.2.1 Overview of Interrupt Sources

13.3.7 DMA

13.3.8 Power Management

13.4 Programming Model

13.4.1 LCD Character Displays

13.4.1.1 Configuration Registers, Setup, and Settings

13.4.1.1.1 Configuration Registers

13.4.1.1.2 Defining Panel Commands and Panel Data

13.4.1.2 CPU Initiated Data Bus Transactions

13.4.1.2.1 Initiating Data Bus Transactions

13.4.1.3 DMA Initiated Data Bus Transactions for LIDD

13.4.1.3.1 DMA Overview for MPU Bus Output

13.4.1.3.2 MCU/LIDD DMA Setup: Example Pseudo Code

13.4.1.4 Passive Matrix

13.4.1.4.1 Monochrome Bitrate Awareness

13.4.2 Active Matrix Displays

13.4.2.1 Interfacing to Dual LVDS Transmitters

13.4.3 System Interaction

13.4.3.1 DMA End of Frame Interrupts

13.4.4 Palette Lookup

13.4.5 Test Logic

13.4.6 Disable and Software Reset Sequence

13.4.7 Precedence Order for Determining Frame Buffer Type

13.5 LCD Registers

13.5.1 PID Register (offset = 0h) [reset = 0h]

13.5.2 CTRL Register (offset = 4h) [reset = 0h]

13.5.3 LIDD_CTRL Register (offset = Ch) [reset = 0h]

13.5.4 LIDD_CS0_CONF Register (offset = 10h) [reset = 0h]

13.5.5 LIDD_CS0_ADDR Register (offset = 14h) [reset = 0h]

13.5.6 LIDD_CS0_DATA Register (offset = 18h) [reset = 0h]

13.5.7 LIDD_CS1_CONF Register (offset = 1Ch) [reset = 0h]

13.5.8 LIDD_CS1_ADDR Register (offset = 20h) [reset = 0h]

13.5.9 LIDD_CS1_DATA Register (offset = 24h) [reset = 0h]

13.5.10 RASTER_CTRL Register (offset = 28h) [reset = 0h]

13.5.11 RASTER_TIMING_0 Register (offset = 2Ch) [reset = 0h]

13.5.12 RASTER_TIMING_1 Register (offset = 30h) [reset = 0h]

13.5.13 RASTER_TIMING_2 Register (offset = 34h) [reset = 0h]

13.5.14 RASTER_SUBPANEL Register (offset = 38h) [reset = 0h]

13.5.15 RASTER_SUBPANEL2 Register (offset = 3Ch) [reset = 0h]

13.5.16 LCDDMA_CTRL Register (offset = 40h) [reset = 0h]

13.5.17 LCDDMA_FB0_BASE Register (offset = 44h) [reset = 0h]

13.5.18 LCDDMA_FB0_CEILING Register (offset = 48h) [reset = 0h]

13.5.19 LCDDMA_FB1_BASE Register (offset = 4Ch) [reset = 0h]

13.5.20 LCDDMA_FB1_CEILING Register (offset = 50h) [reset = 0h]

13.5.21 SYSCONFIG Register (offset = 54h) [reset = 0h]

13.5.22 IRQSTATUS_RAW Register (offset = 58h) [reset = 0h]

13.5.23 IRQSTATUS Register (offset = 5Ch) [reset = 0h]

13.5.24 IRQENABLE_SET Register (offset = 60h) [reset = 0h]

13.5.25 IRQENABLE_CLEAR Register (offset = 64h) [reset = 0h]

13.5.26 CLKC_ENABLE Register (offset = 6Ch) [reset = 0h]

13.5.27 CLKC_RESET Register (offset = 70h) [reset = 0h]

14 Ethernet Subsystem

14.1 Introduction

14.1.1 Features

14.1.2 Unsupported Features

14.2 Integration

14.2.1 Ethernet Switch Connectivity Attributes

14.2.2 Ethernet Switch Clock and Reset Management

14.2.3 Ethernet Switch Pin List

14.2.4 Ethernet Switch RMII Clocking Details

14.2.5 GMII Interface Signal Connections and Descriptions

14.2.5.1 GMII Interface Signal Descriptions in GIG (1000Mbps) Mode

14.2.5.2

14.2.6 RMII Signal Connections and Descriptions

14.2.7 RGMII Signal Connections and Descriptions

14.3 Functional Description

14.3.1 CPSW_3G Subsystem

14.3.1.1 Interrupt Pacing

14.3.1.2 Reset Isolation

14.3.1.2.1 Modes of Operation

14.3.1.3 Interrupts

14.3.1.3.1 Receive Packet Completion Pulse Interrupt (RX_PULSE)

14.3.1.3.2 Transmit Packet Completion Pulse Interrupt (TX_PULSE)

14.3.1.3.3 Receive Threshold Pulse Interrupt (RX_THRESH_PULSE)

14.3.1.3.4 Miscellaneous Pulse Interrupt (MISC_PULSE)

14.3.1.4 Embedded Memories

14.3.2 CPSW_3G

14.3.2.1 Media Independent Interface (GMII)

14.3.2.2 IEEE 1588v2 Clock Synchronization Support

14.3.2.2.1 IEEE 1588v2 Receive Packet Operation

14.3.2.2.2 IEEE 1588v2 Transmit Packet Operation

14.3.2.3 Device Level Ring (DLR) Support

14.3.2.4 CPDMA RX and TX Interfaces

14.3.2.4.1 CPPI Buffer Descriptors

14.3.2.4.2 Receive DMA Interface

14.3.2.4.3 Transmit DMA Interface

14.3.2.4.4 Transmit Rate Limiting

14.3.2.4.5 Command IDLE

14.3.2.5 VLAN Aware Mode

14.3.2.6 VLAN Unaware Mode

14.3.2.7 Address Lookup Engine (ALE)

14.3.2.7.1 Address Table Entry

14.3.2.7.2 Packet Forwarding Processes

14.3.2.7.3 Learning/Updating/Touching Processes

14.3.2.8 Packet Priority Handling

14.3.2.9 FIFO Memory Control

14.3.2.10 FIFO Transmit Queue Control

14.3.2.10.1 Normal Priority Mode

14.3.2.10.2 Dual Mac Mode

14.3.2.10.3 Rate Limit Mode

14.3.2.11 Packet Padding

14.3.2.12 Flow Control

14.3.2.12.1 CPPI Port Flow Control

14.3.2.12.2 Ethernet Port Flow Control

14.3.2.13 Packet Drop Interface

14.3.2.14 Short Gap

14.3.2.15 Switch Latency

14.3.2.16 Emulation Control

14.3.2.17 Software IDLE

14.3.2.18 Software Reset

14.3.2.19 FIFO Loopback

14.3.2.20 CPSW_3G Network Statistics

14.3.2.20.1 Rx-only Statistics Descriptions

14.3.2.20.2 Tx-only Statistics Descriptions

14.3.2.20.3 Rx- and Tx-Shared Statistics Descriptions

14.3.3 Ethernet Mac Sliver (CPGMAC_SL)

14.3.3.1 GMII/MII Media Independent Interface

14.3.3.1.1 Data Reception

14.3.3.1.2 Data Transmission

14.3.3.2 Frame Classification

14.3.4 Command IDLE

14.3.5 RMII Interface

14.3.5.1 RMII Receive (RX)

14.3.5.2 RMII Transmit (TX)

14.3.6 RGMII Interface

14.3.6.1 RGMII Receive (RX)

14.3.6.2 In-Band Mode of Operation

14.3.6.3 Forced Mode of Operation

14.3.6.4 RGMII Transmit (TX)

14.3.7 Common Platform Time Sync (CPTS)

14.3.7.1 Architecture

14.3.7.2 Time Sync Overview

14.3.7.2.1 Time Sync Initialization

14.3.7.2.2 Time Stamp Value

14.3.7.2.3 Event FIFO

14.3.7.2.4 Time Sync Events

14.3.7.3 Interrupt Handling

14.3.8 MDIO

14.3.8.1 MII Management Interface Frame Formats

14.3.8.2 Functional Description

14.4 Software Operation

14.4.1 Transmit Operation

14.4.2 Receive Operation

14.4.3 Initializing the MDIO Module

14.4.4 Writing Data to a PHY Register

14.4.5 Reading Data from a PHY Register

14.4.6 Initialization and Configuration of CPSW

14.5 Ethernet Subsystem Registers

14.5.1 CPSW_ALE Registers

14.5.1.1 IDVER Register (offset = 0h) [reset = 290104h]

14.5.1.2 CONTROL Register (offset = 8h) [reset = 0h]

14.5.1.3 PRESCALE Register (offset = 10h) [reset = 0h]

14.5.1.4 UNKNOWN_VLAN Register (offset = 18h) [reset = 0h]

14.5.1.5 TBLCTL Register (offset = 20h) [reset = 0h]

14.5.1.6 TBLW2 Register (offset = 34h) [reset = 0h]

14.5.1.7 TBLW1 Register (offset = 38h) [reset = 0h]

14.5.1.8 TBLW0 Register (offset = 3Ch) [reset = 0h]

14.5.1.9 PORTCTL0 Register (offset = 40h) [reset = 0h]

14.5.1.10 PORTCTL1 Register (offset = 44h) [reset = 0h]

14.5.1.11 PORTCTL2 Register (offset = 48h) [reset = 0h]

14.5.1.12 PORTCTL3 Register (offset = 4Ch) [reset = 0h]

14.5.1.13 PORTCTL4 Register (offset = 50h) [reset = 0h]

14.5.1.14 PORTCTL5 Register (offset = 54h) [reset = 0h]

14.5.2 CPSW_CPDMA Registers

14.5.2.1 TX_IDVER Register (offset = 0h) [reset = 180108h]

14.5.2.2 TX_CONTROL Register (offset = 4h) [reset = 0h]

14.5.2.3 TX_TEARDOWN Register (offset = 8h) [reset = 0h]

14.5.2.4 RX_IDVER Register (offset = 10h) [reset = C0107h]

14.5.2.5 RX_CONTROL Register (offset = 14h) [reset = 0h]

14.5.2.6 RX_TEARDOWN Register (offset = 18h) [reset = 0h]

14.5.2.7 CPDMA_SOFT_RESET Register (offset = 1Ch) [reset = 0h]

14.5.2.8 DMACONTROL Register (offset = 20h) [reset = 0h]

14.5.2.9 DMASTATUS Register (offset = 24h) [reset = 0h]

14.5.2.10 RX_BUFFER_OFFSET Register (offset = 28h) [reset = 0h]

14.5.2.11 EMCONTROL Register (offset = 2Ch) [reset = 0h]

14.5.2.12 TX_PRI0_RATE Register (offset = 30h) [reset = 0h]

14.5.2.13 TX_PRI1_RATE Register (offset = 34h) [reset = 0h]

14.5.2.14 TX_PRI2_RATE Register (offset = 38h) [reset = 0h]

14.5.2.15 TX_PRI3_RATE Register (offset = 3Ch) [reset = 0h]

14.5.2.16 TX_PRI4_RATE Register (offset = 40h) [reset = 0h]

14.5.2.17 TX_PRI5_RATE Register (offset = 44h) [reset = 0h]

14.5.2.18 TX_PRI6_RATE Register (offset = 48h) [reset = 0h]

14.5.2.19 TX_PRI7_RATE Register (offset = 4Ch) [reset = 0h]

14.5.2.20 TX_INTSTAT_RAW Register (offset = 80h) [reset = 0h]

14.5.2.21 TX_INTSTAT_MASKED Register (offset = 84h) [reset = 0h]

14.5.2.22 TX_INTMASK_SET Register (offset = 88h) [reset = 0h]

14.5.2.23 TX_INTMASK_CLEAR Register (offset = 8Ch) [reset = 0h]

14.5.2.24 CPDMA_IN_VECTOR Register (offset = 90h) [reset = 0h]

14.5.2.25 CPDMA_EOI_VECTOR Register (offset = 94h) [reset = 0h]

14.5.2.26 RX_INTSTAT_RAW Register (offset = A0h) [reset = 0h]

14.5.2.27 RX_INTSTAT_MASKED Register (offset = A4h) [reset = 0h]

14.5.2.28 RX_INTMASK_SET Register (offset = A8h) [reset = 0h]

14.5.2.29 RX_INTMASK_CLEAR Register (offset = ACh) [reset = 0h]

14.5.2.30 DMA_INTSTAT_RAW Register (offset = B0h) [reset = 0h]

14.5.2.31 DMA_INTSTAT_MASKED Register (offset = B4h) [reset = 0h]

14.5.2.32 DMA_INTMASK_SET Register (offset = B8h) [reset = 0h]

14.5.2.33 DMA_INTMASK_CLEAR Register (offset = BCh) [reset = 0h]

14.5.2.34 RX0_PENDTHRESH Register (offset = C0h) [reset = 0h]

14.5.2.35 RX1_PENDTHRESH Register (offset = C4h) [reset = 0h]

14.5.2.36 RX2_PENDTHRESH Register (offset = C8h) [reset = 0h]

14.5.2.37 RX3_PENDTHRESH Register (offset = CCh) [reset = 0h]

14.5.2.38 RX4_PENDTHRESH Register (offset = D0h) [reset = 0h]

14.5.2.39 RX5_PENDTHRESH Register (offset = D4h) [reset = 0h]

14.5.2.40 RX6_PENDTHRESH Register (offset = D8h) [reset = 0h]

14.5.2.41 RX7_PENDTHRESH Register (offset = DCh) [reset = 0h]

14.5.2.42 RX0_FREEBUFFER Register (offset = E0h) [reset = 0h]

14.5.2.43 RX1_FREEBUFFER Register (offset = E4h) [reset = 0h]

14.5.2.44 RX2_FREEBUFFER Register (offset = E8h) [reset = 0h]

14.5.2.45 RX3_FREEBUFFER Register (offset = ECh) [reset = 0h]

14.5.2.46 RX4_FREEBUFFER Register (offset = F0h) [reset = 0h]

14.5.2.47 RX5_FREEBUFFER Register (offset = F4h) [reset = 0h]

14.5.2.48 RX6_FREEBUFFER Register (offset = F8h) [reset = 0h]

14.5.2.49 RX7_FREEBUFFER Register (offset = FCh) [reset = 0h]

14.5.3 CPSW_CPTS Registers

14.5.3.1 CPTS_IDVER Register (offset = 0h) [reset = 4E8A0101h]

14.5.3.2 CPTS_CONTROL Register (offset = 4h) [reset = 0h]

14.5.3.3 CPTS_TS_PUSH Register (offset = Ch) [reset = 0h]

14.5.3.4 CPTS_TS_LOAD_VAL Register (offset = 10h) [reset = 0h]

14.5.3.5 CPTS_TS_LOAD_EN Register (offset = 14h) [reset = 0h]

14.5.3.6 CPTS_INTSTAT_RAW Register (offset = 20h) [reset = 0h]

14.5.3.7 CPTS_INTSTAT_MASKED Register (offset = 24h) [reset = 0h]

14.5.3.8 CPTS_INT_ENABLE Register (offset = 28h) [reset = 0h]

14.5.3.9 CPTS_EVENT_POP Register (offset = 30h) [reset = 0h]

14.5.3.10 CPTS_EVENT_LOW Register (offset = 34h) [reset = 0h]

14.5.3.11 CPTS_EVENT_HIGH Register (offset = 38h) [reset = 0h]

14.5.4 CPSW_STATS Registers

14.5.5 CPDMA_STATERAM Registers

14.5.5.1 TX0_HDP Register (offset = A00h) [reset = 0h]

14.5.5.2 TX1_HDP Register (offset = A04h) [reset = 0h]

14.5.5.3 TX2_HDP Register (offset = A08h) [reset = 0h]

14.5.5.4 TX3_HDP Register (offset = A0Ch) [reset = 0h]

14.5.5.5 TX4_HDP Register (offset = A10h) [reset = 0h]

14.5.5.6 TX5_HDP Register (offset = A14h) [reset = 0h]

14.5.5.7 TX6_HDP Register (offset = A18h) [reset = 0h]

14.5.5.8 TX7_HDP Register (offset = A1Ch) [reset = 0h]

14.5.5.9 RX0_HDP Register (offset = A20h) [reset = 0h]

14.5.5.10 RX1_HDP Register (offset = A24h) [reset = 0h]

14.5.5.11 RX2_HDP Register (offset = A28h) [reset = 0h]

14.5.5.12 RX3_HDP Register (offset = A2Ch) [reset = 0h]

14.5.5.13 RX4_HDP Register (offset = A30h) [reset = 0h]

14.5.5.14 RX5_HDP Register (offset = A34h) [reset = 0h]

14.5.5.15 RX6_HDP Register (offset = A38h) [reset = 0h]

14.5.5.16 RX7_HDP Register (offset = A3Ch) [reset = 0h]

14.5.5.17 TX0_CP Register (offset = A40h) [reset = 0h]

14.5.5.18 TX1_CP Register (offset = A44h) [reset = 0h]

14.5.5.19 TX2_CP Register (offset = A48h) [reset = 0h]

14.5.5.20 TX3_CP Register (offset = A4Ch) [reset = 0h]

14.5.5.21 TX4_CP Register (offset = A50h) [reset = 0h]

14.5.5.22 TX5_CP Register (offset = A54h) [reset = 0h]

14.5.5.23 TX6_CP Register (offset = A58h) [reset = 0h]

14.5.5.24 TX7_CP Register (offset = A5Ch) [reset = 0h]

14.5.5.25 RX0_CP Register (offset = A60h) [reset = 0h]

14.5.5.26 RX1_CP Register (offset = A64h) [reset = 0h]

14.5.5.27 RX2_CP Register (offset = A68h) [reset = 0h]

14.5.5.28 RX3_CP Register (offset = A6Ch) [reset = 0h]

14.5.5.29 RX4_CP Register (offset = A70h) [reset = 0h]

14.5.5.30 RX5_CP Register (offset = A74h) [reset = 0h]

14.5.5.31 RX6_CP Register (offset = A78h) [reset = 0h]

14.5.5.32 RX7_CP Register (offset = A7Ch) [reset = 0h]

14.5.6 CPSW_PORT Registers

14.5.6.1 P0_CONTROL Register (offset = 0h) [reset = 0h]

14.5.6.2 P0_MAX_BLKS Register (offset = 8h) [reset = 104h]

14.5.6.3 P0_BLK_CNT Register (offset = Ch) [reset = 41h]

14.5.6.4 P0_TX_IN_CTL Register (offset = 10h) [reset = 40C0h]

14.5.6.5 P0_PORT_VLAN Register (offset = 14h) [reset = 0h]

14.5.6.6 P0_TX_PRI_MAP Register (offset = 18h) [reset = 33221001h]

14.5.6.7 P0_CPDMA_TX_PRI_MAP Register (offset = 1Ch) [reset = 76543210h]

14.5.6.8 P0_CPDMA_RX_CH_MAP Register (offset = 20h) [reset = 0h]

14.5.6.9 P0_RX_DSCP_PRI_MAP0 Register (offset = 30h) [reset = 0h]

14.5.6.10 P0_RX_DSCP_PRI_MAP1 Register (offset = 34h) [reset = 0h]

14.5.6.11 P0_RX_DSCP_PRI_MAP2 Register (offset = 38h) [reset = 0h]

14.5.6.12 P0_RX_DSCP_PRI_MAP3 Register (offset = 3Ch) [reset = 0h]

14.5.6.13 P0_RX_DSCP_PRI_MAP4 Register (offset = 40h) [reset = 0h]

14.5.6.14 P0_RX_DSCP_PRI_MAP5 Register (offset = 44h) [reset = 0h]

14.5.6.15 P0_RX_DSCP_PRI_MAP6 Register (offset = 48h) [reset = 0h]

14.5.6.16 P0_RX_DSCP_PRI_MAP7 Register (offset = 4Ch) [reset = 0h]

14.5.6.17 P1_CONTROL Register (offset = 100h) [reset = 0h]

14.5.6.18 P1_MAX_BLKS Register (offset = 108h) [reset = 113h]

14.5.6.19 P1_BLK_CNT Register (offset = 10Ch) [reset = 41h]

14.5.6.20 P1_TX_IN_CTL Register (offset = 110h) [reset = 80040C0h]

14.5.6.21 P1_PORT_VLAN Register (offset = 114h) [reset = 0h]

14.5.6.22 P1_TX_PRI_MAP Register (offset = 118h) [reset = 33221001h]

14.5.6.23 P1_TS_SEQ_MTYPE Register (offset = 11Ch) [reset = 1E0000h]

14.5.6.24 P1_SA_LO Register (offset = 120h) [reset = 0h]

14.5.6.25 P1_SA_HI Register (offset = 124h) [reset = 0h]

14.5.6.26 P1_SEND_PERCENT Register (offset = 128h) [reset = 0h]

14.5.6.27 P1_RX_DSCP_PRI_MAP0 Register (offset = 130h) [reset = 0h]

14.5.6.28 P1_RX_DSCP_PRI_MAP1 Register (offset = 134h) [reset = 0h]

14.5.6.29 P1_RX_DSCP_PRI_MAP2 Register (offset = 138h) [reset = 0h]

14.5.6.30 P1_RX_DSCP_PRI_MAP3 Register (offset = 13Ch) [reset = 0h]