IS62WV51216ALL

IS62WV51216BLL

512K x 16 LOW VOLTAGE,

ULTRA LOW POWER CMOS STATIC RAM

DECEMBER 2007

FEATURES

• High-speed access time: 45ns, 55ns

CMOS low power operation

– 36 mW (typical) operating

– 12 µW (typical) CMOS standby

TTL compatible interface levels

Single power supply

– 1.65V--2.2V VDD (62WV51216ALL)

– 2.5V--3.6V VDD (62WV51216BLL)

Fully static operation: no clock or refresh

required

Three state outputs

Data control for upper and lower bytes

Industrial temperature available

Lead-free available

FUNCTIONAL BLOCK DIAGRAM

DESCRIPTION

The ISSI IS62WV51216ALL/ IS62WV51216BLL are high-

speed, 8M bit static RAMs organized as 512K words by 16

bits. It is fabricated using ISSI's high-performance CMOS

technology. This highly reliable process coupled with innovative

circuit design techniques, yields high-performance and low

power consumption devices.

When CS1 is HIGH (deselected) or when CS2 is LOW

(deselected) or when CS1 is LOW, CS2 is HIGH and both LB

and UB are HIGH, the device assumes a standby mode at

which the power dissipation can be reduced down with CMOS

input levels.

Easy memory expansion is provided by using Chip Enable

and Output Enable inputs. The active LOW Write Enable

(WE) controls both writing and reading of the memory. A data

byte allows Upper Byte (UB) and Lower Byte (LB) access.

The IS62WV51216ALL and IS62WV51216BLL are packaged

in the JEDEC standard 48-pin mini BGA (7.2mm x 8.7mm)

and 44-Pin TSOP (TYPE II).

A0-A18

DECODER

512K x 16

MEMORY ARRAY

VDD

GND

I/O0-I/O7

Lower Byte

I/O8-I/O15

Upper Byte

I/O

DATA

CIRCUIT

COLUMN I/O

CS2

CS1

OE

WE

UB

LB

CONTROL

CIRCUIT

Copyright © 2005 Integrated Silicon Solution, Inc. All rights reserved. ISSI reserves the right to make changes to this specification and its products at any time without notice. ISSI assumes no liability

arising out of the application or use of any information, products or services described herein. Customers are advised to obtain the latest version of this device specification before relying on any

published information and before placing orders for products.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

1

�

IS62WV51216ALL, IS62WV51216BLL

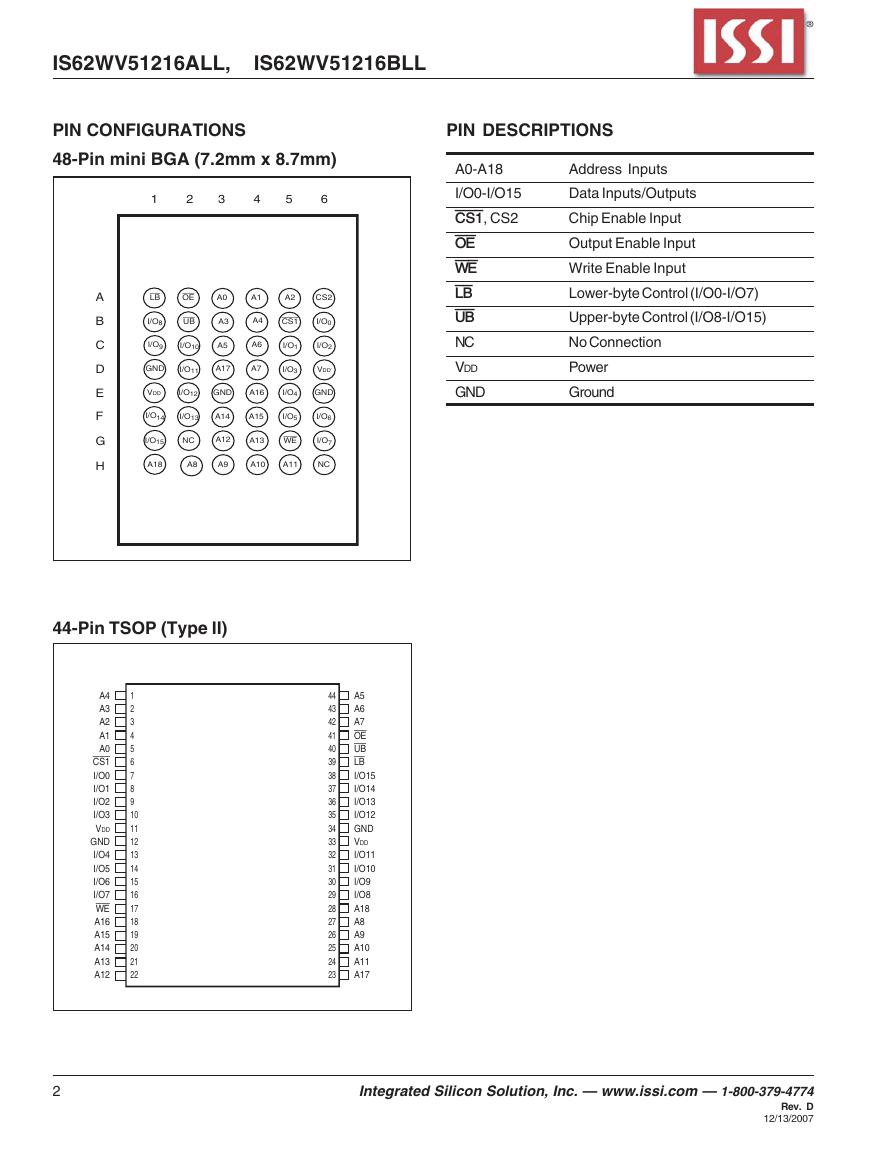

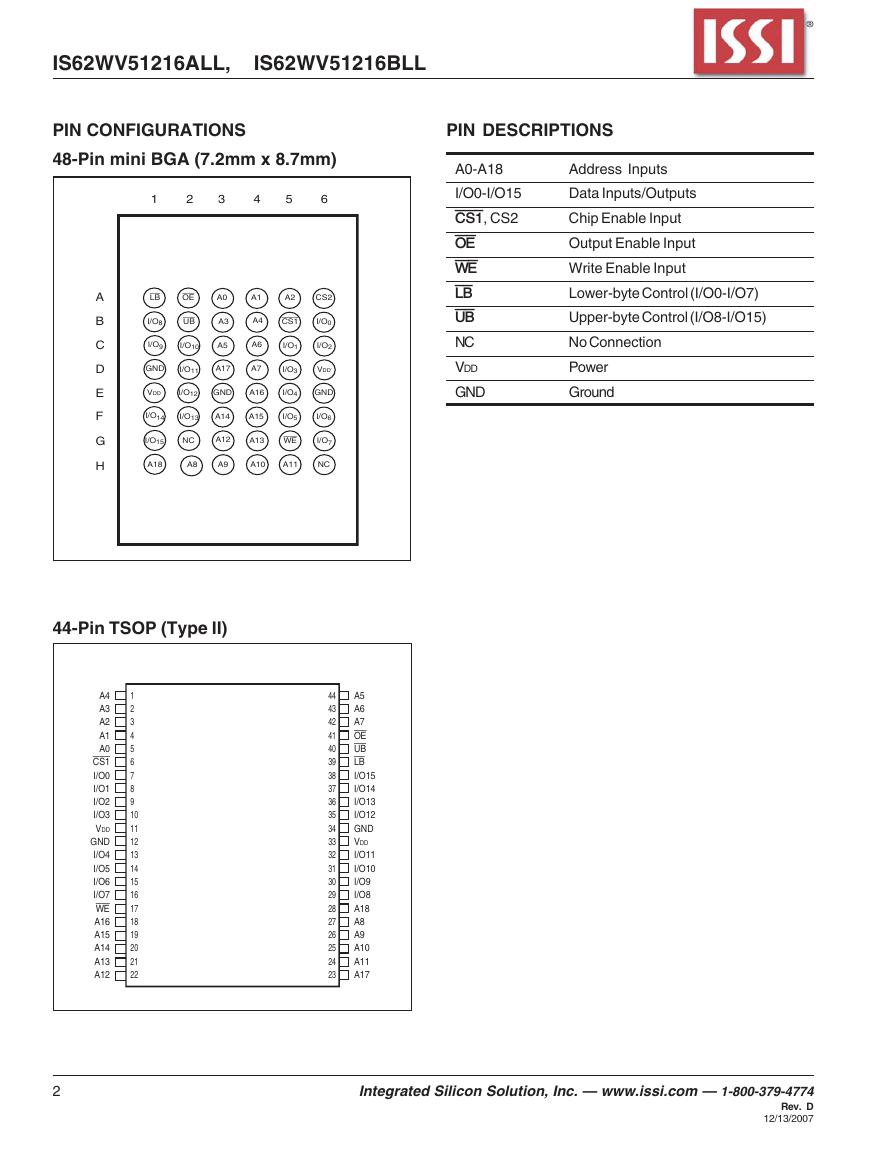

PIN CONFIGURATIONS

48-Pin mini BGA (7.2mm x 8.7mm)

1 2 3 4 5 6

A

B

C

D

E

F

G

H

LB

I/O8

OE

UB

I/O9

I/O10

A0

A3

A5

GND

I/O11

A17

A1

A2

CS2

A4

CS1

I/O0

A6

A7

I/O1

I/O2

I/O3

VDD`

VDD

I/O12

GND

A16

I/O4

GND

I/O14

I/O13

A14

A15

I/O5

I/O6

I/O15

NC

A12

A13

WE

I/O7

A18

A8

A9

A10

A11

NC

PIN DESCRIPTIONS

A0-A18

I/O0-I/O15

CS1, CS2

OE

WE

LB

UB

NC

VDD

GND

Address Inputs

Data Inputs/Outputs

Chip Enable Input

Output Enable Input

Write Enable Input

Lower-byte Control (I/O0-I/O7)

Upper-byte Control (I/O8-I/O15)

No Connection

Power

Ground

44-Pin TSOP (Type II)

A4

A3

A2

A1

A0

CS1

I/O0

I/O1

I/O2

I/O3

VDD

GND

I/O4

I/O5

I/O6

I/O7

WE

A16

A15

A14

A13

A12

1

2

3

4

5

6

7

8

9

10

11

12

13

14

15

16

17

18

19

20

21

22

44

43

42

41

40

39

38

37

36

35

34

33

32

31

30

29

28

27

26

25

24

23

A5

A6

A7

OE

UB

LB

I/O15

I/O14

I/O13

I/O12

GND

VDD

I/O11

I/O10

I/O9

I/O8

A18

A8

A9

A10

A11

A17

2

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

�

IS62WV51216ALL, IS62WV51216BLL

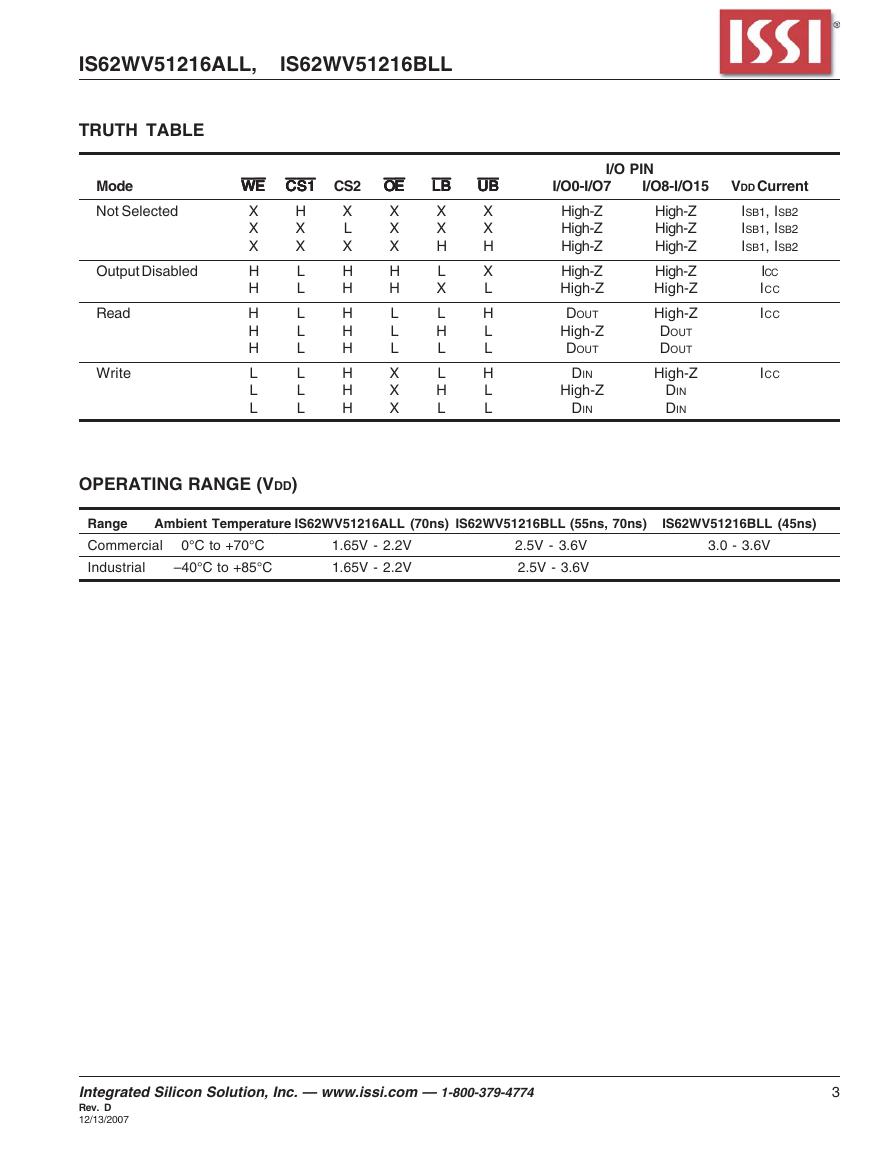

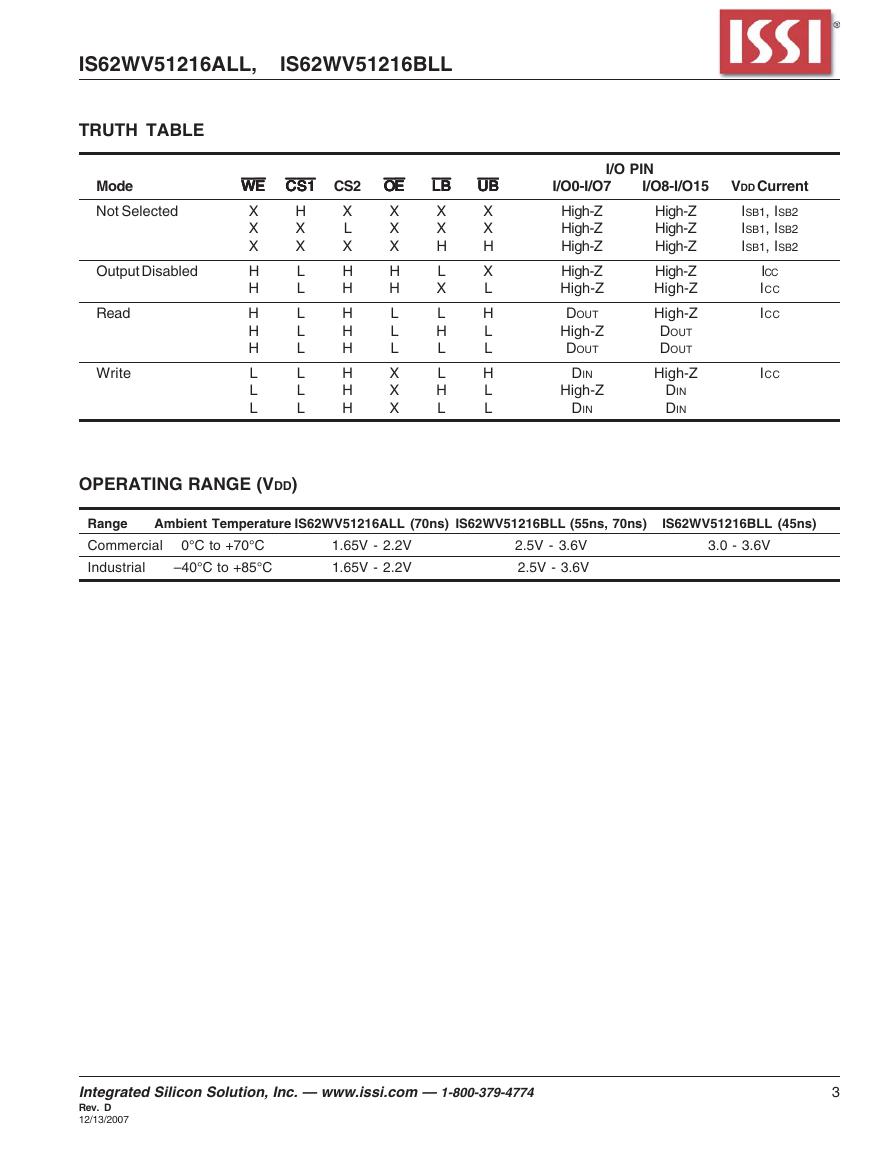

TRUTH TABLE

Mode

Not Selected

Output Disabled

Read

Write

WEWEWEWEWE CS1CS1CS1CS1CS1 CS2

X

X

L

X

X

X

H

H

H

H

H

H

H

H

H

H

H

L

H

L

L

H

H

X

X

L

L

L

L

L

L

L

L

OEOEOEOEOE

X

X

X

H

H

L

L

L

X

X

X

LBLBLBLBLB

X

X

H

L

X

L

H

L

L

H

L

UBUBUBUBUB

X

X

H

X

L

H

L

L

H

L

L

I/O PIN

I/O0-I/O7

High-Z

High-Z

High-Z

High-Z

High-Z

DOUT

High-Z

DOUT

DIN

High-Z

DIN

I/O8-I/O15

VDD Current

ISB1, ISB2

ISB1, ISB2

ISB1, ISB2

ICC

ICC

ICC

ICC

High-Z

High-Z

High-Z

High-Z

High-Z

High-Z

DOUT

DOUT

High-Z

DIN

DIN

OPERATING RANGE (VDD)

Range

Commercial

Industrial

Ambient Temperature IS62WV51216ALL (70ns) IS62WV51216BLL (55ns, 70ns)

0°C to +70°C

–40°C to +85°C

1.65V - 2.2V

1.65V - 2.2V

2.5V - 3.6V

2.5V - 3.6V

IS62WV51216BLL (45ns)

3.0 - 3.6V

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

3

�

IS62WV51216ALL, IS62WV51216BLL

ABSOLUTE MAXIMUM RATINGS(1)

Symbol

VTERM

TBIAS

VDD

TSTG

PT

Note:

1. Stress greater than those listed under ABSOLUTE MAXIMUM RATINGS may cause permanent damage to the

Parameter

Terminal Voltage with Respect to GND

Temperature Under Bias

VDD Related to GND

Storage Temperature

Power Dissipation

–40 to +85

–0.2 to +3.8

–65 to +150

–0.2 to VDD+0.3

Unit

V

°C

V

°C

W

Value

1.0

device. This is a stress rating only and functional operation of the device at these or any other conditions above

those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum

rating conditions for extended periods may affect reliability.

DC ELECTRICAL CHARACTERISTICS (Over Operating Range)

Symbol Parameter

VOH

Output HIGH Voltage

VOL

VIH

Output LOW Voltage

Input HIGH Voltage

VIL(1)

Input LOW Voltage

Test Conditions

IOH = -0.1 mA

IOH = -1 mA

IOL = 0.1 mA

IOL = 2.1 mA

VDD

1.65-2.2V

2.5-3.6V

1.65-2.2V

2.5-3.6V

1.65-2.2V

2.5-3.6V

1.65-2.2V

2.5-3.6V

Input Leakage

Output Leakage

ILI

ILO

Notes:

1. VIL (min.) = –1.0V for pulse width less than 10 ns.

GND ≤ VIN ≤ VDD

GND ≤ VOUT ≤ VDD, Outputs Disabled

Min.

1.4

2.2

—

—

1.4

2.2

–0.2

–0.2

–1

–1

Max.

—

—

0.2

0.4

VDD + 0.2

VDD + 0.3

0.4

0.6

1

1

Unit

V

V

V

V

V

V

V

V

µA

µA

4

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

�

IS62WV51216ALL, IS62WV51216BLL

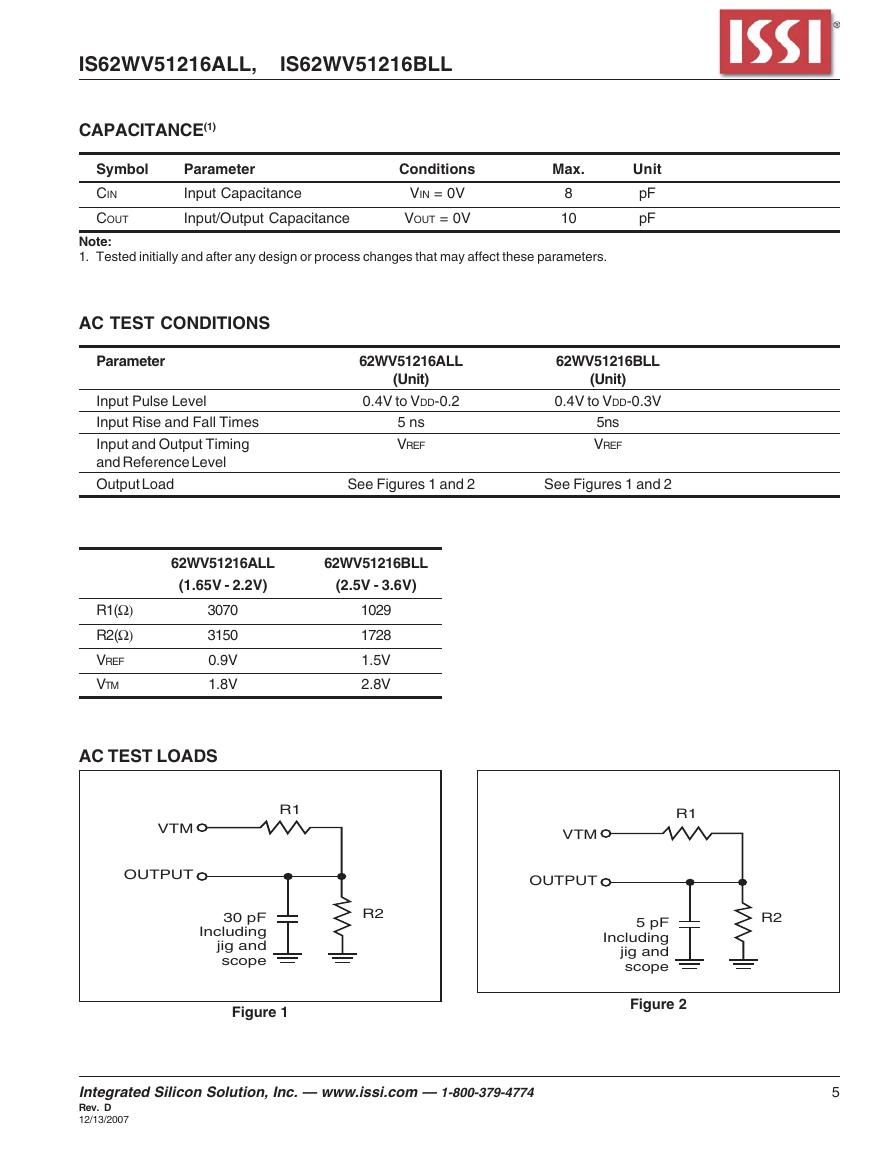

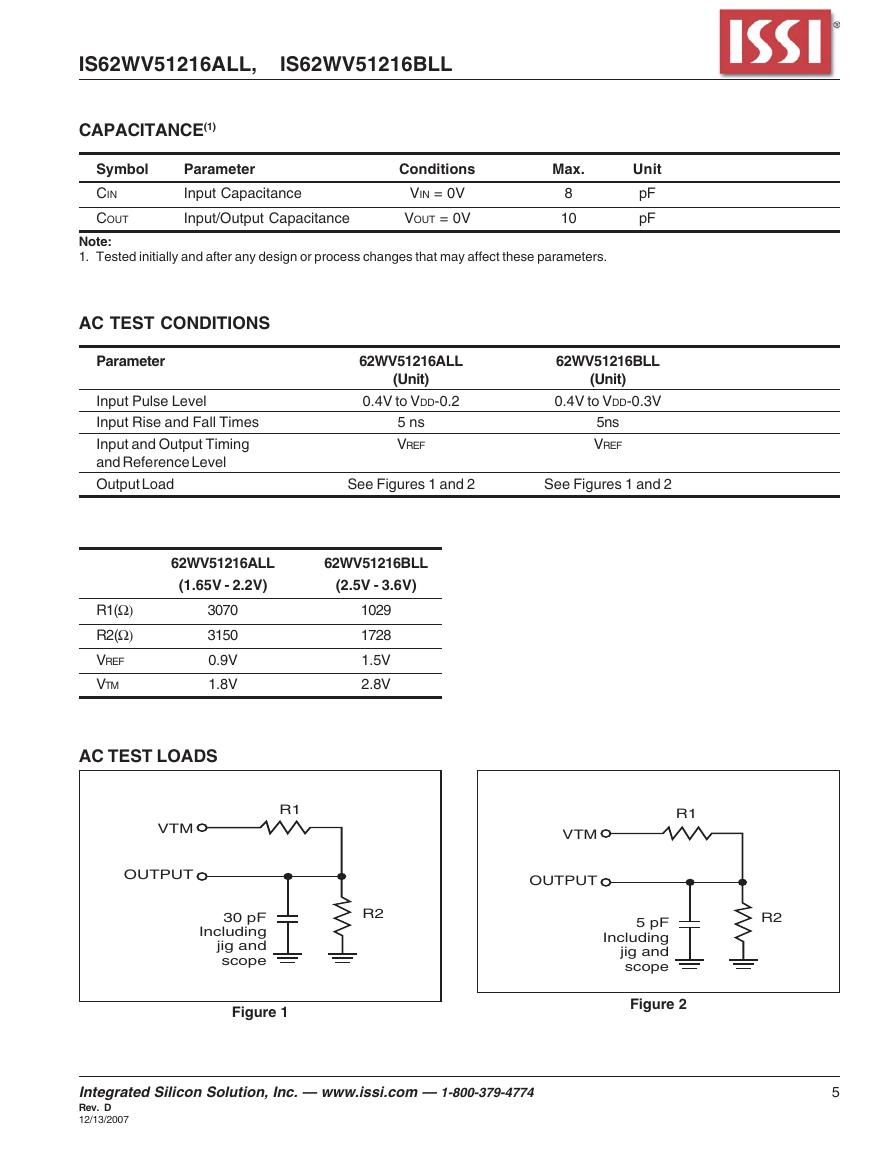

CAPACITANCE(1)

Symbol

CIN

COUT

Parameter

Input Capacitance

Input/Output Capacitance

Conditions

VIN = 0V

VOUT = 0V

Max.

8

10

Unit

pF

pF

Note:

1. Tested initially and after any design or process changes that may affect these parameters.

AC TEST CONDITIONS

Parameter

Input Pulse Level

Input Rise and Fall Times

Input and Output Timing

and Reference Level

Output Load

62WV51216ALL

(Unit)

0.4V to VDD-0.2

5 ns

VREF

62WV51216BLL

(Unit)

0.4V to VDD-0.3V

5ns

VREF

See Figures 1 and 2

See Figures 1 and 2

62WV51216ALL

(1.65V - 2.2V)

62WV51216BLL

(2.5V - 3.6V)

1029

1728

1.5V

2.8V

R2

R1(Ω)

R2(Ω)

VREF

VTM

3070

3150

0.9V

1.8V

AC TEST LOADS

R1

VTM

OUTPUT

30 pF

Including

jig and

scope

Figure 1

R1

VTM

OUTPUT

R2

5 pF

Including

jig and

scope

Figure 2

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

5

�

IS62WV51216ALL, IS62WV51216BLL

IS62WV51216ALL, POWER SUPPLY CHARACTERISTICS(1) (Over Operating Range)

Symbol

Parameter

Test Conditions

ICC

ICC1

ISB1

VDD Dynamic Operating

Supply Current

Operating Supply

Current

TTL Standby Current

(TTL Inputs)

OR

ULB Control

ISB2

CMOS Standby

Current (CMOS Inputs)

OR

ULB Control

VDD = Max.,

IOUT = 0 mA, f = fMAX

VDD = Max., CS1 = 0.2V

WE = VDD – 0.2V

CS2 = VDD – 0.2V, f = 1MHZ

VDD = Max.,

VIN = VIH or VIL

CS1 = VIH , CS2 = VIL,

f = 1 MHZ

Com.

Ind.

Com.

Ind.

Com.

Ind.

VDD = Max., VIN = VIH or VIL

CS1 = VIL, f = 0, UB = VIH, LB = VIH

VDD = Max.,

CS1 ≥ VDD – 0.2V,

CS2 ≤ 0.2V,

VIN ≥ VDD – 0.2V, or

VIN ≤ 0.2V, f = 0

Com.

Ind.

typ.(1)

VDD = Max., CS1 = VIL, CS2=VIH

VIN ≥ VDD – 0.2V, or VIN ≤ 0.2V, f = 0;

UB / LB = VDD – 0.2V

Note:.

1. Typical values are measured at VDD = 1.8V, TA = 25oC and not 100% tested.

Max.

70

20

25

4

4

0.3

0.3

Unit

mA

mA

mA

µA

15

21

3

6

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

�

IS62WV51216ALL, IS62WV51216BLL

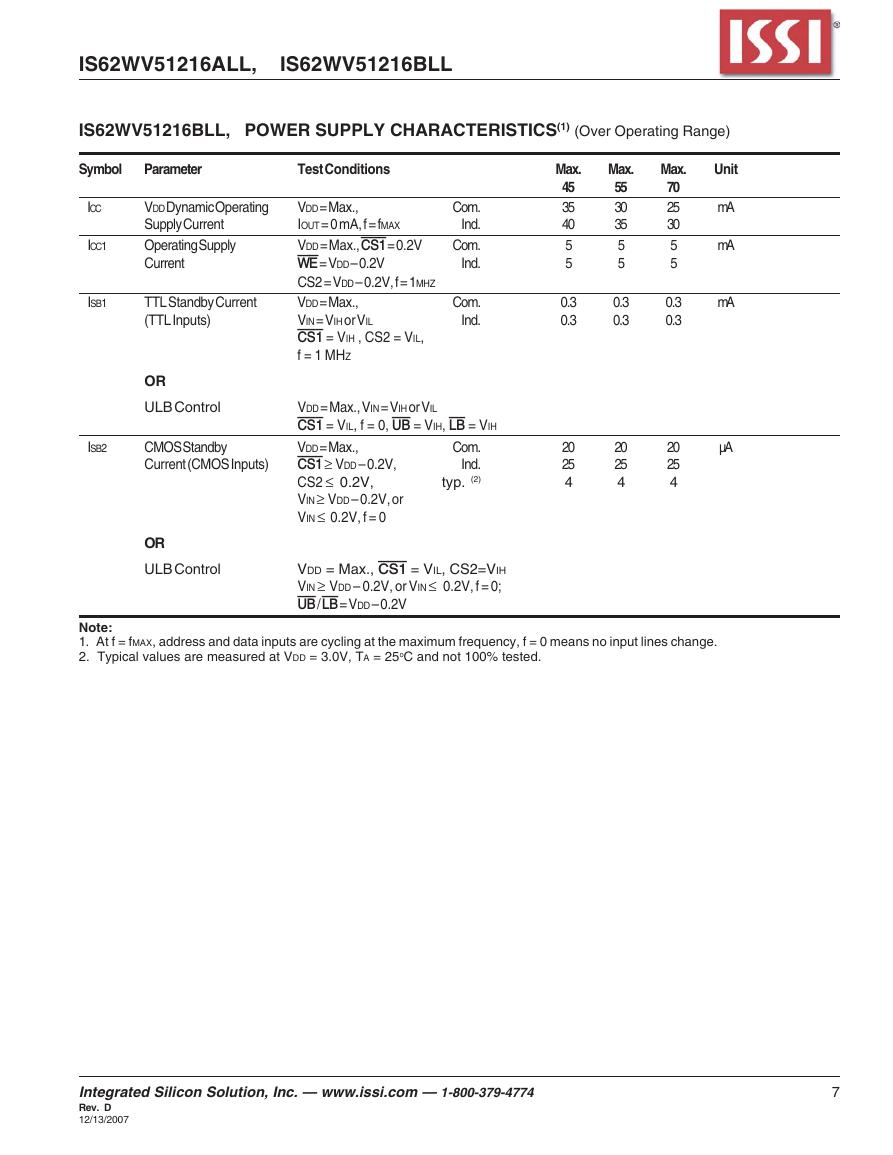

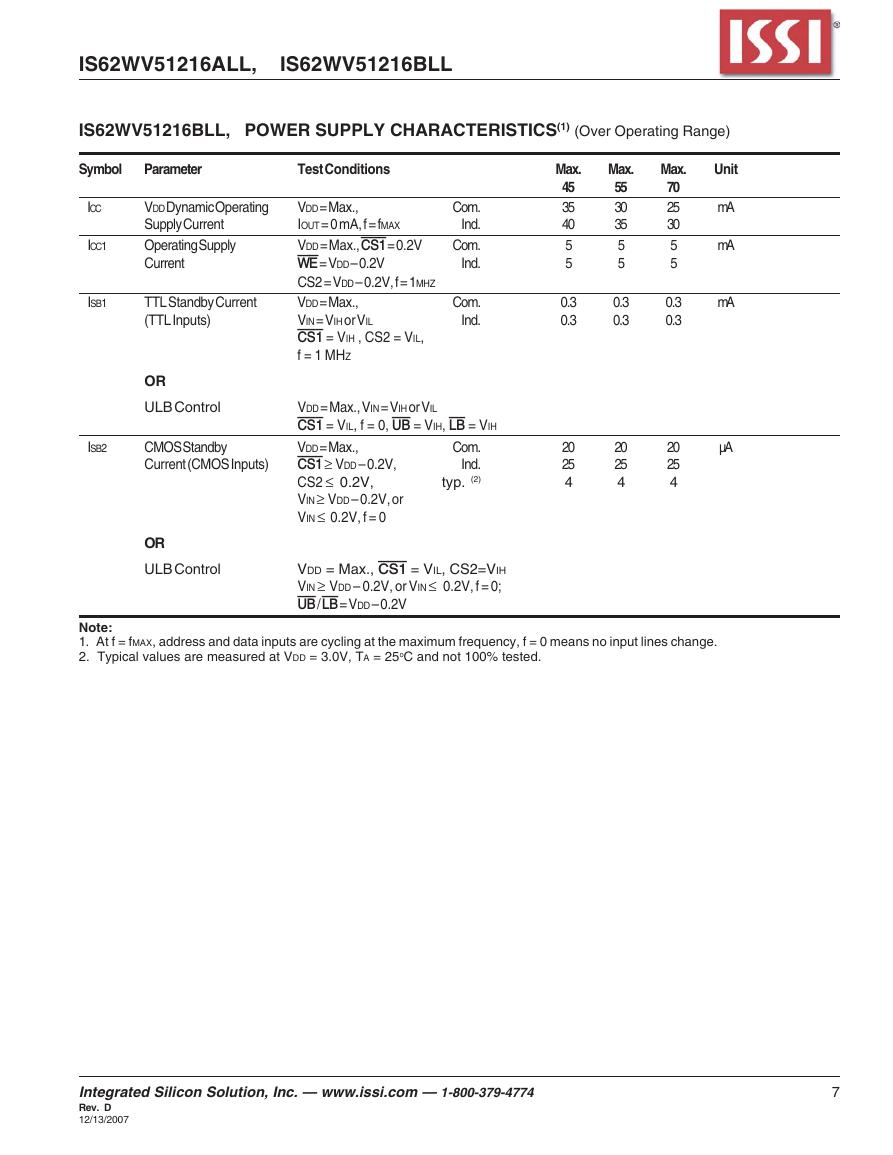

IS62WV51216BLL, POWER SUPPLY CHARACTERISTICS(1) (Over Operating Range)

Symbol

Parameter

Test Conditions

ICC

ICC1

ISB1

VDD Dynamic Operating

Supply Current

Operating Supply

Current

TTL Standby Current

(TTL Inputs)

OR

ULB Control

ISB2

CMOS Standby

Current (CMOS Inputs)

OR

ULB Control

VDD = Max.,

IOUT = 0 mA, f = fMAX

VDD = Max., CS1 = 0.2V

WE = VDD – 0.2V

CS2 = VDD – 0.2V, f = 1MHZ

VDD = Max.,

VIN = VIH or VIL

CS1 = VIH , CS2 = VIL,

f = 1 MHZ

Com.

Ind.

Com.

Ind.

Com.

Ind.

VDD = Max., VIN = VIH or VIL

CS1 = VIL, f = 0, UB = VIH, LB = VIH

VDD = Max.,

CS1 ≥ VDD – 0.2V,

CS2 ≤ 0.2V,

VIN ≥ VDD – 0.2V, or

VIN ≤ 0.2V, f = 0

Com.

Ind.

typ. (2)

VDD = Max., CS1 = VIL, CS2=VIH

VIN ≥ VDD – 0.2V, or VIN ≤ 0.2V, f = 0;

UB / LB = VDD – 0.2V

Max.

45

35

40

5

5

0.3

0.3

Max.

55

30

35

5

5

0.3

0.3

Max.

70

25

30

5

5

0.3

0.3

Unit

mA

mA

mA

20

25

4

20

25

4

20

25

4

µA

Note:

1. At f = fMAX, address and data inputs are cycling at the maximum frequency, f = 0 means no input lines change.

2. Typical values are measured at VDD = 3.0V, TA = 25oC and not 100% tested.

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

7

�

IS62WV51216ALL, IS62WV51216BLL

READ CYCLE SWITCHING CHARACTERISTICS(1) (Over Operating Range)

45 ns

55 ns

70 ns

Max.

Max.

Max.

—

70

—

70

35

25

—

25

—

70

25

—

Parameter

Read Cycle Time

Address Access Time

Output Hold Time

CS1/CS2 Access Time

OE Access Time

OE to High-Z Output

OE to Low-Z Output

Symbol

tRC

tAA

tOHA

tACS1/tACS2

tDOE

tHZOE(2)

tLZOE(2)

tHZCS1/tHZCS2(2) CS1/CS2 to High-Z Output

tLZCS1/tLZCS2(2) CS1/CS2 to Low-Z Output

tBA

tHZB

tLZB

Notes:

1. Test conditions assume signal transition times of 5 ns or less, timing reference levels of 0.9V/1.5V, input pulse levels of 0.4 to

LB, UB Access Time

LB, UB to High-Z Output

LB, UB to Low-Z Output

Min.

70

—

10

—

—

—

5

0

10

—

0

0

Min.

45

—

10

—

—

—

5

0

10

—

0

0

Unit

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

Min.

55

—

10

—

—

—

5

0

10

—

0

0

—

55

—

55

25

20

—

20

—

55

20

—

—

45

—

45

20

15

—

15

—

45

15

—

VDD-0.2V/0.4V to VDD-0.3V and output loading specified in Figure 1.

2. Tested with the load in Figure 2. Transition is measured ±500 mV from steady-state voltage. Not 100% tested.

AC WAVEFORMS

READ CYCLE NO. 1(1,2) (Address Controlled) (CS1 = OE = VIL, CS2 = WE = VIH, UB or LB = VIL)

ADDRESS

DQ0-D15

PREVIOUS DATA VALID

tRC

tAA

tOHA

tOHA

DATA VALID

8

Integrated Silicon Solution, Inc. — www.issi.com — 1-800-379-4774

Rev. D

12/13/2007

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf