Rule Category

NOVAS Software, Inc.

2025 Gateway Place, Suite 480,

San Jose, CA 95110

1-888-NOVAS-38 (1-888-668-2738)

�

Printed on November 6, 2000

This manual supports nLint1.0 and higher versions.

No part of this manual may be reproduced in any form or by any means without written

permission of:

NOVAS Software, Inc.

2025 Gateway Place, Suite 480,

San Jose, CA 95110 U.S.A.

Copyright

1999-2000 NOVAS Software, Inc.

RESTRICTED RIGHTS

The information contained in this document is subject to change without notice.

�

Contents

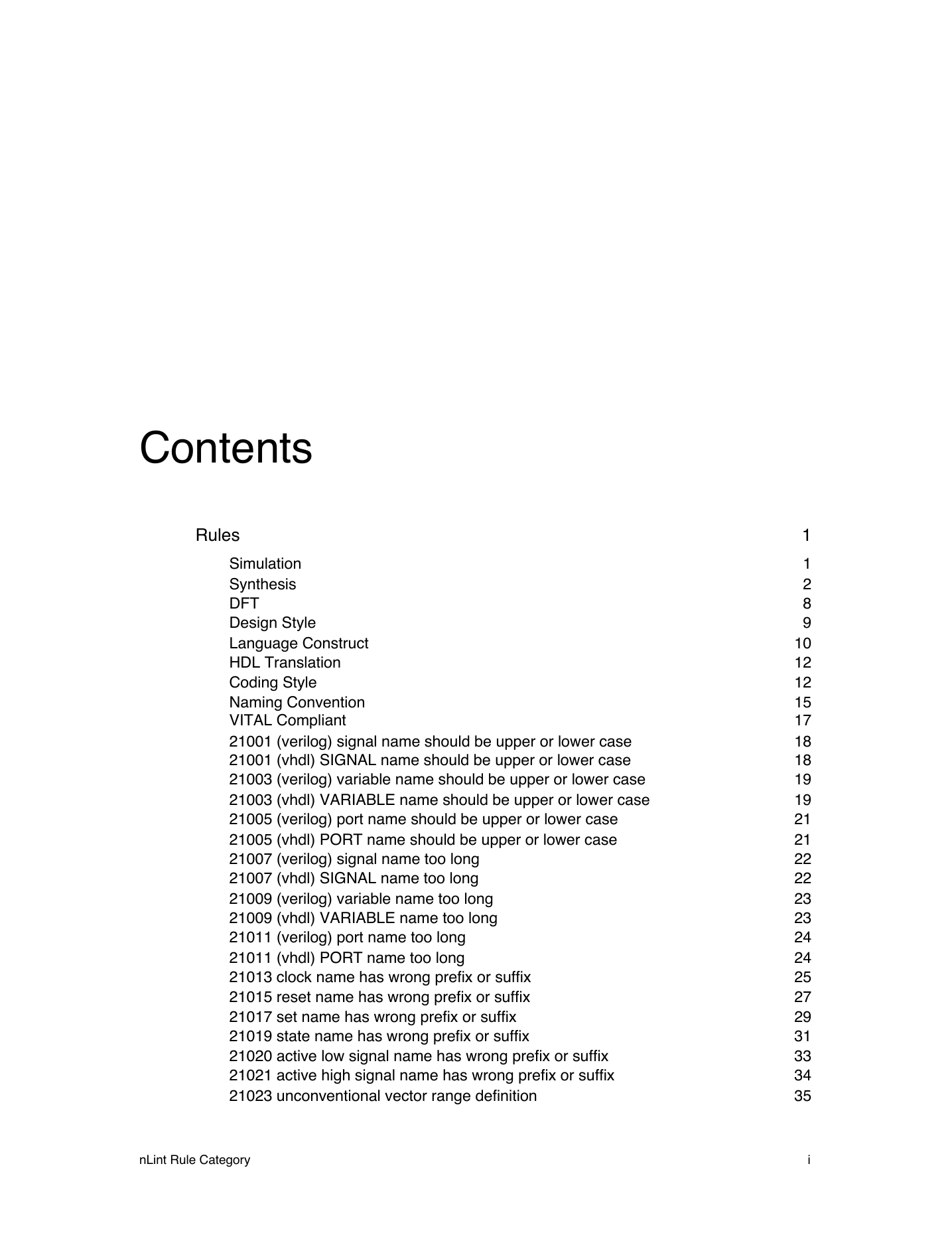

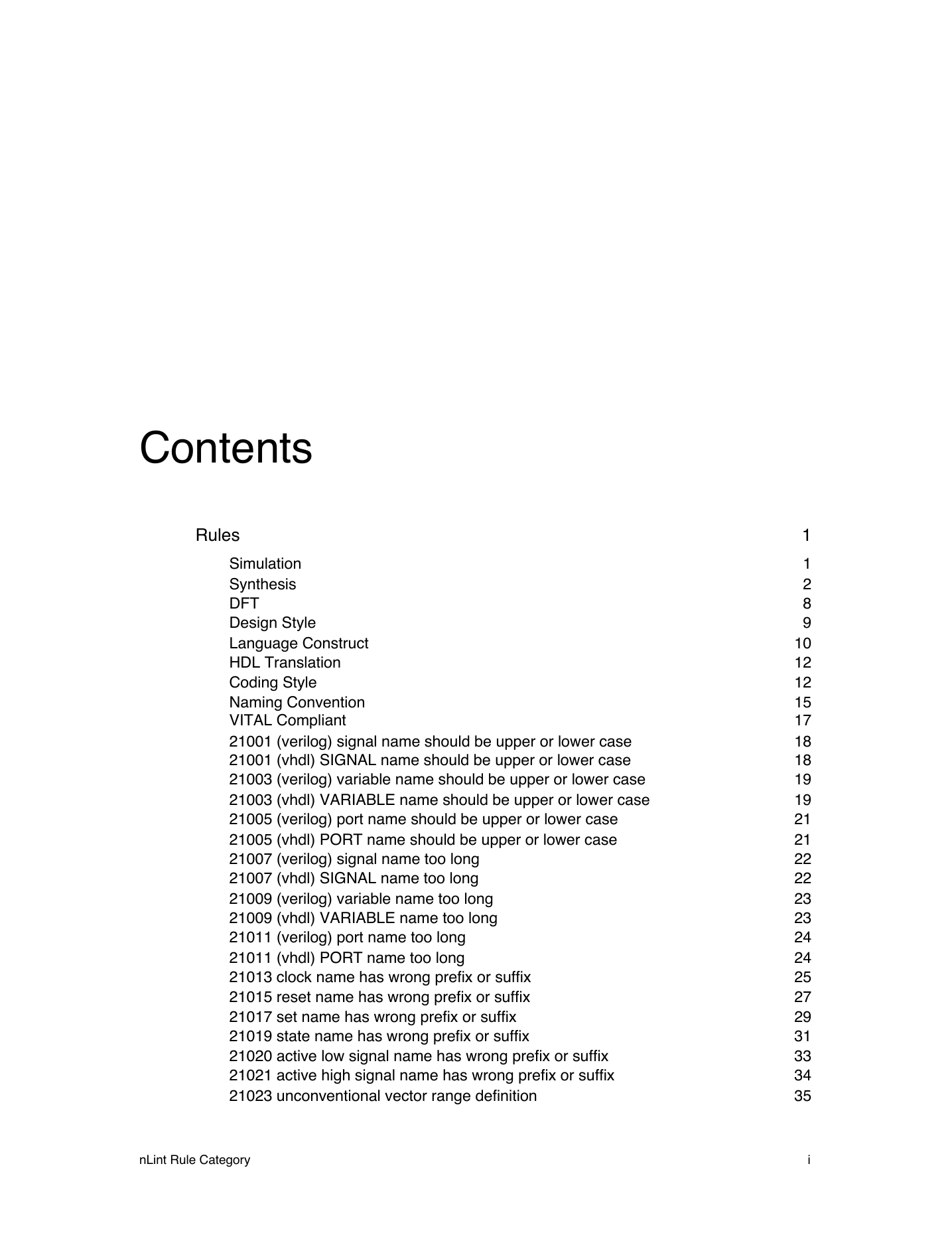

Rules

Simulation

Synthesis

DFT

Design Style

Language Construct

HDL Translation

Coding Style

Naming Convention

VITAL Compliant

21001 (verilog) signal name should be upper or lower case

21001 (vhdl) SIGNAL name should be upper or lower case

21003 (verilog) variable name should be upper or lower case

21003 (vhdl) VARIABLE name should be upper or lower case

21005 (verilog) port name should be upper or lower case

21005 (vhdl) PORT name should be upper or lower case

21007 (verilog) signal name too long

21007 (vhdl) SIGNAL name too long

21009 (verilog) variable name too long

21009 (vhdl) VARIABLE name too long

21011 (verilog) port name too long

21011 (vhdl) PORT name too long

21013 clock name has wrong prefix or suffix

21015 reset name has wrong prefix or suffix

21017 set name has wrong prefix or suffix

21019 state name has wrong prefix or suffix

21020 active low signal name has wrong prefix or suffix

21021 active high signal name has wrong prefix or suffix

21023 unconventional vector range definition

nLint Rule Category

1

1

2

8

9

10

12

12

15

17

18

18

19

19

21

21

22

22

23

23

24

24

25

27

29

31

33

34

35

i

�

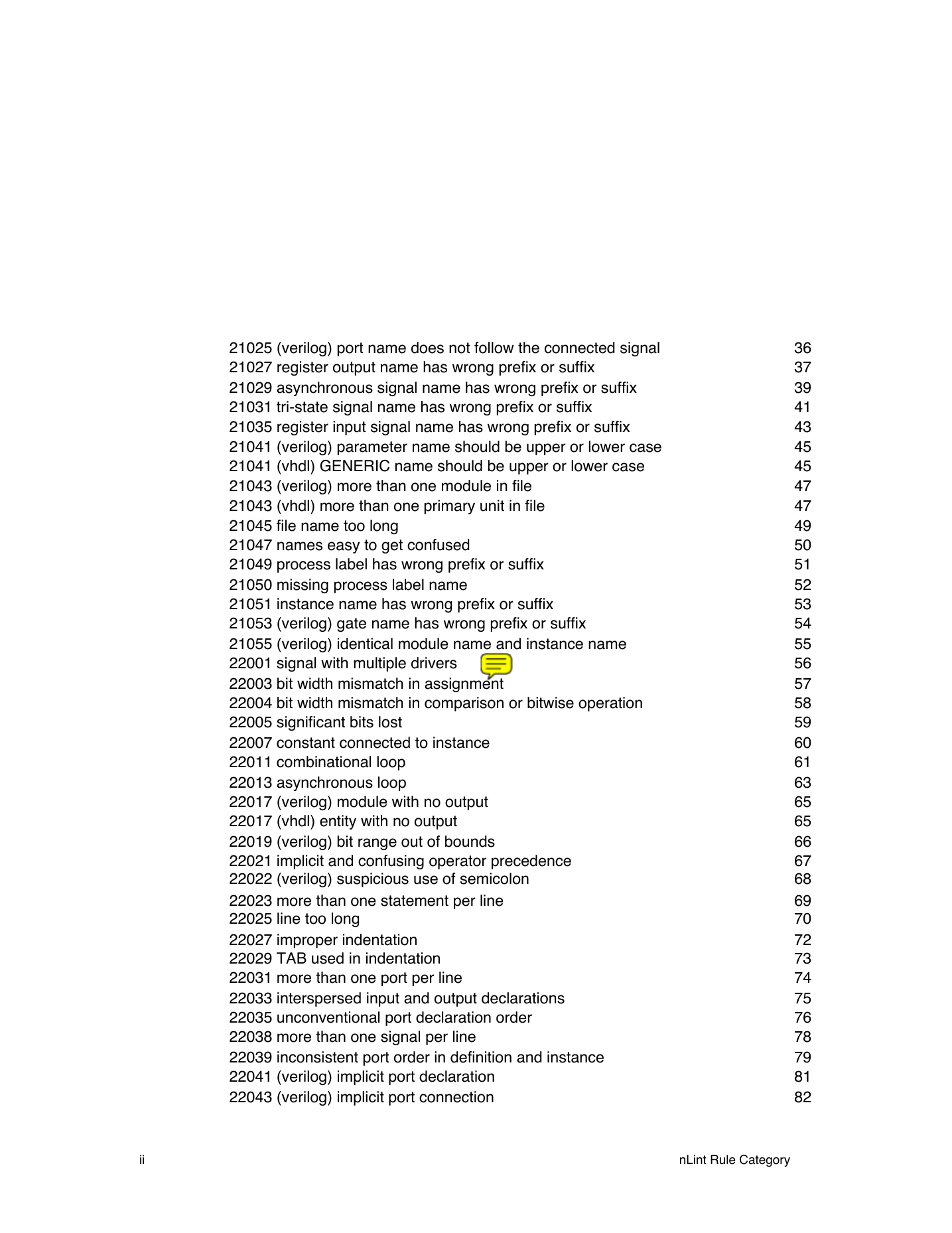

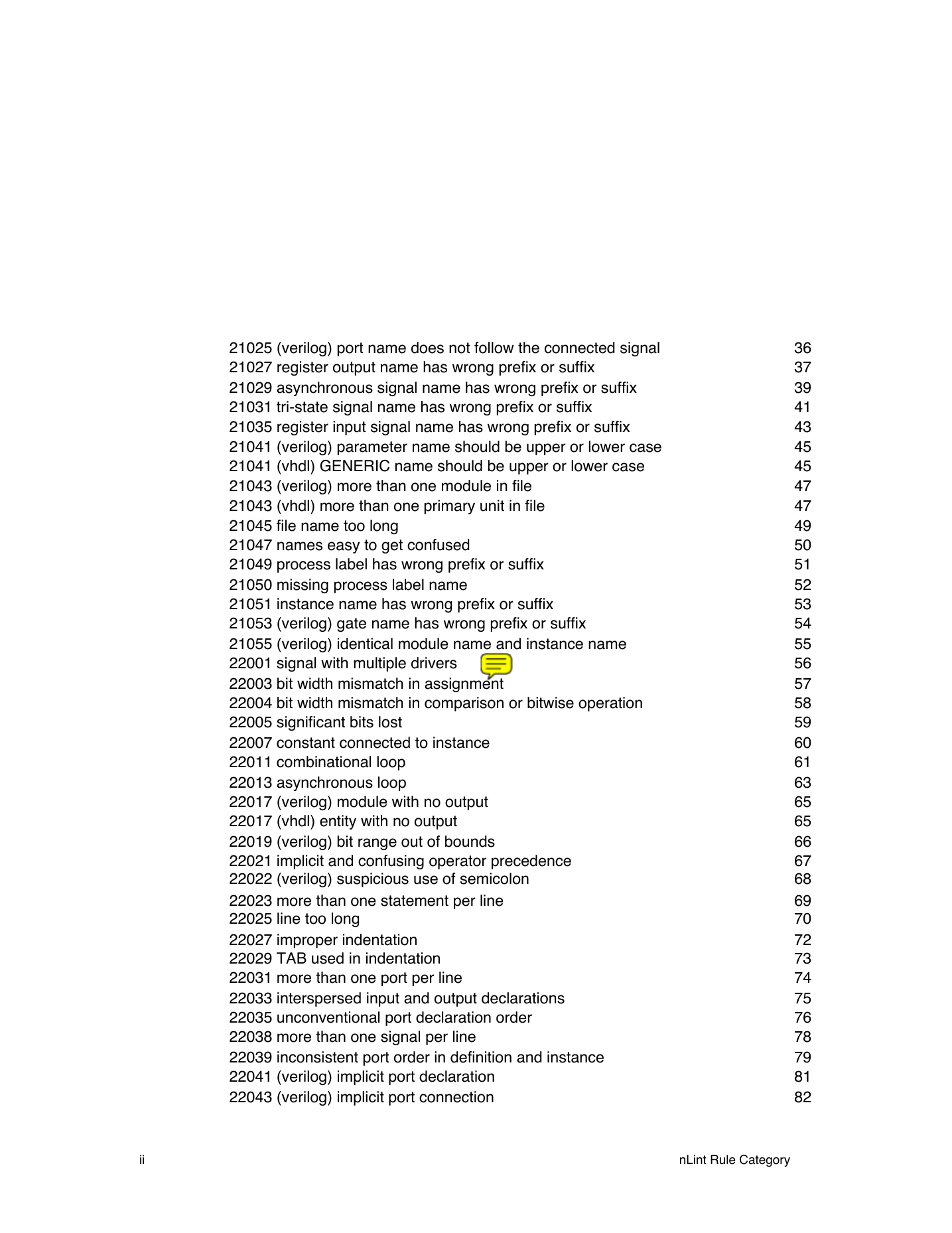

21025 (verilog) port name does not follow the connected signal

21027 register output name has wrong prefix or suffix

21029 asynchronous signal name has wrong prefix or suffix

21031 tri-state signal name has wrong prefix or suffix

21035 register input signal name has wrong prefix or suffix

21041 (verilog) parameter name should be upper or lower case

21041 (vhdl) GENERIC name should be upper or lower case

21043 (verilog) more than one module in file

21043 (vhdl) more than one primary unit in file

21045 file name too long

21047 names easy to get confused

21049 process label has wrong prefix or suffix

21050 missing process label name

21051 instance name has wrong prefix or suffix

21053 (verilog) gate name has wrong prefix or suffix

21055 (verilog) identical module name and instance name

22001 signal with multiple drivers

22003 bit width mismatch in assignment

22004 bit width mismatch in comparison or bitwise operation

22005 significant bits lost

22007 constant connected to instance

22011 combinational loop

22013 asynchronous loop

22017 (verilog) module with no output

22017 (vhdl) entity with no output

22019 (verilog) bit range out of bounds

22021 implicit and confusing operator precedence

22022 (verilog) suspicious use of semicolon

22023 more than one statement per line

22025 line too long

22027 improper indentation

22029 TAB used in indentation

22031 more than one port per line

22033 interspersed input and output declarations

22035 unconventional port declaration order

22038 more than one signal per line

22039 inconsistent port order in definition and instance

22041 (verilog) implicit port declaration

22043 (verilog) implicit port connection

36

37

39

41

43

45

45

47

47

49

50

51

52

53

54

55

56

57

58

59

60

61

63

65

65

66

67

68

69

70

72

73

74

75

76

78

79

81

82

ii

nLint Rule Category

�

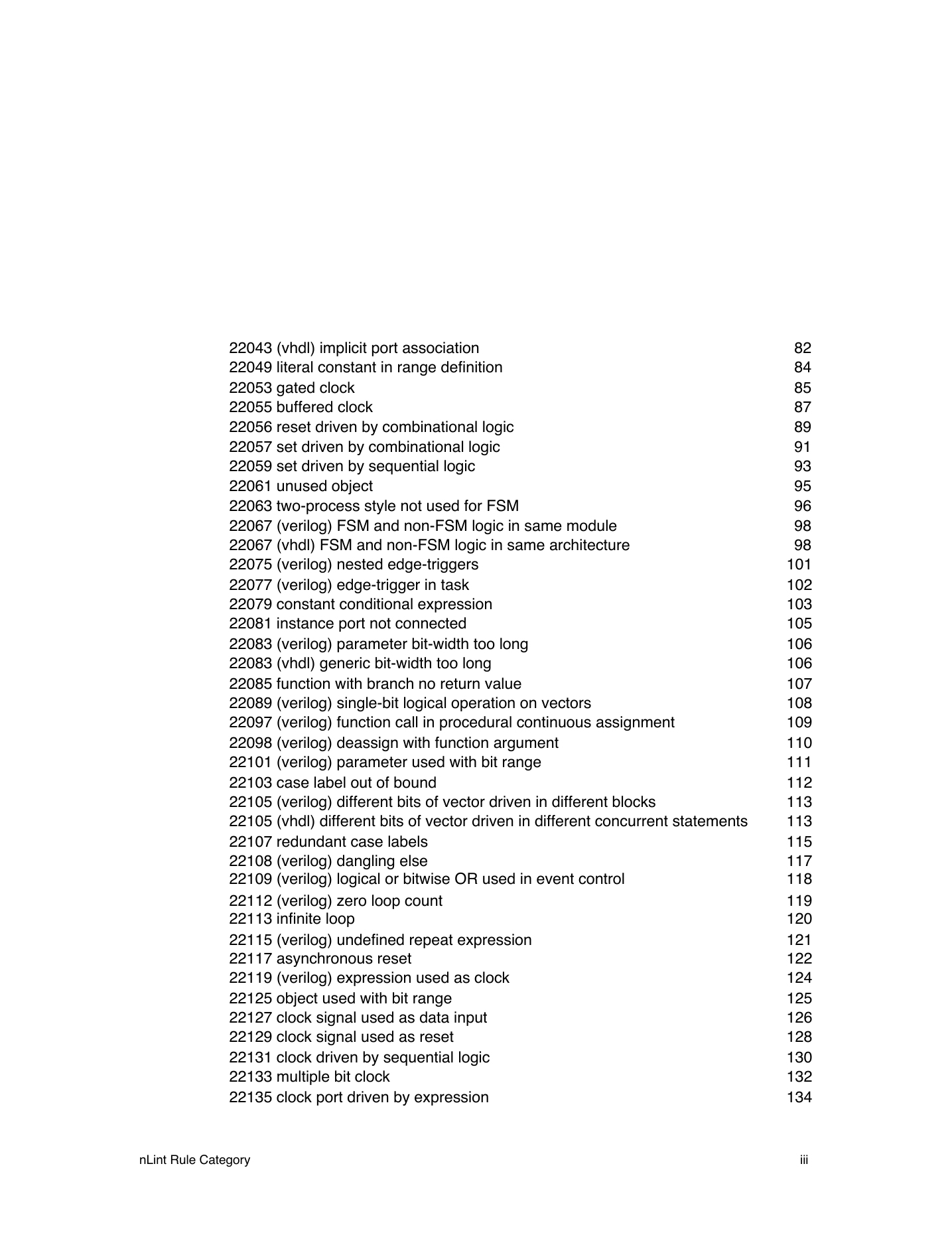

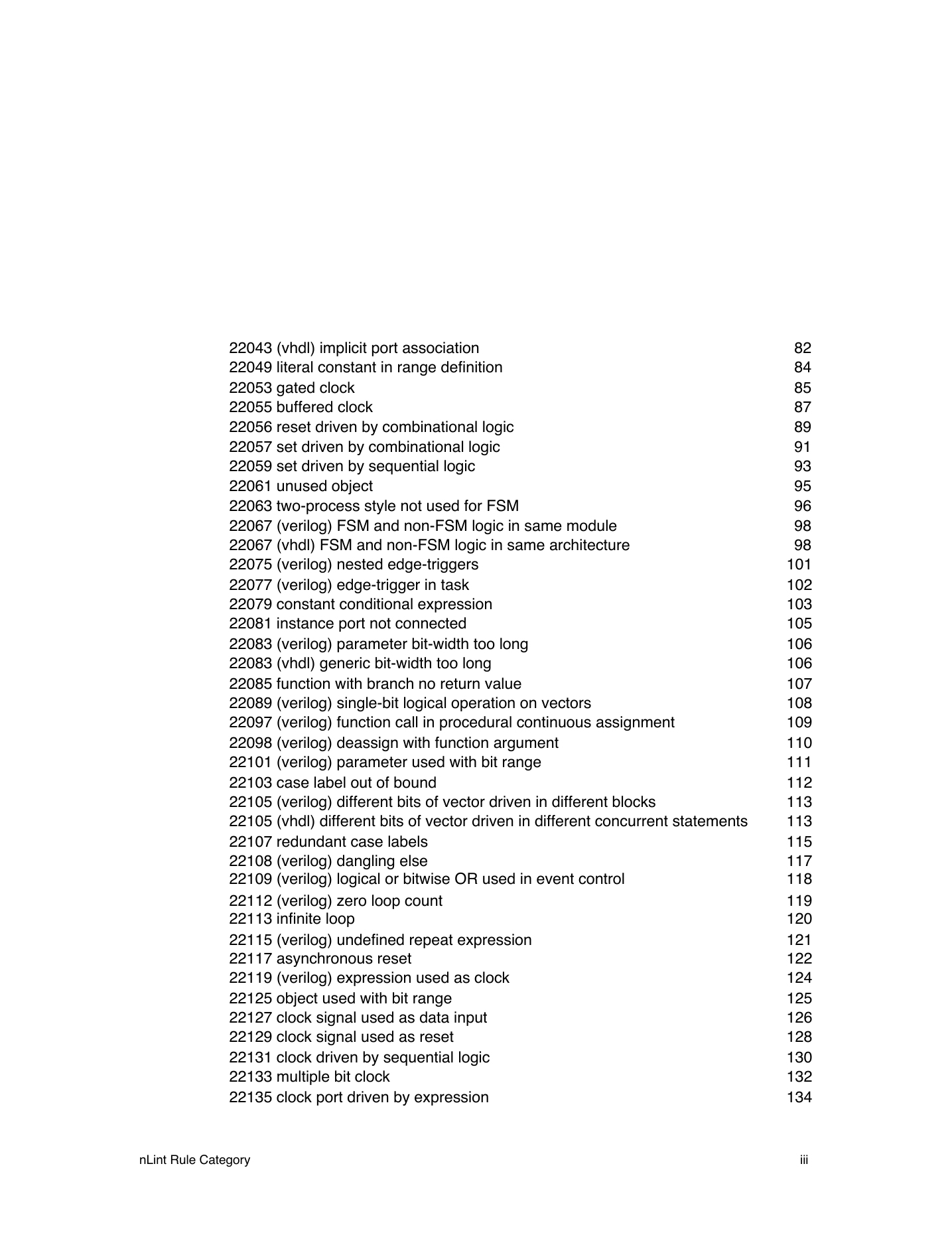

22043 (vhdl) implicit port association

22049 literal constant in range definition

22053 gated clock

22055 buffered clock

22056 reset driven by combinational logic

22057 set driven by combinational logic

22059 set driven by sequential logic

22061 unused object

22063 two-process style not used for FSM

22067 (verilog) FSM and non-FSM logic in same module

22067 (vhdl) FSM and non-FSM logic in same architecture

22075 (verilog) nested edge-triggers

22077 (verilog) edge-trigger in task

22079 constant conditional expression

22081 instance port not connected

22083 (verilog) parameter bit-width too long

22083 (vhdl) generic bit-width too long

22085 function with branch no return value

22089 (verilog) single-bit logical operation on vectors

22097 (verilog) function call in procedural continuous assignment

22098 (verilog) deassign with function argument

22101 (verilog) parameter used with bit range

22103 case label out of bound

22105 (verilog) different bits of vector driven in different blocks

22105 (vhdl) different bits of vector driven in different concurrent statements

22107 redundant case labels

22108 (verilog) dangling else

22109 (verilog) logical or bitwise OR used in event control

22112 (verilog) zero loop count

22113 infinite loop

22115 (verilog) undefined repeat expression

22117 asynchronous reset

22119 (verilog) expression used as clock

22125 object used with bit range

22127 clock signal used as data input

22129 clock signal used as reset

22131 clock driven by sequential logic

22133 multiple bit clock

22135 clock port driven by expression

nLint Rule Category

82

84

85

87

89

91

93

95

96

98

98

101

102

103

105

106

106

107

108

109

110

111

112

113

113

115

117

118

119

120

121

122

124

125

126

128

130

132

134

iii

�

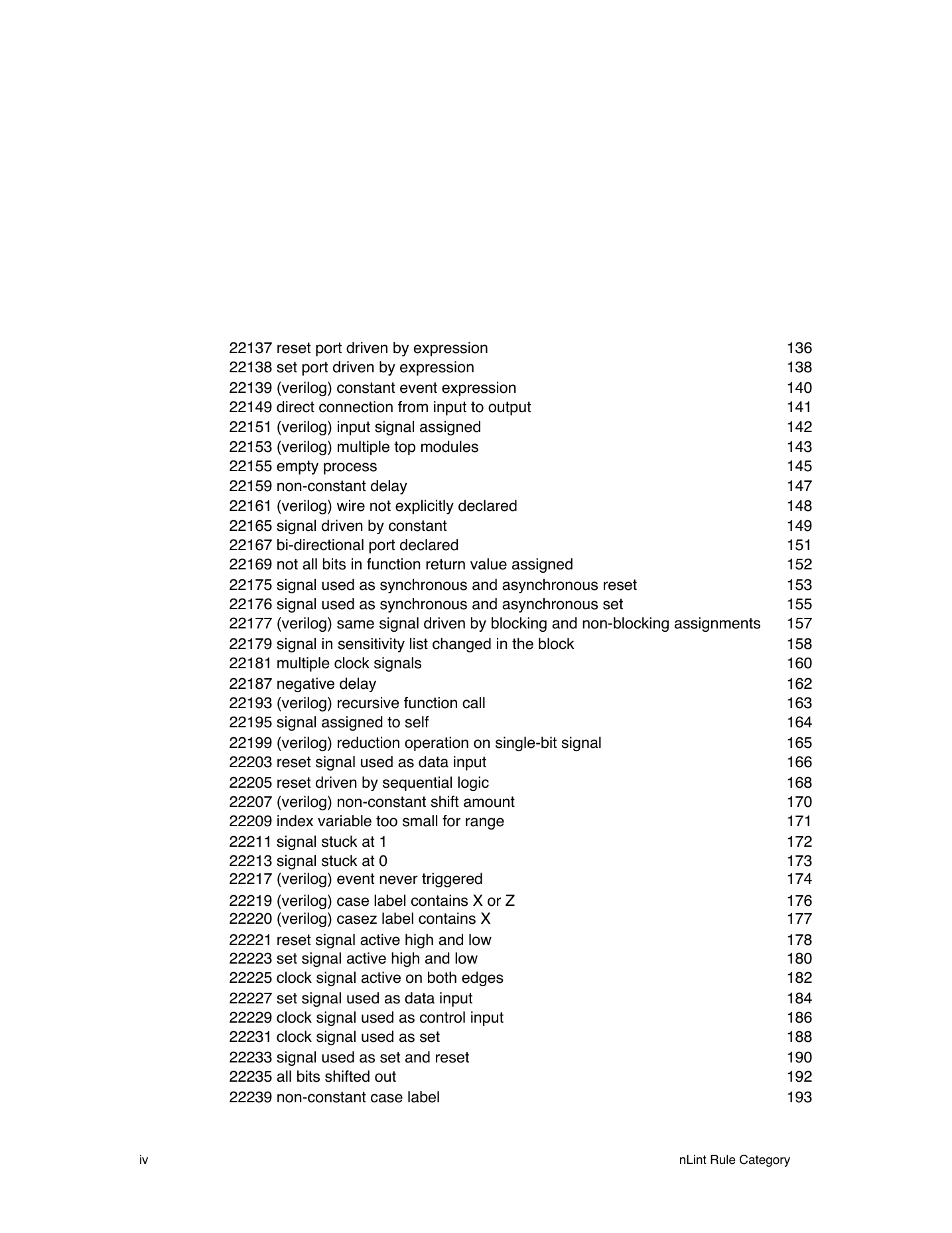

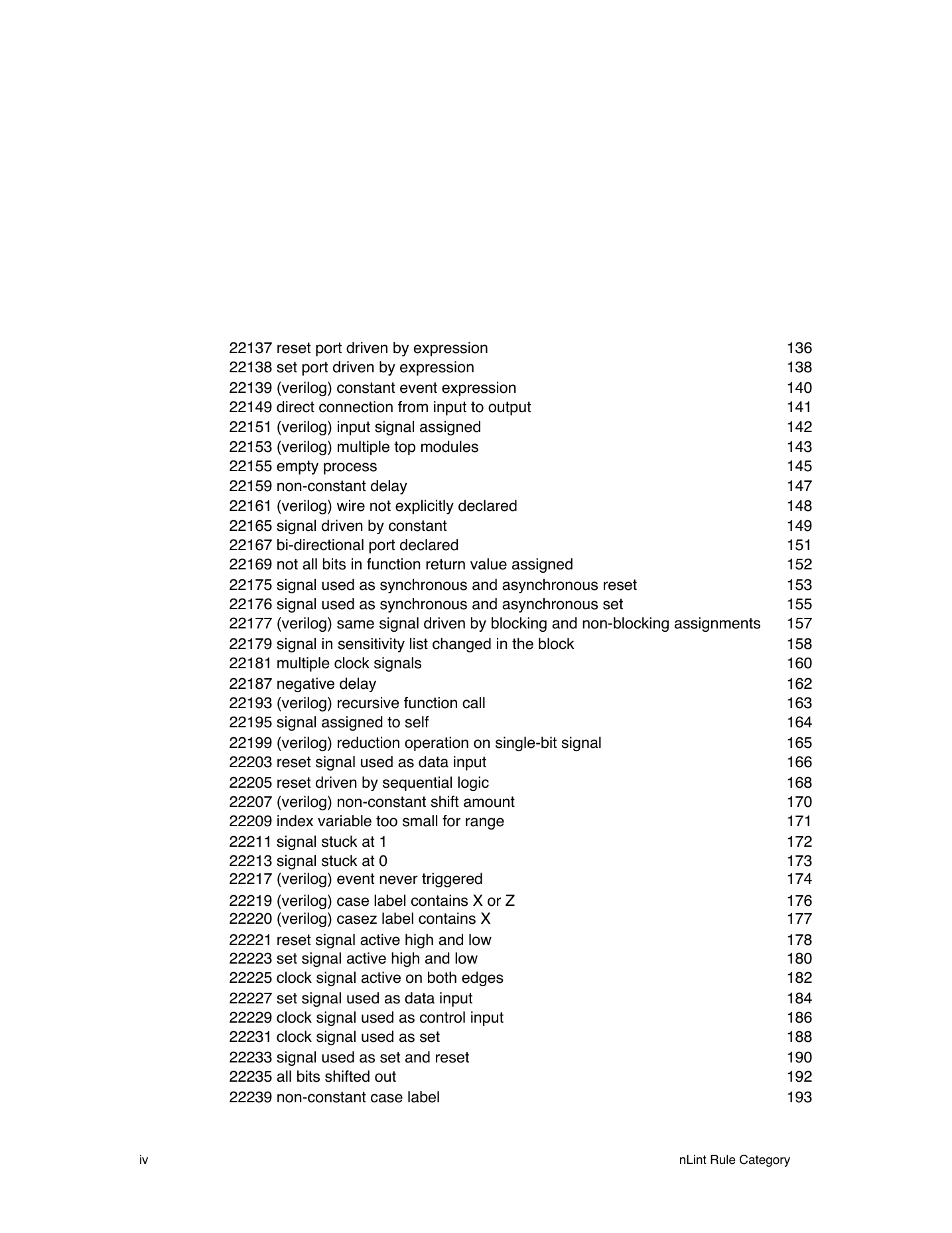

22137 reset port driven by expression

22138 set port driven by expression

22139 (verilog) constant event expression

22149 direct connection from input to output

22151 (verilog) input signal assigned

22153 (verilog) multiple top modules

22155 empty process

22159 non-constant delay

22161 (verilog) wire not explicitly declared

22165 signal driven by constant

22167 bi-directional port declared

22169 not all bits in function return value assigned

22175 signal used as synchronous and asynchronous reset

22176 signal used as synchronous and asynchronous set

22177 (verilog) same signal driven by blocking and non-blocking assignments

22179 signal in sensitivity list changed in the block

22181 multiple clock signals

22187 negative delay

22193 (verilog) recursive function call

22195 signal assigned to self

22199 (verilog) reduction operation on single-bit signal

22203 reset signal used as data input

22205 reset driven by sequential logic

22207 (verilog) non-constant shift amount

22209 index variable too small for range

22211 signal stuck at 1

22213 signal stuck at 0

22217 (verilog) event never triggered

22219 (verilog) case label contains X or Z

22220 (verilog) casez label contains X

22221 reset signal active high and low

22223 set signal active high and low

22225 clock signal active on both edges

22227 set signal used as data input

22229 clock signal used as control input

22231 clock signal used as set

22233 signal used as set and reset

22235 all bits shifted out

22239 non-constant case label

136

138

140

141

142

143

145

147

148

149

151

152

153

155

157

158

160

162

163

164

165

166

168

170

171

172

173

174

176

177

178

180

182

184

186

188

190

192

193

iv

nLint Rule Category

�

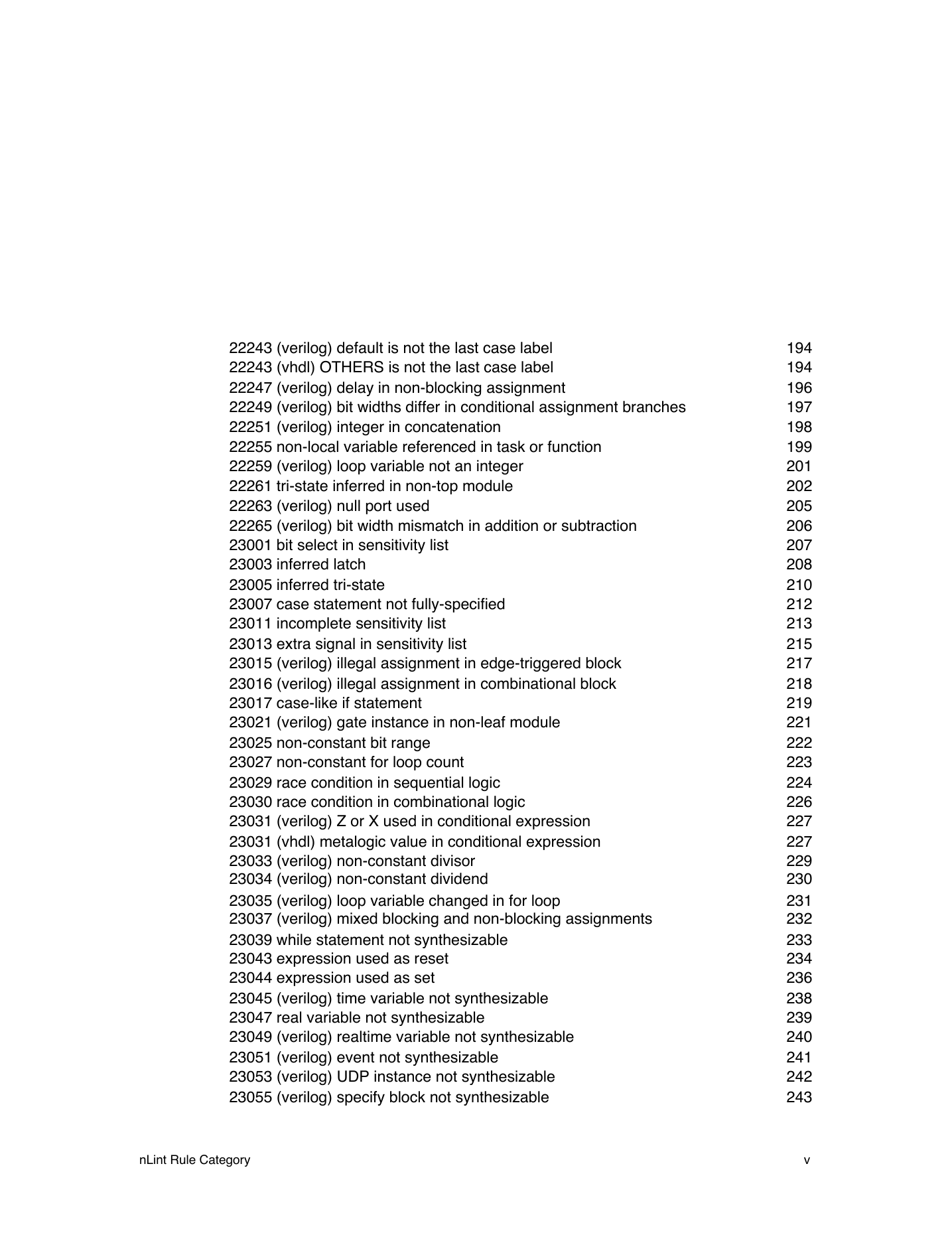

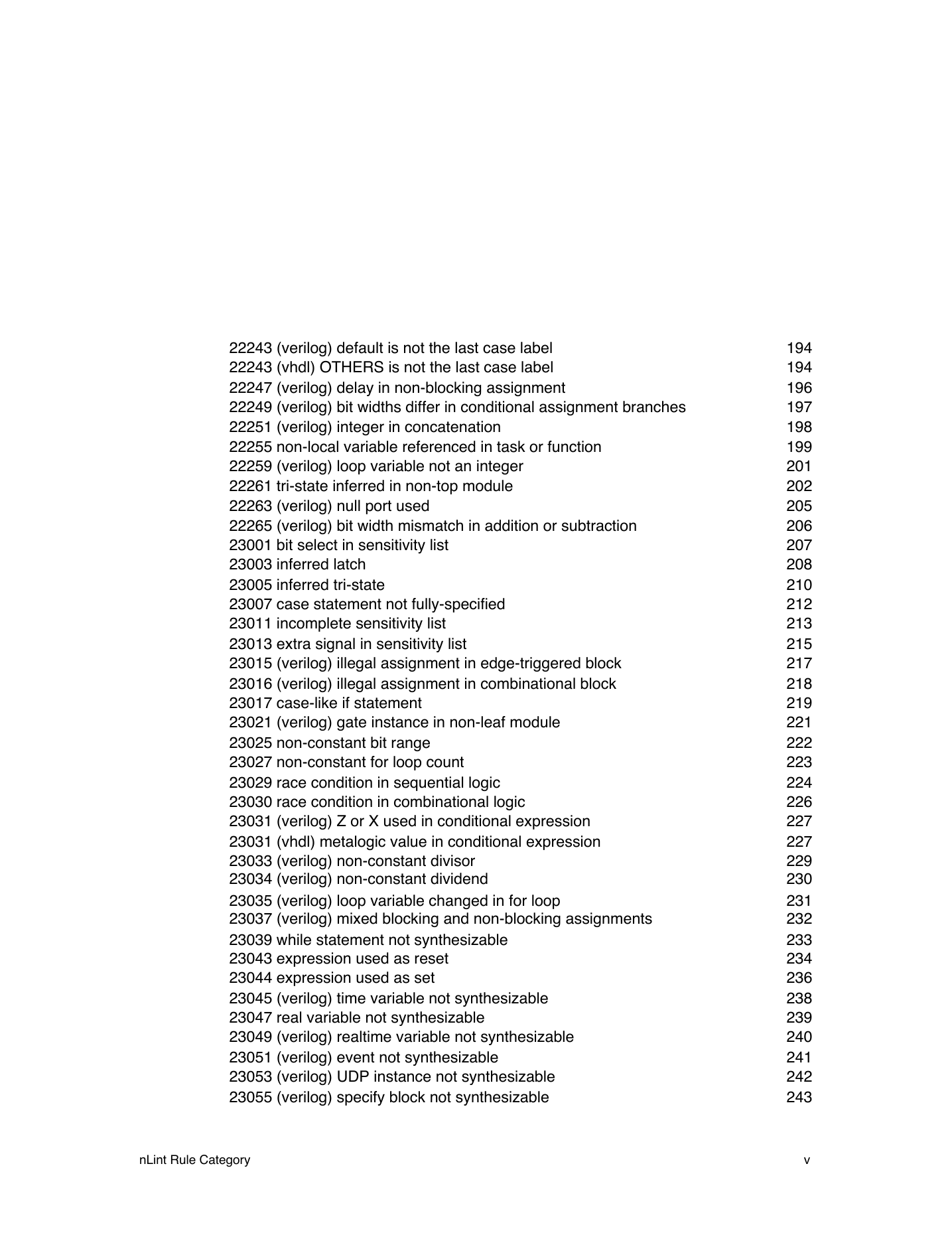

22243 (verilog) default is not the last case label

22243 (vhdl) OTHERS is not the last case label

22247 (verilog) delay in non-blocking assignment

22249 (verilog) bit widths differ in conditional assignment branches

22251 (verilog) integer in concatenation

22255 non-local variable referenced in task or function

22259 (verilog) loop variable not an integer

22261 tri-state inferred in non-top module

22263 (verilog) null port used

22265 (verilog) bit width mismatch in addition or subtraction

23001 bit select in sensitivity list

23003 inferred latch

23005 inferred tri-state

23007 case statement not fully-specified

23011 incomplete sensitivity list

23013 extra signal in sensitivity list

23015 (verilog) illegal assignment in edge-triggered block

23016 (verilog) illegal assignment in combinational block

23017 case-like if statement

23021 (verilog) gate instance in non-leaf module

23025 non-constant bit range

23027 non-constant for loop count

23029 race condition in sequential logic

23030 race condition in combinational logic

23031 (verilog) Z or X used in conditional expression

23031 (vhdl) metalogic value in conditional expression

23033 (verilog) non-constant divisor

23034 (verilog) non-constant dividend

23035 (verilog) loop variable changed in for loop

23037 (verilog) mixed blocking and non-blocking assignments

23039 while statement not synthesizable

23043 expression used as reset

23044 expression used as set

23045 (verilog) time variable not synthesizable

23047 real variable not synthesizable

23049 (verilog) realtime variable not synthesizable

23051 (verilog) event not synthesizable

23053 (verilog) UDP instance not synthesizable

23055 (verilog) specify block not synthesizable

nLint Rule Category

194

194

196

197

198

199

201

202

205

206

207

208

210

212

213

215

217

218

219

221

222

223

224

226

227

227

229

230

231

232

233

234

236

238

239

240

241

242

243

v

�

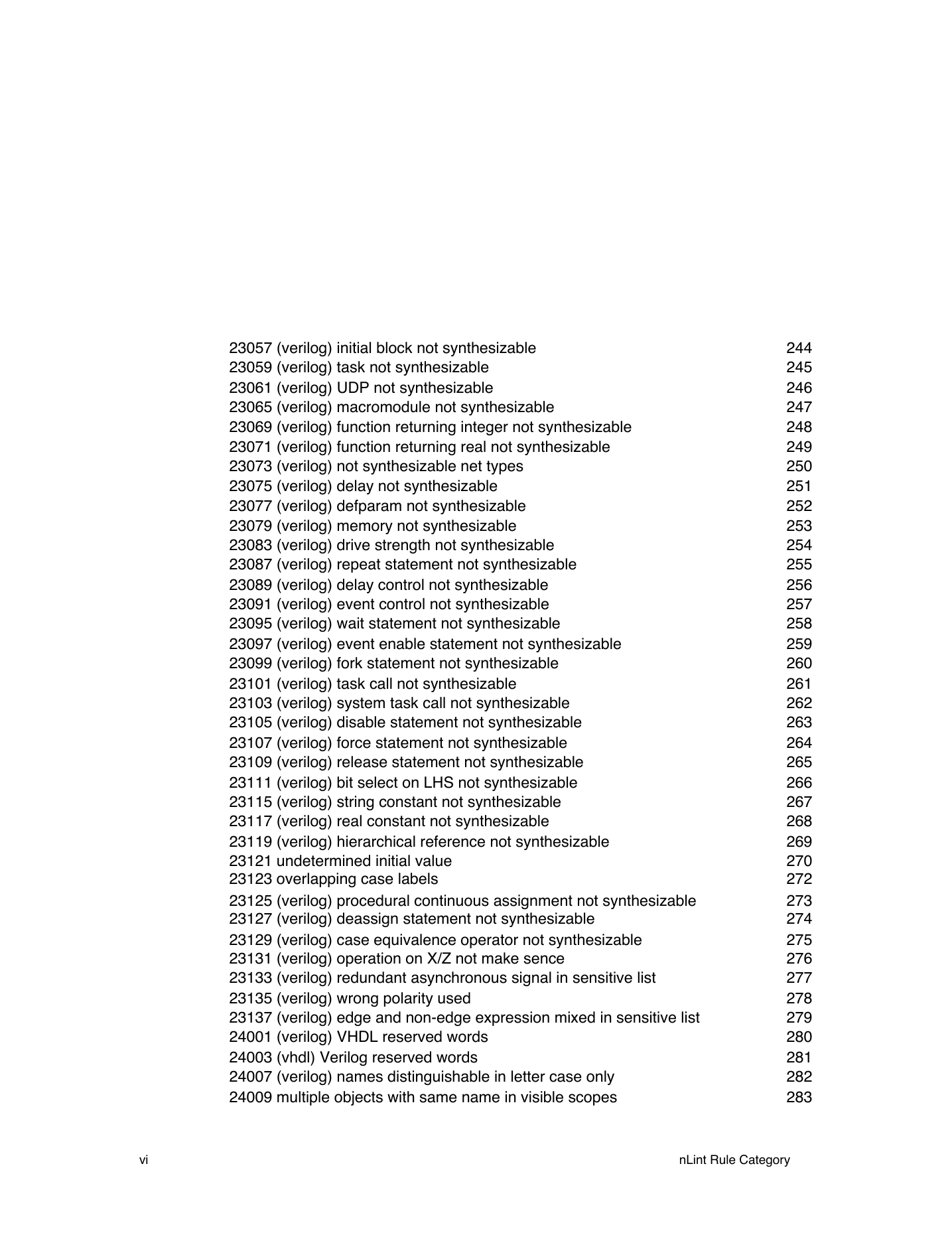

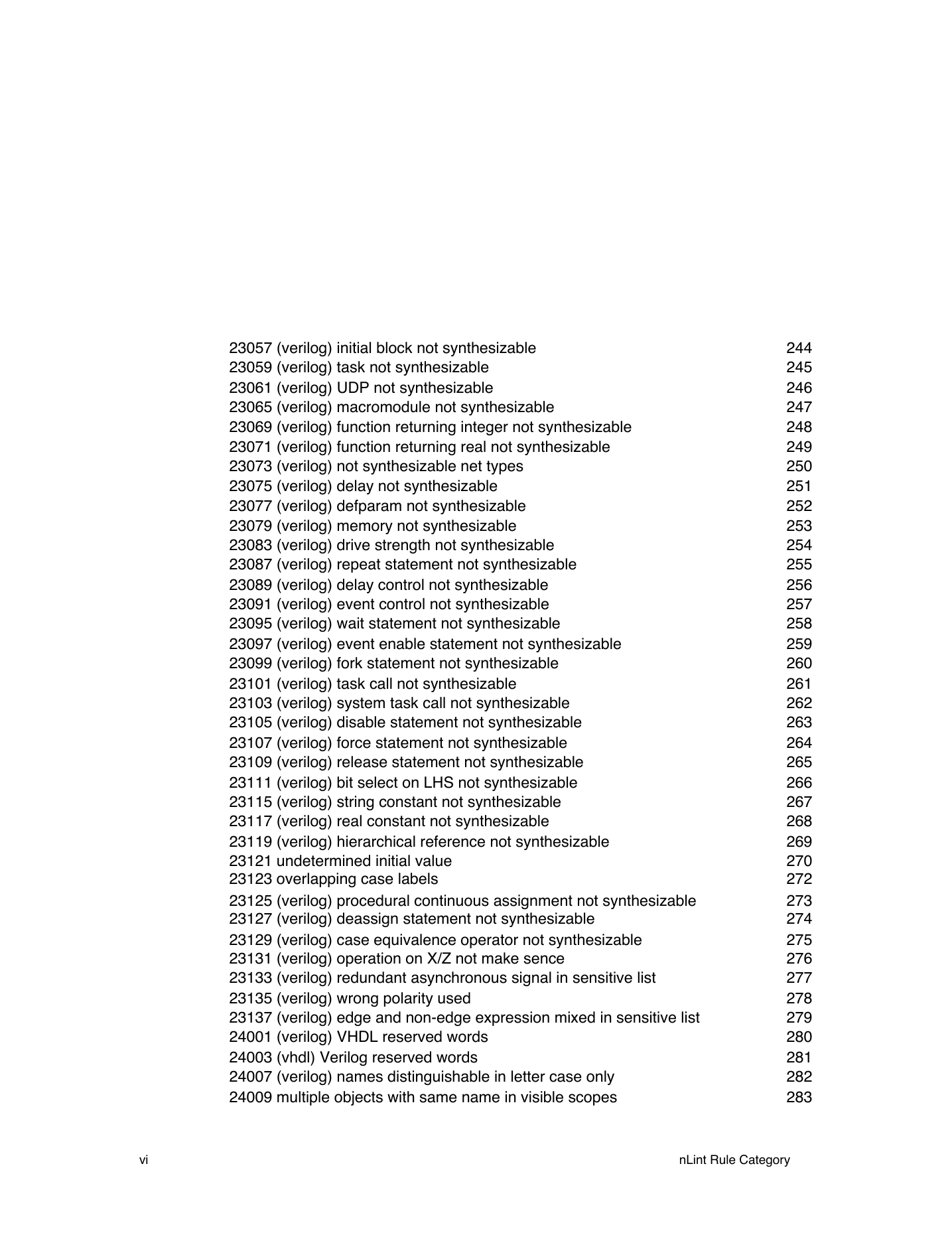

23057 (verilog) initial block not synthesizable

23059 (verilog) task not synthesizable

23061 (verilog) UDP not synthesizable

23065 (verilog) macromodule not synthesizable

23069 (verilog) function returning integer not synthesizable

23071 (verilog) function returning real not synthesizable

23073 (verilog) not synthesizable net types

23075 (verilog) delay not synthesizable

23077 (verilog) defparam not synthesizable

23079 (verilog) memory not synthesizable

23083 (verilog) drive strength not synthesizable

23087 (verilog) repeat statement not synthesizable

23089 (verilog) delay control not synthesizable

23091 (verilog) event control not synthesizable

23095 (verilog) wait statement not synthesizable

23097 (verilog) event enable statement not synthesizable

23099 (verilog) fork statement not synthesizable

23101 (verilog) task call not synthesizable

23103 (verilog) system task call not synthesizable

23105 (verilog) disable statement not synthesizable

23107 (verilog) force statement not synthesizable

23109 (verilog) release statement not synthesizable

23111 (verilog) bit select on LHS not synthesizable

23115 (verilog) string constant not synthesizable

23117 (verilog) real constant not synthesizable

23119 (verilog) hierarchical reference not synthesizable

23121 undetermined initial value

23123 overlapping case labels

23125 (verilog) procedural continuous assignment not synthesizable

23127 (verilog) deassign statement not synthesizable

23129 (verilog) case equivalence operator not synthesizable

23131 (verilog) operation on X/Z not make sence

23133 (verilog) redundant asynchronous signal in sensitive list

23135 (verilog) wrong polarity used

23137 (verilog) edge and non-edge expression mixed in sensitive list

24001 (verilog) VHDL reserved words

24003 (vhdl) Verilog reserved words

24007 (verilog) names distinguishable in letter case only

24009 multiple objects with same name in visible scopes

244

245

246

247

248

249

250

251

252

253

254

255

256

257

258

259

260

261

262

263

264

265

266

267

268

269

270

272

273

274

275

276

277

278

279

280

281

282

283

vi

nLint Rule Category

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc