多路彩灯控制器的设计与分析

一、系统设计要求

今需设计一个十六路彩灯控制器,六种花型循环变化,有清零

开关,并且选择快慢两种节拍。

硬件描述语言(HDL)是相对于一般的计算机软件语言而言的。

HDL 是用于设计硬件电子系统的计算机语言,他描述电子系统的

逻辑功能,电路结构和连接方式。设计者可以用 HDL 程序来描述

所希望的电路系统,规定其结构特征和电路的行为方式,然后利

用综合器和适配器将此程序变成控制 FPGA 和 CPLD 内部结构,并

实现相应逻辑功能的门级或更底层的结构网表文件和下载文件。

VHDL 主要用于描述数字系统的结构,行为,功能和接口。与其他

的 HDL 语言相比,VHDL 具有更强的行为描述能力,从而决定了它

成为系统设计领域最佳的硬件描述语言。强大的行为描述能力是

避开具体的器件结构。从逻辑行为上描述和设计大规模电子系统

的重要保证。EDA 功能强大,描述能力强,可移植性好研制周期

短.成本低等特点,本课题以 Alter 公司提供的 Max+Plus 为平台,

设计一个可变速的彩灯控制器,可以在不修改硬件电路的基础上,

仅通过更改软件就能实现任意修改花型的编程控制方案,实现 16

只 LED 以 6 种花型和两种速度循环变化显示,而且设计非常方便,

设计的电路保密性。

二、课程设计目的

1.进一步掌握数字电路课程所学的理论知识。

2.了解数字电路设计的基本思想和方法,学会科学分析和解决问题。

3.熟悉几种常用集成数字芯片,并掌握工作原理,进一步学会使用

其进行电路设计。

4.培养独立思考的能力和动手操作的能力。

三、总体设计步骤

�

1,设计思路

用 VHDL 进行设计,首先应该理解,VHDL 语言是一种全方位硬

件描述语言,包括系统行为级,寄存器传输级和逻辑门级多个设

计层次。应充分利用 VHDL 自顶向下的设计优点以及层次化的设计

概念,层次概念对于设计复杂的数字系统是非常有用的,它使得

我们可以从简单的单元入手,逐渐构成庞大而复杂的系统。

首先进行系统模块的划分,规定每一个模块的功能以及各模块

之间的接口,最终设计方案分为三大模块:16 路花样彩灯显示器.

时序控制器,整个电路系统,从而达到控制彩灯闪烁速度的快慢和

花型的变换。

自动控制多路彩灯按预设的花型进行转换;花型种类不少于三种;

花型自拟分别用快慢两种节拍实现花型变换

选择:用可编辑逻辑 器实现

二、设计方案的设计

根据题目实际要求,经过分析与思考,拟定以下两种方案:

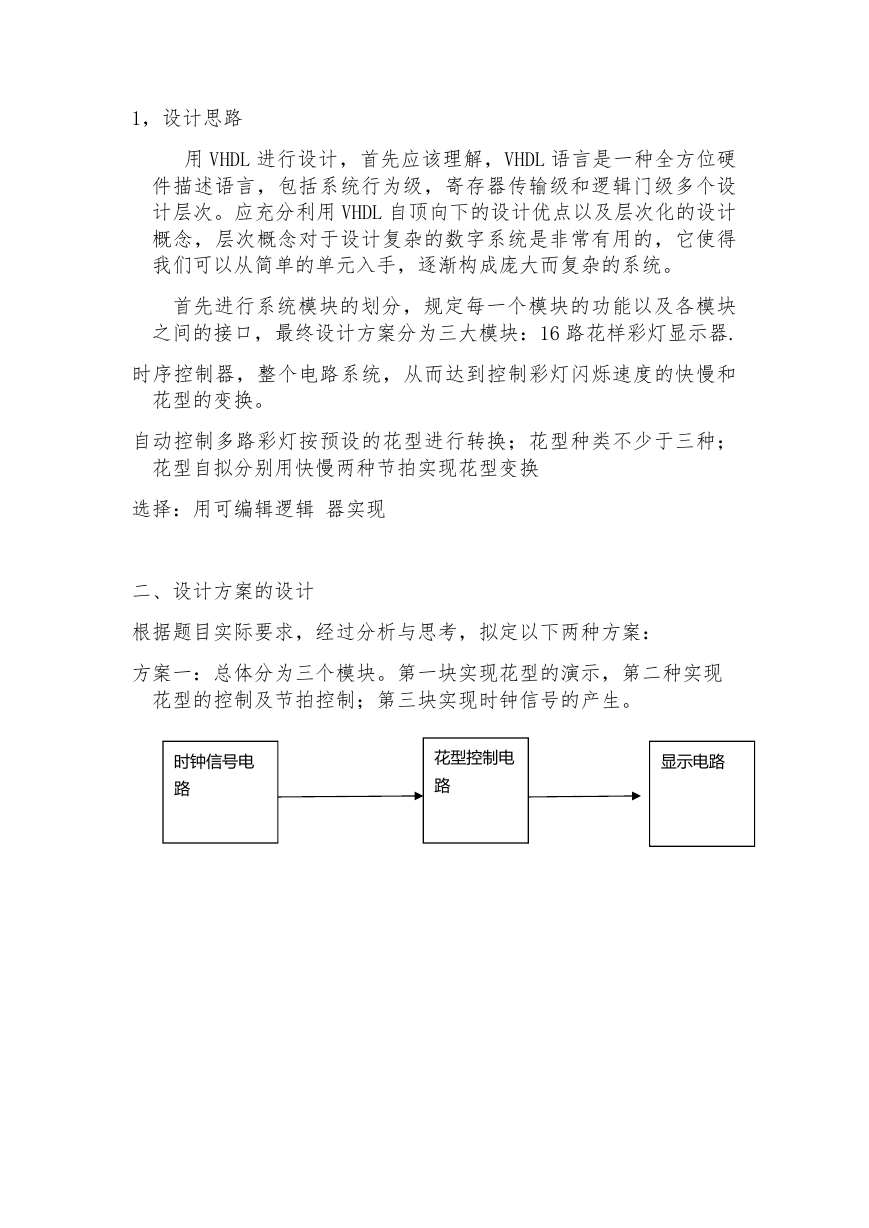

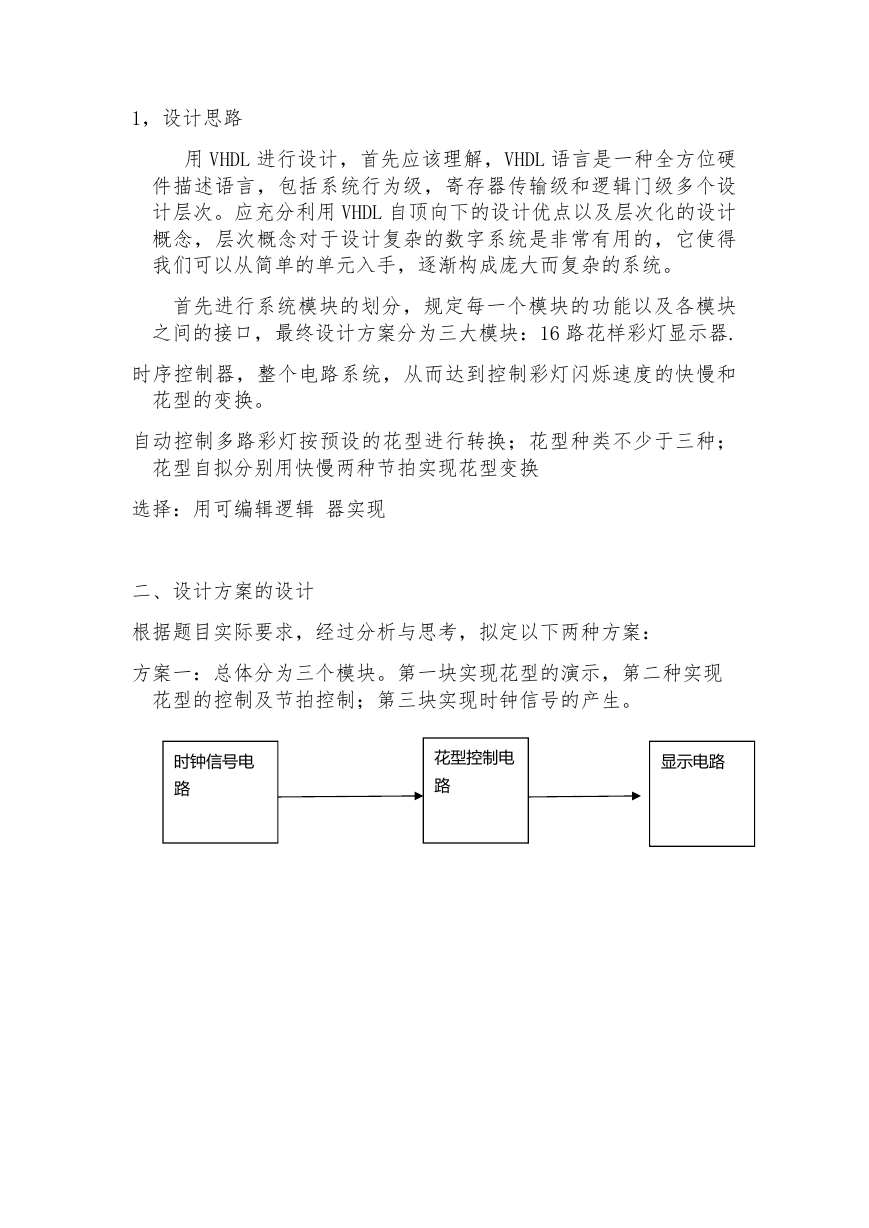

方案一:总体分为三个模块。第一块实现花型的演示,第二种实现

花型的控制及节拍控制;第三块实现时钟信号的产生。

时钟信号电

路

花型控制电

路

显示电路

�

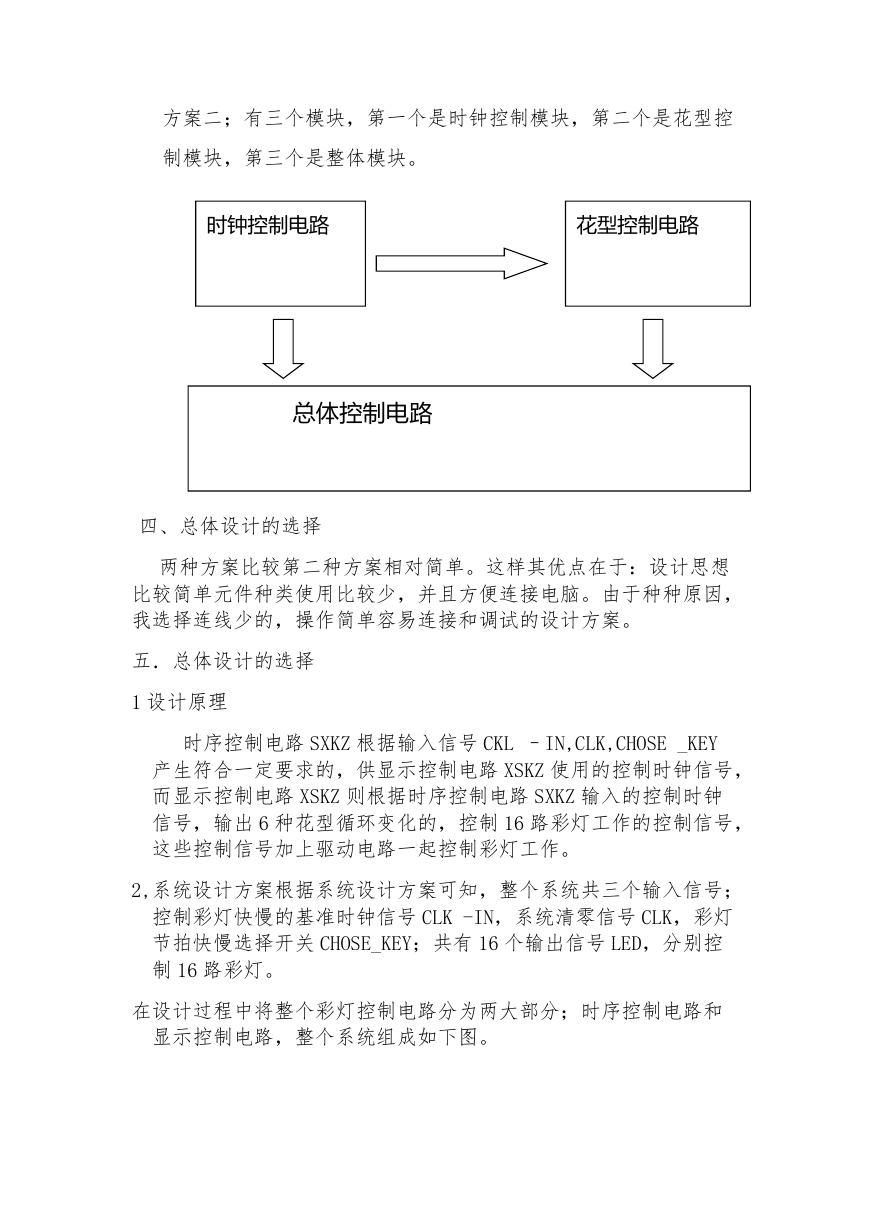

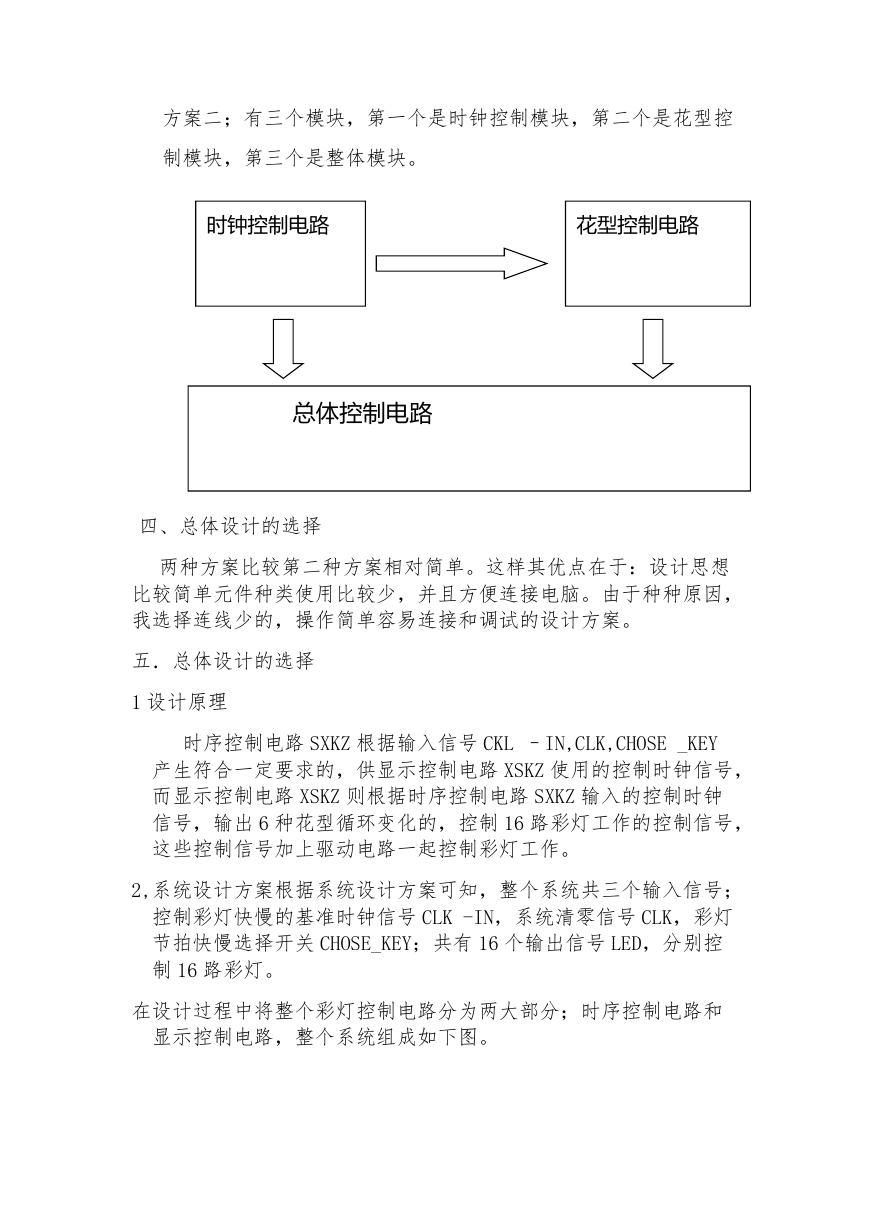

方案二;有三个模块,第一个是时钟控制模块,第二个是花型控

制模块,第三个是整体模块。

时钟控制电路

花型控制电路

总体控制电路

四、总体设计的选择

两种方案比较第二种方案相对简单。这样其优点在于:设计思想

比较简单元件种类使用比较少,并且方便连接电脑。由于种种原因,

我选择连线少的,操作简单容易连接和调试的设计方案。

五.总体设计的选择

1 设计原理

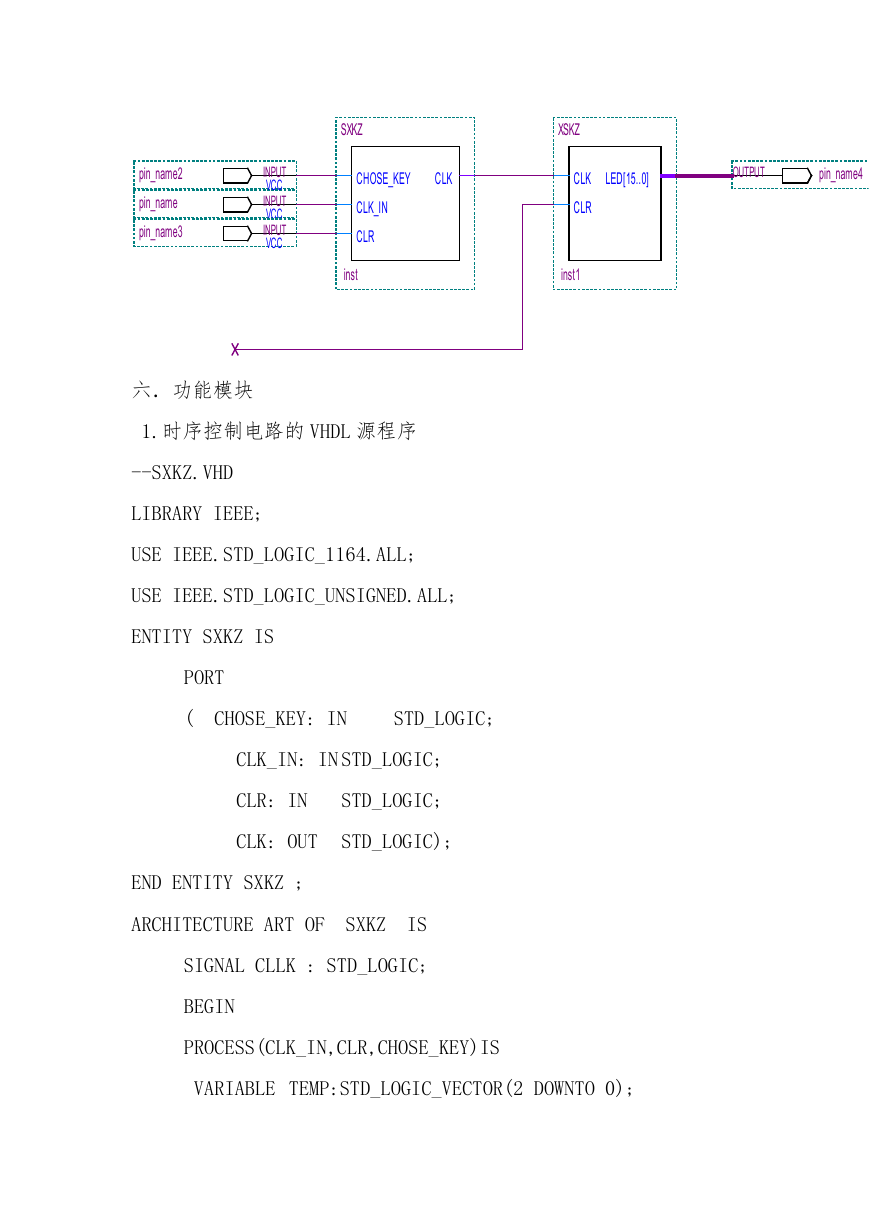

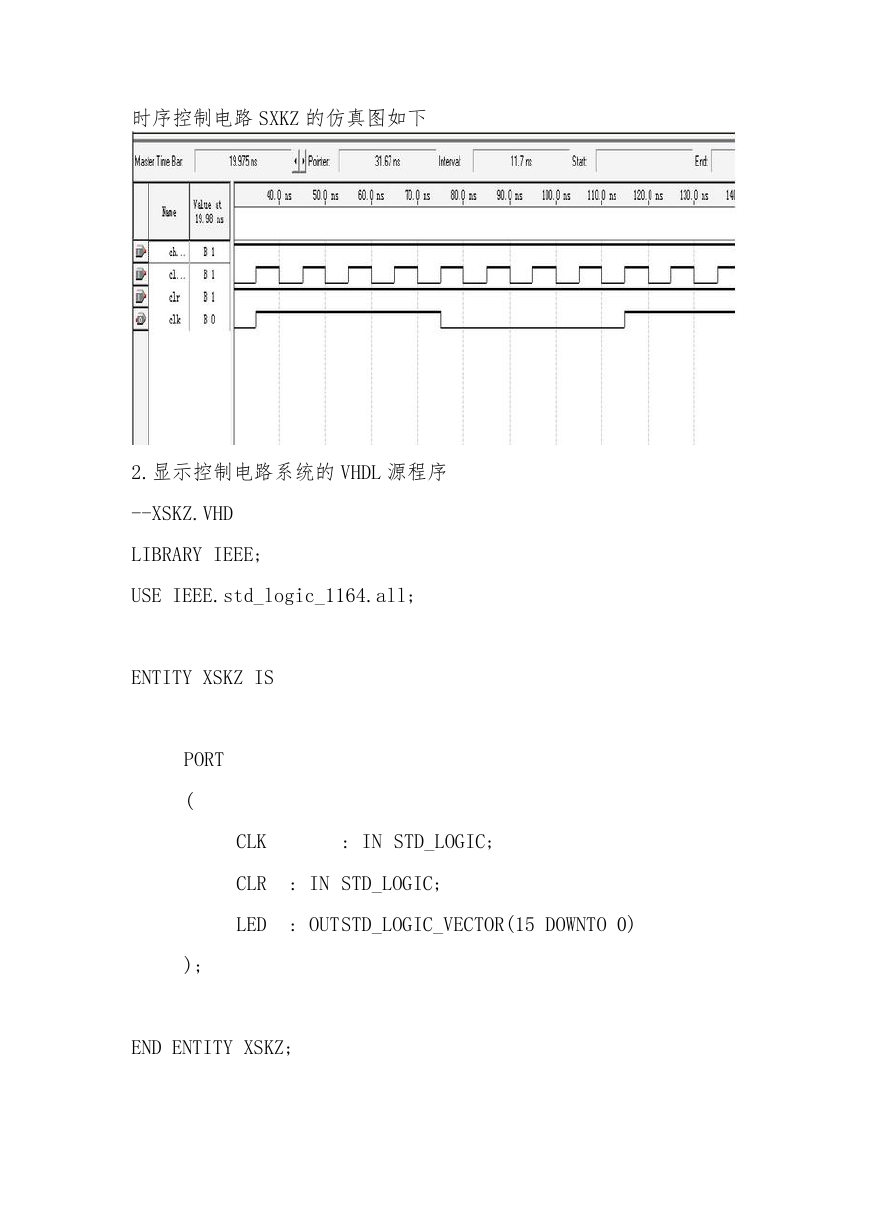

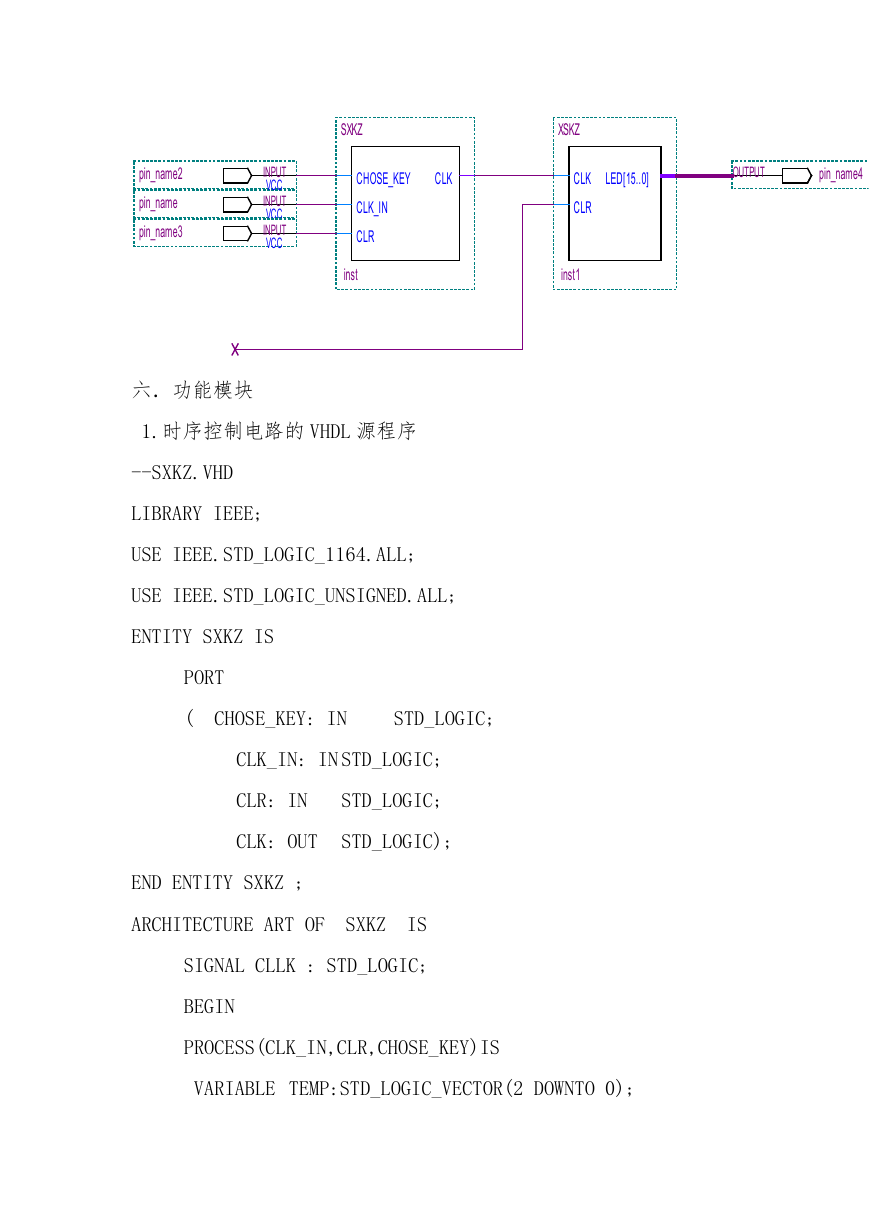

时序控制电路 SXKZ 根据输入信号 CKL –IN,CLK,CHOSE _KEY

产生符合一定要求的,供显示控制电路 XSKZ 使用的控制时钟信号,

而显示控制电路 XSKZ 则根据时序控制电路 SXKZ 输入的控制时钟

信号,输出 6 种花型循环变化的,控制 16 路彩灯工作的控制信号,

这些控制信号加上驱动电路一起控制彩灯工作。

2,系统设计方案根据系统设计方案可知,整个系统共三个输入信号;

控制彩灯快慢的基准时钟信号 CLK -IN,系统清零信号 CLK,彩灯

节拍快慢选择开关 CHOSE_KEY;共有 16 个输出信号 LED,分别控

制 16 路彩灯。

在设计过程中将整个彩灯控制电路分为两大部分;时序控制电路和

显示控制电路,整个系统组成如下图。

�

pin_name2

pin_name

pin_name3

INPUT

VCC

INPUT

VCC

INPUT

VCC

SXKZ

CLK

CHOSE_KEY

CLK_IN

CLR

inst

XSKZ

CLK

CLR

inst1

LED[15..0]

OUTPUT

pin_name4

六.功能模块

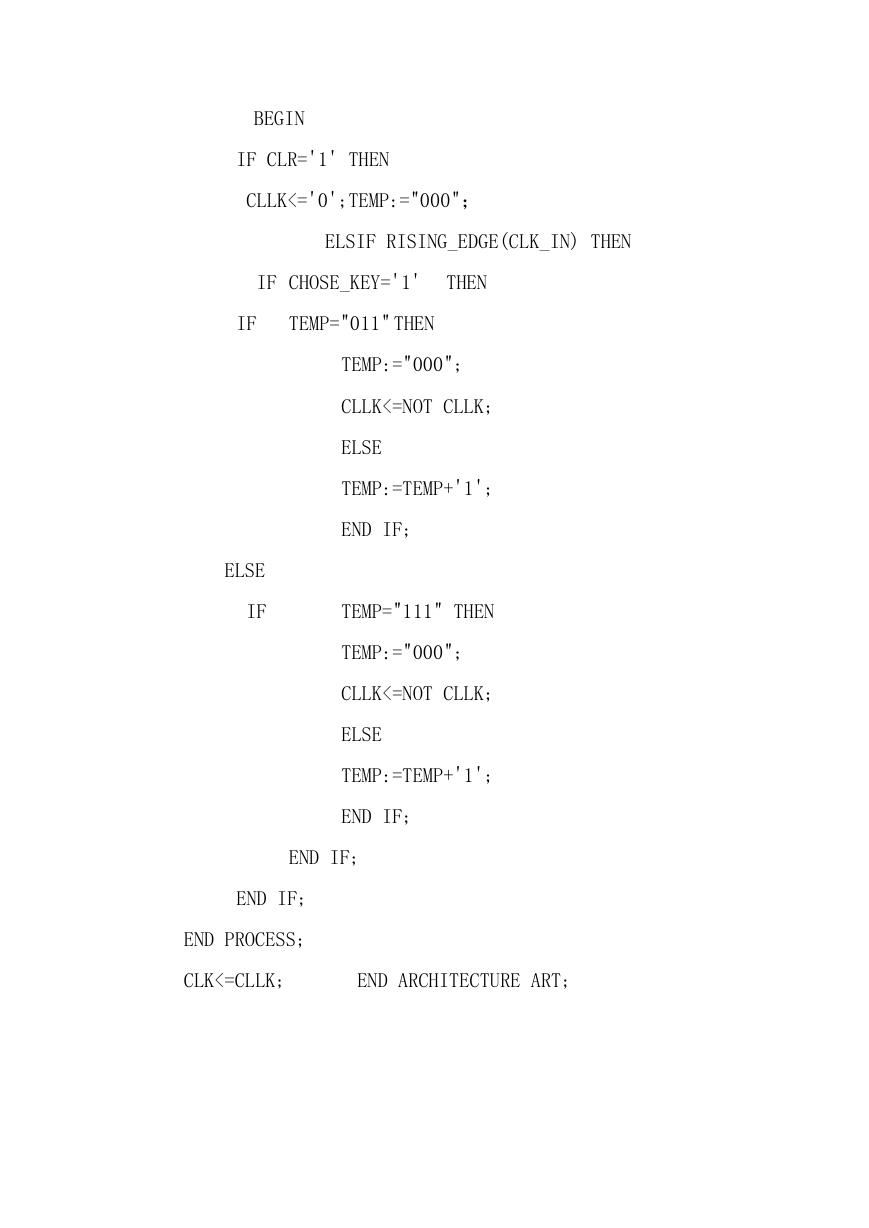

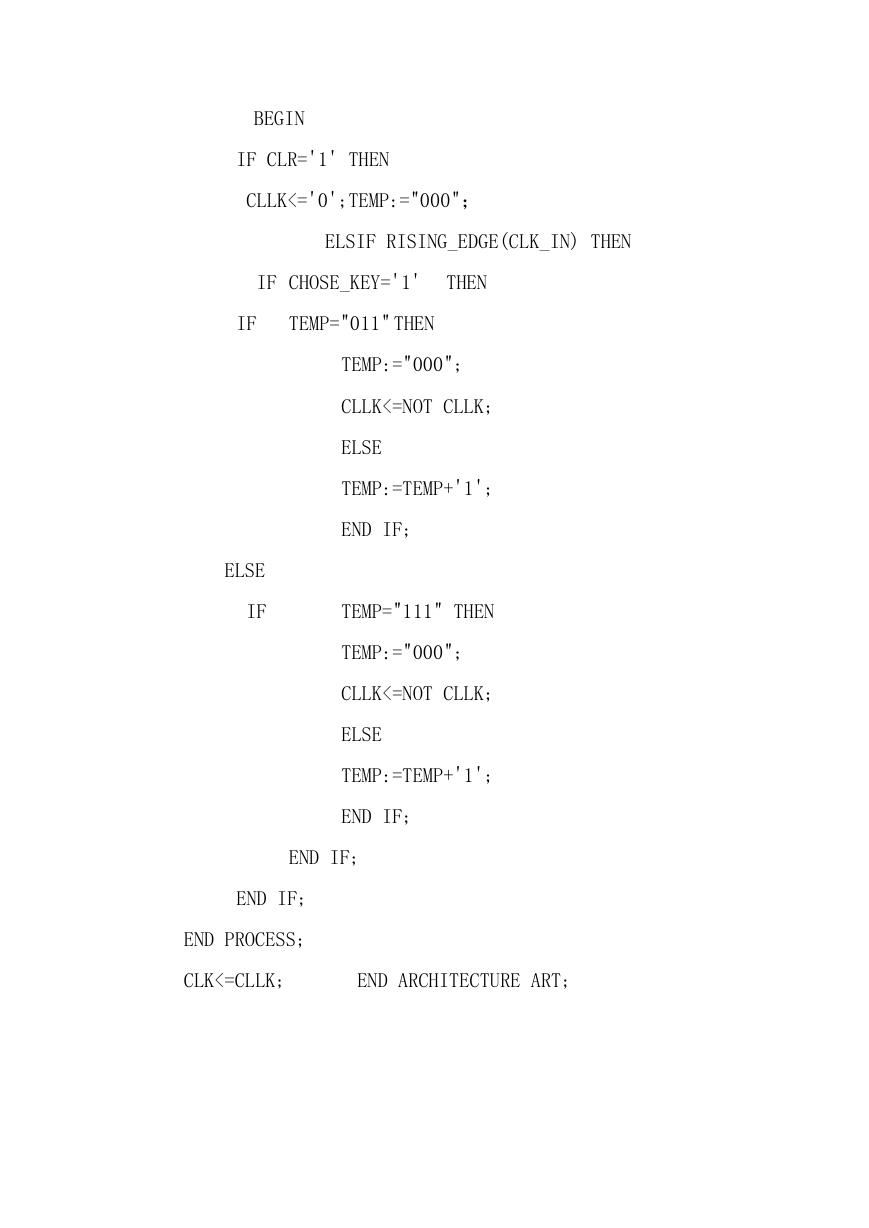

1.时序控制电路的 VHDL 源程序

--SXKZ.VHD

LIBRARY IEEE;

USE IEEE.STD_LOGIC_1164.ALL;

USE IEEE.STD_LOGIC_UNSIGNED.ALL;

ENTITY SXKZ IS

PORT

( CHOSE_KEY: IN

STD_LOGIC;

CLK_IN: IN STD_LOGIC;

CLR: IN

STD_LOGIC;

CLK: OUT

STD_LOGIC);

END ENTITY SXKZ ;

ARCHITECTURE ART OF SXKZ IS

SIGNAL CLLK : STD_LOGIC;

BEGIN

PROCESS(CLK_IN,CLR,CHOSE_KEY)IS

VARIABLE TEMP:STD_LOGIC_VECTOR(2 DOWNTO 0);

�

BEGIN

IF CLR='1' THEN

CLLK<='0';TEMP:="000";

ELSIF RISING_EDGE(CLK_IN) THEN

IF CHOSE_KEY='1'

THEN

IF

TEMP="011" THEN

TEMP:="000";

CLLK<=NOT CLLK;

ELSE

TEMP:=TEMP+'1';

END IF;

TEMP="111" THEN

TEMP:="000";

CLLK<=NOT CLLK;

ELSE

TEMP:=TEMP+'1';

ELSE

IF

END IF;

END IF;

END IF;

END PROCESS;

CLK<=CLLK;

END ARCHITECTURE ART;

�

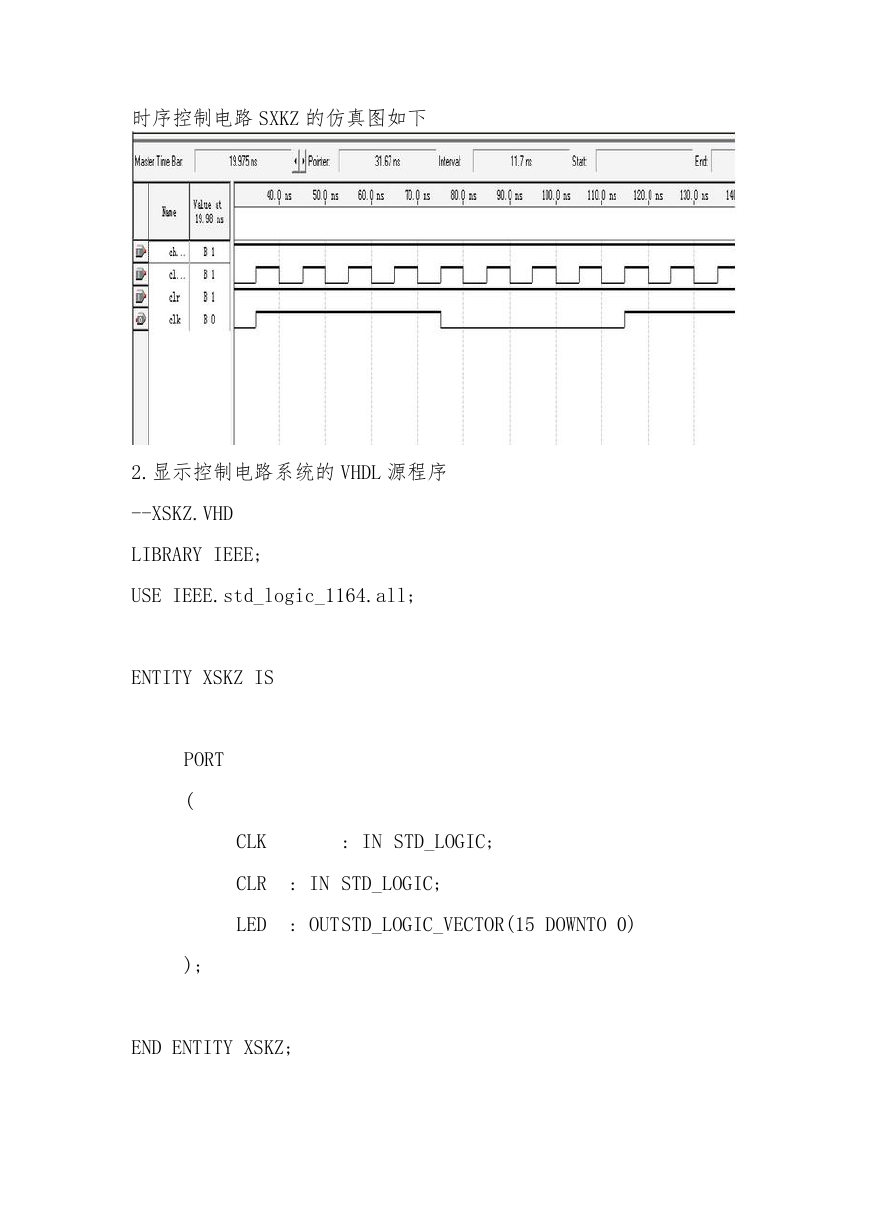

时序控制电路 SXKZ 的仿真图如下

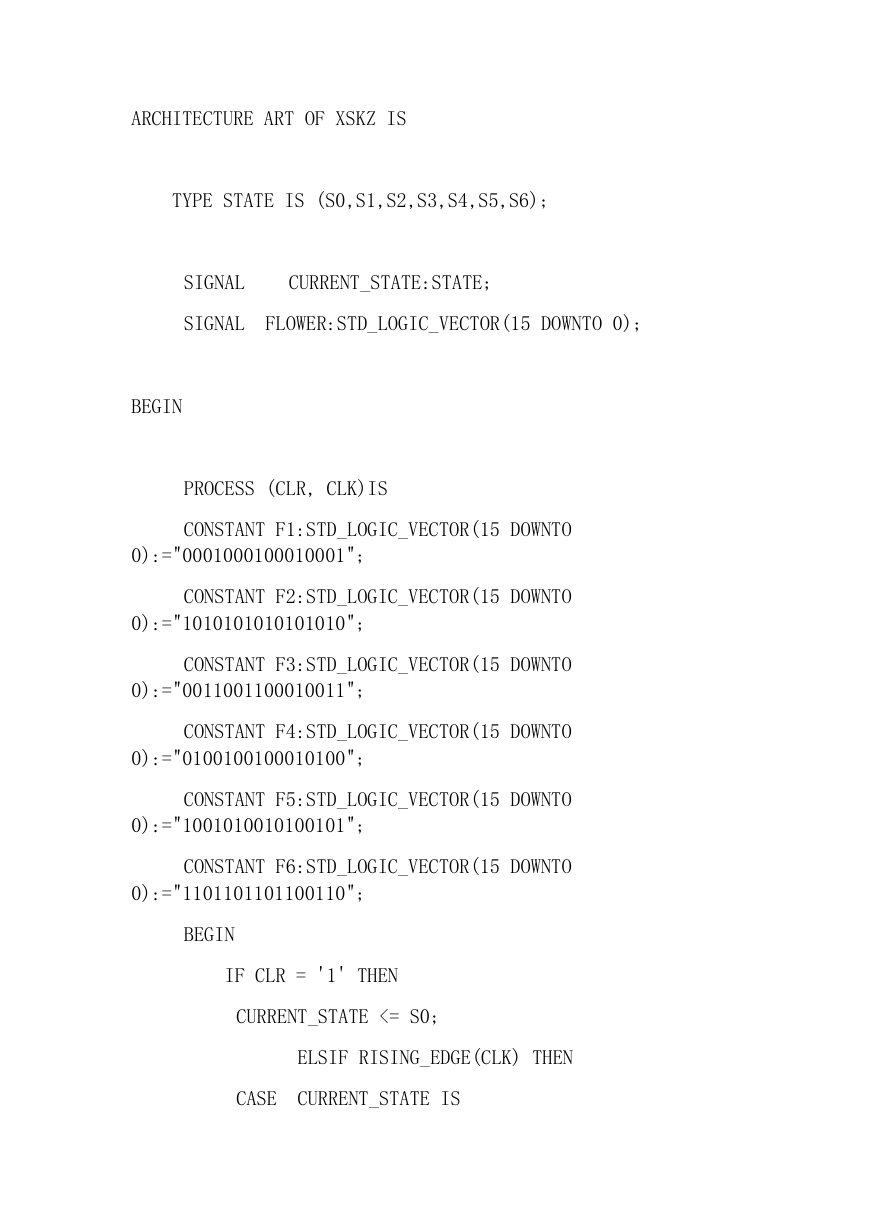

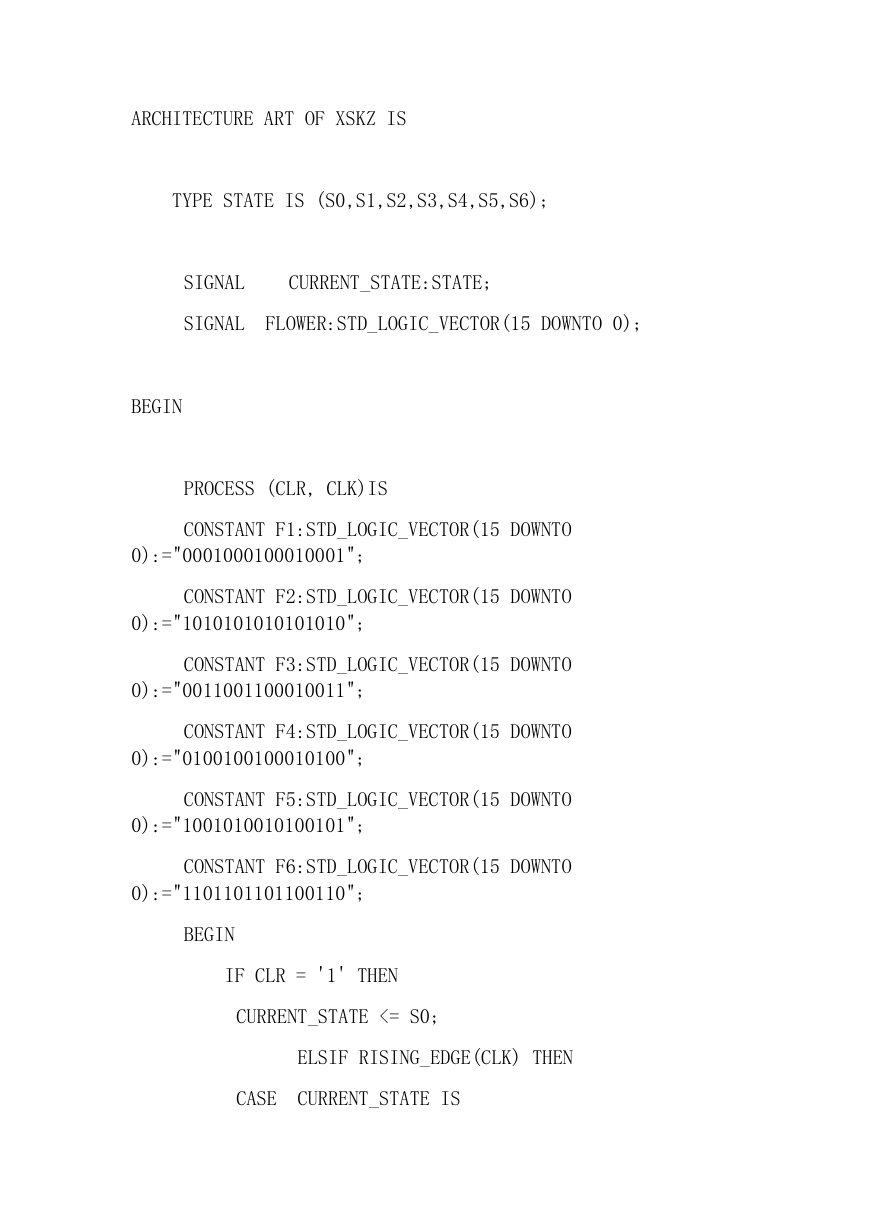

2.显示控制电路系统的 VHDL 源程序

--XSKZ.VHD

LIBRARY IEEE;

USE IEEE.std_logic_1164.all;

ENTITY XSKZ IS

PORT

(

);

CLK

: IN STD_LOGIC;

CLR

: IN STD_LOGIC;

LED

: OUTSTD_LOGIC_VECTOR(15 DOWNTO 0)

END ENTITY XSKZ;

�

ARCHITECTURE ART OF XSKZ IS

TYPE STATE IS (S0,S1,S2,S3,S4,S5,S6);

SIGNAL

CURRENT_STATE:STATE;

SIGNAL FLOWER:STD_LOGIC_VECTOR(15 DOWNTO 0);

BEGIN

PROCESS (CLR, CLK)IS

CONSTANT F1:STD_LOGIC_VECTOR(15 DOWNTO

0):="0001000100010001";

CONSTANT F2:STD_LOGIC_VECTOR(15 DOWNTO

0):="1010101010101010";

CONSTANT F3:STD_LOGIC_VECTOR(15 DOWNTO

0):="0011001100010011";

CONSTANT F4:STD_LOGIC_VECTOR(15 DOWNTO

0):="0100100100010100";

CONSTANT F5:STD_LOGIC_VECTOR(15 DOWNTO

0):="1001010010100101";

CONSTANT F6:STD_LOGIC_VECTOR(15 DOWNTO

0):="1101101101100110";

BEGIN

IF CLR = '1' THEN

CURRENT_STATE <= S0;

ELSIF RISING_EDGE(CLK) THEN

CASE CURRENT_STATE IS

�

WHEN S0=>

FLOWER<="ZZZZZZZZZZZZZZZZ";

CURRENT_STATE<=S1;

WHEN S1=>

FLOWER<=F1;

CURRENT_STATE<=S2;

WHEN S2=>

FLOWER<=F2;

CURRENT_STATE<=S3;

WHEN S3=>

FLOWER<=F3;

CURRENT_STATE<=S4;

WHEN S4=>

FLOWER<=F4;

CURRENT_STATE<=S5;

WHEN S5=>

FLOWER<=F5;

CURRENT_STATE<=S6;

WHEN S6=>

FLOWER<=F6;

CURRENT_STATE<=S1;

END CASE;

END IF;

END PROCESS;

LED<=FLOWER;

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc