10-Pin, 24-Bit, 192 kHz Stereo D/A Converter

CS4344/5/8

Features

Multi-bit Delta-Sigma Modulator

24-bit Conversion

Automatically Detects Sample Rates up to

192 kHz.

105 dB Dynamic Range

-90 dB THD+N

Low Clock-Jitter Sensitivity

Single +3.3 or +5 V Power Supply

Filtered Line-Level Outputs

On-chip Digital De-emphasis

Popguard® Technology

Small 10-pin TSSOP Package

Description

The CS4344 family members (CS4344, CS4345, and

CS4348) are complete, stereo digital-to-analog output

systems including interpolation, multibit D/A conversion

and output analog filtering in a 10-pin package. The

CS4344 family supports major audio data interface for-

mats. Individual devices differ only in the supported

interface format.

The CS4344 family is based on a fourth-order multibit

delta-sigma modulator with a linear analog low-pass fil-

ter. This family also includes autospeed mode detection

using both sample rate and master clock ratio as a

method of auto-selecting sampling rates between 2 kHz

and 200 kHz.

The CS4344 family contains on-chip digital deempha-

sis, operates from a single +3.3 V or +5 V power supply,

and requires minimal support circuitry. These features

are ideal for DVD players & recorders, digital televi-

sions, home theater and set top box products, and

automotive audio systems.

The CS4344 family is available in a 10-pin TSSOP

package in both Commercial (-10 to +85 °C) and Auto-

motive grades (-40 to +85 °C). See Section 8. “Ordering

Information” on page 23 for complete details.

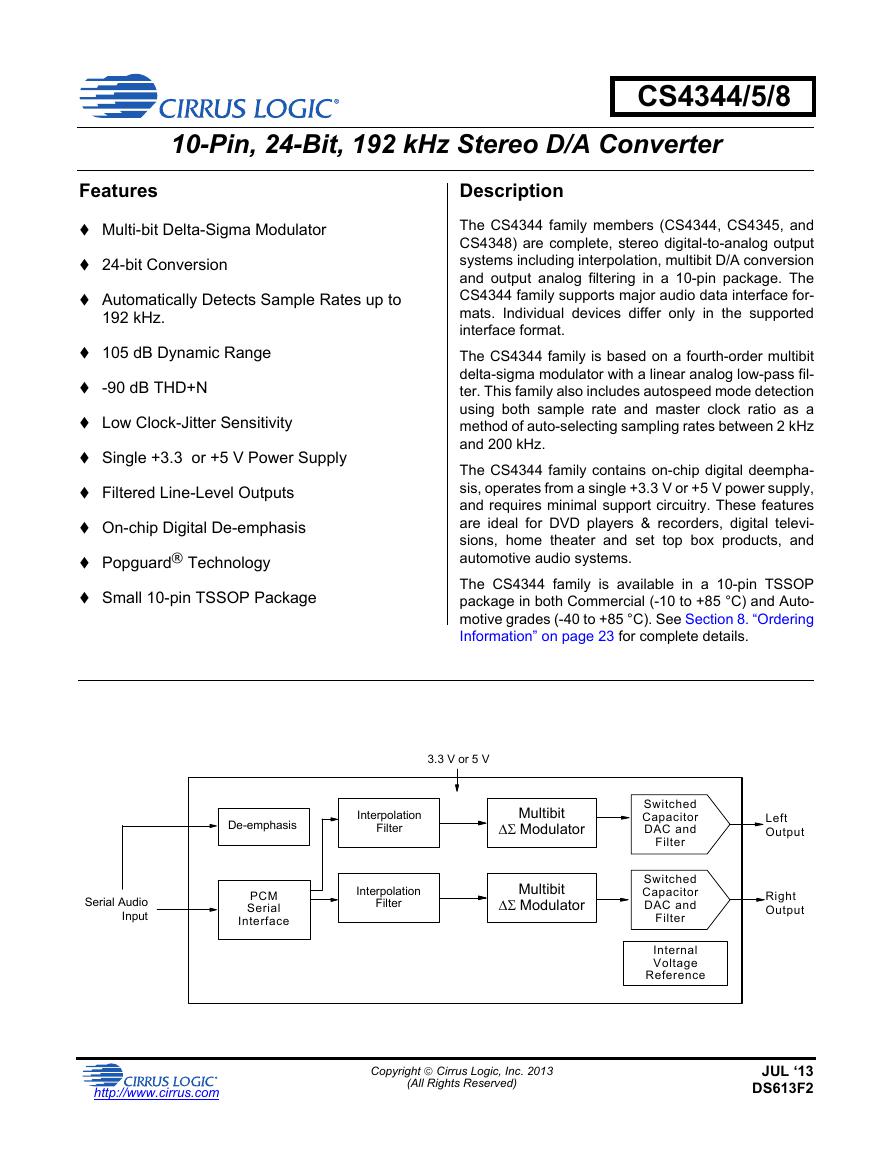

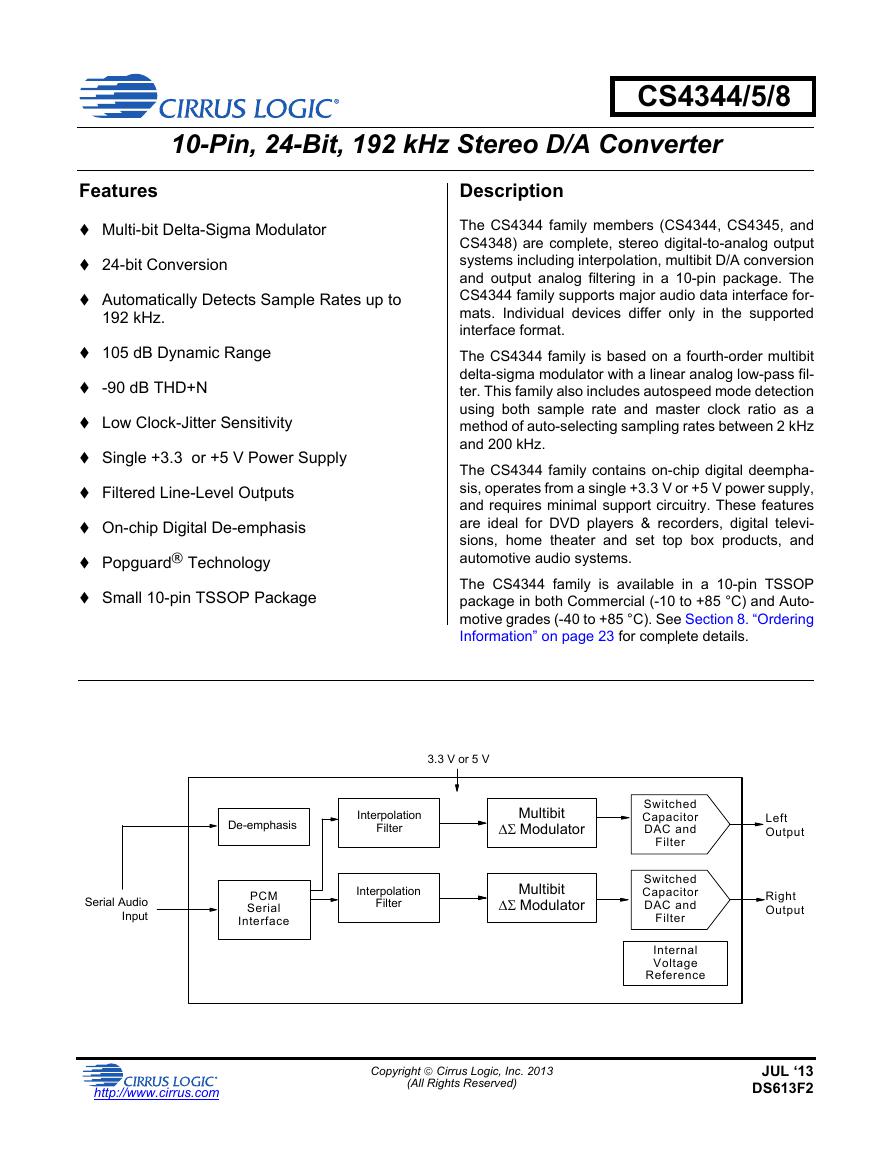

3.3 V or 5 V

De-emphasis

Interpolation

Filter

Multibit

Modulator

Serial Audio

Input

PCM

Serial

Interface

Interpolation

Filter

Multibit

Modulator

Left

Output

Right

Output

Switched

Capacitor

DAC and

Filter

Switched

Capacitor

DAC and

Filter

Internal

Voltage

Reference

http://www.cirrus.com

Copyright Cirrus Logic, Inc. 2013

(All Rights Reserved)

JUL ‘13

DS613F2

�

TABLE OF CONTENTS

CS4344/5/8

1. PIN DESCRIPTIONS .............................................................................................................................. 4

2. CHARACTERISTICS AND SPECIFICATIONS ...................................................................................... 5

SPECIFIED OPERATING CONDITIONS ............................................................................................... 5

ABSOLUTE MAXIMUM RATINGS ......................................................................................................... 5

DAC ANALOG CHARACTERISTICS ..................................................................................................... 6

DAC ANALOG CHARACTERISTICS - ALL MODES ............................................................................. 6

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE ........................................ 7

DIGITAL INPUT CHARACTERISTICS ................................................................................................... 8

POWER AND THERMAL CHARACTERISTICS ................................................................................... 8

SWITCHING CHARACTERISTICS - SERIAL AUDIO INTERFACE ...................................................... 9

3. TYPICAL CONNECTION DIAGRAM ................................................................................................... 11

4. APPLICATIONS ................................................................................................................................... 12

4.1 Master Clock ................................................................................................................................... 12

4.2 Serial Clock .................................................................................................................................... 12

4.2.1 External Serial Clock Mode ................................................................................................... 12

4.2.2 Internal Serial Clock Mode .................................................................................................... 12

4.3 De-Emphasis .................................................................................................................................. 15

4.4 Initialization and Power-Down ........................................................................................................ 15

4.5 Output Transient Control ................................................................................................................ 15

4.5.1 Power-Up .............................................................................................................................. 15

4.5.2 Power-Down .......................................................................................................................... 15

4.6 Grounding and Power Supply Decoupling ...................................................................................... 17

4.7 Analog Output and Filtering ............................................................................................................ 17

5. FILTER PLOTS ..................................................................................................................................... 18

6. PARAMETER DEFINITIONS ................................................................................................................ 21

7. PACKAGE DIMENSIONS .................................................................................................................... 22

8. ORDERING INFORMATION ................................................................................................................ 23

8.1 Functional Compatibility ................................................................................................................. 23

8.2 Selection Guide .............................................................................................................................. 23

9. REVISION HISTORY ............................................................................................................................ 24

2

�

CS4344/5/8

LIST OF FIGURES

Figure 1.Output Test Load . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Figure 2.Maximum Loading . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .8

Figure 3.External Serial Mode Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Figure 4.Internal Serial Mode Input Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Figure 5.Internal Serial Clock Generation . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .10

Figure 6.Typical Connection Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .11

Figure 7.CS4344 Data Format (I2S) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 8.CS4345 Data Format (Left Justified) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .13

Figure 9.CS4348 Data Format (Right Justified 16) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .14

Figure 10.De-Emphasis Curve (Fs = 44.1kHz) . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .15

Figure 11.CS4344/5/8 Initialization and Power-down Sequence . . . . . . . . . . . . . . . . . . . . . . .16

Figure 12.Single-Speed Stopband Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 13.Single-Speed Transition Band . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 14.Single-Speed Transition Band . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 15.Single-Speed Passband Ripple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .18

Figure 16.Double-Speed Stopband Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 17.Double-Speed Transition Band . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 18.Double-Speed Transition Band . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 19.Double-Speed Passband Ripple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .19

Figure 20.Quad-Speed Stopband Rejection . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Figure 21.Quad-Speed Transition Band . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Figure 22.Quad-Speed Transition Band . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

Figure 23.Quad-Speed Passband Ripple . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . .20

3

�

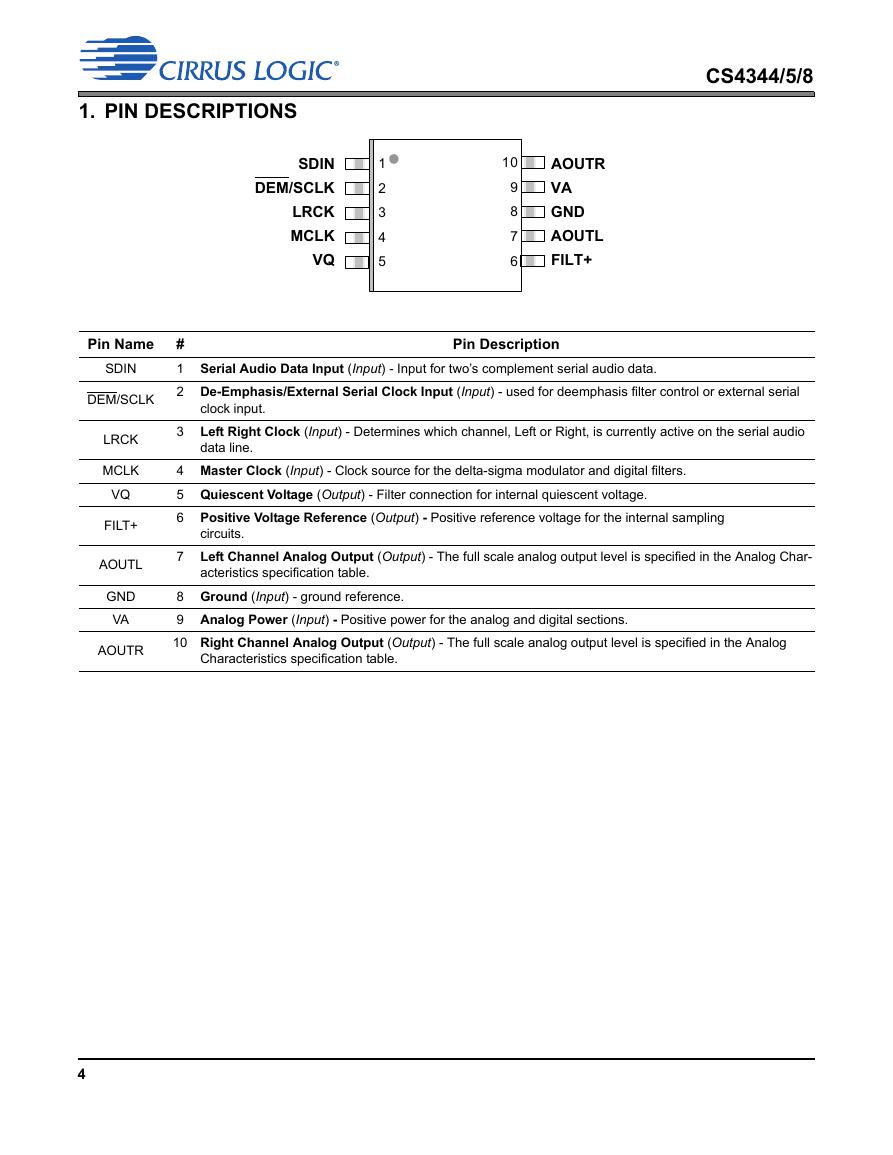

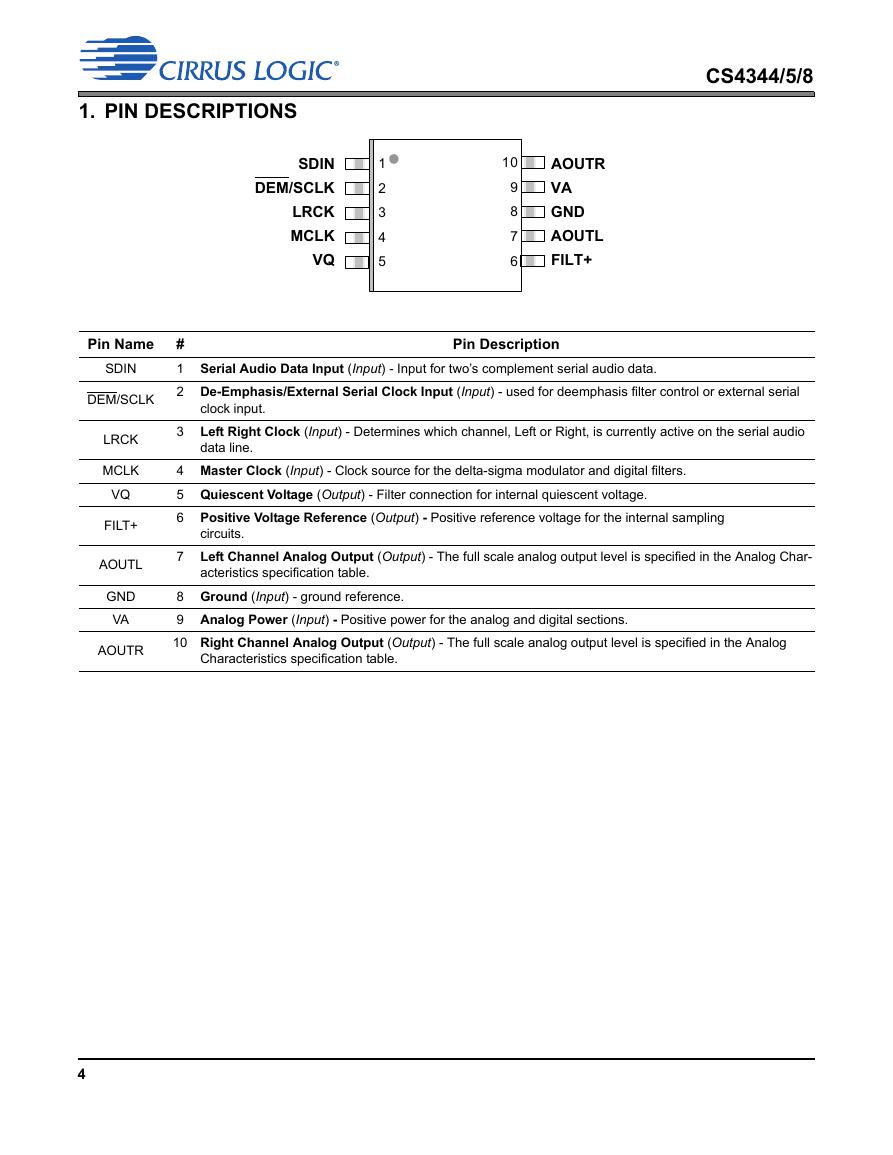

1. PIN DESCRIPTIONS

CS4344/5/8

SDIN

DEM/SCLK

LRCK

MCLK

VQ

1

2

3

4

5

10

9

8

7

6

AOUTR

VA

GND

AOUTL

FILT+

8 Ground (Input) - ground reference.

9 Analog Power (Input) - Positive power for the analog and digital sections.

10 Right Channel Analog Output (Output) - The full scale analog output level is specified in the Analog

Characteristics specification table.

#

1 Serial Audio Data Input (Input) - Input for two’s complement serial audio data.

2 De-Emphasis/External Serial Clock Input (Input) - used for deemphasis filter control or external serial

Pin Description

clock input.

Left Right Clock (Input) - Determines which channel, Left or Right, is currently active on the serial audio

data line.

4 Master Clock (Input) - Clock source for the delta-sigma modulator and digital filters.

5 Quiescent Voltage (Output) - Filter connection for internal quiescent voltage.

6 Positive Voltage Reference (Output) - Positive reference voltage for the internal sampling

circuits.

Left Channel Analog Output (Output) - The full scale analog output level is specified in the Analog Char-

acteristics specification table.

3

7

Pin Name

SDIN

DEM/SCLK

LRCK

MCLK

VQ

FILT+

AOUTL

GND

VA

AOUTR

4

�

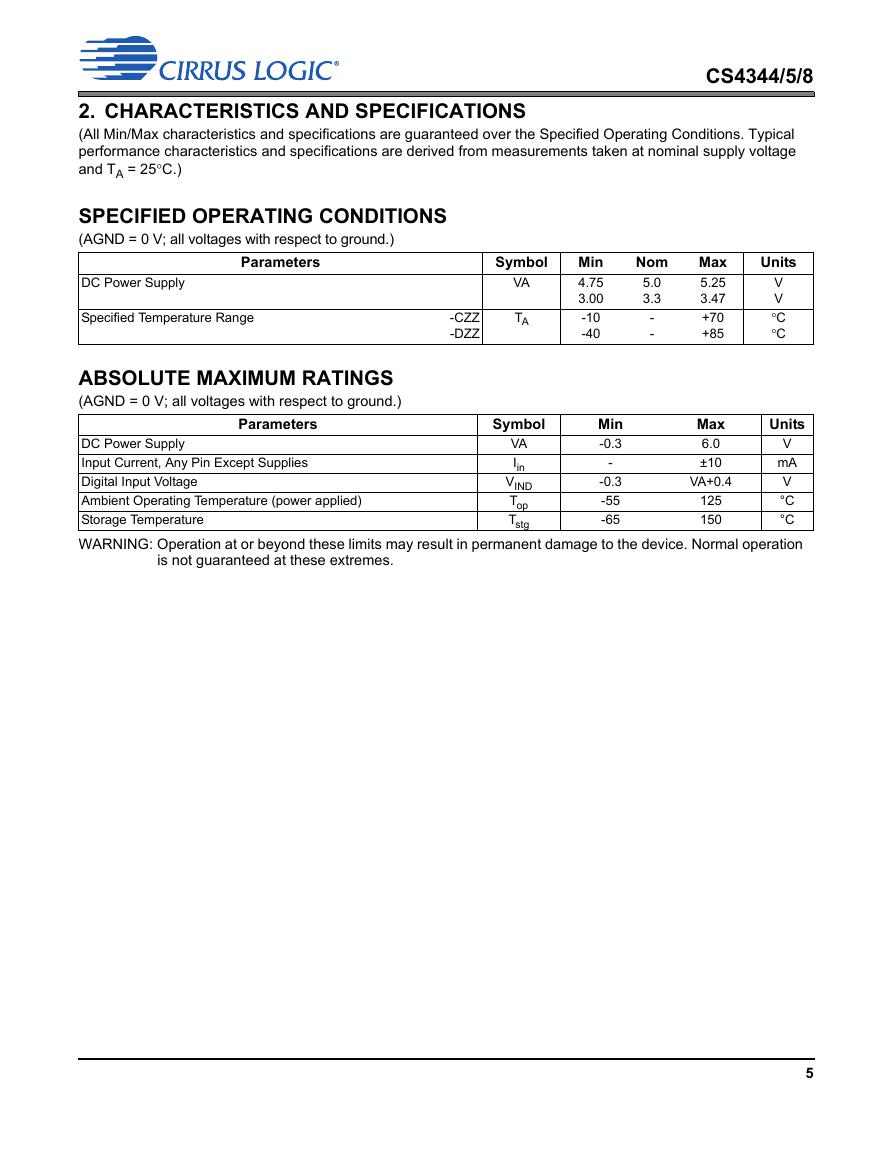

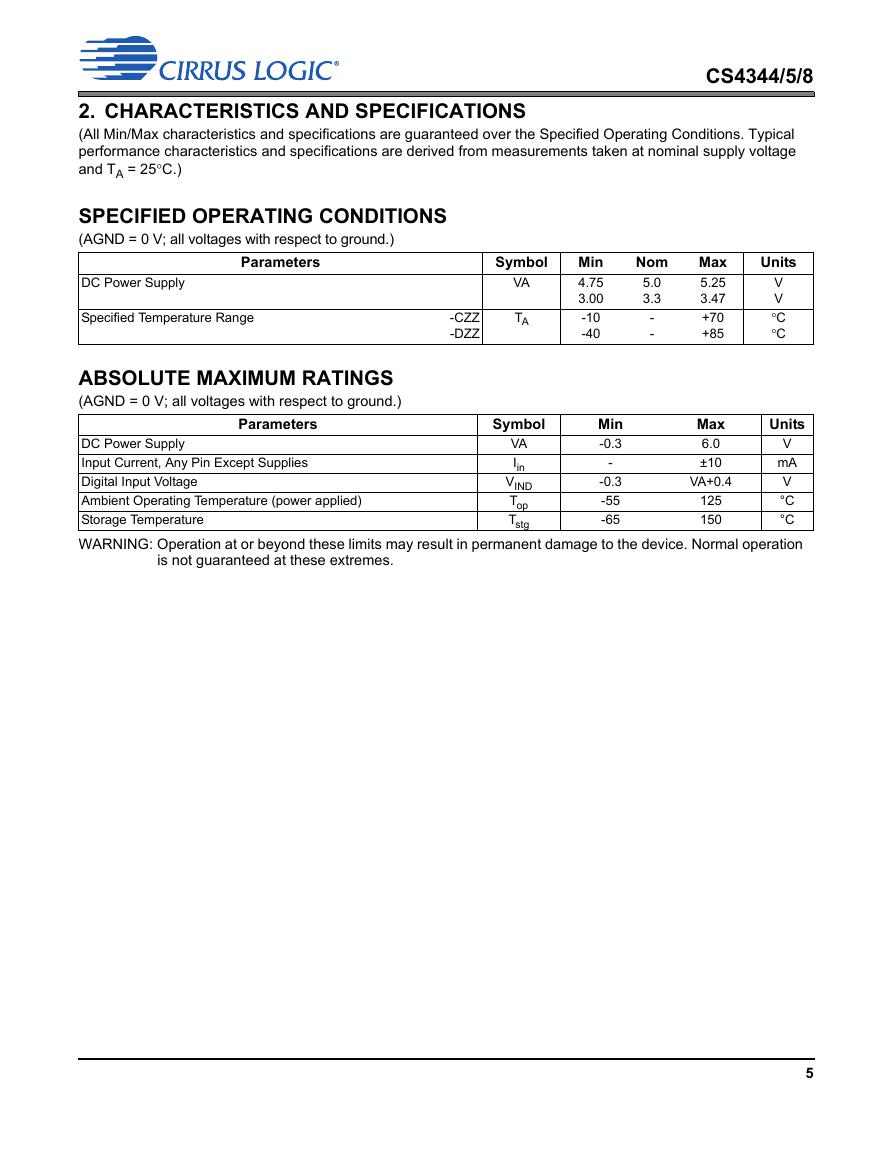

2. CHARACTERISTICS AND SPECIFICATIONS

(All Min/Max characteristics and specifications are guaranteed over the Specified Operating Conditions. Typical

performance characteristics and specifications are derived from measurements taken at nominal supply voltage

and TA = 25C.)

CS4344/5/8

SPECIFIED OPERATING CONDITIONS

(AGND = 0 V; all voltages with respect to ground.)

Parameters

DC Power Supply

Specified Temperature Range

Symbol

VA

TA

Min

4.75

3.00

-10

-40

Nom

5.0

3.3

-

-

Max

5.25

3.47

+70

+85

Units

V

V

C

C

-CZZ

-DZZ

ABSOLUTE MAXIMUM RATINGS

(AGND = 0 V; all voltages with respect to ground.)

Parameters

Symbol

DC Power Supply

Input Current, Any Pin Except Supplies

Digital Input Voltage

Ambient Operating Temperature (power applied)

Storage Temperature

WARNING: Operation at or beyond these limits may result in permanent damage to the device. Normal operation

VA

Iin

VIND

Top

Tstg

V

mA

V

°C

°C

125

150

is not guaranteed at these extremes.

Min

-0.3

-

-0.3

-55

-65

Units

Max

6.0

±10

VA+0.4

5

�

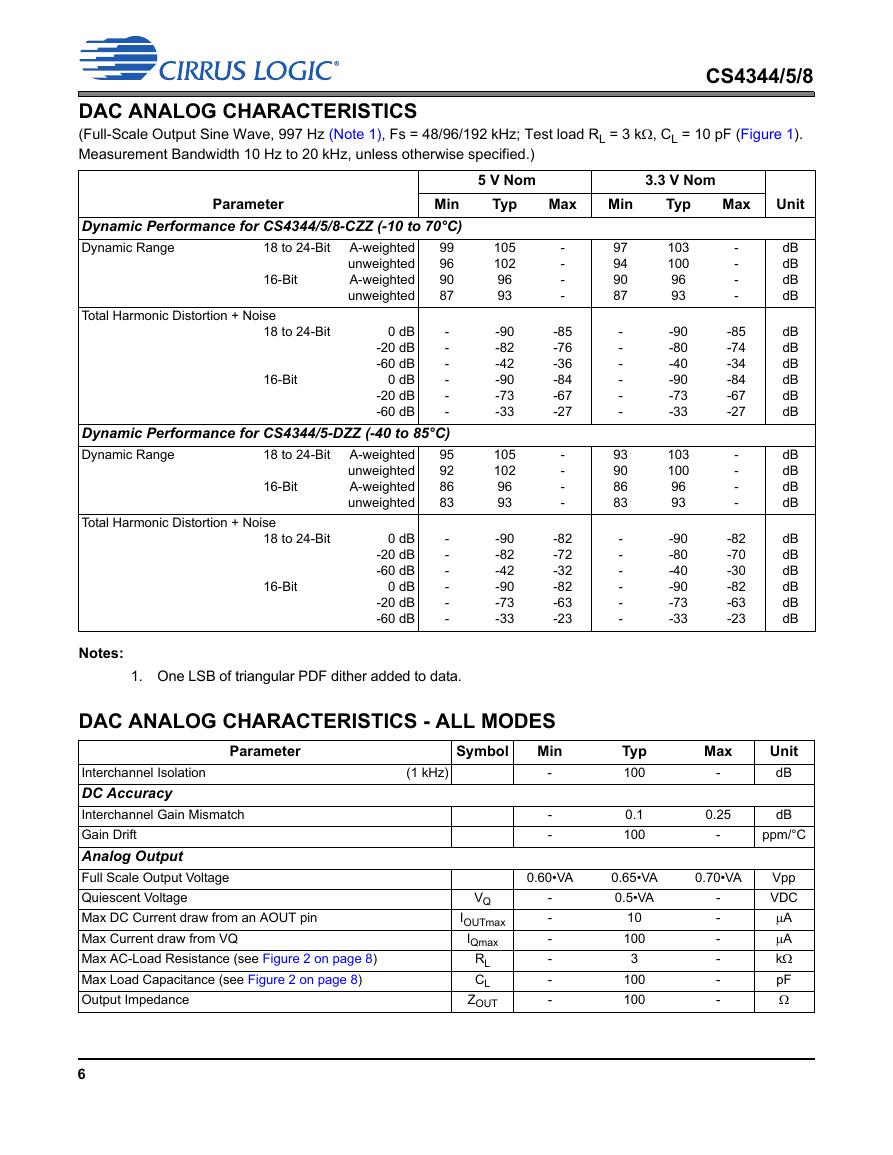

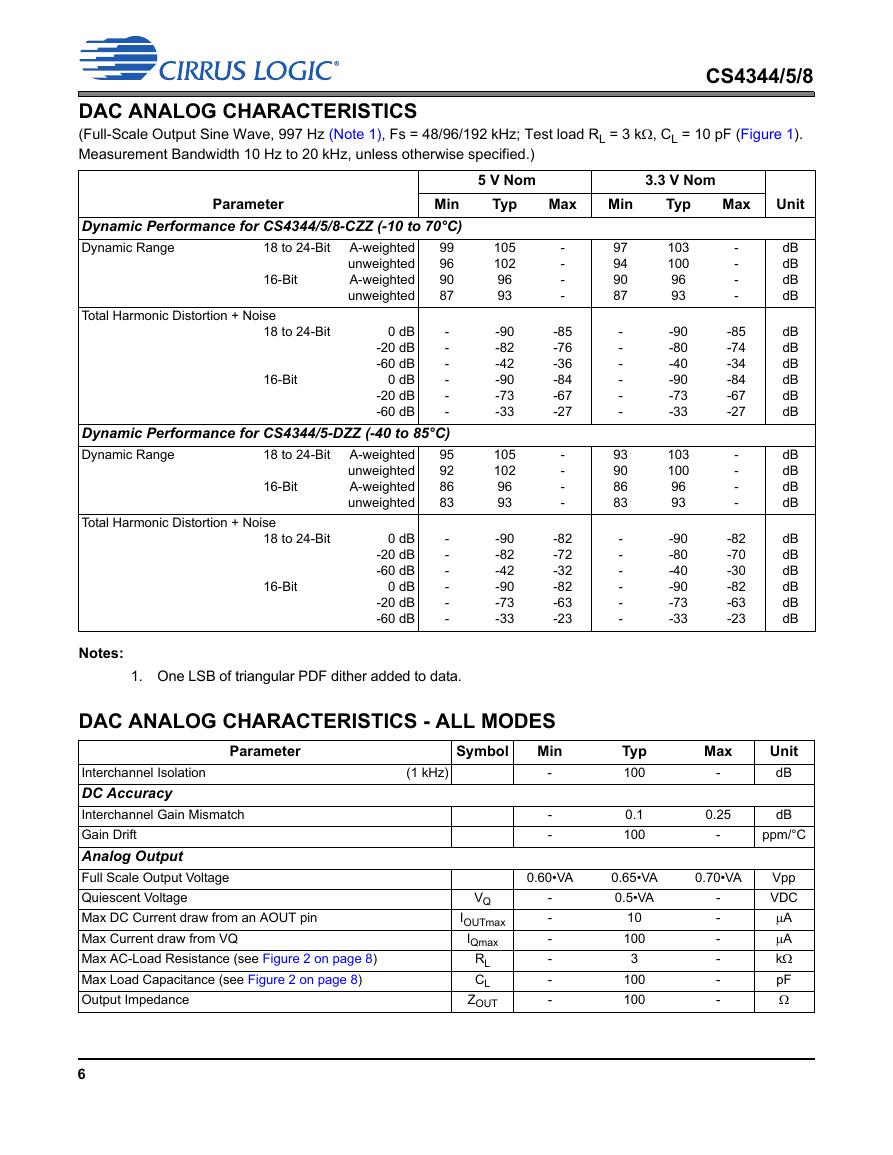

DAC ANALOG CHARACTERISTICS

(Full-Scale Output Sine Wave, 997 Hz (Note 1), Fs = 48/96/192 kHz; Test load RL = 3 k, CL = 10 pF (Figure 1).

Measurement Bandwidth 10 Hz to 20 kHz, unless otherwise specified.)

5 V Nom

3.3 V Nom

CS4344/5/8

Parameter

Min

Dynamic Performance for CS4344/5/8-CZZ (-10 to 70°C)

99

Dynamic Range

96

90

87

A-weighted

unweighted

A-weighted

unweighted

18 to 24-Bit

16-Bit

Total Harmonic Distortion + Noise

16-Bit

18 to 24-Bit

-

-

-

-

-

-

Dynamic Performance for CS4344/5-DZZ (-40 to 85°C)

Dynamic Range

95

92

86

83

A-weighted

unweighted

A-weighted

unweighted

0 dB

-20 dB

-60 dB

0 dB

-20 dB

-60 dB

18 to 24-Bit

16-Bit

Total Harmonic Distortion + Noise

18 to 24-Bit

16-Bit

0 dB

-20 dB

-60 dB

0 dB

-20 dB

-60 dB

-

-

-

-

-

-

Notes:

1. One LSB of triangular PDF dither added to data.

Typ

Max

Min

Typ

Max

Unit

105

102

96

93

-90

-82

-42

-90

-73

-33

105

102

96

93

-90

-82

-42

-90

-73

-33

-

-

-

-

-85

-76

-36

-84

-67

-27

-

-

-

-

-82

-72

-32

-82

-63

-23

97

94

90

87

-

-

-

-

-

-

93

90

86

83

-

-

-

-

-

-

103

100

96

93

-90

-80

-40

-90

-73

-33

103

100

96

93

-90

-80

-40

-90

-73

-33

-

-

-

-

-85

-74

-34

-84

-67

-27

-

-

-

-

-82

-70

-30

-82

-63

-23

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

dB

DAC ANALOG CHARACTERISTICS - ALL MODES

Min

-

Parameter

Symbol

(1 kHz)

Interchannel Isolation

DC Accuracy

Interchannel Gain Mismatch

Gain Drift

Analog Output

Full Scale Output Voltage

Quiescent Voltage

Max DC Current draw from an AOUT pin

Max Current draw from VQ

Max AC-Load Resistance (see Figure 2 on page 8)

Max Load Capacitance (see Figure 2 on page 8)

Output Impedance

6

Typ

100

0.1

100

0.65•VA

0.5•VA

10

100

3

100

100

Max

-

0.25

-

0.70•VA

-

-

-

-

-

-

Unit

dB

dB

ppm/°C

Vpp

VDC

A

A

k

pF

-

-

0.60•VA

-

-

-

-

-

-

VQ

IOUTmax

IQmax

RL

CL

ZOUT

�

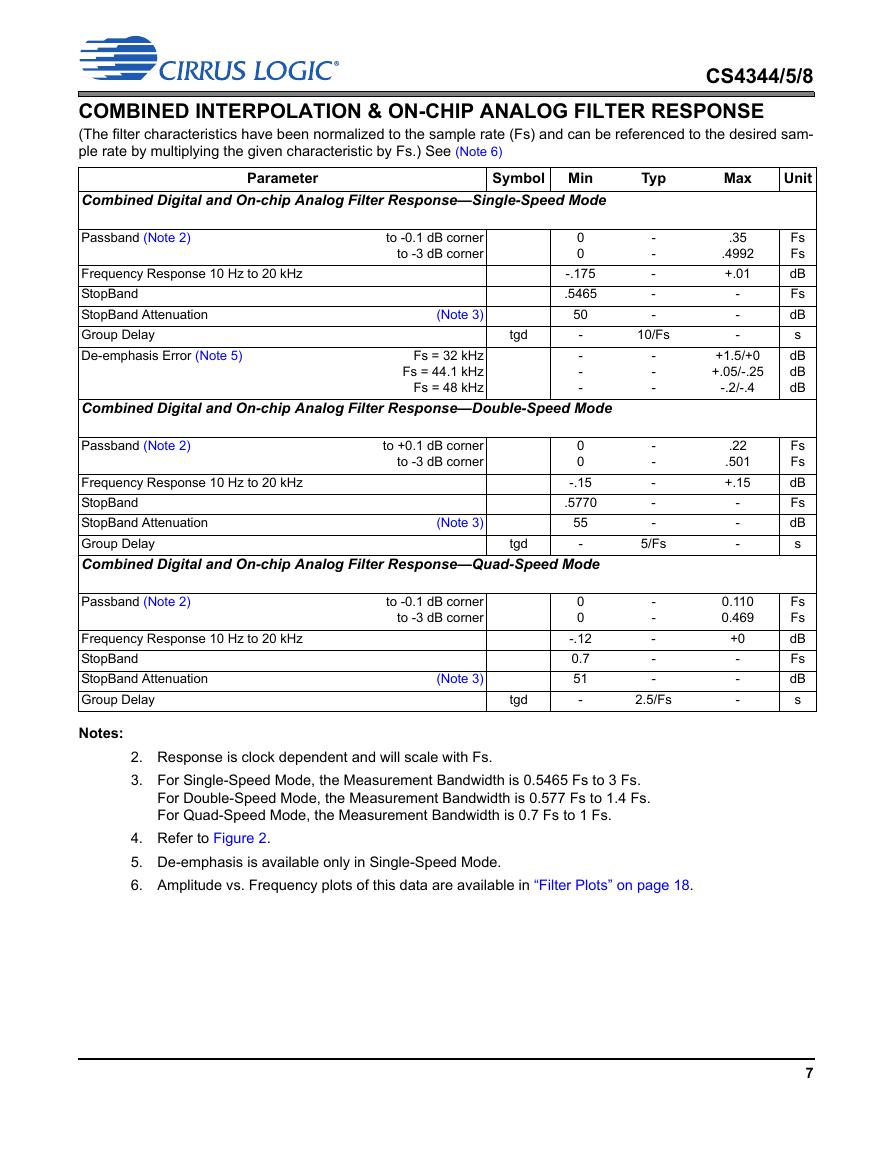

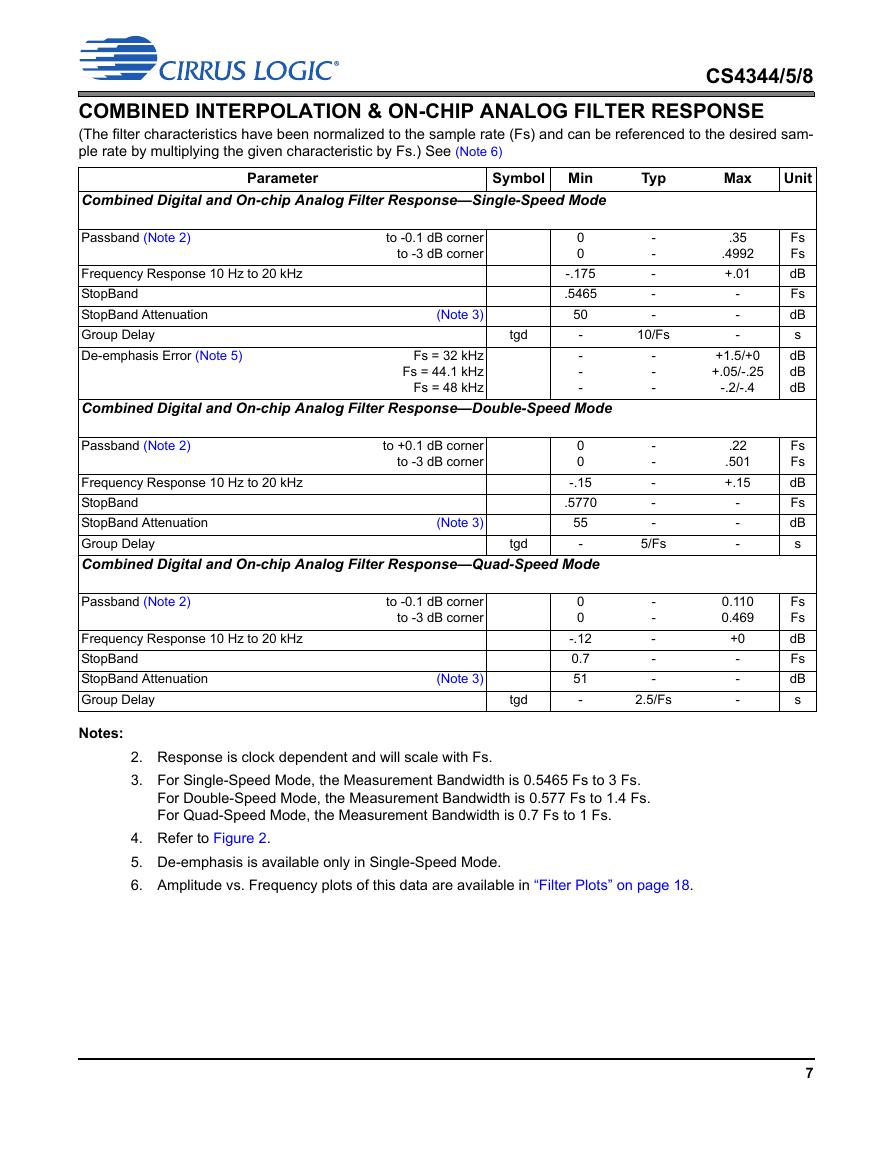

COMBINED INTERPOLATION & ON-CHIP ANALOG FILTER RESPONSE

(The filter characteristics have been normalized to the sample rate (Fs) and can be referenced to the desired sam-

ple rate by multiplying the given characteristic by Fs.) See (Note 6)

Parameter

Symbol Min

Typ

Max

Unit

Combined Digital and On-chip Analog Filter Response—Single-Speed Mode

CS4344/5/8

Passband (Note 2)

Frequency Response 10 Hz to 20 kHz

StopBand

StopBand Attenuation

Group Delay

De-emphasis Error (Note 5)

to -0.1 dB corner

to -3 dB corner

(Note 3)

tgd

Fs = 32 kHz

Fs = 44.1 kHz

Fs = 48 kHz

0

0

-.175

.5465

50

-

-

-

-

Combined Digital and On-chip Analog Filter Response—Double-Speed Mode

Passband (Note 2)

to +0.1 dB corner

to -3 dB corner

Frequency Response 10 Hz to 20 kHz

StopBand

StopBand Attenuation

Group Delay

Combined Digital and On-chip Analog Filter Response—Quad-Speed Mode

(Note 3)

tgd

Passband (Note 2)

Frequency Response 10 Hz to 20 kHz

StopBand

StopBand Attenuation

Group Delay

Notes:

to -0.1 dB corner

to -3 dB corner

(Note 3)

tgd

0

0

-.12

0.7

51

-

-

-

-

-

-

10/Fs

-

-

-

-

-

-

-

-

5/Fs

-

-

-

-

-

2.5/Fs

.35

.4992

+.01

-

-

-

+1.5/+0

+.05/-.25

-.2/-.4

.22

.501

+.15

-

-

-

0.110

0.469

+0

-

-

-

Fs

Fs

dB

Fs

dB

s

dB

dB

dB

Fs

Fs

dB

Fs

dB

s

Fs

Fs

dB

Fs

dB

s

0

0

-.15

.5770

55

-

2. Response is clock dependent and will scale with Fs.

3. For Single-Speed Mode, the Measurement Bandwidth is 0.5465 Fs to 3 Fs.

For Double-Speed Mode, the Measurement Bandwidth is 0.577 Fs to 1.4 Fs.

For Quad-Speed Mode, the Measurement Bandwidth is 0.7 Fs to 1 Fs.

4. Refer to Figure 2.

5. De-emphasis is available only in Single-Speed Mode.

6. Amplitude vs. Frequency plots of this data are available in “Filter Plots” on page 18.

7

�

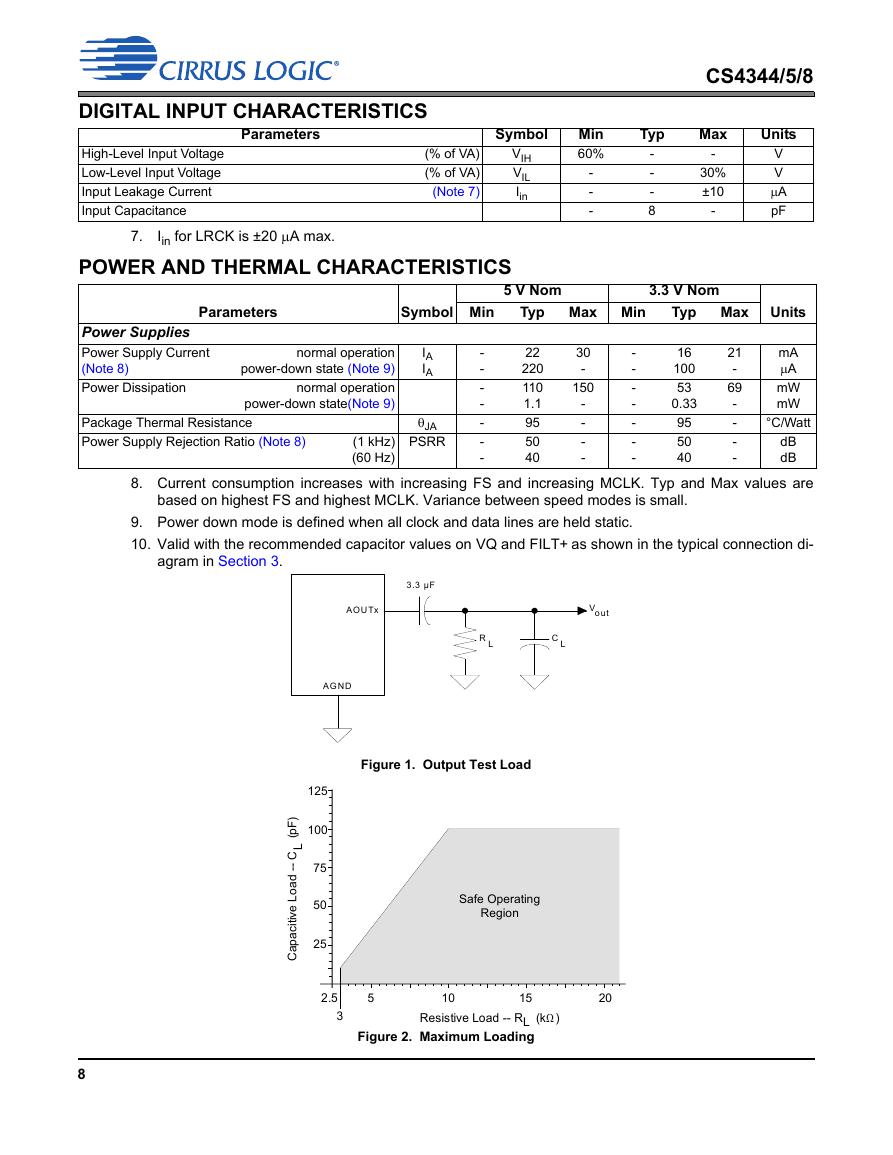

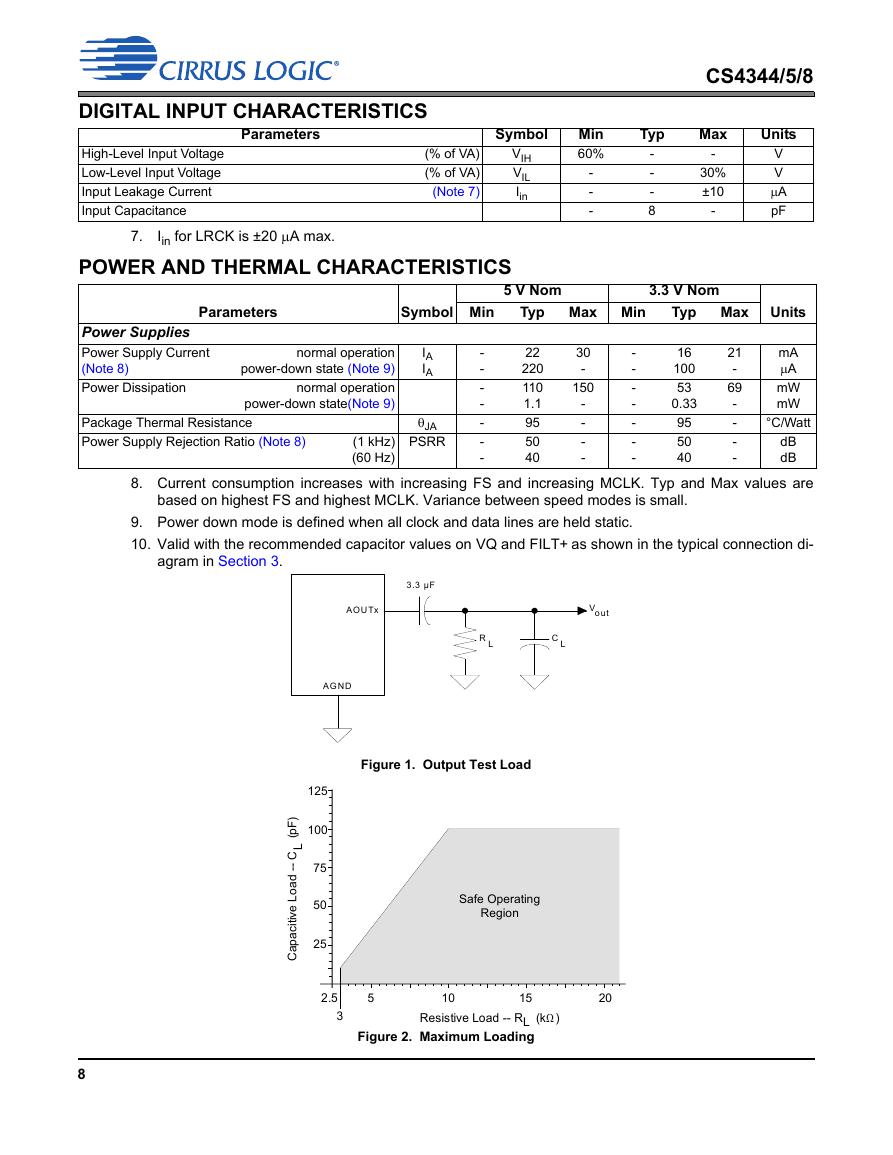

DIGITAL INPUT CHARACTERISTICS

Parameters

Symbol

High-Level Input Voltage

Low-Level Input Voltage

Input Leakage Current

Input Capacitance

7.

Iin for LRCK is ±20 A max.

(% of VA)

(% of VA)

(Note 7)

VIH

VIL

Iin

CS4344/5/8

Min

60%

-

-

-

Typ

-

-

-

8

Max

-

30%

±10

-

Units

V

V

A

pF

POWER AND THERMAL CHARACTERISTICS

5 V Nom

3.3 V Nom

Parameters

Symbol Min

Typ Max Min

Typ Max

Units

Power Supplies

Power Supply Current

(Note 8)

Power Dissipation

normal operation

power-down state (Note 9)

normal operation

power-down state(Note 9)

IA

IA

Package Thermal Resistance

Power Supply Rejection Ratio (Note 8)

JA

PSRR

(1 kHz)

(60 Hz)

-

-

-

-

-

-

-

22

220

110

1.1

95

50

40

30

-

150

-

-

-

-

-

-

-

-

-

-

-

16

100

53

0.33

95

50

40

21

-

69

-

-

-

-

mA

A

mW

mW

°C/Watt

dB

dB

8. Current consumption increases with increasing FS and increasing MCLK. Typ and Max values are

based on highest FS and highest MCLK. Variance between speed modes is small.

9. Power down mode is defined when all clock and data lines are held static.

10. Valid with the recommended capacitor values on VQ and FILT+ as shown in the typical connection di-

agram in Section 3.

3.3 µF

AOUTx

Vout

R L

C L

AGND

125

100

75

50

25

2.5

3

Figure 1. Output Test Load

Safe Operating

Region

5

10

15

L

Figure 2. Maximum Loading

Resistive Load -- R (k )

20

)

F

p

(

C

L

-

-

d

a

o

L

e

v

i

t

i

c

a

p

a

C

8

�

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf