General Description

Features

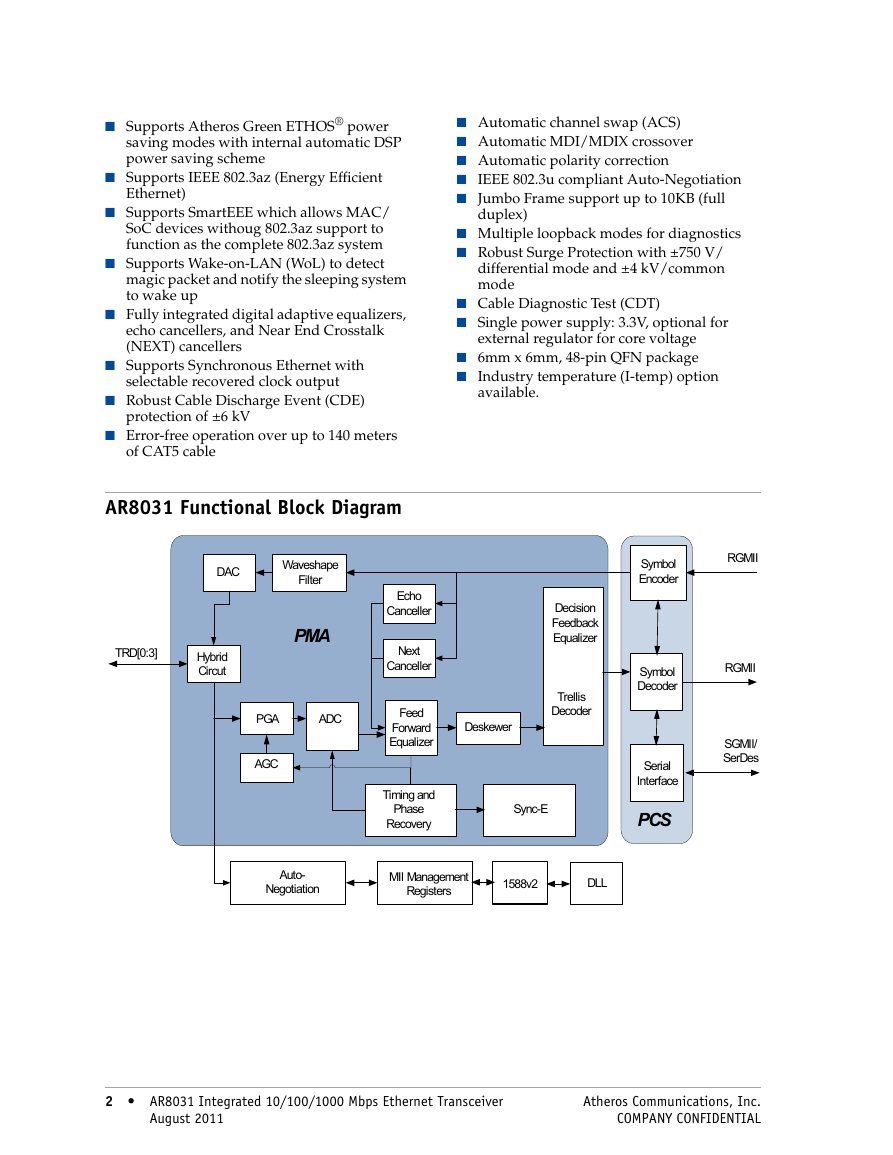

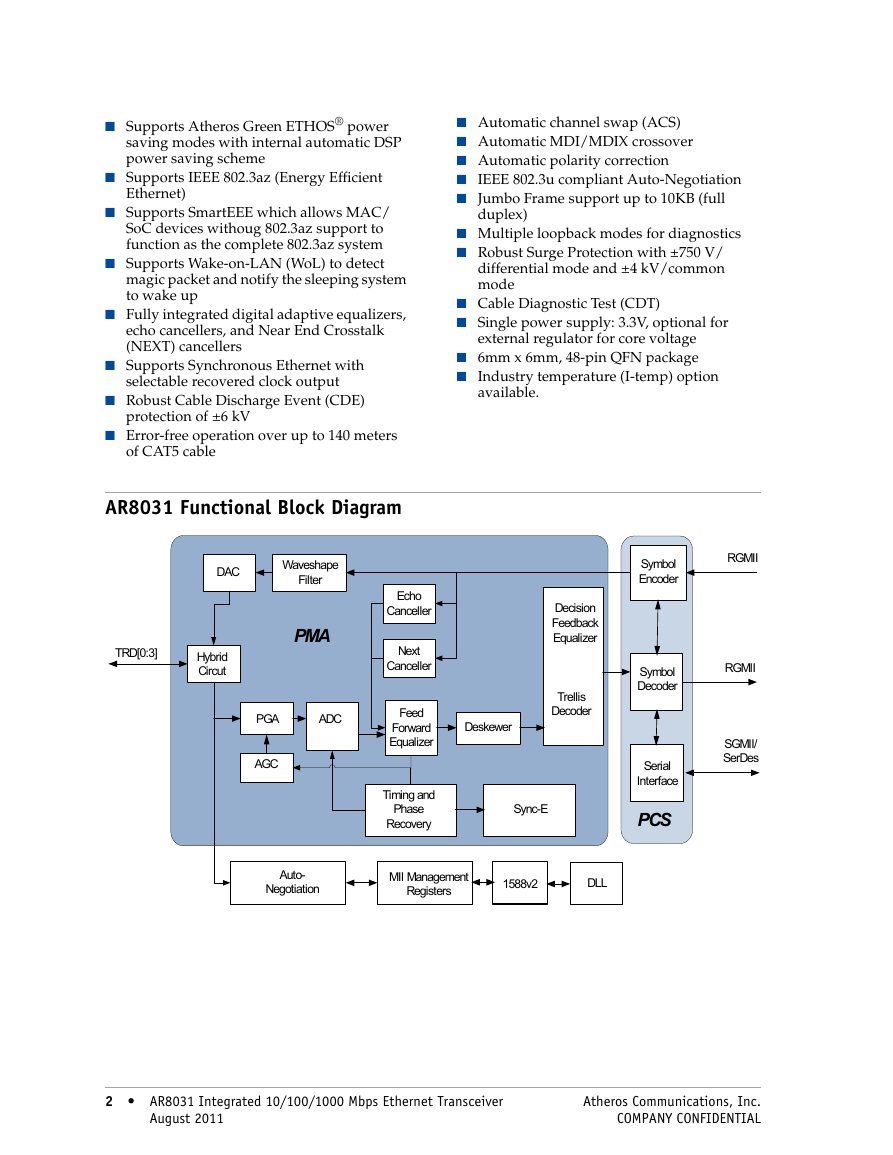

AR8031 Functional Block Diagram

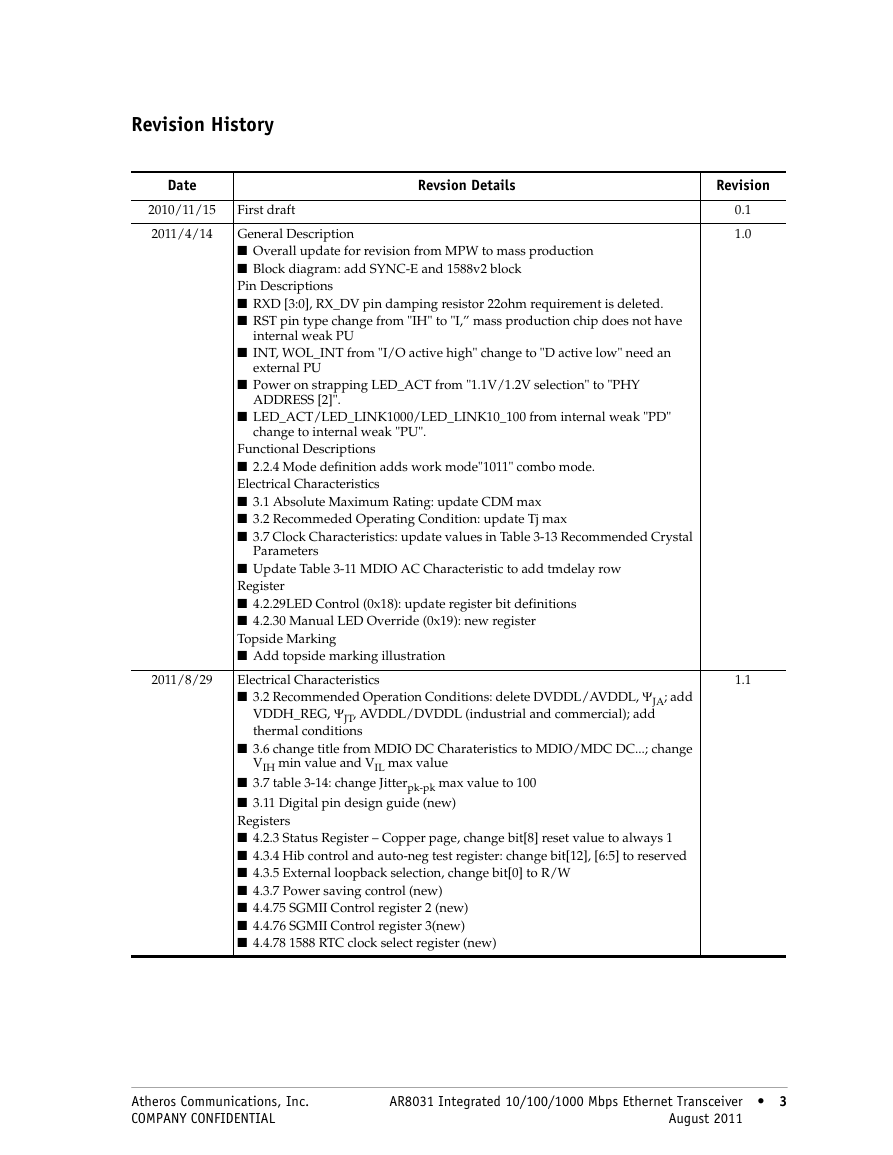

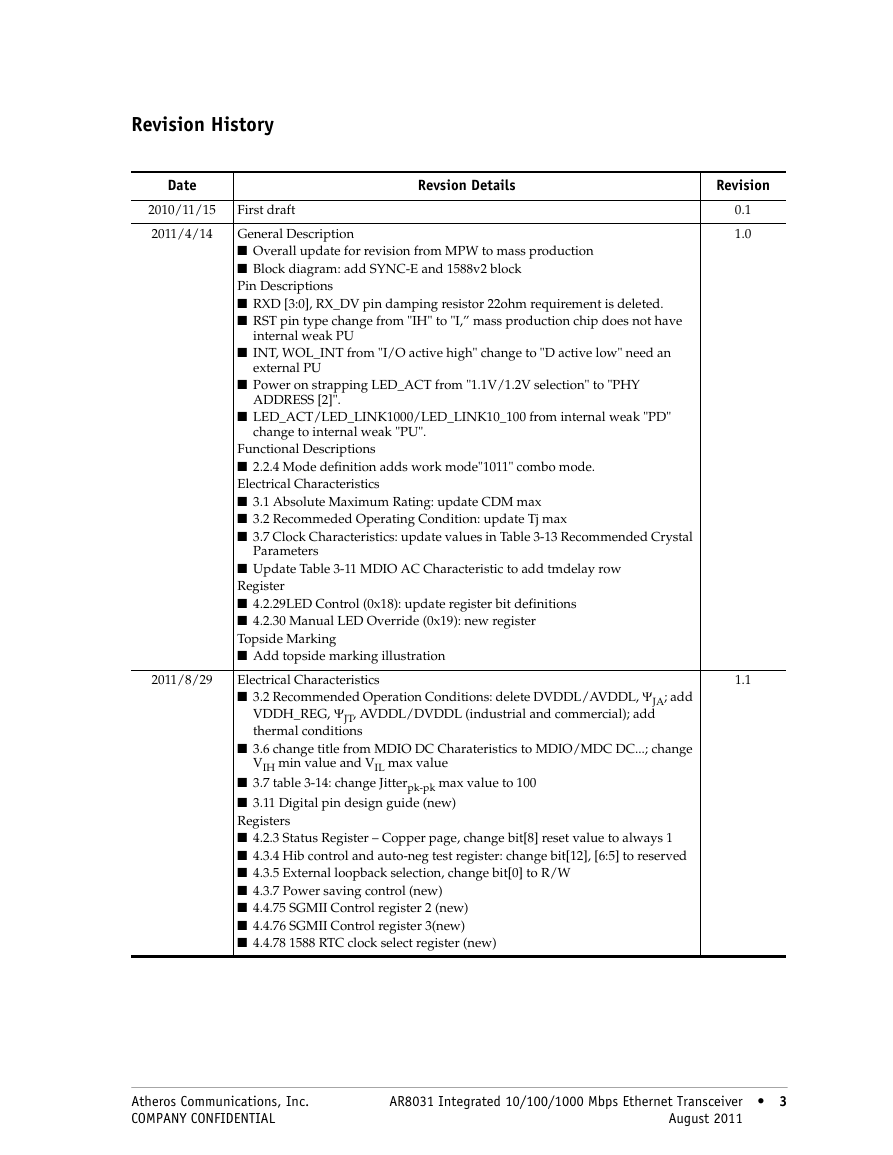

Revision History

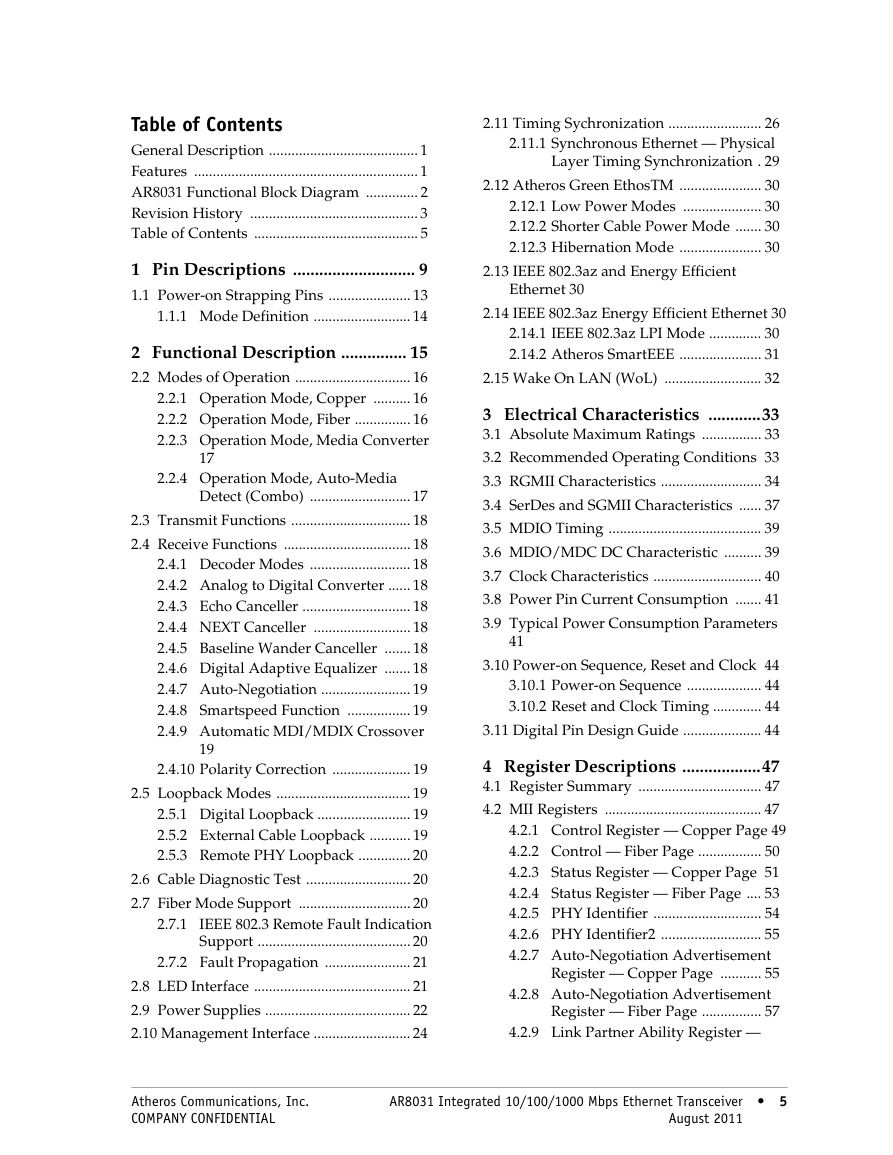

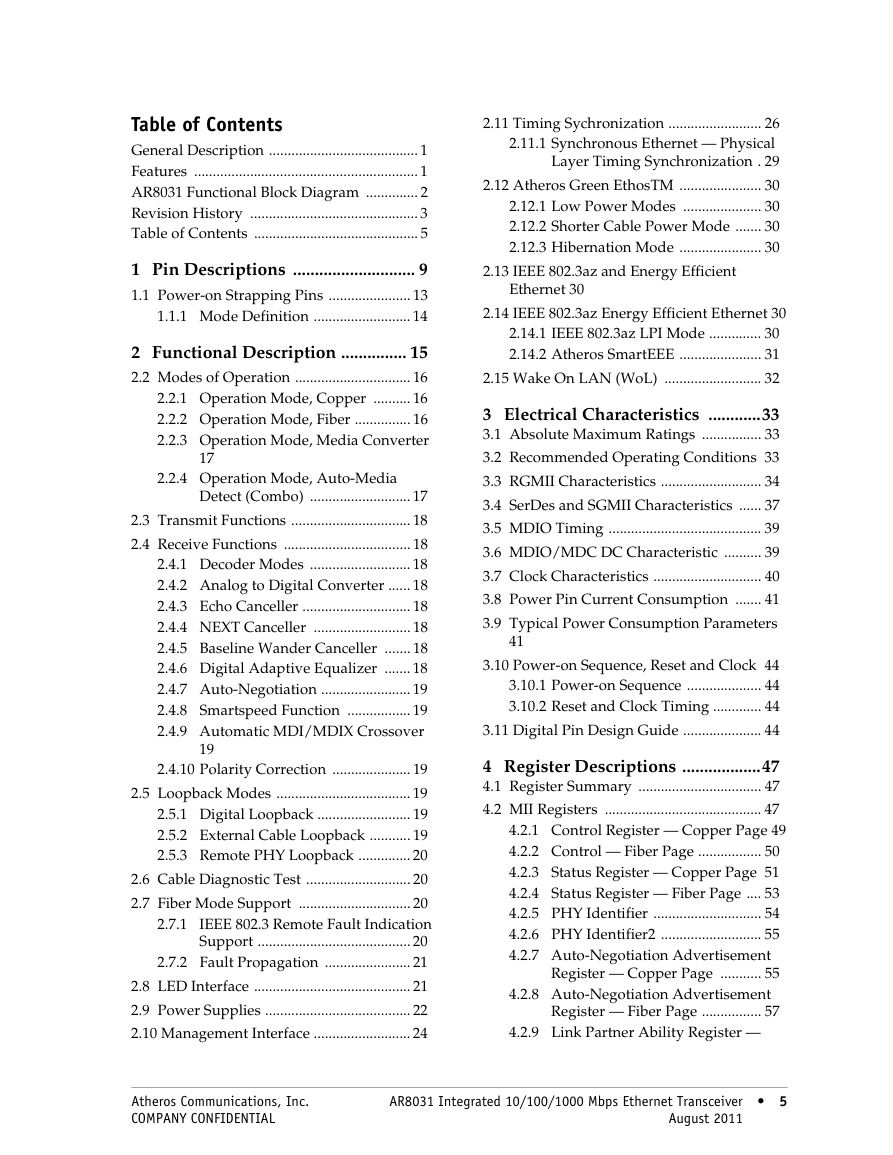

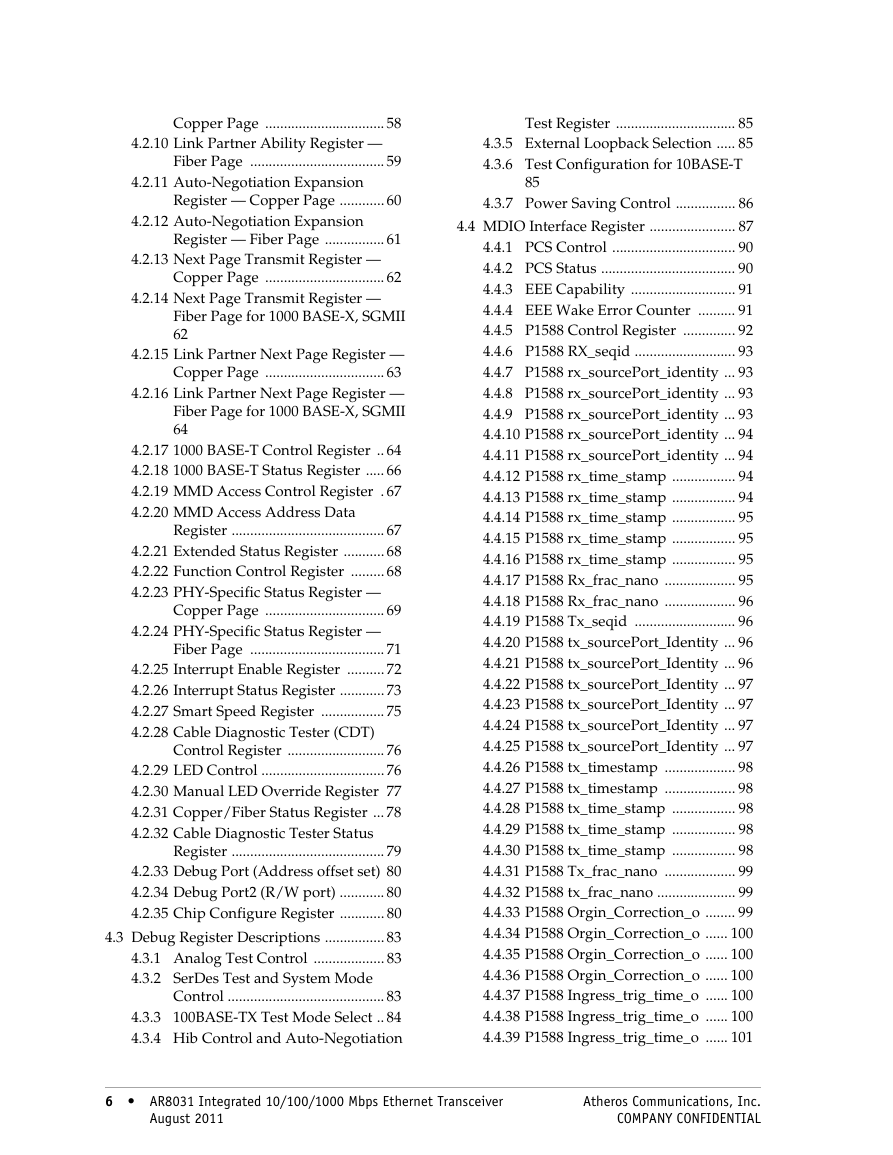

Table of Contents

1. Pin Descriptions

1.1 Power-on Strapping Pins

1.1.1 Mode Definition

2. Functional Description

2.2 Modes of Operation

2.2.1 Operation Mode, Copper

2.2.2 Operation Mode, Fiber

2.2.3 Operation Mode, Media Converter

2.2.4 Operation Mode, Auto-Media Detect (Combo)

2.3 Transmit Functions

2.4 Receive Functions

2.4.1 Decoder Modes

2.4.2 Analog to Digital Converter

2.4.3 Echo Canceller

2.4.4 NEXT Canceller

2.4.5 Baseline Wander Canceller

2.4.6 Digital Adaptive Equalizer

2.4.7 Auto-Negotiation

2.4.8 Smartspeed Function

2.4.9 Automatic MDI/MDIX Crossover

2.4.10 Polarity Correction

2.5 Loopback Modes

2.5.1 Digital Loopback

2.5.2 External Cable Loopback

2.5.3 Remote PHY Loopback

2.6 Cable Diagnostic Test

2.7 Fiber Mode Support

2.7.1 IEEE 802.3 Remote Fault Indication Support

2.7.2 Fault Propagation

2.8 LED Interface

2.9 Power Supplies

2.10 Management Interface

2.11 Timing Sychronization

2.11.1 Synchronous Ethernet - Physical Layer Timing Synchronization

2.12 Atheros Green EthosTM

2.12.1 Low Power Modes

2.12.2 Shorter Cable Power Mode

2.12.3 Hibernation Mode

2.13 IEEE 802.3az and Energy Efficient Ethernet

2.14 IEEE 802.3az Energy Efficient Ethernet

2.14.1 IEEE 802.3az LPI Mode

2.14.2 Atheros SmartEEE

2.15 Wake On LAN (WoL)

3. Electrical Characteristics

3.1 Absolute Maximum Ratings

3.2 Recommended Operating Conditions

3.3 RGMII Characteristics

3.4 SerDes and SGMII Characteristics

3.5 MDIO Timing

3.6 MDIO/MDC DC Characteristic

3.7 Clock Characteristics

3.8 Power Pin Current Consumption

3.9 Typical Power Consumption Parameters

3.10 Power-on Sequence, Reset and Clock

3.10.1 Power-on Sequence

3.10.2 Reset and Clock Timing

3.11 Digital Pin Design Guide

4. Register Descriptions

4.1 Register Summary

4.2 MII Registers

4.2.1 Control Register - Copper Page

4.2.2 Control - Fiber Page

4.2.3 Status Register - Copper Page

4.2.4 Status Register - Fiber Page

4.2.5 PHY Identifier

4.2.6 PHY Identifier2

4.2.7 Auto-Negotiation Advertisement Register - Copper Page

4.2.8 Auto-Negotiation Advertisement Register - Fiber Page

4.2.9 Link Partner Ability Register - Copper Page

4.2.10 Link Partner Ability Register - Fiber Page

4.2.11 Auto-Negotiation Expansion Register - Copper Page

4.2.12 Auto-Negotiation Expansion Register - Fiber Page

4.2.13 Next Page Transmit Register - Copper Page

4.2.14 Next Page Transmit Register - Fiber Page for 1000 BASE-X, SGMII

4.2.15 Link Partner Next Page Register - Copper Page

4.2.16 Link Partner Next Page Register - Fiber Page for 1000 BASE-X, SGMII

4.2.17 1000 BASE-T Control Register

4.2.18 1000 BASE-T Status Register

4.2.19 MMD Access Control Register

4.2.20 MMD Access Address Data Register

4.2.21 Extended Status Register

4.2.22 Function Control Register

4.2.23 PHY-Specific Status Register - Copper Page

4.2.24 PHY-Specific Status Register - Fiber Page

4.2.25 Interrupt Enable Register

4.2.26 Interrupt Status Register

4.2.27 Smart Speed Register

4.2.28 Cable Diagnostic Tester (CDT) Control Register

4.2.29 LED Control

4.2.30 Manual LED Override Register

4.2.31 Copper/Fiber Status Register

4.2.32 Cable Diagnostic Tester Status Register

4.2.33 Debug Port (Address offset set)

4.2.34 Debug Port2 (R/W port)

4.2.35 Chip Configure Register

4.3 Debug Register Descriptions

4.3.1 Analog Test Control

4.3.2 SerDes Test and System Mode Control

4.3.3 100BASE-TX Test Mode Select

4.3.4 Hib Control and Auto-Negotiation Test Register

4.3.5 External Loopback Selection

4.3.6 Test Configuration for 10BASE-T

4.3.7 Power Saving Control

4.4 MDIO Interface Register

4.4.1 PCS Control

4.4.2 PCS Status

4.4.3 EEE Capability

4.4.4 EEE Wake Error Counter

4.4.5 P1588 Control Register

4.4.6 P1588 RX_seqid

4.4.7 P1588 rx_sourcePort_identity

4.4.8 P1588 rx_sourcePort_identity

4.4.9 P1588 rx_sourcePort_identity

4.4.10 P1588 rx_sourcePort_identity

4.4.11 P1588 rx_sourcePort_identity

4.4.12 P1588 rx_time_stamp

4.4.13 P1588 rx_time_stamp

4.4.14 P1588 rx_time_stamp

4.4.15 P1588 rx_time_stamp

4.4.16 P1588 rx_time_stamp

4.4.17 P1588 Rx_frac_nano

4.4.18 P1588 Rx_frac_nano

4.4.19 P1588 Tx_seqid

4.4.20 P1588 tx_sourcePort_Identity

4.4.21 P1588 tx_sourcePort_Identity

4.4.22 P1588 tx_sourcePort_Identity

4.4.23 P1588 tx_sourcePort_Identity

4.4.24 P1588 tx_sourcePort_Identity

4.4.25 P1588 tx_sourcePort_Identity

4.4.26 P1588 tx_timestamp

4.4.27 P1588 tx_timestamp

4.4.28 P1588 tx_time_stamp

4.4.29 P1588 tx_time_stamp

4.4.30 P1588 tx_time_stamp

4.4.31 P1588 Tx_frac_nano

4.4.32 P1588 tx_frac_nano

4.4.33 P1588 Orgin_Correction_o

4.4.34 P1588 Orgin_Correction_o

4.4.35 P1588 Orgin_Correction_o

4.4.36 P1588 Orgin_Correction_o

4.4.37 P1588 Ingress_trig_time_o

4.4.38 P1588 Ingress_trig_time_o

4.4.39 P1588 Ingress_trig_time_o

4.4.40 P1588 Ingress_trig_time_o

4.4.41 P1588 Tx_latency_o

4.4.42 P1588 Inc_value_o

4.4.43 P1588 Inc_value_o

4.4.44 P1588 Nano_offset_o

4.4.45 P1588 Nano_offset_o

4.4.46 P1588 Sec_offset_o

4.4.47 P1588 Sec_offset_o

4.4.48 P1588 Sec_offset_o

4.4.49 P1588 Real_time_i

4.4.50 P1588 Real_time_i

4.4.51 P1588 Real_time_i

4.4.52 P1588 Real_time_i

4.4.53 P1588 Real_time_i

4.4.54 P1588 Rtc_frac_nano_i

4.4.55 P1588 Rtc_frac_nano_i

4.4.56 Wake-on-LAN Internal Address 1

4.4.57 Wake-on-LAN Internal Address 2

4.4.58 Wake-on-LAN Internal Address 3

4.4.59 Rem_phy_lpbk

4.4.60 SmartEEE Control 1

4.4.61 SmartEEE Control 2

4.4.62 SmartEEE control 3

4.4.63 Auto-Negotiation Control 1

4.4.64 Auto-Negotiation Status

4.4.65 Auto-Negotiation XNP Transmit

4.4.66 Auto-Negotiation XNP transmit1

4.4.67 Auto-Negotiation XNP Transmit2

4.4.68 Auto-Negotiation LP XNP Ability

4.4.69 Auto-Negotiation LP XNP Ability1

4.4.70 Auto-Negotiation LP XNP ability2

4.4.71 EEE Advertisement

4.4.72 EEE LP advertisement

4.4.73 EEE Ability Auto-negotiation Result

4.4.74 SGMII Control Register 1

4.4.75 SGMII Control Register 2

4.4.76 SGMII Control Register 3

4.4.77 CLK_25M Clock Select

4.4.78 1588 Clock Select

5. Package Dimensions

6. Ordering Information

7. Topside Marking

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc