PCIe技术介绍

�

PCIe总线的基础知识

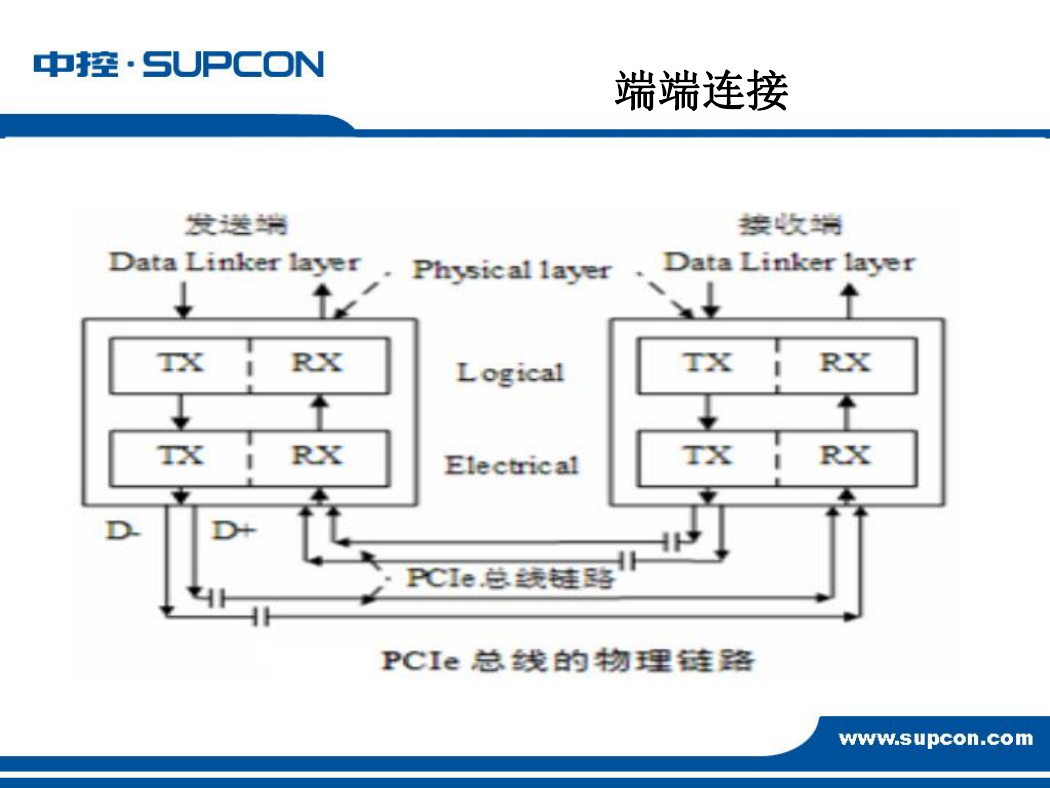

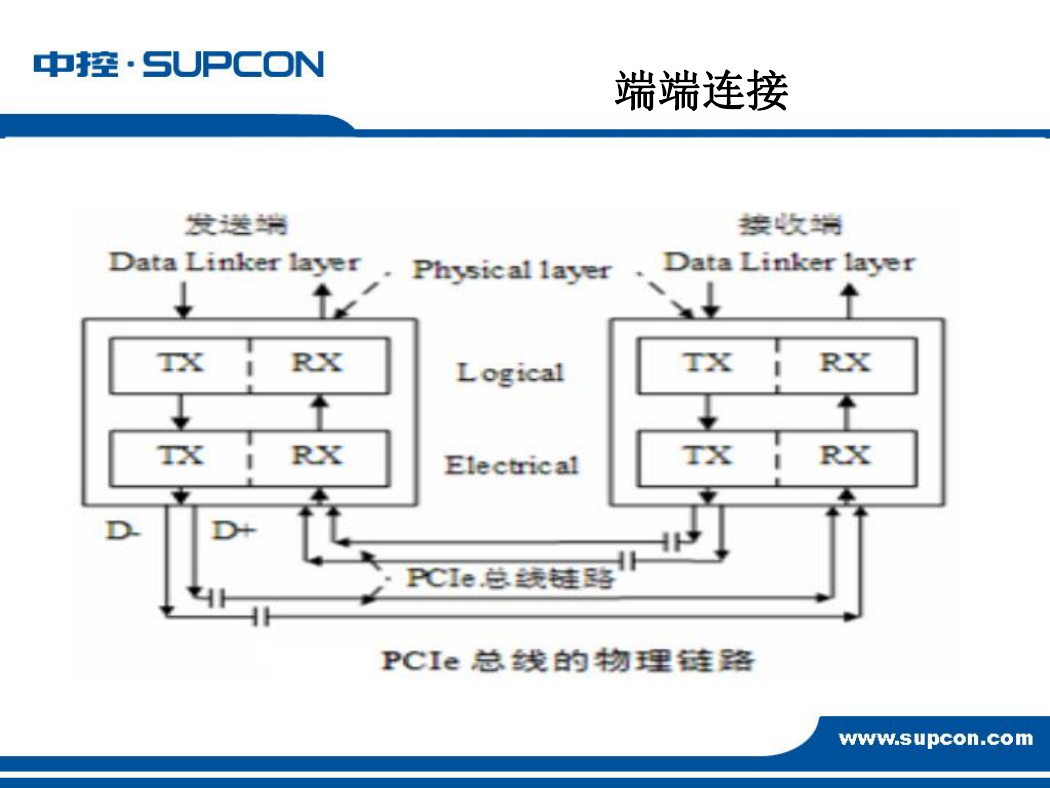

Ø 端到端的数据传递

Ø PCIe链路使用“端到端的数据传送方式”,发送端和

接收端中都含有TX(发送逻辑)和RX(接收逻辑) 。

Ø 在PCIe总线的物理链路的一个数据通路(Lane)中,由

两组差分信号,共4根信号线组成。其中发送端的TX部

件与接收端的RX部件使用一组差分信号连接,该链路

也被称为发送端的发送链路,也是接收端的接收链路;

而发送端的RX部件与接收端的TX部件使用另一组差分

信号连接,该链路也被称为发送端的接收链路,也是

接收端的发送链路。一个PCIe链路可以由多个Lane组

成。

�

端端连接

�

PCB布线及优缺点

Ø 高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦

合。该电容也被称为AC耦合电容。PCIe链路使用差分信号进行数

据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过

比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑

“0”。

Ø 与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在

布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此

外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号

上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。

因此差分信号可以使用更高的总线频率。

Ø 此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic

Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、

极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵

消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点

也是显而易见的,一是差分信号使用两根信号传送一位数据;二

是差分信号的布线相对严格一些。

�

总线频率及编解码

Ø PCIe总线规范与总线频率和编码的关系

Ø 使用的总线频率并不相同,其使用的数据编码方式也

不相同。PCIe总线V1.x和V2.0规范在物理层中使用

8/10b编码,即在PCIe链路上的10 bit中含有8 bit的有

效数据;而V3.0规范使用128/130b编码方式,即在

PCIe链路上的130 bit中含有128 bit的有效数据。

�

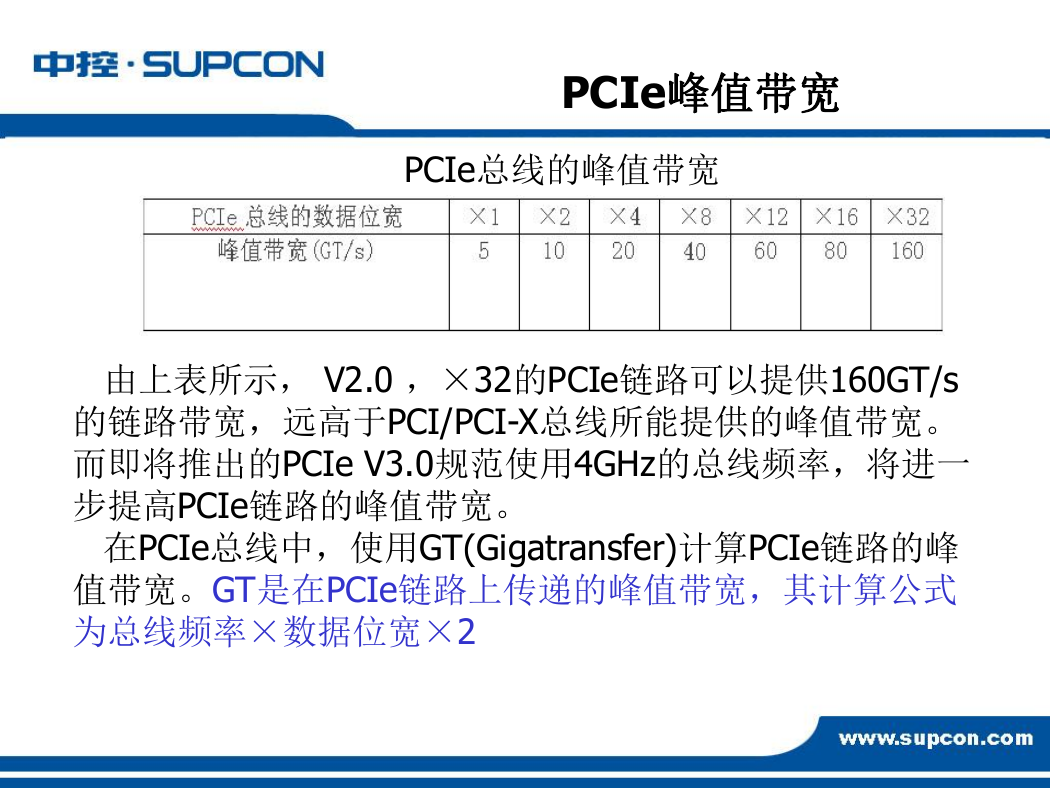

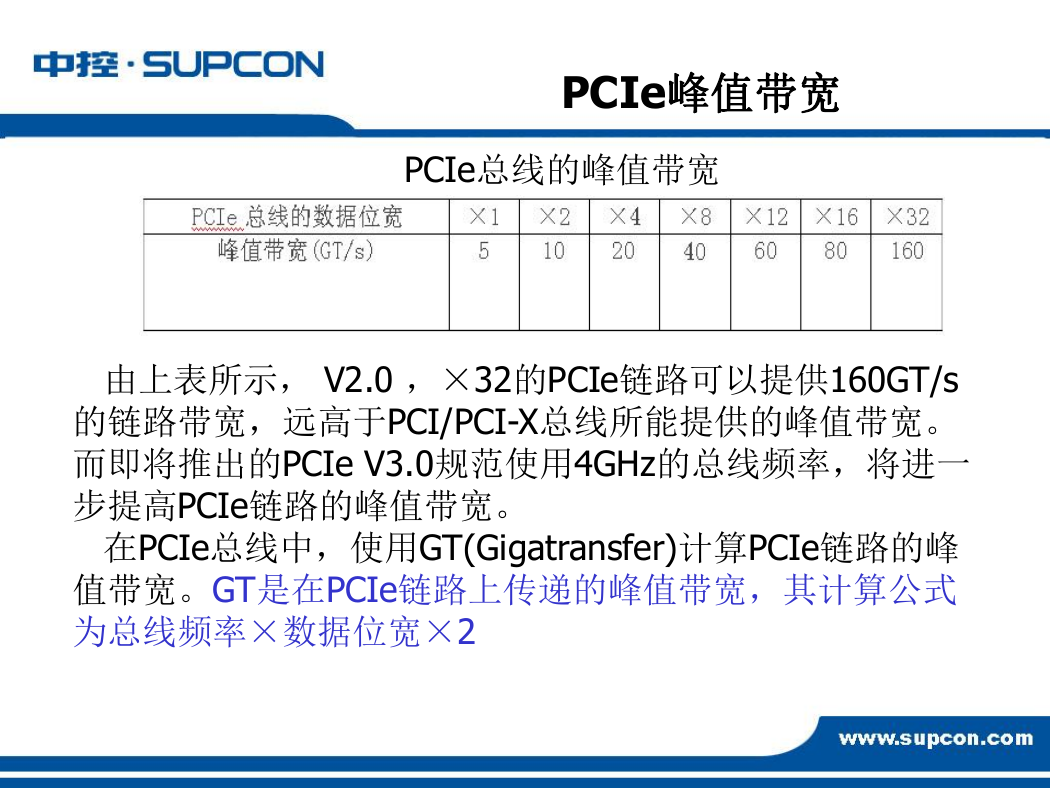

PCIe峰值带宽

PCIe总线的峰值带宽

由上表所示, V2.0 ,×32的PCIe链路可以提供160GT/s

的链路带宽,远高于PCI/PCI-X总线所能提供的峰值带宽。

而即将推出的PCIe V3.0规范使用4GHz的总线频率,将进一

步提高PCIe链路的峰值带宽。

在PCIe总线中,使用GT(Gigatransfer)计算PCIe链路的峰

值带宽。GT是在PCIe链路上传递的峰值带宽,其计算公式

为总线频率×数据位宽×2

�

PCIe总线使用的信号

Ø PCIe总线物理链路间的数据传送使用基于时钟的同步传送

机制,但是在物理链路上并没有时钟线,PCIe总线的接收

端含有时钟恢复模块CDR(Clock Data Recovery),CDR将

从接收报文中提取接收时钟,从而进行同步数据传递。

Ø 值得注意的是,在一个PCIe设备中除了需要从报文中提取

时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参

考时钟。

�

电源线和数据线

Ø PCIe设备使用两种电源信号供电,分别是Vcc与Vaux,其额定电压为

3.3V。其中Vcc为主电源,PCIe设备使用的主要逻辑模块均使用Vcc供

电,而一些与电源管理相关的逻辑使用Vaux供电。在PCIe设备中,一

些特殊的寄存器通常使用Vaux供电,如Sticky Register,此时即使PCIe

设备的Vcc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器

的内容也不会发生改变。

Ø 在PCIe总线中,使用Vaux的主要原因是为了降低功耗和缩短系统恢复

时间。因为Vaux在多数情况下并不会被移除,因此当PCIe设备的Vcc恢

复后,该设备不用重新恢复使用Vaux供电的逻辑,从而设备可以很快

地恢复到正常工作状状态。

Ø PCIe链路的最大宽度为×32,但是在实际应用中,×32的链路宽度极

少使用。在一个处理器系统中,一般提供×16的PCIe插槽,并使用

PETp0~15、PETn0~15和PERp0~15、PERn0~15共64根信号线组成32

对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号

用于接收链路。除此之外PCIe总线还使用了下列辅助信号。

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc