基于 Quartus II 的运算器的设计与实现

【摘 要】 本文借助于 Quartus II 软件在计算机上仿真制作了具有简单运算功

能的运算器,由此我们一方面可以了解电路仿真的主要流程,另一方面可以验证运算器的功

能。

【关键词】 Quartus II EDA 运算器 仿真

0 引言

电路设计对于电子信息类专业的学生而言是十分重要的,它是将理论知识运用于实践的

一个重要途径。它对巩固课堂教学内容,提高学生的动手能力具有重要作用。但对于一些比

较复杂的实验,学生要用大量的时间和精力进行电路连接和线路检查,常常是事倍功半,实

验效果不是很理想。将计算机模拟引入到实验教学中,既可以使学生随时进行实验,又可以

直接获取结果,增加学生的感性认识。而且计算机模拟仿真让设计变得更易实现,这不仅节

约了经济上的开销,还节约了大量的时间与精力。这里介绍的 Quartus II 可以弥补原先许

多数字芯片和线路连接的繁琐步骤和手工操作,使原先复杂的实现过程变得容易理解与掌

握,而且还能帮助学生更快、更好地掌握课堂理论内容,加深对概念原理的理解,进一步培

养学生的综合设计能力、排除故障能力和创新能力[1]。

本文借助 Quartus II6.0 现有的器件,设计了一个运算器,使用 Quartus II6.0 完成仿

真,并通过仿真波形展示该运算器是如何实现运算器功能的。

1 用 Quartus II 做电路设计实验的优点

Quartus II6.0 是由美国 Altera 公司开发的,是一款功能比较强的 EDA 工具软件,它

的优势主要体现在其功能齐全,方便简单。具有可编程系统(SOPC)设计的综合性环境,也是

适合 SOPC 的最全面的设计环境[2]。它拥有现场可编程阵列(FPGA)和复杂可编程器件(CPLD)

设计的所有阶段的解决方案。它的简单易用,方便快捷,给设计者减少了难度,节约了很多

时间 [3] 。

为了改变延续多年的“实验内容单一,实验设备陈旧,实验时间受限,实验效果差[4] ”

的状况,考虑到学校机房有许多时间向学生开放,另外考虑到许多学生自己有电脑,我们选

用了 Quartus II。Quartus II 功能强大、界面友好、易于掌握,彻底改变了传统的实验教

学模式,实验具有开放性、可编程性强、设计空间大、时间灵活等特点,并具有较高的实验

效率。它可以培养学生的动手能力和分析问题、解决问题的能力,增强学生对实验的浓厚兴

趣,提高实践教学的质量。其显著特点如下:

开放性好:学生可以在机房的开放时间进行实验,也可以在自己宿舍里的电脑上做实验;

学生可以在实验课之前预习,也可以在实验课之后进行复习;优秀学生可以进行提高训练,

来不及的和不会的学生可以在课后进行补差练习;相关课程结束后,感兴趣的学生也可以在

此方面继续钻研。

可操作性强:对提高学生的动手能力,加强学生对计算机整体和各组成部分的理解,增

强学生计算机系统综合设计能力都有很大帮助。

实验内容安排合理:实验能够与理论教学紧密结合,实验内容由简到繁,由浅入深,循

序渐进,使学生在课堂上学到的理论知识在实验中得到验证。

实验结果直观:实验平台采用的是 QuartusII,使用方便,操作简单,实验结果学生一

目了然。

实验内容有趣:实验内容紧扣教学内容,通过实验让学生更直观地理解书本知识,改变

�

了以往学生认为做实验没意思的状况,使学生做实验的兴趣越来越浓厚。

2 运算器的设计

一个简单的运算器由 ALU (两片 74181),数据寄存器 DR1,DR2(两片 74273)以及数据

缓冲器 ALU_BUF (一片 74244)构成[5],它们可以完成 DR1 与 DR2 的运算,具体的运算功能请

见下面的功能表[6]。

S3

S2

S1

S0

M=H 逻辑

M=L 算术运算

正 逻 辑

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

运算

—A

BA

—AB

0

AB

—B

A⊕B

A —B

—A+B

BA

B

AB

1

A+ —B

A+B

A

Cn=1

A

A+B

A+ —B

减 1

A 加 A —B

(A+B) 加 A —B

A 减 B 减 1

A —B减 1

A 加 AB

A 加 B

Cn=0

A 加 1

(A+B)加 1

(A+ —B)加 1

0

A 加 A —B加 1

(A+B)加 A —B加 1

A 减 B

A —B

A 加 AB 加 1

A 加 B 加 1

(A+ —B)加 AB

(A+ —B)加 AB 加 1

AB 减 1

A 加 A

(A+B)加 A

(A+ —B)加 A

A 减 1

AB

A 加 A 加 1

(A+B)加 A 加 1

(A+ —B)加 A 加 1

A

2.1 运算器的各个输入控制端口如下:

a)控制端 S0~S3, 组合控制运算器执行不同的运算,如:1001 时可以执行加(控制端

M 为低电平,控制端 CN0 时为高电平时有效)。

b)控制端 M,高电平时控制运算器执行算术运算,低电平时控制运算器执行逻辑运算。

c)控制端 N_AU(与 N_IN 互斥使用),运算器部件输出运算结果传送总线的使能端(注:

为了方便和以后设计的其它计算机部件连接,我们在这里设置了总线);

d)控制端 N_IN(与 N_ALU 互斥使用),输入数据传送总线的使能端;

e)控制端 LDDR1,数据寄存器 DR1 的时钟使能信号,上升沿到来时触发;

f)控制端 LDDR2,数据寄存器 DR2 的时钟使能信号,上升沿到来时触发;

g)时钟信号 CLK1,用来产生运算器部件所需的时钟信号;

h)控制端 CN0,运算器的低位进位端。低电平为有进位,高电平时为无进位(注:只

有在算术运算是有效);

2.2 运算器部件的各个输出端口如下:

a)DR1_OUT0~DR1_OUT7,数据寄存器 DR1 的显示灯;

b)DR2_OUT0~DR2_OUT7, 数据寄存器 DR2 的显示灯;

�

c)BUS0~BUS7,总线的数据显示灯;

d)CN8_ALU;运算器的高位进位端。高电平为有进位,低电平时为无进位;

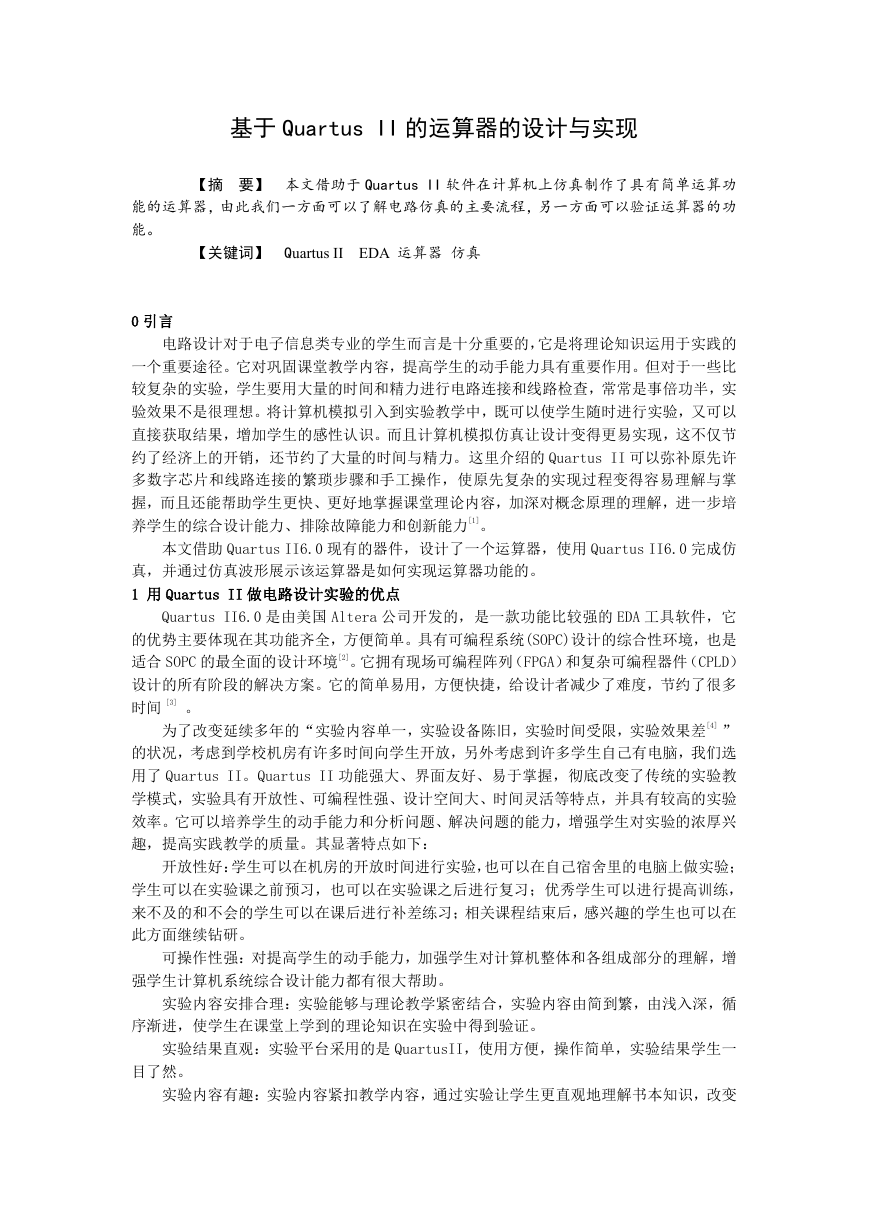

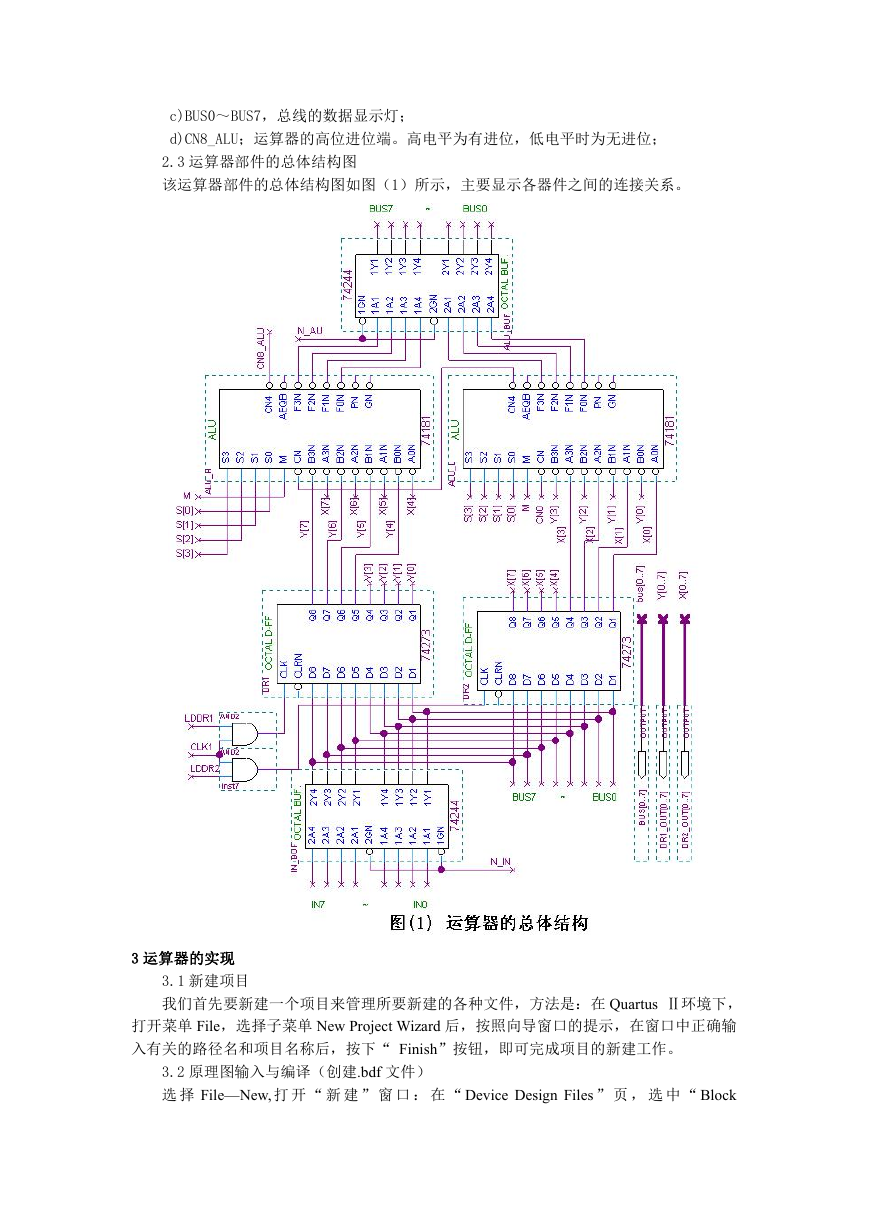

2.3 运算器部件的总体结构图

该运算器部件的总体结构图如图(1)所示,主要显示各器件之间的连接关系。

3 运算器的实现

3.1 新建项目

我们首先要新建一个项目来管理所要新建的各种文件,方法是:在 Quartus Ⅱ环境下,

打开菜单 File,选择子菜单 New Project Wizard 后,按照向导窗口的提示,在窗口中正确输

入有关的路径名和项目名称后,按下“ Finish”按钮,即可完成项目的新建工作。

3.2 原理图输入与编译(创建.bdf 文件)

选 择 File—New, 打 开 “ 新 建 ” 窗 口 : 在 “ Device Design Files ” 页 , 选 中 “ Block

�

Diagram/Schematic File”项后,按下“OK”按钮即可打开原理图编辑器,进行原理图的录

入编辑,在进行逻辑图输入时,在编辑区的空白处双击鼠标左键,即可打开标题栏为

“Symbol”的窗口:你只需在“Name”标签下的输入框中输入要用到的器件的名称(比如

74181、input、output 等等),就可以把该器件输入到编辑区中。待线路连接等编辑工作完成

后,即可按下“►”按钮进行编译。

3.3 创建向量波形文件(创建.vwf 文件)

当原理图编译完成后,会出现对话框“Full compilation was successful”,此时就要新建

波形文件,以便利用波形文件进行仿真分析。打开新建窗口,选择“Other files”标签,选

中“Vector waveform File”一项,按下“OK”按钮,即可新建一个波形文件,双击 Name

下面的空白区域后出现“Insert Node or Bus”对话框,点击“Node Finder”按钮,在弹出的

“Node Finder”对话框 Filter 中选择“Pins: all”,点击“Start” 按钮,然后在选中下面正中

的“》”按钮,点击当前对话框的“OK” 按钮,最后再点击“Insert Node or Bus”对话框的

“OK” 按钮即可。

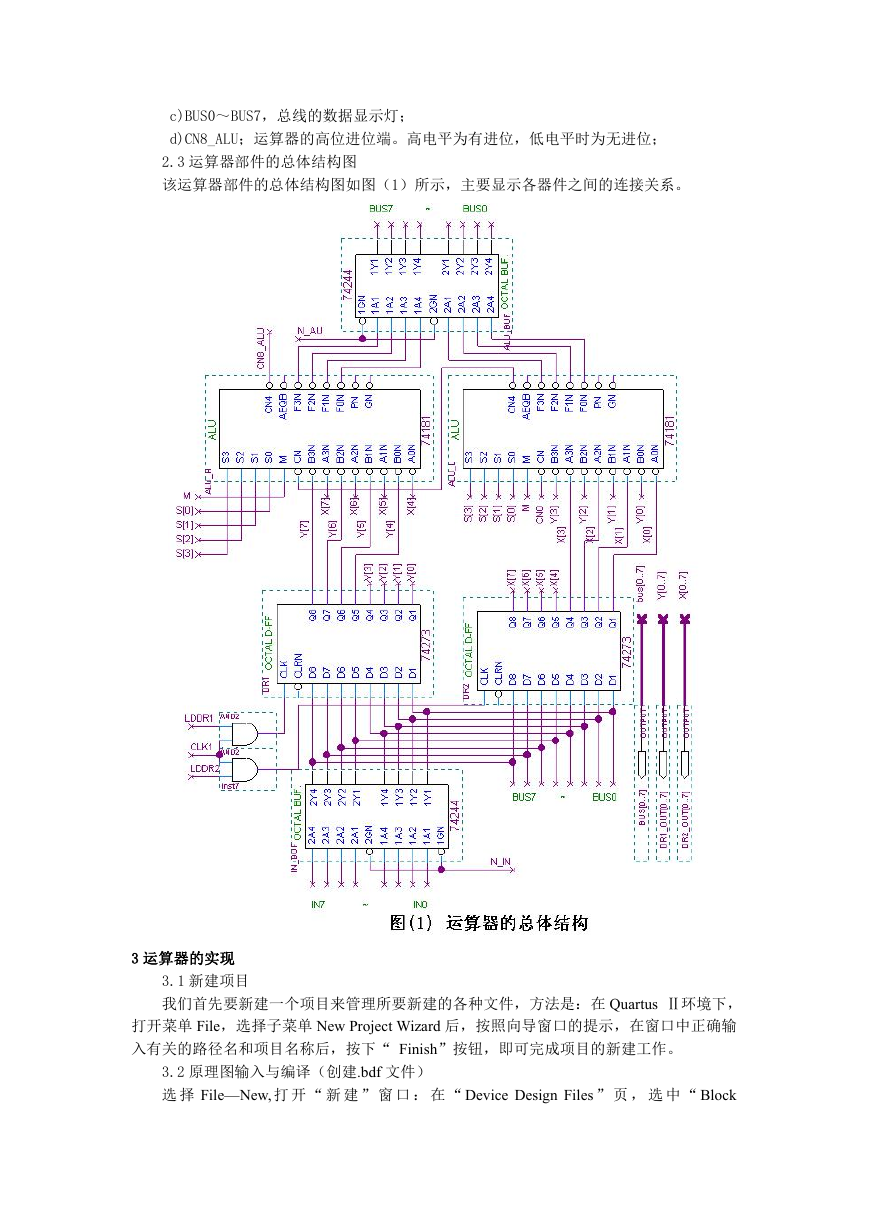

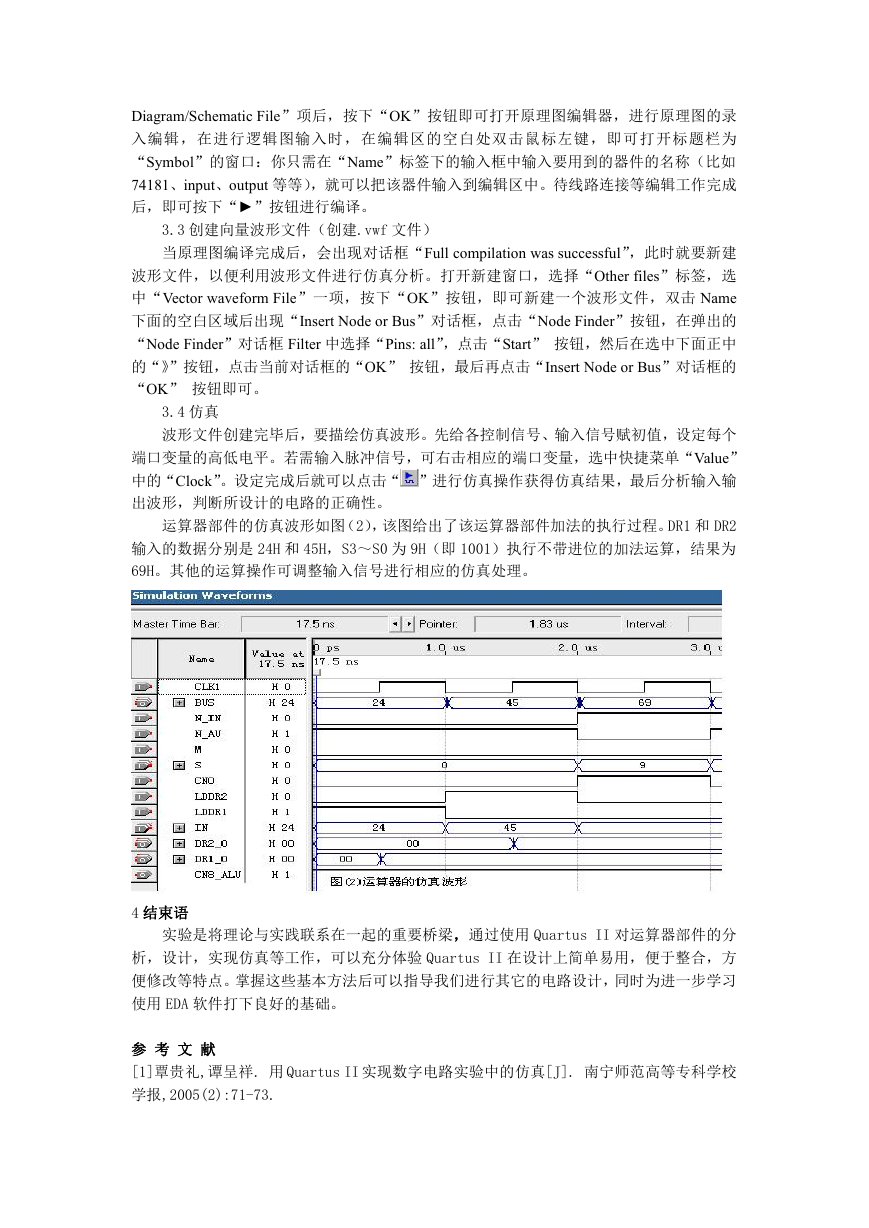

3.4 仿真

波形文件创建完毕后,要描绘仿真波形。先给各控制信号、输入信号赋初值,设定每个

端口变量的高低电平。若需输入脉冲信号,可右击相应的端口变量,选中快捷菜单“Value”

中的“Clock”。设定完成后就可以点击“ ”进行仿真操作获得仿真结果,最后分析输入输

出波形,判断所设计的电路的正确性。

运算器部件的仿真波形如图(2),该图给出了该运算器部件加法的执行过程。DR1 和 DR2

输入的数据分别是 24H 和 45H,S3~S0 为 9H(即 1001)执行不带进位的加法运算,结果为

69H。其他的运算操作可调整输入信号进行相应的仿真处理。

4 结束语

实验是将理论与实践联系在一起的重要桥梁,通过使用 Quartus II 对运算器部件的分

析,设计,实现仿真等工作,可以充分体验 Quartus II 在设计上简单易用,便于整合,方

便修改等特点。掌握这些基本方法后可以指导我们进行其它的电路设计,同时为进一步学习

使用 EDA 软件打下良好的基础。

参 考 文 献

[1]覃贵礼,谭呈祥. 用 Quartus II 实现数字电路实验中的仿真[J]. 南宁师范高等专科学校

学报,2005(2):71-73.

�

[2]郑亚民,许敏. 基于 Quartus II 的带计时器功能的秒表系统设计[J]. 电子工程师,

2005(01):59-62.

[3] 李 雪 梅 . 用 Quartu II4.0 设 计 数 字 电 路 过 程 的 介 绍 [J]. 现 代 电 子 技 术 ,

2005(06):35-38.

[4] 裘雪红. 计算机组成原理实验指导[EB/OL].

http://202.117.112.23/zcyl/experiment/guide.htm, 2007-6-10/2007-8-26.

[5]王爱英. 计算机组成与结构[M]. 北京:清华大学出版社,2001: 170-172.

[6]东南大学计算机学院. ALU 部件 [EB/OL].

http://cse.seu.edu.cn/people/xuzaolin/Chapter3/untitled14.html, 2007-5-11/2007-8-23.

Design and Implementation of Arithmetic Unit based on Quartus II

Cheng Yao,Wang Li-chun,Gu Hui

(School of Computer Science & Technology, Nantong University, Jiangsu, China 226019)

Abstract: In this article, the authors design and implementation a arithmetic unit based on

Quartus II. It can help us to learn the main flow of circuit simulation and validate the function of

the arithmetic unit.

Key words: Quartus II, EDA, Arithmetic Unit, Simulation

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc