ARMv7-M Architecture Reference Manual

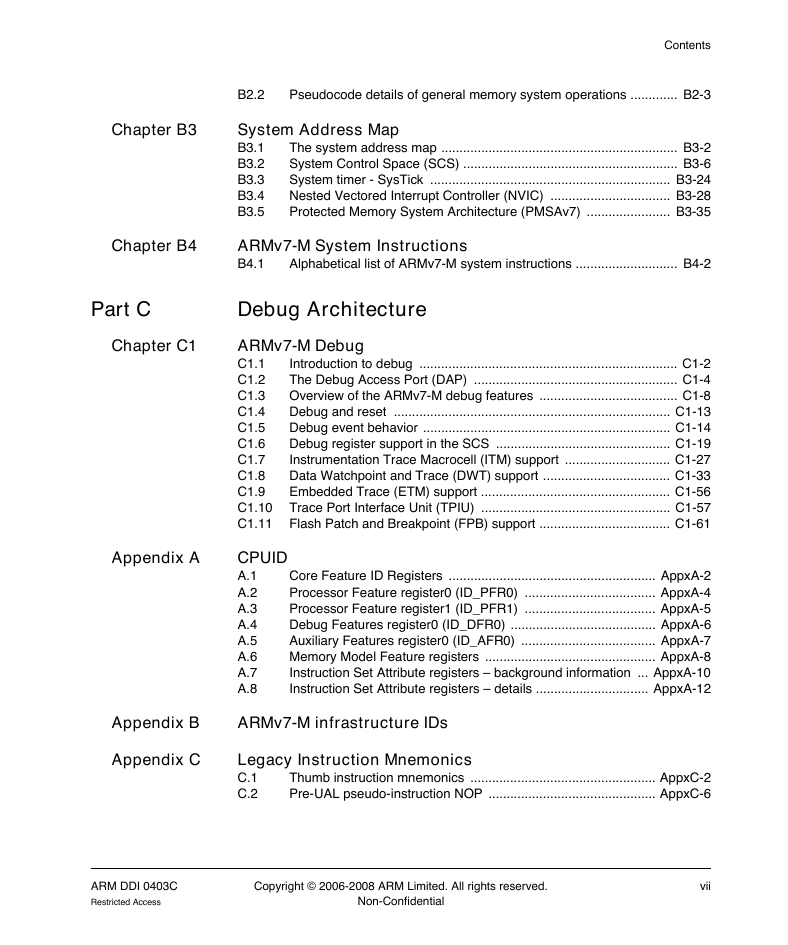

Contents

List of Tables

List of Figures

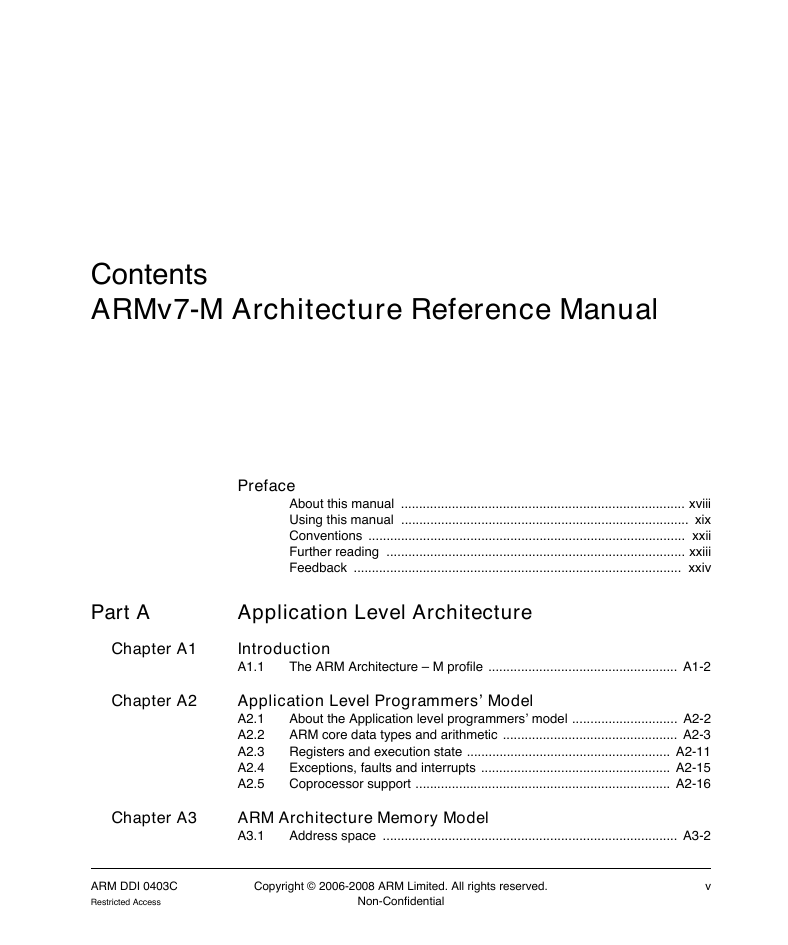

Preface

About this manual

Using this manual

Part A, Application level architecture

Part B, system level architecture

Part C, debug architecture

Part D, appendices

Conventions

General typographic conventions

Further reading

ARM publications

Feedback

Feedback on this book

Application Level Architecture

Introduction

A1.1 The ARM Architecture – M profile

Application Level Programmers’ Model

A2.1 About the Application level programmers’ model

A2.1.1 Privileged execution

A2.1.2 System level architecture

A2.2 ARM core data types and arithmetic

A2.2.1 Integer arithmetic

Shift and rotate operations

Pseudocode details of addition and subtraction

Pseudocode details of saturation

A2.3 Registers and execution state

A2.3.1 ARM core registers

Pseudocode details of ARM core register operations

A2.3.2 The Application Program Status Register (APSR)

A2.3.3 Execution state support

A2.3.4 Privileged execution

A2.4 Exceptions, faults and interrupts

A2.4.1 System related events

A2.5 Coprocessor support

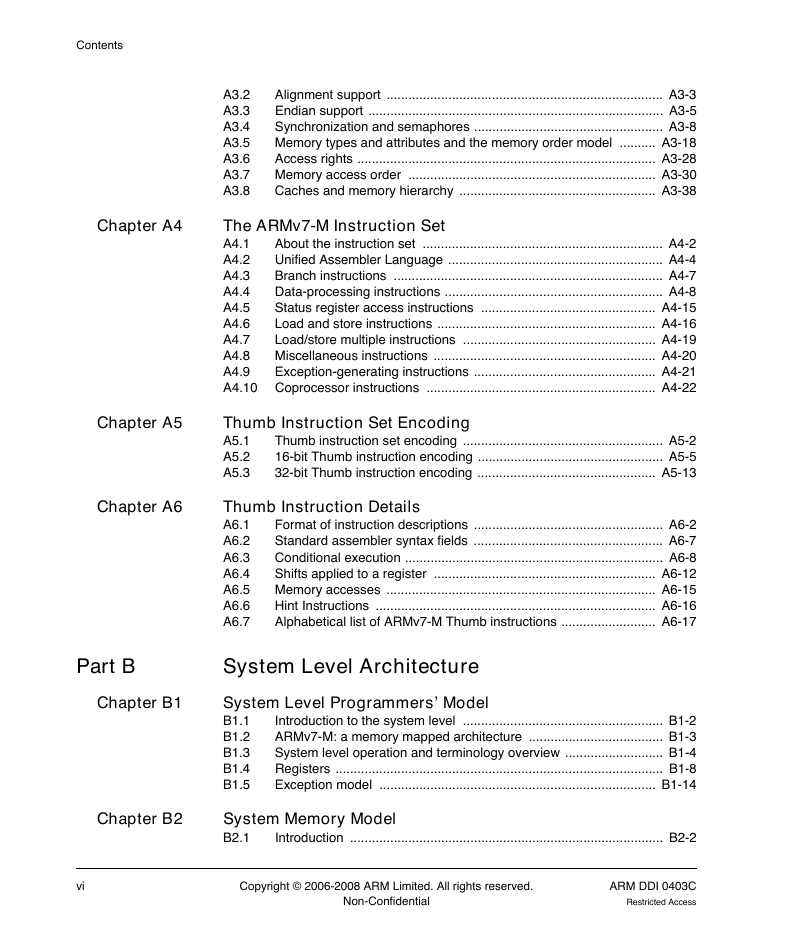

ARM Architecture Memory Model

A3.1 Address space

A3.1.1 Virtual versus physical addressing

A3.2 Alignment support

A3.2.1 Alignment behavior

Alignment and data access

Alignment and updates to the PC

A3.3 Endian support

A3.3.1 Control of the Endian Mapping in ARMv7-M

Instruction alignment and byte ordering

A3.3.2 Element size and Endianness

A3.3.3 Instructions to reverse bytes in a general-purpose register

A3.4 Synchronization and semaphores

A3.4.1 Exclusive access instructions and Non-shareable memory regions

A3.4.2 Exclusive access instructions and Shareable memory regions

Operation of the global monitor

A3.4.3 Tagging and the size of the tagged memory block

A3.4.4 Context switch support

A3.4.5 Load-Exclusive and Store-Exclusive usage restrictions

A3.4.6 Synchronization primitives and the memory order model

A3.5 Memory types and attributes and the memory order model

A3.5.1 Memory types

A3.5.2 Summary of ARMv7 memory attributes

A3.5.3 Atomicity in the ARM architecture

Single-copy atomicity

Multi-copy atomicity

A3.5.4 Normal memory

Non-shareable Normal memory

Shareable Normal memory

Write-Through cacheable, Write-Back cacheable and Non-cacheable Normal memory

A3.5.5 Device memory

Shareable attribute for Device memory regions

A3.5.6 Strongly-ordered memory

A3.5.7 Memory access restrictions

A3.6 Access rights

A3.6.1 Privilege level access controls for data accesses

A3.6.2 Privilege level access controls for instruction accesses

A3.7 Memory access order

A3.7.1 Reads and writes

Reads

Writes

Synchronization primitives

Observability and completion

A3.7.2 Ordering requirements for memory accesses

Program order for instruction execution

A3.7.3 Memory barriers

Data Memory Barrier (DMB)

Data Synchronization Barrier (DSB)

Instruction Synchronization Barrier (ISB)

A3.8 Caches and memory hierarchy

A3.8.1 Introduction to caches

A3.8.2 Implication of caches to the application programmer

A3.8.3 Preloading caches

The ARMv7-M Instruction Set

A4.1 About the instruction set

A4.1.1 ARMv7-M and interworking support

A4.1.2 Conditional execution

A4.2 Unified Assembler Language

A4.2.1 Conditional instructions

A4.2.2 Use of labels in UAL instruction syntax

A4.3 Branch instructions

A4.4 Data-processing instructions

A4.4.1 Standard data-processing instructions

A4.4.2 Shift instructions

A4.4.3 Multiply instructions

A4.4.4 Saturating instructions

A4.4.5 Packing and unpacking instructions

A4.4.6 Miscellaneous data-processing instructions

A4.4.7 Divide instructions

A4.5 Status register access instructions

A4.6 Load and store instructions

A4.6.1 Loads to the PC

A4.6.2 Halfword and byte loads and stores

A4.6.3 Unprivileged loads and stores

A4.6.4 Exclusive loads and stores

A4.6.5 Addressing modes

A4.7 Load/store multiple instructions

A4.7.1 Loads to the PC

A4.8 Miscellaneous instructions

A4.9 Exception-generating instructions

A4.10 Coprocessor instructions

Thumb Instruction Set Encoding

A5.1 Thumb instruction set encoding

A5.1.1 UNDEFINED and UNPREDICTABLE instruction set space

A5.1.2 Use of 0b1111 as a register specifier

A5.1.3 Use of 0b1101 as a register specifier

R13[1:0] definition

32-bit Thumb instruction support for R13

16-bit Thumb instruction support for R13

A5.2 16-bit Thumb instruction encoding

A5.2.1 Shift (immediate), add, subtract, move, and compare

A5.2.2 Data processing

A5.2.3 Special data instructions and branch and exchange

A5.2.4 Load/store single data item

A5.2.5 Miscellaneous 16-bit instructions

If-Then, and hints

A5.2.6 Conditional branch, and supervisor call

A5.3 32-bit Thumb instruction encoding

A5.3.1 Data processing (modified immediate)

A5.3.2 Modified immediate constants in Thumb instructions

Carry out

Operation

A5.3.3 Data processing (plain binary immediate)

A5.3.4 Branches and miscellaneous control

Hint instructions

Miscellaneous control instructions

A5.3.5 Load/store multiple

A5.3.6 Load/store dual or exclusive, table branch

A5.3.7 Load word

A5.3.8 Load halfword, unallocated memory hints

A5.3.9 Load byte, memory hints

A5.3.10 Store single data item

A5.3.11 Data processing (shifted register)

Move register and immediate shifts

A5.3.12 Data processing (register)

A5.3.13 Miscellaneous operations

A5.3.14 Multiply, and multiply accumulate

A5.3.15 Long multiply, long multiply accumulate, and divide

A5.3.16 Coprocessor instructions

Thumb Instruction Details

A6.1 Format of instruction descriptions

A6.1.1 Instruction section title

A6.1.2 Introduction to the instruction

A6.1.3 Instruction encodings

A6.1.4 Assembler syntax

Assembler syntax prototype line conventions

A6.1.5 Pseudocode describing how the instruction operates

A6.1.6 Exception information

A6.1.7 Notes

A6.2 Standard assembler syntax fields

A6.3 Conditional execution

A6.3.1 Pseudocode details of conditional execution

A6.3.2 Conditional execution of undefined instructions

A6.3.3 ITSTATE

Pseudocode details of ITSTATE operation

A6.4 Shifts applied to a register

A6.4.1 Constant shifts

Encoding

A6.4.2 Register controlled shifts

A6.4.3 Shift operations

A6.5 Memory accesses

A6.6 Hint Instructions

A6.6.1 Memory hints

A6.6.2 NOP-compatible hints

A6.7 Alphabetical list of ARMv7-M Thumb instructions

A6.7.1 ADC (immediate)

Assembler syntax

Operation

Exceptions

A6.7.2 ADC (register)

Assembler syntax

Operation

Exceptions

A6.7.3 ADD (immediate)

Assembler syntax

Operation

Exceptions

A6.7.4 ADD (register)

Assembler syntax

Operation

Exceptions

A6.7.5 ADD (SP plus immediate)

Assembler syntax

Operation

Exceptions

A6.7.6 ADD (SP plus register)

Assembler syntax

Operation

Exceptions

A6.7.7 ADR

Assembler syntax

Operation

Exceptions

A6.7.8 AND (immediate)

Assembler syntax

Operation

Exceptions

A6.7.9 AND (register)

Assembler syntax

Operation

Exceptions

A6.7.10 ASR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.11 ASR (register)

Assembler syntax

Operation

Exceptions

A6.7.12 B

Assembler syntax

Operation

Exceptions

Related encodings

A6.7.13 BFC

Assembler syntax

Operation

Exceptions

A6.7.14 BFI

Assembler syntax

Operation

Exceptions

A6.7.15 BIC (immediate)

Assembler syntax

Operation

Exceptions

A6.7.16 BIC (register)

Assembler syntax

Operation

Exceptions

A6.7.17 BKPT

Assembler syntax

Operation

Exceptions

A6.7.18 BL

Assembler syntax

Operation

Exceptions

Note

A6.7.19 BLX (register)

Assembler syntax

Operation

Exceptions

A6.7.20 BX

Assembler syntax

Operation

Exceptions

A6.7.21 CBNZ, CBZ

Assembler syntax

Operation

Exceptions

A6.7.22 CDP, CDP2

Assembler syntax

Operation

Exceptions

Notes

A6.7.23 CLREX

Assembler syntax

Operation

Exceptions

A6.7.24 CLZ

Assembler syntax

Operation

Exceptions

A6.7.25 CMN (immediate)

Assembler syntax

Operation

Exceptions

A6.7.26 CMN (register)

Assembler syntax

Operation

Exceptions

A6.7.27 CMP (immediate)

Assembler syntax

Operation

Exceptions

A6.7.28 CMP (register)

Assembler syntax

Operation

Exceptions

A6.7.29 CPS

Note

A6.7.30 CPY

Assembler syntax

Exceptions

A6.7.31 DBG

Assembler syntax

Operation

Exceptions

A6.7.32 DMB

Assembler syntax

Operation

Exceptions

A6.7.33 DSB

Assembler syntax

Operation

Exceptions

A6.7.34 EOR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.35 EOR (register)

Assembler syntax

Operation

Exceptions

A6.7.36 ISB

Assembler syntax

Operation

Exceptions

A6.7.37 IT

Assembler syntax

Operation

Exceptions

Related encodings

A6.7.38 LDC, LDC2 (immediate)

Assembler syntax

Operation

Exceptions

A6.7.39 LDC, LDC2 (literal)

Assembler syntax

Operation

Exceptions

A6.7.40 LDM / LDMIA / LDMFD

Assembler syntax

Operation

Exceptions

A6.7.41 LDMDB / LDMEA

Assembler syntax

Operation

Exceptions

A6.7.42 LDR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.43 LDR (literal)

Assembler syntax

Operation

Exceptions

A6.7.44 LDR (register)

Assembler syntax

Operation

Exceptions

A6.7.45 LDRB (immediate)

Assembler syntax

Operation

Exceptions

A6.7.46 LDRB (literal)

Assembler syntax

Operation

Exceptions

A6.7.47 LDRB (register)

Assembler syntax

Operation

Exceptions

A6.7.48 LDRBT

Assembler syntax

Operation

Exceptions

A6.7.49 LDRD (immediate)

Assembler syntax

Operation

Exceptions

A6.7.50 LDRD (literal)

Assembler syntax

Operation

Exceptions

A6.7.51 LDREX

Assembler syntax

Operation

Exceptions

A6.7.52 LDREXB

Assembler syntax

Operation

Exceptions

A6.7.53 LDREXH

Assembler syntax

Operation

Exceptions

A6.7.54 LDRH (immediate)

Assembler syntax

Operation

Exceptions

Unallocated memory hints

A6.7.55 LDRH (literal)

Assembler syntax

Operation

Exceptions

A6.7.56 LDRH (register)

Assembler syntax

Operation

Exceptions

A6.7.57 LDRHT

Assembler syntax

Operation

Exceptions

A6.7.58 LDRSB (immediate)

Assembler syntax

Operation

Exceptions

A6.7.59 LDRSB (literal)

Assembler syntax

Operation

Exceptions

A6.7.60 LDRSB (register)

Assembler syntax

Operation

Exceptions

A6.7.61 LDRSBT

Assembler syntax

Operation

Exceptions

A6.7.62 LDRSH (immediate)

Assembler syntax

Operation

Exceptions

A6.7.63 LDRSH (literal)

Assembler syntax

Operation

Exceptions

Unallocated memory hints

A6.7.64 LDRSH (register)

Assembler syntax

Operation

Exceptions

A6.7.65 LDRSHT

Assembler syntax

Operation

Exceptions

A6.7.66 LDRT

Assembler syntax

Operation

Exceptions

A6.7.67 LSL (immediate)

Assembler syntax

Operation

Exceptions

A6.7.68 LSL (register)

Assembler syntax

Operation

Exceptions

A6.7.69 LSR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.70 LSR (register)

Assembler syntax

Operation

Exceptions

A6.7.71 MCR, MCR2

Assembler syntax

Operation

Exceptions

Notes

A6.7.72 MCRR, MCRR2

Assembler syntax

Operation

Exceptions

A6.7.73 MLA

Assembler syntax

Operation

Exceptions

A6.7.74 MLS

Assembler syntax

Operation

Exceptions

A6.7.75 MOV (immediate)

Assembler syntax

Operation

Exceptions

A6.7.76 MOV (register)

Assembler syntax

Operation

Exceptions

A6.7.77 MOV (shifted register)

Assembler syntax

Exceptions

A6.7.78 MOVT

Assembler syntax

Operation

Exceptions

A6.7.79 MRC, MRC2

Assembler syntax

Operation

Exceptions

A6.7.80 MRRC, MRRC2

Assembler syntax

Operation

Exceptions

A6.7.81 MRS

Note

A6.7.82 MSR (register)

Note

A6.7.83 MUL

Assembler syntax

Operation

Exceptions

A6.7.84 MVN (immediate)

Assembler syntax

Operation

Exceptions

A6.7.85 MVN (register)

Assembler syntax

Operation

Exceptions

A6.7.86 NEG

Assembler syntax

Exceptions

A6.7.87 NOP

Assembler syntax

Operation

Exceptions

A6.7.88 ORN (immediate)

Assembler syntax

Operation

Exceptions

A6.7.89 ORN (register)

Assembler syntax

Operation

Exceptions

A6.7.90 ORR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.91 ORR (register)

Assembler syntax

Operation

Exceptions

A6.7.92 PLD, PLDW (immediate)

Assembler syntax

Operation

Exceptions

A6.7.93 PLD (literal)

Assembler syntax

Operation

Exceptions

A6.7.94 PLD (register)

Assembler syntax

Operation

Exceptions

A6.7.95 PLI (immediate, literal)

Assembler syntax

Operation

Exceptions

A6.7.96 PLI (register)

Assembler syntax

Operation

Exceptions

A6.7.97 POP

Assembler syntax

Operation

Exceptions

A6.7.98 PUSH

Assembler syntax

Operation

Exceptions

A6.7.99 RBIT

Assembler syntax

Operation

Exceptions

A6.7.100 REV

Assembler syntax

Operation

Exceptions

A6.7.101 REV16

Assembler syntax

Operation

Exceptions

A6.7.102 REVSH

Assembler syntax

Operation

Exceptions

A6.7.103 ROR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.104 ROR (register)

Assembler syntax

Operation

Exceptions

A6.7.105 RRX

Assembler syntax

Operation

Exceptions

A6.7.106 RSB (immediate)

Assembler syntax

Operation

Exceptions

A6.7.107 RSB (register)

Assembler syntax

Operation

Exceptions

A6.7.108 SBC (immediate)

Assembler syntax

Operation

Exceptions

A6.7.109 SBC (register)

Assembler syntax

Operation

Exceptions

A6.7.110 SBFX

Assembler syntax

Operation

Exceptions

A6.7.111 SDIV

Assembler syntax

Operation

Exceptions

Notes

A6.7.112 SEV

Assembler syntax

Operation

Exceptions

A6.7.113 SMLAL

Assembler syntax

Operation

Exceptions

A6.7.114 SMULL

Assembler syntax

Operation

Exceptions

A6.7.115 SSAT

Assembler syntax

Operation

Exceptions

A6.7.116 STC, STC2

Assembler syntax

Operation

Exceptions

A6.7.117 STM / STMIA / STMEA

Assembler syntax

Operation

Exceptions

A6.7.118 STMDB / STMFD

Assembler syntax

Operation

Exceptions

A6.7.119 STR (immediate)

Assembler syntax

Operation

Exceptions

A6.7.120 STR (register)

Assembler syntax

Operation

Exceptions

A6.7.121 STRB (immediate)

Assembler syntax

Operation

Exceptions

A6.7.122 STRB (register)

Assembler syntax

Operation

Exceptions

A6.7.123 STRBT

Assembler syntax

Operation

Exceptions

A6.7.124 STRD (immediate)

Assembler syntax

Operation

Exceptions

A6.7.125 STREX

Assembler syntax

Operation

Exceptions

A6.7.126 STREXB

Assembler syntax

Operation

Exceptions

A6.7.127 STREXH

Assembler syntax

Operation

Exceptions

A6.7.128 STRH (immediate)

Assembler syntax

Operation

Exceptions

A6.7.129 STRH (register)

Assembler syntax

Operation

Exceptions

A6.7.130 STRHT

Assembler syntax

Operation

Exceptions

A6.7.131 STRT

Assembler syntax

Operation

Exceptions

A6.7.132 SUB (immediate)

Assembler syntax

Operation

Exceptions

A6.7.133 SUB (register)

Assembler syntax

Operation

Exceptions

A6.7.134 SUB (SP minus immediate)

Assembler syntax

Operation

Exceptions

A6.7.135 SUB (SP minus register)

Assembler syntax

Operation

Exceptions

A6.7.136 SVC (formerly SWI)

Assembler syntax

Operation

Exceptions

A6.7.137 SXTB

Assembler syntax

Operation

Exceptions

A6.7.138 SXTH

Assembler syntax

Operation

Exceptions

A6.7.139 TBB, TBH

Assembler syntax

Operation

Exceptions

A6.7.140 TEQ (immediate)

Assembler syntax

Operation

Exceptions

A6.7.141 TEQ (register)

Assembler syntax

Operation

Exceptions

A6.7.142 TST (immediate)

Assembler syntax

Operation

Exceptions

A6.7.143 TST (register)

Assembler syntax

Operation

Exceptions

A6.7.144 UBFX

Assembler syntax

Operation

Exceptions

A6.7.145 UDIV

Assembler syntax

Operation

Exceptions

A6.7.146 UMLAL

Assembler syntax

Operation

Exceptions

A6.7.147 UMULL

Assembler syntax

Operation

Exceptions

A6.7.148 USAT

Assembler syntax

Operation

Exceptions

A6.7.149 UXTB

Assembler syntax

Operation

Exceptions

A6.7.150 UXTH

Assembler syntax

Operation

Exceptions

A6.7.151 WFE

Assembler syntax

Operation

Exceptions

A6.7.152 WFI

Assembler syntax

Operation

Exceptions

Notes

A6.7.153 YIELD

Assembler syntax

Operation

Exceptions

System Level Architecture

System Level Programmers’ Model

B1.1 Introduction to the system level

B1.2 ARMv7-M: a memory mapped architecture

B1.3 System level operation and terminology overview

B1.3.1 Modes, Privilege and Stacks

B1.3.2 Exceptions

Priority Levels and Execution Pre-emption

Exception Return

B1.3.3 Execution State

B1.3.4 Debug State

B1.4 Registers

B1.4.1 The SP registers

B1.4.2 The special-purpose program status registers (xPSR)

B1.4.3 The special-purpose mask registers

B1.4.4 The special-purpose control register

B1.4.5 Reserved special-purpose register bits

B1.4.6 Special-purpose register updates and the memory order model

B1.4.7 Register related definitions for pseudocode

Pseudocode details for ARM core register access in the Thumb instruction set

B1.5 Exception model

B1.5.1 Overview of the exceptions supported

B1.5.2 Exception number definition

B1.5.3 The vector table

B1.5.4 Exception priorities and pre-emption

Priority grouping

Execution priority and priority boosting within the core

Priority escalation

SVCall, PendSV and critical region code avoidance

B1.5.5 Reset behavior

B1.5.6 Exception entry behavior

B1.5.7 Stack alignment on exception entry

Theory of operation

Compatibility

B1.5.8 Exception return behavior

Integrity checks on exception returns

Exception return operation

B1.5.9 Exceptions in single-word load operations

B1.5.10 Exceptions in LDM and STM operations

Load multiple and PC in load list

Load-store multiple, base register update and the ICI bits

B1.5.11 Exceptions on exception entry

Late arriving exceptions

Derived exceptions

B1.5.12 Tail-chaining and exceptions on exception return

Derived exceptions

Tail-chaining

Use of tail-chaining as an optimization for pending exceptions

Late arrival pre-emption and tail-chaining during exception returns

B1.5.13 Exception status and control

B1.5.14 Fault behavior

Fault status and address information

B1.5.15 Unrecoverable exception cases

B1.5.16 Reset management

Reset and debug

B1.5.17 Power management

B1.5.18 Wait For Event and Send Event

WFE wake-up events

The Event Register

The Send Event instruction

The Wait For Event instruction

Pseudocode details of the Wait For Event lock mechanism

B1.5.19 Wait For Interrupt

Using WFI to indicate an idle state on bus interfaces

Pseudocode details of Wait For Interrupt

System Memory Model

B2.1 Introduction

B2.2 Pseudocode details of general memory system operations

B2.2.1 Memory data type definitions

B2.2.2 Basic memory accesses

B2.2.3 Interfaces to memory system specific pseudocode

B2.2.4 Aligned memory accesses

B2.2.5 Unaligned memory accesses

B2.2.6 Reverse endianness

B2.2.7 Pseudocode details of operations on exclusive monitors

B2.2.8 Access permission checking

B2.2.9 MPU access control decode

B2.2.10 Default memory access decode

B2.2.11 MemManage fault handling

System Address Map

B3.1 The system address map

B3.1.1 General rules applying to PPB register access

B3.2 System Control Space (SCS)

B3.2.1 System control and ID blocks

The Interrupt Controller Type Register (ICTR)

The Auxiliary Control Register (ACTLR)

B3.2.2 System ID register support in the SCS

CPU attribute ID registers

B3.2.3 The System Control Block (SCB)

Interrupt Control State Register (ICSR)

Vector Table Offset Register (VTOR)

Application Interrupt and Reset Control Register (AIRCR)

System Control Register (SCR)

Configuration and Control Register (CCR)

System Handler Priority Register 1 (SHPR1)

System Handler Priority Register 2 (SHPR2)

System Handler Priority Register 3 (SHPR3)

System Handler Control and State Register (SHCSR)

Configurable Fault Status Registers (UserFault, BusFault, and MemManage)

HardFault Status register (HFSR)

Debug Fault Status Register (DFSR)

Auxiliary Fault Status Register (AFSR)

MemManage Address Register (MMFAR)

BusFault Address Register (BFAR)

Coprocessor Access Control Register (CPACR)

Software Trigger Interrupt Register (STIR)

B3.3 System timer - SysTick

B3.3.1 Theory of operation

B3.3.2 System timer register support in the SCS

SysTick Control and Status Register (SYST_CSR)

SysTick Reload Value Register (SYST_RVR)

SysTick Current Value Register (SYST_CVR)

SysTick Calibration value Register (SYST_CALIB)

B3.4 Nested Vectored Interrupt Controller (NVIC)

B3.4.1 Theory of operation

External interrupt input behavior

B3.4.2 NVIC register support in the SCS

Interrupt Controller Type Register (ICTR)

Interrupt Set-Enable and Clear-Enable Registers (NVIC_ISERx and NVIC_ICERx)

Interrupt Set-Pending and Clear-Pending Registers (NVIC_ISPRx and NVIC_ICPRx)

Active Bit Register (NVIC_IABRx)

Interrupt Priority Register (NVIC_IPRx)

B3.5 Protected Memory System Architecture (PMSAv7)

B3.5.1 PMSAv7 compliant MPU operation

Sub-region support

ARMv7-M specific support

MPU pseudocode

MPU fault support

B3.5.2 Register support for PMSAv7 in the SCS

MPU Type Register (MPU_TYPE)

MPU Control Register (MPU_CTRL)

MPU Region Number Register (MPU_RNR)

MPU Region Base Address Register (MPU_RBAR)

MPU Region Attribute and Size Register (MPU_RASR)

MPU alias register support

ARMv7-M System Instructions

B4.1 Alphabetical list of ARMv7-M system instructions

B4.1.1 CPS

Assembler syntax

Operation

Exceptions

Notes

B4.1.2 MRS

Assembler syntax

Operation

Exceptions

Notes

B4.1.3 MSR (register)

Assembler syntax

Operation

Exceptions

Notes

Debug Architecture

ARMv7-M Debug

C1.1 Introduction to debug

C1.2 The Debug Access Port (DAP)

C1.2.1 General rules applying to debug register access

C1.3 Overview of the ARMv7-M debug features

C1.3.1 Debug authentication

C1.3.2 External debug request

C1.3.3 External restart request

DBGRESTART and DBGRESTARTED

C1.3.4 Debug support in ARMv7-M

Recommended levels of debug

C1.4 Debug and reset

C1.5 Debug event behavior

C1.5.1 Debug stepping

Debug monitor stepping

C1.6 Debug register support in the SCS

C1.6.1 Debug Fault Status Register (DFSR)

C1.6.2 Debug Halting Control and Status Register (DHCSR)

C1.6.3 Debug Core Register Selector Register (DCRSR)

C1.6.4 Debug Core Register Data Register (DCRDR)

C1.6.5 Debug Exception and Monitor Control Register (DEMCR)

Vector catch support

C1.7 Instrumentation Trace Macrocell (ITM) support

C1.7.1 Theory of operation

Timestamp support

Synchronization support

C1.7.2 Register support for the ITM

Stimulus Portx Register - ITM_STIM[255:0] (0xE0000000 to 0xE00003FC)

Trace Enable Register - ITM_TER[7:0] (0xE0000E00 to 0xE0000E1C)

Trace Privilege Register - ITM_TPR (0xE0000E40)

Trace Control Register – ITM_TCR (0xE0000E80)

C1.8 Data Watchpoint and Trace (DWT) support

C1.8.1 Theory of operation

Exception trace support

Cycle counter and PC sampling support

Profiling counter support

Profiling counter accuracy

Program counter sampling support

Comparator support

LinkAddr() support

Comparator support - cycle count matching

Comparator support - instruction address matching

Comparator support - data address matching

Comparator support - watchpoint data value matching

C1.8.2 Register support for the DWT

Control Register (DWT_CTRL)

Cycle Count Register (DWT_CYCCNT)

CPI Count Register (DWT_CPICNT)

Exception Overhead Count Register (DWT_EXCCNT)

Sleep Count Register (DWT_SLEEPCNT)

LSU Count Register (DWT_LSUCNT)

Folded-instruction Count Register (DWT_FOLDCNT)

Program Counter Sample Register (DWT_PCSR)

Comparator Register (DWT_COMPx)

Mask Register (DWT_MASKx)

Function Register (DWT_FUNCTIONx)

C1.9 Embedded Trace (ETM) support

C1.10 Trace Port Interface Unit (TPIU)

C1.10.1 The TPIU Programmers’ Model

Supported Synchronous Port Sizes Register (TPIU_SSPSR, 0xE0040000)

Current Synchronous Port Size Register (TPIU_CSPSR, 0xE0040004)

Asynchronous Clock Prescaler Register (TPIU_ACPR, 0xE0040010)

Selected Pin Protocol Register (TPIU_SPPR, 0xE00400F0)

TPIU Type Register (TPIU_TYPE, 0xE0040FC8)

C1.11 Flash Patch and Breakpoint (FPB) support

C1.11.1 Theory of operation

C1.11.2 Register support for the FPB

FlashPatch Control Register (FP_CTRL)

FlashPatch Remap Register (FP_REMAP)

FlashPatch Comparator Register – instruction comparison (FP_COMPx)

FlashPatch Comparator Register – literal comparison (FP_COMPx)

Appendices

CPUID

A.1 Core Feature ID Registers

A.1.1 Convention for CPUID attribute descriptions

A.2 Processor Feature register0 (ID_PFR0)

A.3 Processor Feature register1 (ID_PFR1)

A.4 Debug Features register0 (ID_DFR0)

A.5 Auxiliary Features register0 (ID_AFR0)

A.6 Memory Model Feature registers

A.6.1 Memory Model Feature register0 (ID_MMFR0)

A.6.2 Memory Model Feature register1 (ID_MMFR1)

A.6.3 Memory Model Feature register2 (ID_MMFR2)

A.6.4 Memory Model Feature register3 (ID_MMFR3)

A.7 Instruction Set Attribute registers – background information

A.7.1 The basic instruction set

A.7.2 General rules

A.7.3 Q flag support

A.7.4 MOV instructions

A.7.5 Non-MOV data-processing instructions

A.7.6 Multiply instructions

A.7.7 Branches

A.7.8 Load/store single instructions

A.7.9 Load/store multiple instructions

A.8 Instruction Set Attribute registers – details

A.8.1 Instruction Set Attributes Register0 (ID_ISAR0)

A.8.2 Instruction Set Attributes Register1 (ID_ISAR1)

A.8.3 Instruction Set Attributes Register2 (ID_ISAR2)

A.8.4 Instruction Set Attributes Register3 (ID_ISAR3)

A.8.5 Instruction Set Attributes Register3 (ID_ISAR4)

ARMv7-M infrastructure IDs

Legacy Instruction Mnemonics

C.1 Thumb instruction mnemonics

C.2 Pre-UAL pseudo-instruction NOP

Deprecated Features in ARMv7-M

Debug ITM and DWT packet protocol

E.1 Packet Types

E.1.1 Sync Packet

E.1.2 Overflow Packet

E.1.3 Timestamp Packet

E.1.4 Software Instrumentation Packet

E.1.5 Hardware Source Packet

E.1.6 Extension Packets

E.1.7 Reserved Encodings

E.1.8 Multiple Source Arbitration

E.2 DWT packet formats

E.2.1 Event Packets – Discriminator ID0

E.2.2 Exception Trace Packets – Discriminator ID1

E.2.3 PC Sample Packets – Discriminator ID2

E.2.4 Data Trace (Watchpoint) Packets – Discriminator ID8 to ID23

Packet format - data trace PC sampling

Packet format - data trace address offset

ARMv7-R differences

F.1 Endian support

F.2 Application level support

F.3 System level support

F.4 Debug support

Pseudocode definition

G.1 Instruction encoding diagrams and pseudocode

G.1.1 Pseudocode

G.2 Limitations of pseudocode

G.3 Data Types

G.3.1 General data type rules

G.3.2 Bitstrings

G.3.3 Integers

G.3.4 Reals

G.3.5 Booleans

G.3.6 Enumerations

G.3.7 Lists

G.3.8 Arrays

G.4 Expressions

G.4.1 General expression syntax

G.4.2 Operators and functions - polymorphism and prototypes

G.4.3 Precedence rules

G.5 Operators and built-in functions

G.5.1 Operations on generic types

Equality and non-equality testing

Conditional selection

G.5.2 Operations on booleans

G.5.3 Bitstring manipulation

Bitstring length and top bit

Bitstring concatenation and replication

Bitstring extraction

Logical operations on bitstrings

Bitstring count

Testing a bitstring for being all zero or all ones

Lowest and highest set bits of a bitstring

Zero-extension and sign-extension of bitstrings

Converting bitstrings to integers

G.5.4 Arithmetic

Unary plus, minus and absolute value

Addition and subtraction

Comparisons

Multiplication

Division and modulo

Square Root

Rounding and aligning

Scaling

Maximum and minimum

G.6 Statements and program structure

G.6.1 Simple statements

Assignments

Procedure calls

Return statements

UNDEFINED

UNPREDICTABLE

SEE...

IMPLEMENTATION_DEFINED

SUBARCHITECTURE_DEFINED

G.6.2 Compound statements

if ... then ... else ...

repeat ... until ...

while ... do

for ...

case ... of ...

Procedure and function definitions

G.6.3 Comments

G.7 Miscellaneous helper procedures and functions

G.7.1 ArchVersion()

G.7.2 BadReg()

G.7.3 BreakPoint()

G.7.4 CallSupervisor()

G.7.5 ConditionPassed()

G.7.6 Coproc_Accepted()

G.7.7 Coproc_DoneLoading()

G.7.8 Coproc_DoneStoring()

G.7.9 Coproc_GetOneWord()

G.7.10 Coproc_GetTwoWords()

G.7.11 Coproc_GetWordToStore()

G.7.12 Coproc_InternalOperation()

G.7.13 Coproc_SendLoadedWord()

G.7.14 Coproc_SendOneWord()

G.7.15 Coproc_SendTwoWords()

G.7.16 DataMemoryBarrier()

G.7.17 DataSynchronizationBarrier()

G.7.18 EncodingSpecificOperations()

G.7.19 GenerateCoprocessorException()

G.7.20 GenerateIntegerZeroDivide()

G.7.21 Hint_Debug()

G.7.22 Hint_PreloadData()

G.7.23 Hint_PreloadDataForWrite()

G.7.24 Hint_PreloadInstr()

G.7.25 Hint_SendEvent()

G.7.26 Hint_Yield()

G.7.27 InstructionSynchronizationBarrier()

G.7.28 IntegerZeroDivideTrappingEnabled()

G.7.29 ProcessorID()

G.7.30 SetPending()

G.7.31 ThisInstr()

Pseudocode Index

H.1 Pseudocode operators and keywords

H.2 Pseudocode functions and procedures

Register Index

I.1 ARM core registers

I.2 Memory mapped system registers

I.3 Memory mapped debug registers

Glossary

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc