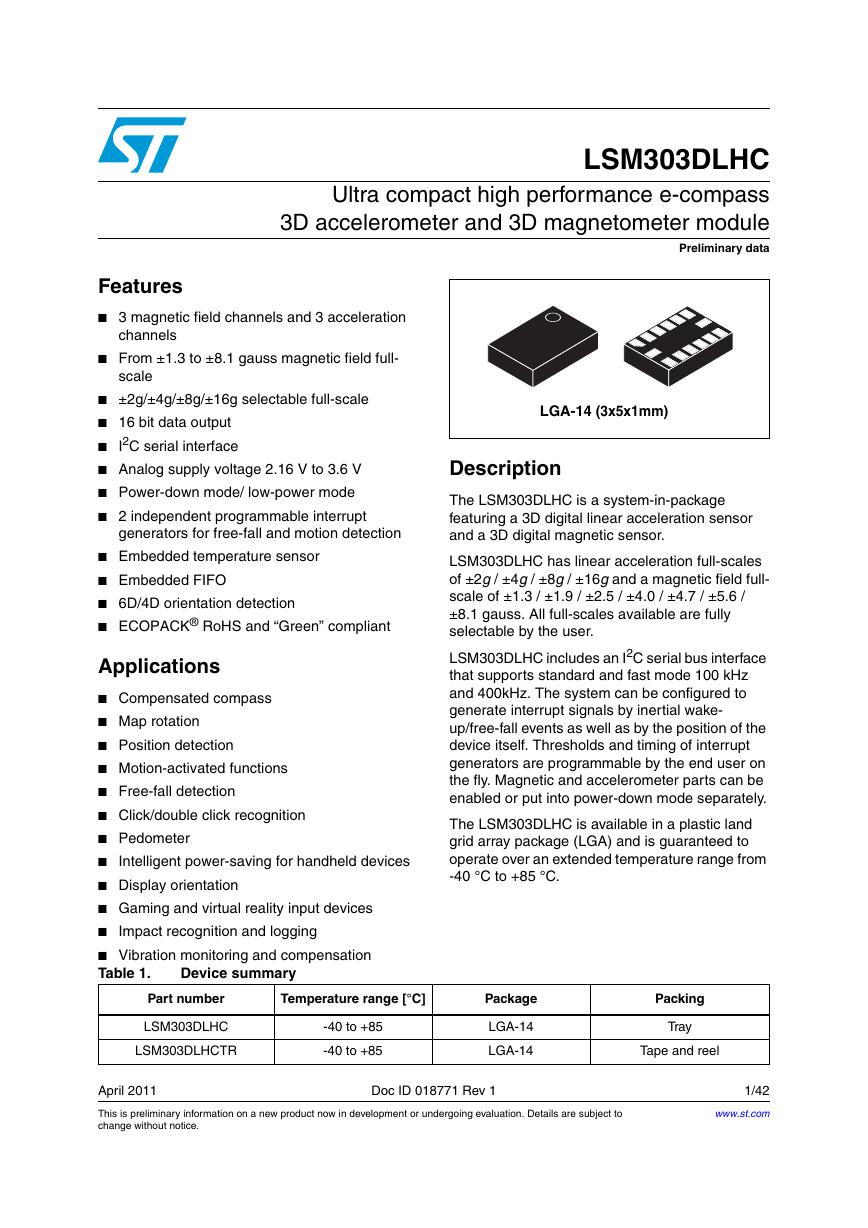

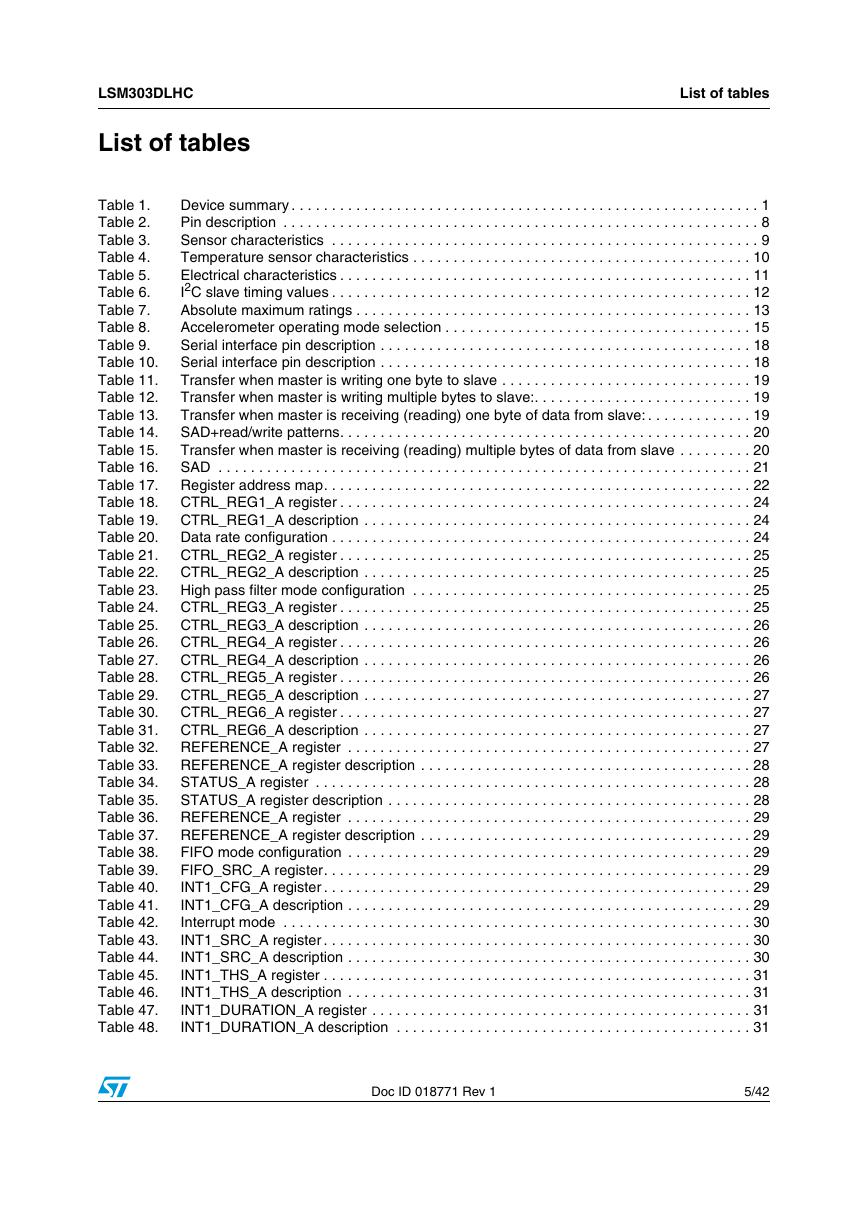

Table 1. Device summary

1 Block diagram and pin description

1.1 Block diagram

Figure 1. Block diagram

1.2 Pin description

Figure 2. Pin connection

Table 2. Pin description

2 Module specifications

2.1 Sensor characteristics

Table 3. Sensor characteristics

2.2 Temperature sensor characteristics

Table 4. Temperature sensor characteristics

2.3 Electrical characteristics

Table 5. Electrical characteristics

2.4 Communication interfaces characteristics

2.4.1 Sensor I2C - inter IC control interface

Table 6. I2C slave timing values

Figure 3. I2C slave timing diagram

2.5 Absolute maximum ratings

Table 7. Absolute maximum ratings

2.6 Terminology

2.6.1 Linear accel eration sensitivity

2.6.2 Zero-g level

3 Functionality

Table 8. Accelerometer operating mode selection

3.1 Factory calibration

4 Application hints

Figure 4. LSM303DLHC electrical connection

4.1 capacitors

4.2 Pull-up resistors

4.3 Digital interface power supply

4.4 Soldering information

4.5 High current wiring effects

5 Digital interfaces

Table 9. Serial interface pin description

5.1 I2C serial interface

Table 10. Serial interface pin description

5.1.1 I2C operation

Table 11. Transfer when master is writing one byte to slave

Table 12. Transfer when master is writing multiple bytes to slave:

Table 13. Transfer when master is receiving (reading) one byte of data from slave:

5.1.2 Linear acceleration digital interface

Table 14. SAD+Read/Write patterns

Table 15. Transfer when master is receiving (reading) multiple bytes of data from slave

5.1.3 Magnetic field digital interface

Table 16. SAD

6 Register mapping

Table 17. Register address map

7 Register description

7.1 Linear acceleration register description

7.1.1 CTRL_REG1_A (20h)

Table 18. CTRL_REG1_A register

Table 19. CTRL_REG1_A description

Table 20. Data rate configuration

7.1.2 CTRL_REG2_A (21h)

Table 21. CTRL_REG2_A register

Table 22. CTRL_REG2_A description

Table 23. High pass filter mode configuration

7.1.3 CTRL_REG3_A (22h)

Table 24. CTRL_REG3_A register

Table 25. CTRL_REG3_A description

7.1.4 CTRL_REG4_A (23h)

Table 26. CTRL_REG4_A register

Table 27. CTRL_REG4_A description

7.1.5 CTRL_REG5_A (24h)

Table 28. CTRL_REG5_A register

Table 29. CTRL_REG5_A description

7.1.6 CTRL_REG6_A (25h)

Table 30. CTRL_REG6_A register

Table 31. CTRL_REG6_A description

7.1.7 REFERENCE/DATACAPTURE_A (26h)

Table 32. REFERENCE_A register

Table 33. REFERENCE_A register description

7.1.8 STATUS_REG_A (27h)

Table 34. STATUS_A register

Table 35. STATUS_A register description

7.1.9 OUT_X_L_A (28h), OUT_X_H_A (29h)

7.1.10 OUT_Y_L_A (2Ah), OUT_Y_H_A (2Bh)

7.1.11 OUT_Z_L_A (2Ch), OUT_Z_H_A (2Dh)

7.1.12 FIFO_CTRL_REG_A (2Eh)

Table 36. REFERENCE_A register

Table 37. REFERENCE_A register description

Table 38. FIFO mode configuration

7.1.13 FIFO_SRC_REG_A (2Fh)

Table 39. FIFO_SRC_A register

7.1.14 INT1_CFG_A (30h)

Table 40. INT1_CFG_A register

Table 41. INT1_CFG_A description

Table 42. Interrupt mode

7.1.15 INT1_SRC_A (31h)

Table 43. INT1_SRC_A register

Table 44. INT1_SRC_A description

7.1.16 INT1_THS_A (32h)

Table 45. INT1_THS_A register

Table 46. INT1_THS_A description

7.1.17 INT1_DURATION_A (33h)

Table 47. INT1_DURATION_A register

Table 48. INT1_DURATION_A description

7.1.18 INT2_CFG_A (34h)

Table 49. INT2_CFG_A register

Table 50. INT2_CFG_A description

Table 51. Interrupt mode

7.1.19 INT2_SRC_A (35h)

Table 52. INT2_SRC_A register

Table 53. INT2_SRC_A description

7.1.20 INT2_THS_A (36h)

Table 54. INT2_THS_A register

Table 55. INT2_THS_A description

7.1.21 INT2_DURATION_A (37h)

Table 56. INT2_DURATION_A register

Table 57. INT2_DURATION_A description

7.1.22 CLICK_CFG_A (38h)

Table 58. CLICK_CFG_A register

Table 59. CLICK_CFG_A description

7.1.23 CLICK_SRC_A (39h)

Table 60. CLICK_SRC_A register

Table 61. CLICK_SRC_A description

7.1.24 CLICK_THS_A (3Ah)

Table 62. CLICK_THS_A register

Table 63. CLICK_SRC_A description

7.1.25 TIME_LIMIT_A (3Bh)

Table 64. TIME_LIMIT_A register

Table 65. TIME_LIMIT_A description

7.1.26 TIME_LATENCY_A (3Ch)

Table 66. TIME_LATENCY_A register

Table 67. TIME_LATENCY_A description

7.1.27 TIME WINDOW_A (3Dh)

Table 68. TIME_WINDOW_A register

Table 69. TIME_WINDOW_A description

7.2 Magnetic field sensing register description

7.2.1 CRA_REG_M (00h)

Table 70. CRA_REG_M register

Table 71. CRA_REG_M description

Table 72. Data rate configurations

7.2.2 CRB_REG_M (01h)

Table 73. CRA_REG register

Table 74. CRA_REG description

Table 75. Gain setting

7.2.3 MR_REG_M (02h)

Table 76. MR_REG

Table 77. MR_REG description

Table 78. Magnetic sensor operating mode

7.2.4 OUT_X_H_M (03), OUT_X_LH_M (04h)

7.2.5 OUT_Z_H_M (05), OUT_Z_L_M (06h)

7.2.6 OUT_Y_H_M (07), OUT_Y_L_M (08h)

7.2.7 SR_REG_M (09h)

Table 79. SR register

Table 80. SR register description

7.2.8 IR_REG_M (0Ah/0Bh/0Ch)

Table 81. IRA_REG_M

Table 82. IRB_REG_M

Table 83. IRC_REG_M

7.2.9 TEMP_OUT_H_M (31h), TEMP_OUT_L_M (32h)

Table 84. TEMP_OUT_H_M register

Table 85. TEMP_OUT_L_M register

Table 86. TEMP_OUT resolution

8 Package information

Figure 5. LGA-14: mechanical data and package dimensions

9 Revision history

Table 87. Document revision history

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf

V2版本原理图(Capacitive-Fingerprint-Reader-Schematic_V2).pdf 摄像头工作原理.doc

摄像头工作原理.doc VL53L0X简要说明(En.FLVL53L00216).pdf

VL53L0X简要说明(En.FLVL53L00216).pdf 原理图(DVK720-Schematic).pdf

原理图(DVK720-Schematic).pdf 原理图(Pico-Clock-Green-Schdoc).pdf

原理图(Pico-Clock-Green-Schdoc).pdf 原理图(RS485-CAN-HAT-B-schematic).pdf

原理图(RS485-CAN-HAT-B-schematic).pdf File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf

File:SIM7500_SIM7600_SIM7800 Series_SSL_Application Note_V2.00.pdf ADS1263(Ads1262).pdf

ADS1263(Ads1262).pdf 原理图(Open429Z-D-Schematic).pdf

原理图(Open429Z-D-Schematic).pdf 用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf

用户手册(Capacitive_Fingerprint_Reader_User_Manual_CN).pdf CY7C68013A(英文版)(CY7C68013A).pdf

CY7C68013A(英文版)(CY7C68013A).pdf TechnicalReference_Dem.pdf

TechnicalReference_Dem.pdf