用 CPU 配置 Altera 公司的 FPGA

一. 概 述

目前很多产品都广泛用了 FPGA,虽然品种不同,但编程方式几乎都一样:利用专用的

EPROM 对 FPGA 进行配置。专用的 EPROM 价格不便宜,且大不跟上都是一次性 OPT 方式

编程。一旦更改 FPGA 设计,代价不小。 为了进一步降低产品的成本和升级成本,可

以考虑利用板上现有 CPU 子系统中空闲的 ROM 空间存放 FPGA 的配置数据,并由 CPU

模拟专用 EPROM 对 FPGA 进行配置。 本文将以 PowerPC860 和 EP1K30 为例,讲解如何

利用 CPU 来配置 FPGA。

CPU 配置 FPGA 的优点

与 Configuration EPROM 方式相比本设计有如下优点:

1. 降低硬件成本——省去了 FPGA 专用 EPROM 的成本,而几乎不增加其他成本。以 A

LTERA 的 10K 系列为例,板上至少要配一片以上的 EPC1,每片 EPC1 的价格要几十元,

容量 1M 位。提供 1Mb 的存储空间,对于大部分单板来说(如 860 系统的单板),是

不需要增加硬件的。即使增加 1Mb 存储空间,通用存储器也会比 FPGA 专用 EPROM 便

宜。

2. 可多次编程——FPGA 专用 EPROM 几乎都是 OTP,一旦更换 FPGA 版本,旧版本的

并不便宜的 EPROM 只能丢弃。如果使用本设计对 FPGA 配置,选用可擦除的通用存储

器保存 FPGA 的编程数据,更换 FPGA 版本,无须付出任何硬件代价。这也是降低硬件

成本的一个方面。

3. 实现真正"现场可编程"--FPGA 的特点就是"现场可编程",只有使用 CPU 对 FPGA

编程才能体现这一特点。如果设计周全的话,单板上的 FPGA 可以做到在线升级。

4. 减少生产工序--省去了对"FPGA 专用 EPROM"烧结的工序,对提高生产率,降低生

产成本等均有好处。对于双面再流焊的单板,更可省去手工补焊 DIP 器件的工序。

当然,与 Configuration EPROM 方式相比也有一些需要注意的的地方:

�

1. 需要 CPU 提供 5 根 I/O 线--一般来说,这并不困难。对于 MPC860 一类的 CPU 来

说,区区 5 根 I/O 线是不成问题的。即使是某些设计中实在没有多余的 I/O 供配置使

用,也可通过板上的 PLD 扩展。虽然这样做可能会增加成本,但获得的真正"现场可

编程"的功能是非常宝贵的。

2. CPU 的 Boot 应不依赖于 FPGA--这在单板设计时需要特别考虑的。由于 CPU 对 FP

GA 进行配置所需的资源很少,这一点比较容易做到。

设计摘要

本设计严格按照 FPGA 的 PS 配置流程进行,并在配置过程中始终监测工作状态,在完

善的软件配合下,可纠正如上电次序导致配置不正常等错误。因此,采用此方法对 F

PGA 进行配置,性能将优于 Configuration EPROM 方式。

本设计是利用板上现有 CPU 子系统中空闲的 ROM 空间存放 FPGA 的配置数据,并由 CP

U 模拟专用 EPROM 对 FPGA 进行配置,以降低硬件成本并实现 FPGA 的在线升级。

本设计已在 MPC860 和 EP1K30 环境下完成验证,适用于有 5 个多余 I/O 的 CPU 对 Alt

era FPGA 的配置。

参考资料

ALTERA:AN-116 Configuring SRAM-Based LUT Devices

ALTERA: ACEX 1K Programmable Logic Device Family

二. 硬件设计

1.配置基本原理

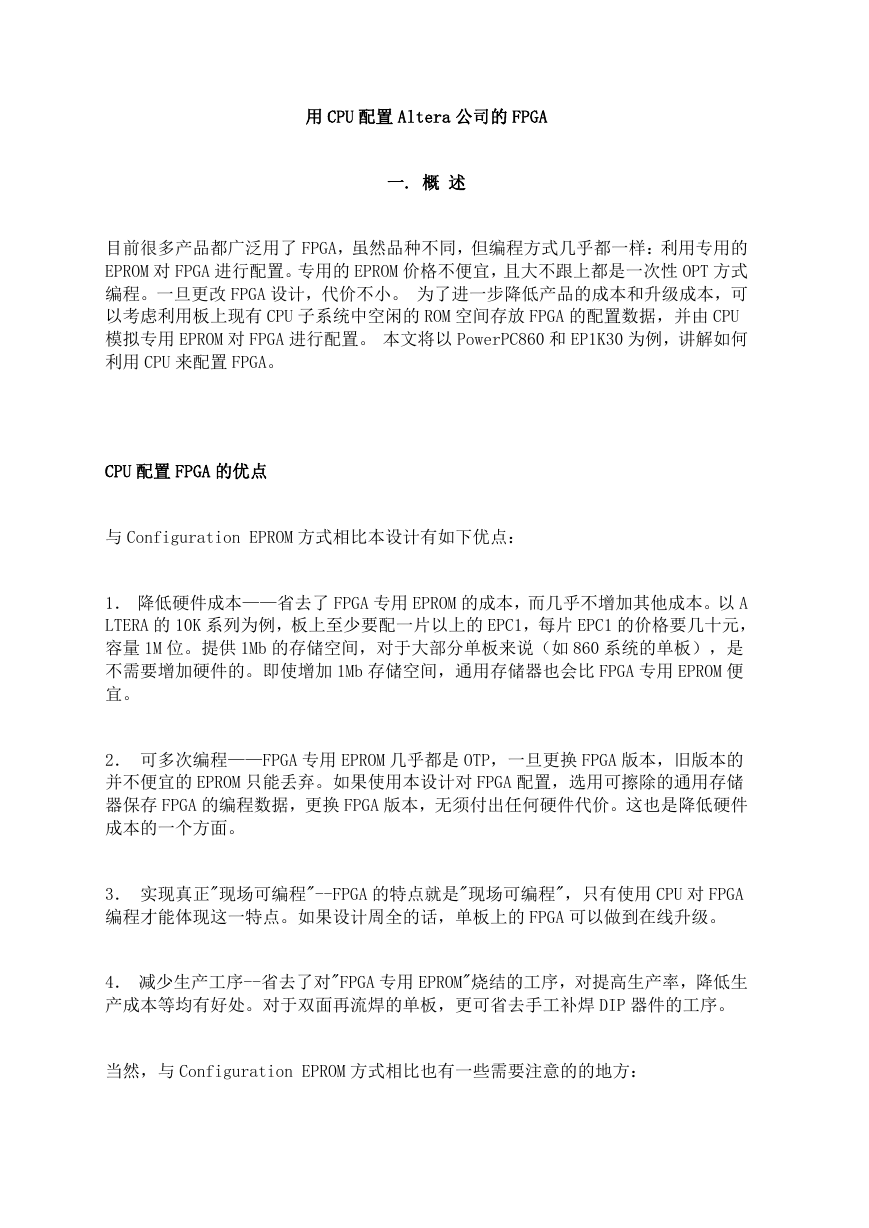

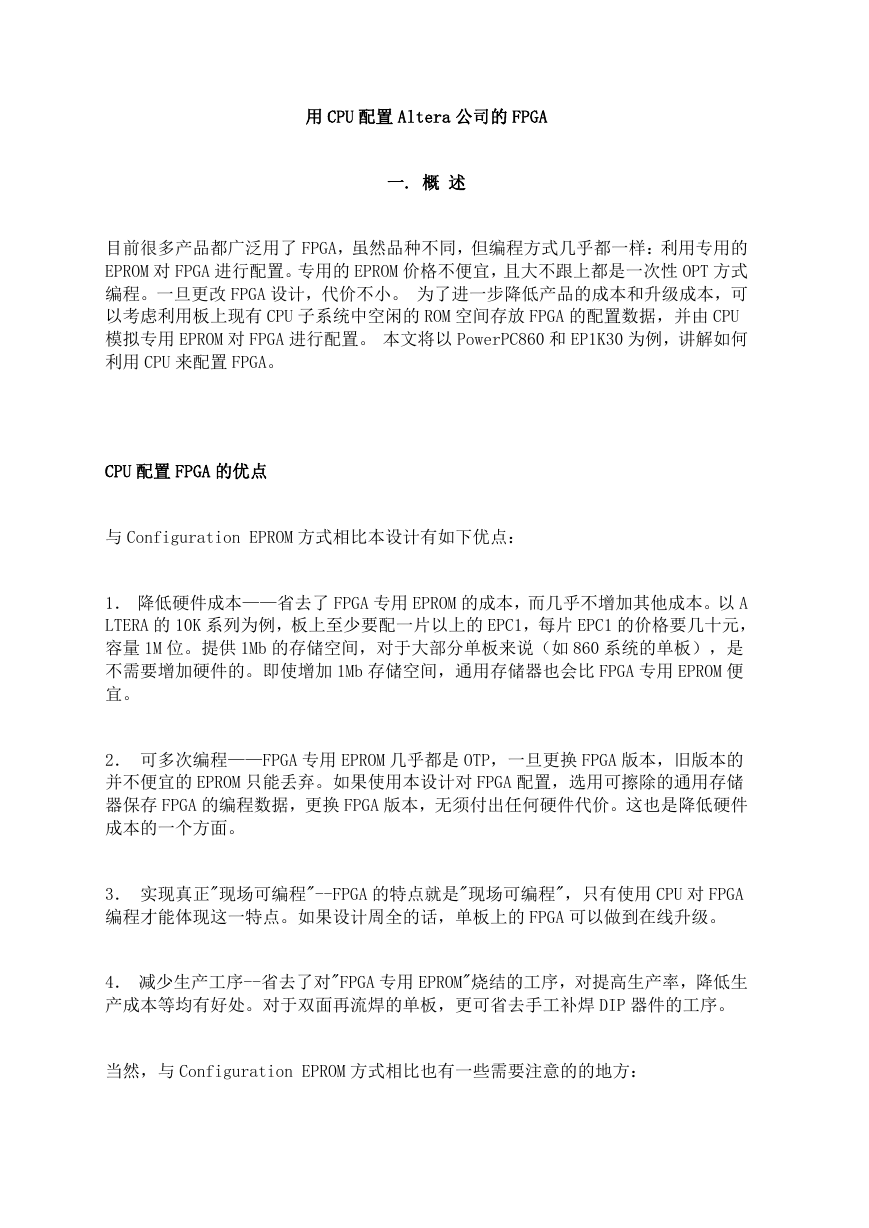

RAM-Based FPGA 由于 SRAM 工艺的特点,掉电后数据会消失。因此,每次系统上电后,均需对 FPGA 进行配

置。对于 Altera 的 FPGA,配置方法可分为:专用的 EPROM (Configuration EPROM)、PS(Passive serial 无

源串行)、PPS(Passive parallel synchronous 无源同步并行)、PPA(Passive parallel asynchronous 无源异步并

�

行)、JTAG(不是所有器件都支持)。

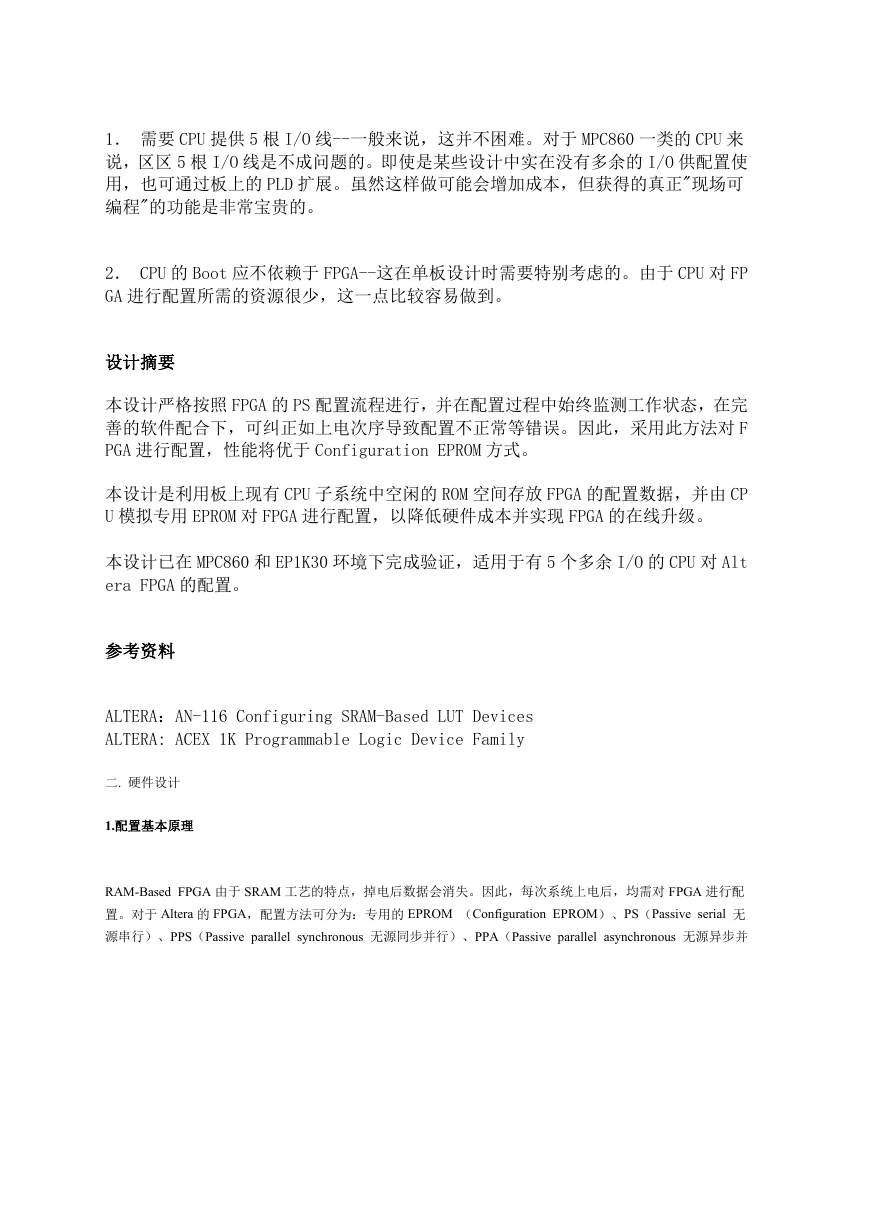

本设计采用 PS 方式对 FPGA 进行配置,是基于如下几个方面的考虑:

1. PS 方式连线最简单

2. 与 Configuration EPROM 方式可以兼容(MSEL0、1 设置不变)

3. 与并行配置相比,误操作的几率小,可靠性高

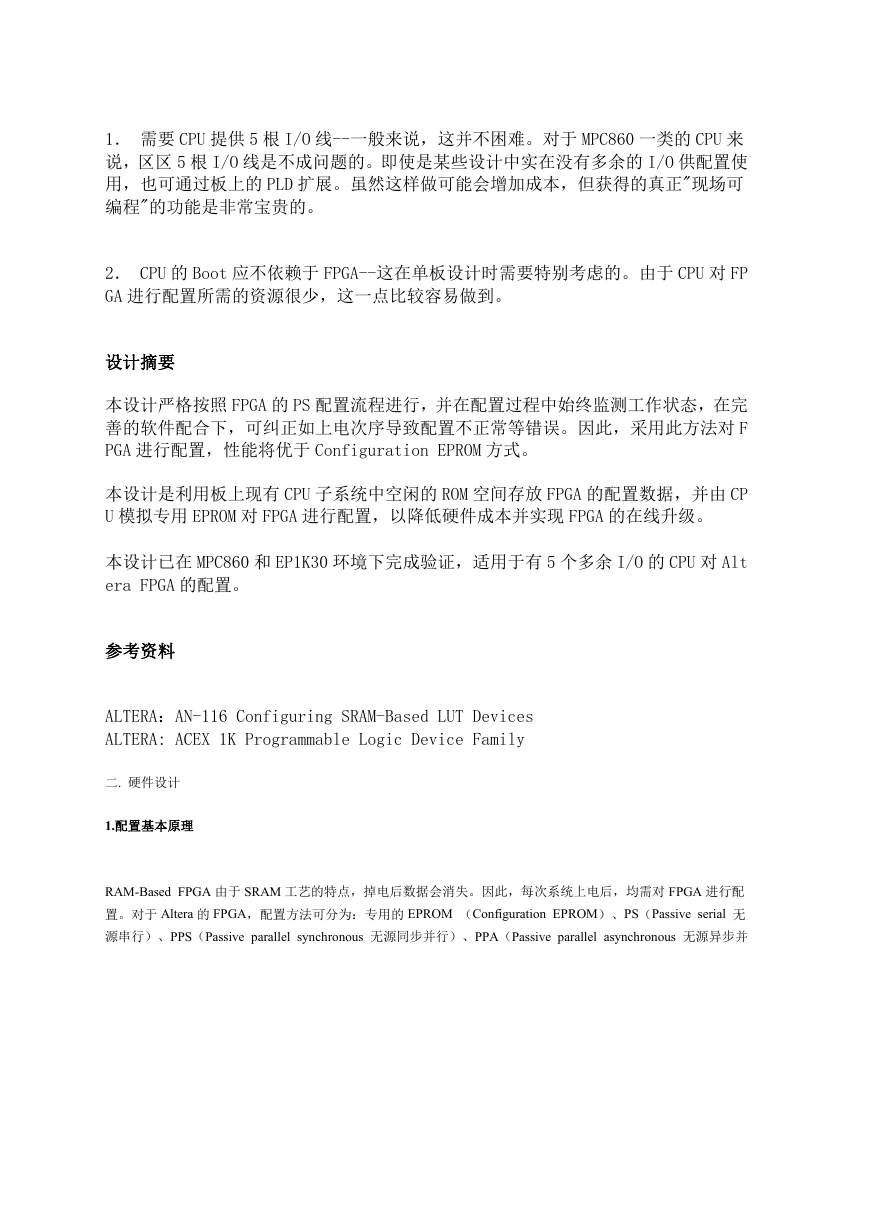

只需利用 CPU 的 5 个 I/O 线,就可按图 2 所指示的时序对 FPGA 进行 PS 方式的配置。

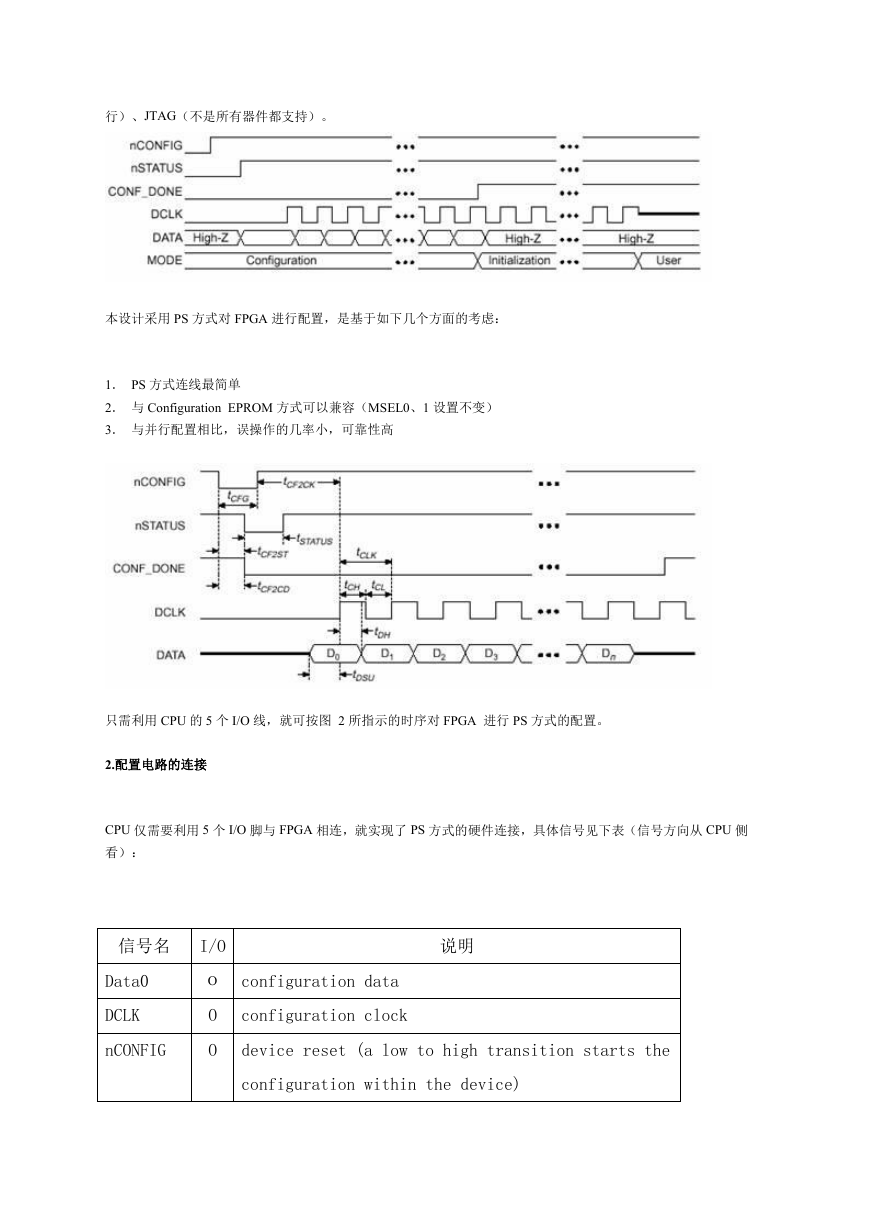

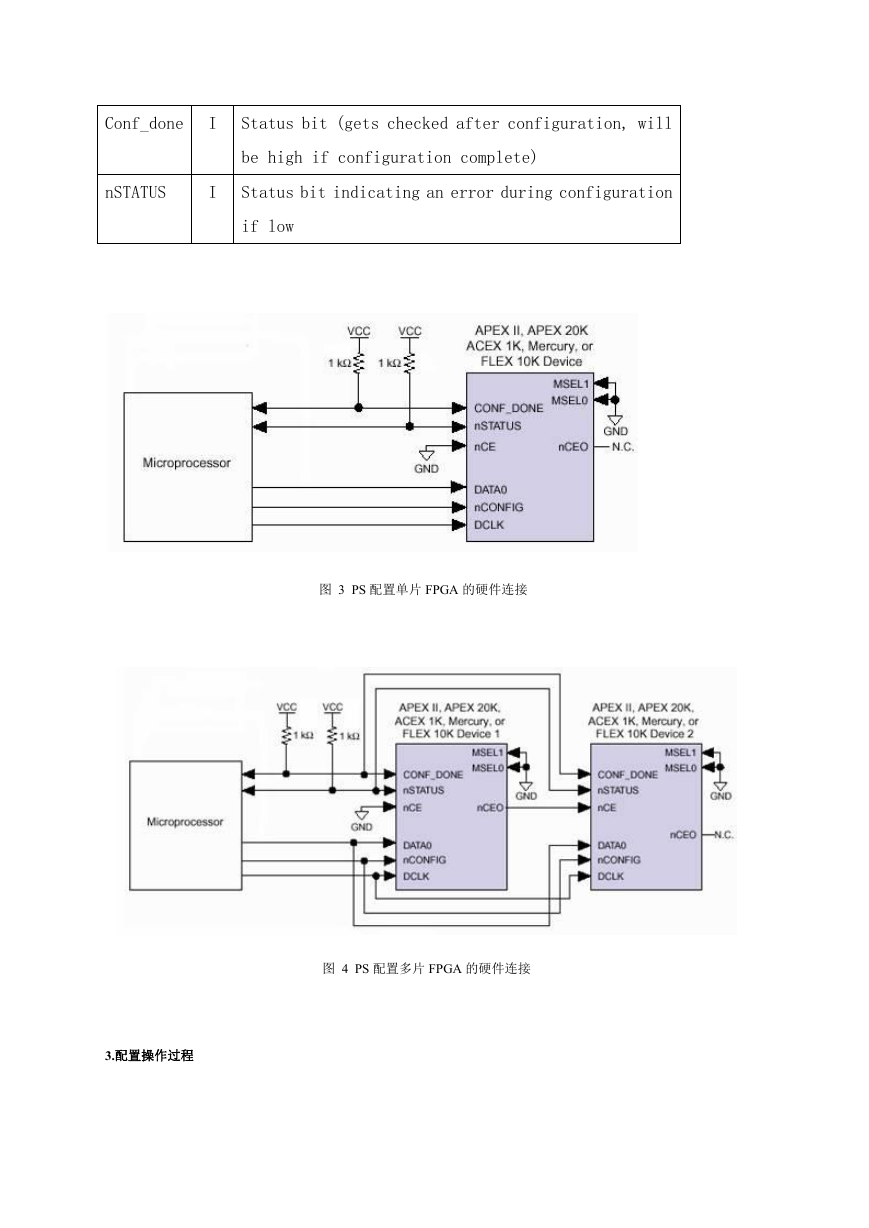

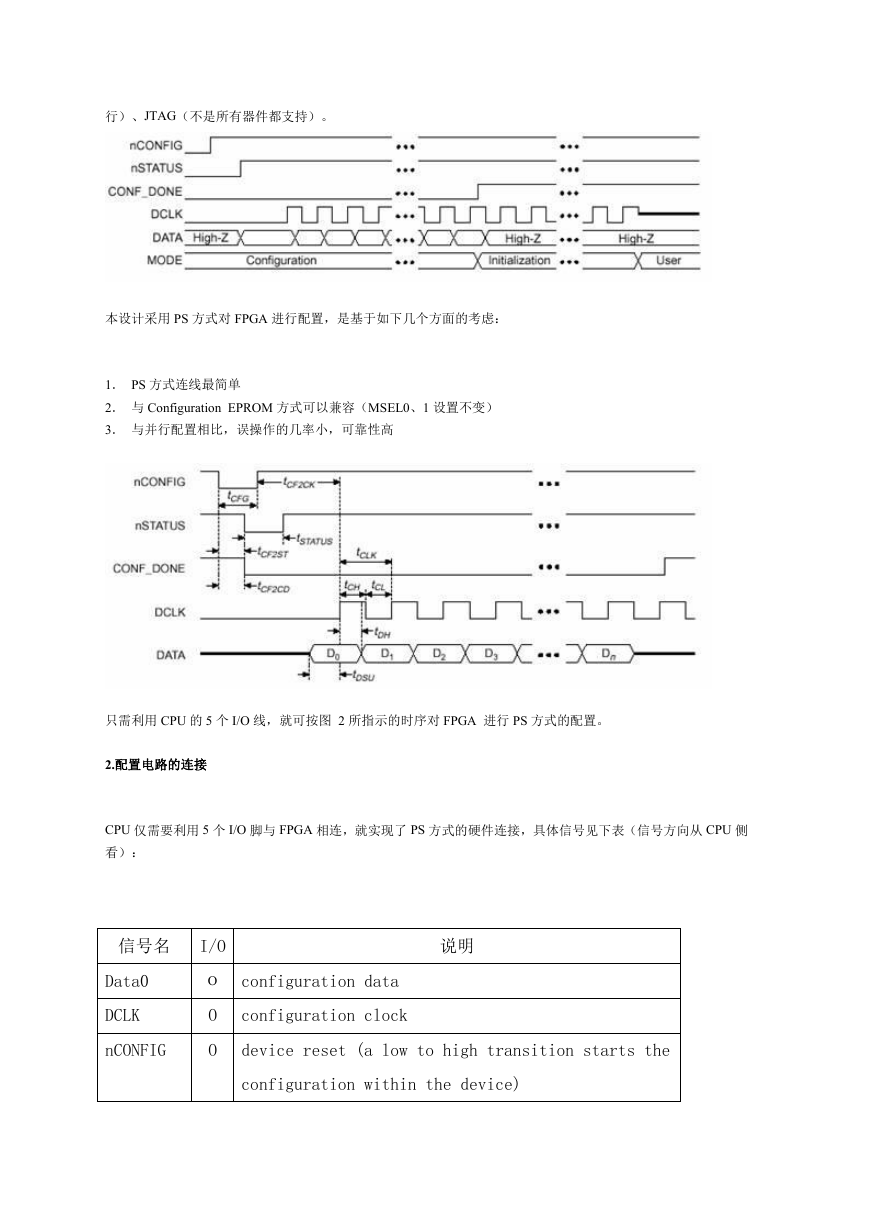

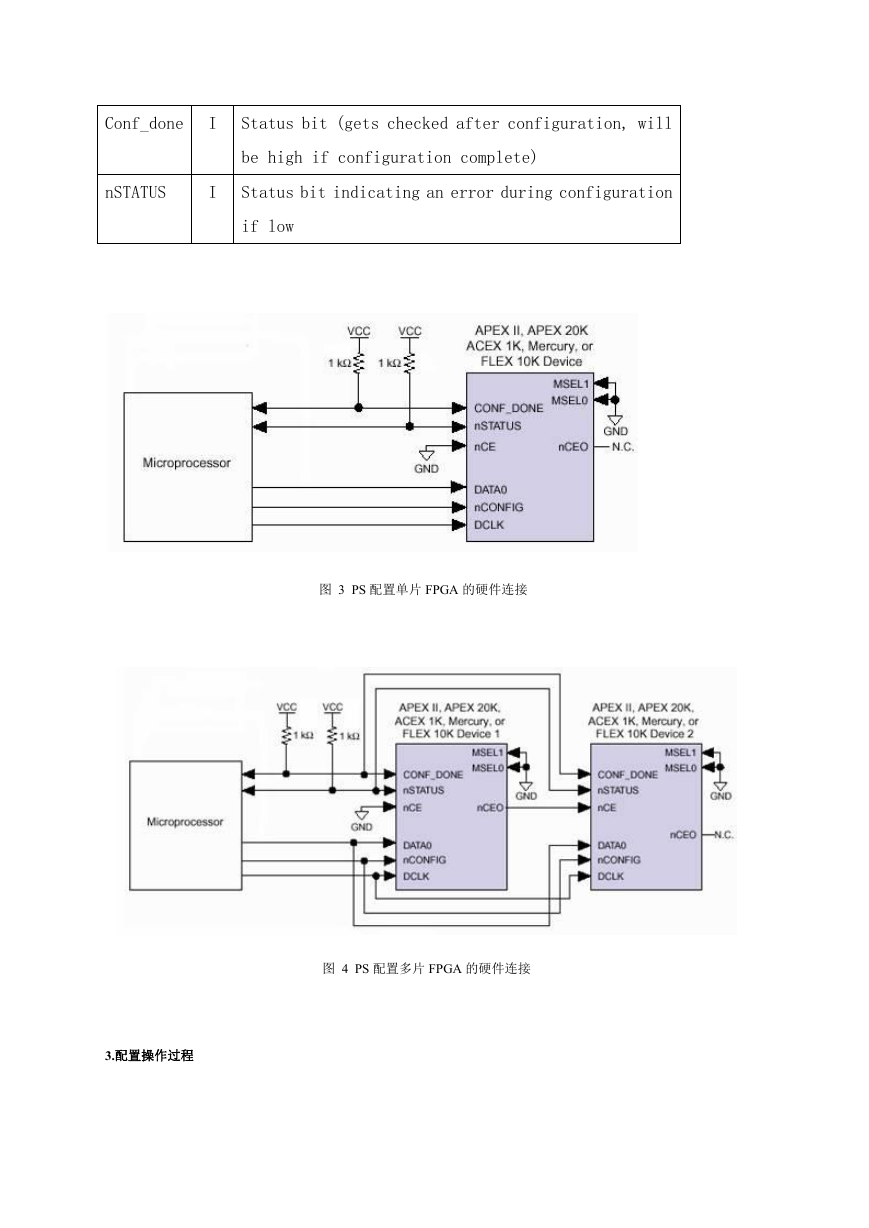

2.配置电路的连接

CPU 仅需要利用 5 个 I/O 脚与 FPGA 相连,就实现了 PS 方式的硬件连接,具体信号见下表(信号方向从 CPU 侧

看):

信号名 I/O

Data0

DCLK

nCONFIG

O

O

O

说明

configuration data

configuration clock

device reset (a low to high transition starts the

configuration within the device)

�

Conf_done

I

Status bit (gets checked after configuration, will

be high if configuration complete)

nSTATUS

I

Status bit indicating an error during configuration

if low

图 3 PS 配置单片 FPGA 的硬件连接

图 4 PS 配置多片 FPGA 的硬件连接

3.配置操作过程

�

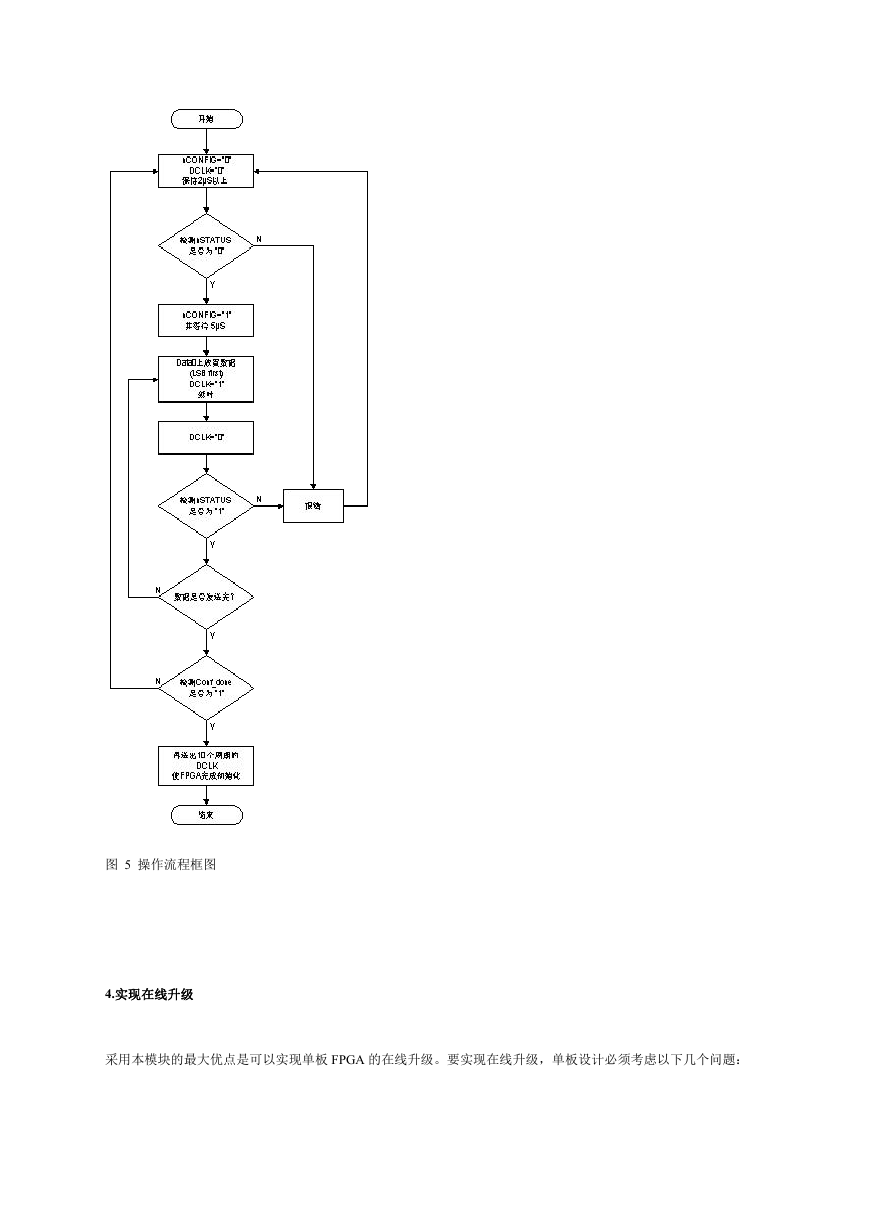

CPU 按下列步骤操作 I/O 口线,即可完成对 FPGA 的配置:

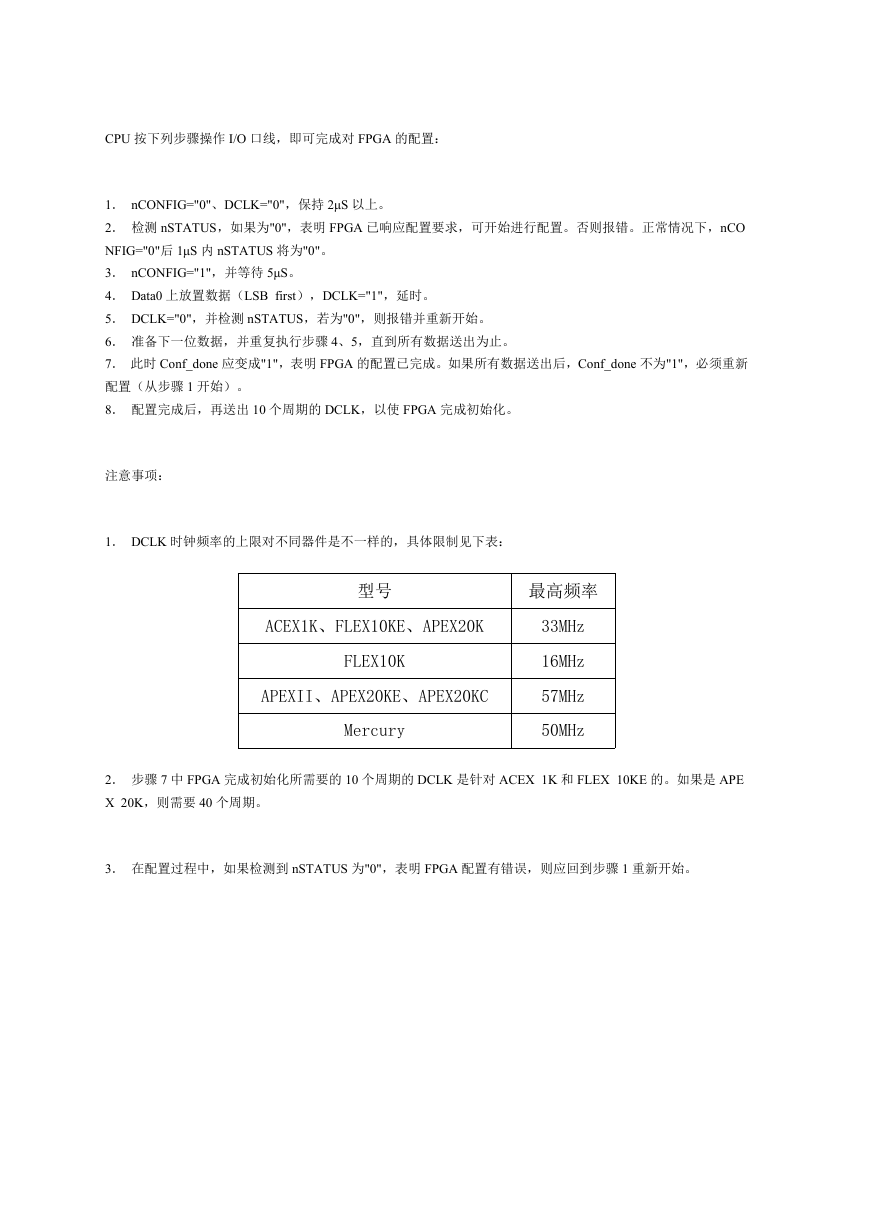

1. nCONFIG="0"、DCLK="0",保持 2μS 以上。

2. 检测 nSTATUS,如果为"0",表明 FPGA 已响应配置要求,可开始进行配置。否则报错。正常情况下,nCO

NFIG="0"后 1μS 内 nSTATUS 将为"0"。

3. nCONFIG="1",并等待 5μS。

4. Data0 上放置数据(LSB first),DCLK="1",延时。

5. DCLK="0",并检测 nSTATUS,若为"0",则报错并重新开始。

6. 准备下一位数据,并重复执行步骤 4、5,直到所有数据送出为止。

7. 此时 Conf_done 应变成"1",表明 FPGA 的配置已完成。如果所有数据送出后,Conf_done 不为"1",必须重新

配置(从步骤 1 开始)。

8. 配置完成后,再送出 10 个周期的 DCLK,以使 FPGA 完成初始化。

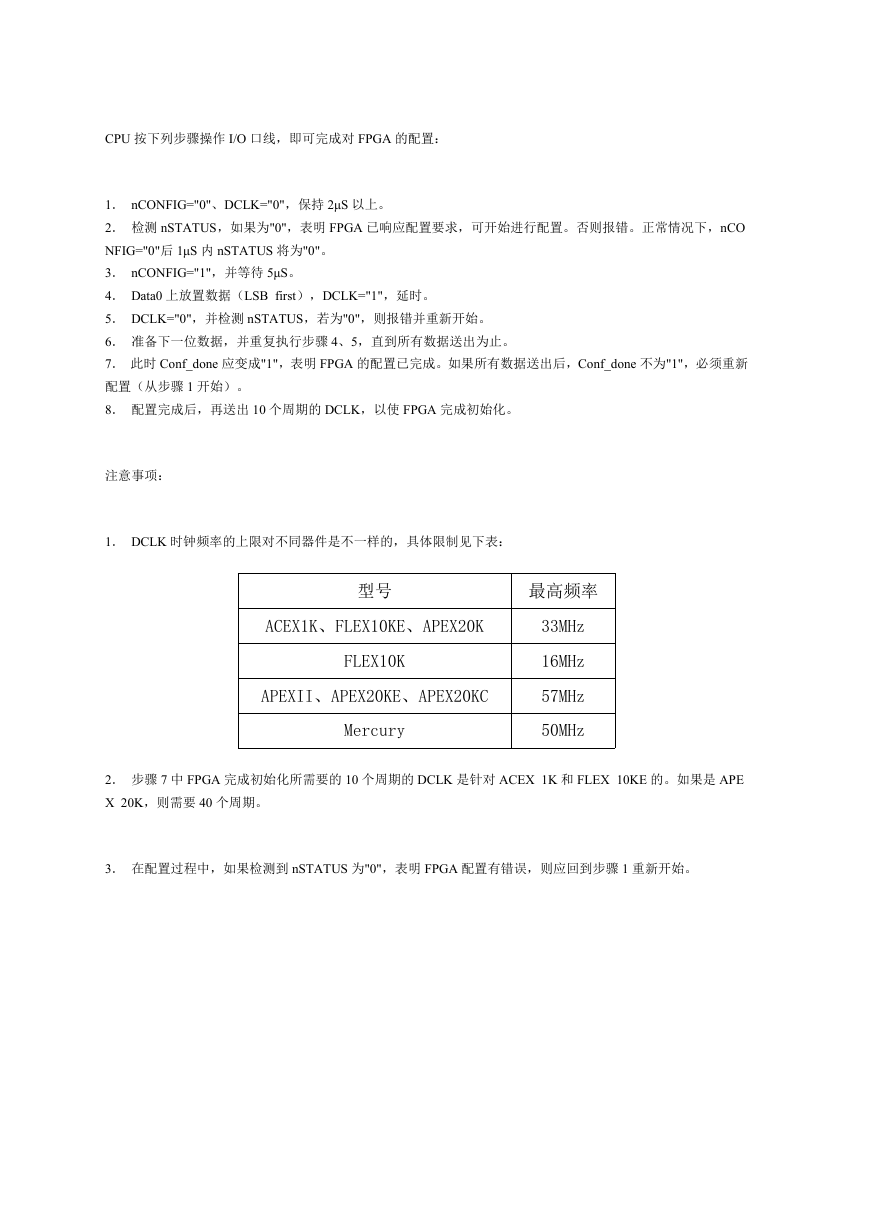

注意事项:

1. DCLK 时钟频率的上限对不同器件是不一样的,具体限制见下表:

型号

最高频率

ACEX1K、FLEX10KE、APEX20K

FLEX10K

APEXII、APEX20KE、APEX20KC

Mercury

33MHz

16MHz

57MHz

50MHz

2. 步骤 7 中 FPGA 完成初始化所需要的 10 个周期的 DCLK 是针对 ACEX 1K 和 FLEX 10KE 的。如果是 APE

X 20K,则需要 40 个周期。

3. 在配置过程中,如果检测到 nSTATUS 为"0",表明 FPGA 配置有错误,则应回到步骤 1 重新开始。

�

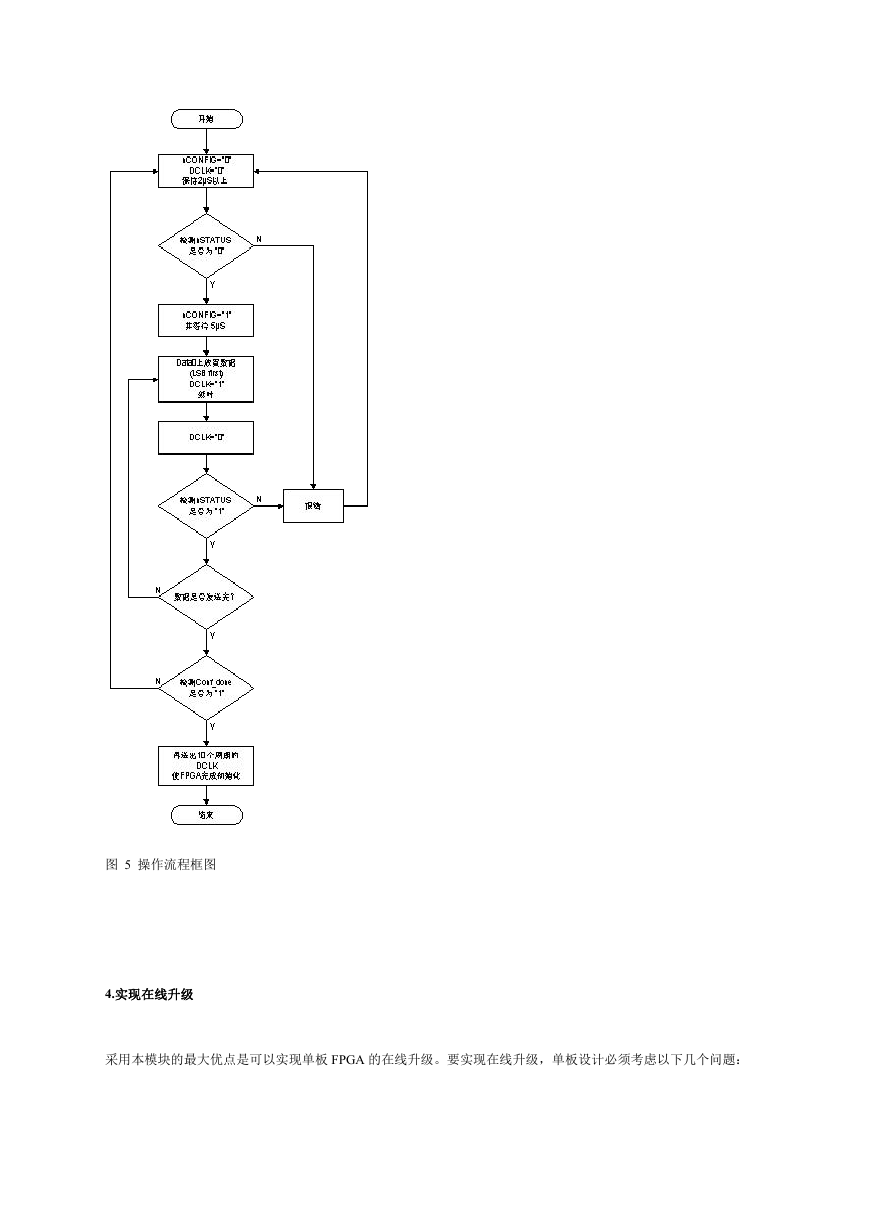

图 5 操作流程框图

4.实现在线升级

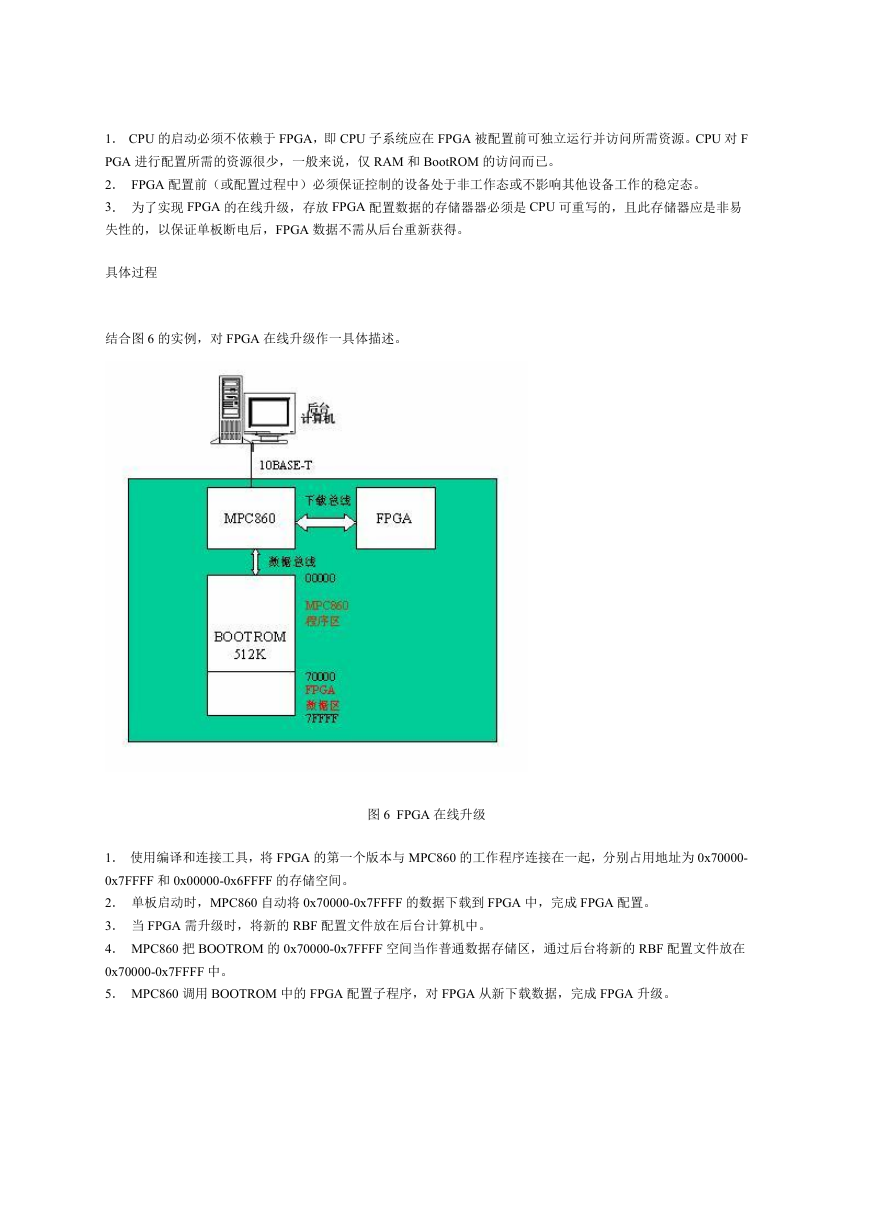

采用本模块的最大优点是可以实现单板 FPGA 的在线升级。要实现在线升级,单板设计必须考虑以下几个问题:

�

1. CPU 的启动必须不依赖于 FPGA,即 CPU 子系统应在 FPGA 被配置前可独立运行并访问所需资源。CPU 对 F

PGA 进行配置所需的资源很少,一般来说,仅 RAM 和 BootROM 的访问而已。

2. FPGA 配置前(或配置过程中)必须保证控制的设备处于非工作态或不影响其他设备工作的稳定态。

3. 为了实现 FPGA 的在线升级,存放 FPGA 配置数据的存储器器必须是 CPU 可重写的,且此存储器应是非易

失性的,以保证单板断电后,FPGA 数据不需从后台重新获得。

具体过程

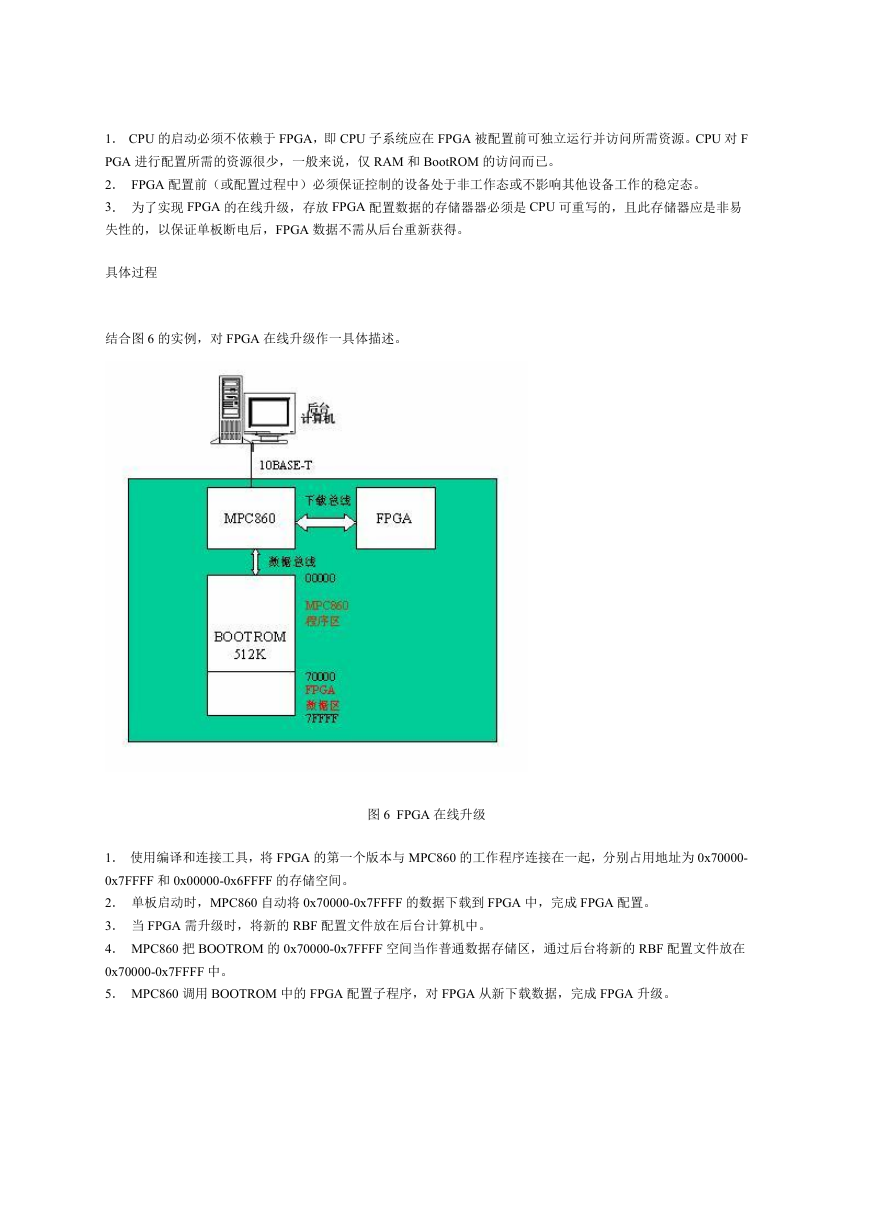

结合图 6 的实例,对 FPGA 在线升级作一具体描述。

图 6 FPGA 在线升级

1. 使用编译和连接工具,将 FPGA 的第一个版本与 MPC860 的工作程序连接在一起,分别占用地址为 0x70000-

0x7FFFF 和 0x00000-0x6FFFF 的存储空间。

2. 单板启动时,MPC860 自动将 0x70000-0x7FFFF 的数据下载到 FPGA 中,完成 FPGA 配置。

3. 当 FPGA 需升级时,将新的 RBF 配置文件放在后台计算机中。

4. MPC860 把 BOOTROM 的 0x70000-0x7FFFF 空间当作普通数据存储区,通过后台将新的 RBF 配置文件放在

0x70000-0x7FFFF 中。

5. MPC860 调用 BOOTROM 中的 FPGA 配置子程序,对 FPGA 从新下载数据,完成 FPGA 升级。

�

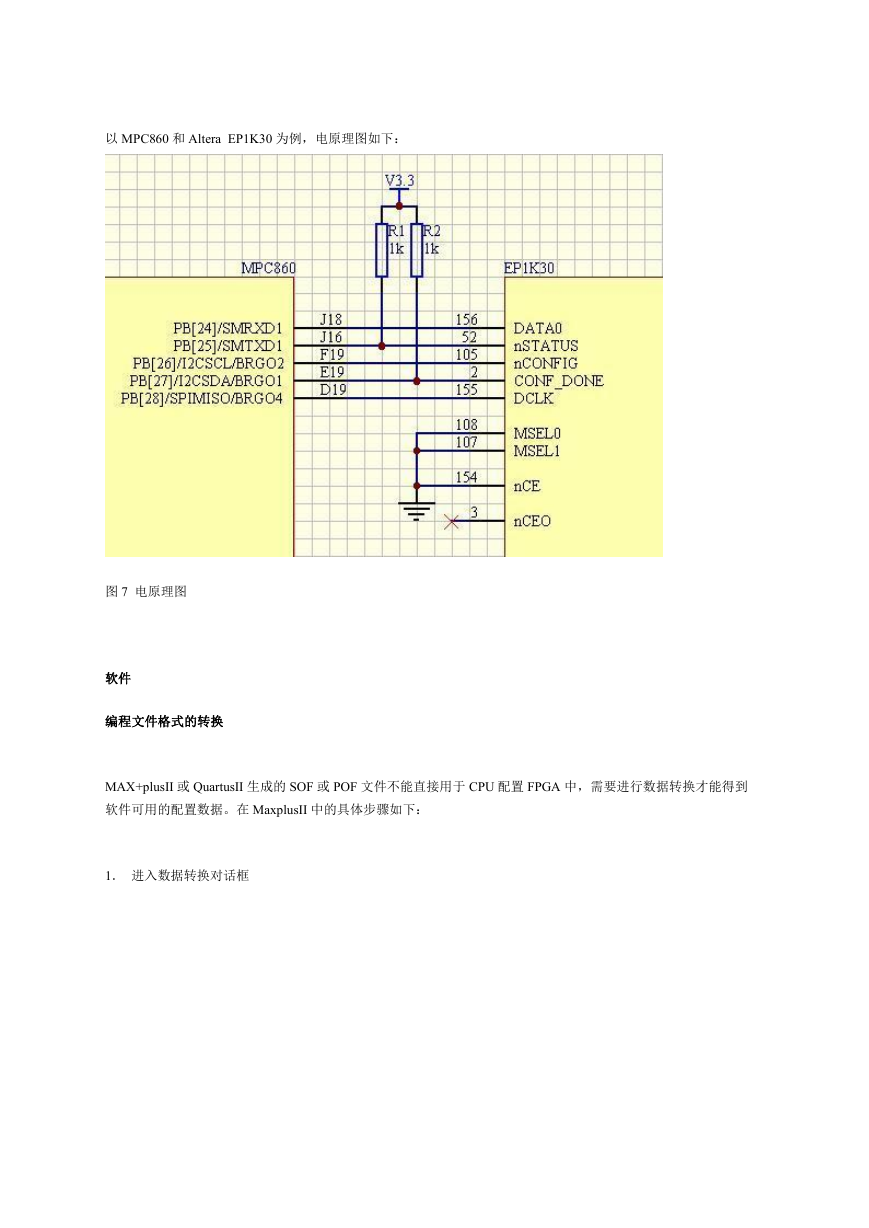

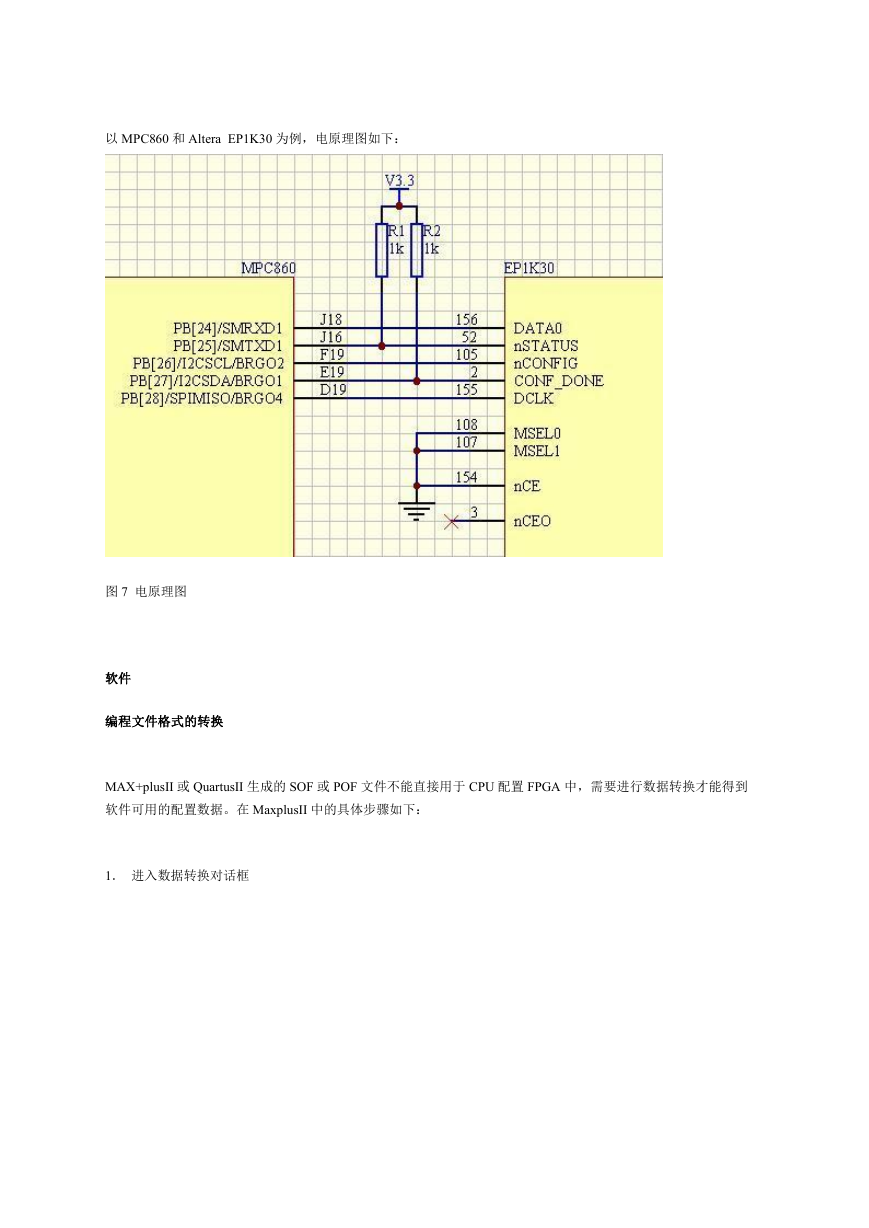

以 MPC860 和 Altera EP1K30 为例,电原理图如下:

图 7 电原理图

软件

编程文件格式的转换

MAX+plusII 或 QuartusII 生成的 SOF 或 POF 文件不能直接用于 CPU 配置 FPGA 中,需要进行数据转换才能得到

软件可用的配置数据。在 MaxplusII 中的具体步骤如下:

1. 进入数据转换对话框

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc