2012 年秋《模拟电子技术基础》课程设计报告

模拟电子技术课程

设计报告

学校名称:

青岛大学

学院名称:

自动化工程学院

专业班级:

学

姓

号:

名:

10 级电子 2 班

201040600539

生兆东

2012 年 9 月 17 日

1

�

2012 年秋《模拟电子技术基础》课程设计报告

半导体三极管 β 值测量仪设计报告

摘要: 设计制作一个自动测量三极管直流放大系数 β值范围的装置。

一、设计内容及基本要求:

1、对被测 NPN 型三极管值分三档;

2、β值的范围分别为 80~120 及 120~160,160~200 对应的分档编号分别是 1、

2、3;待测三极管为空时显示 0,超过 200 显示 4。

3、用数码管显示 β值的档次;

4、 用数码管显示 β的值。二、

系统方案设计,比较与论证

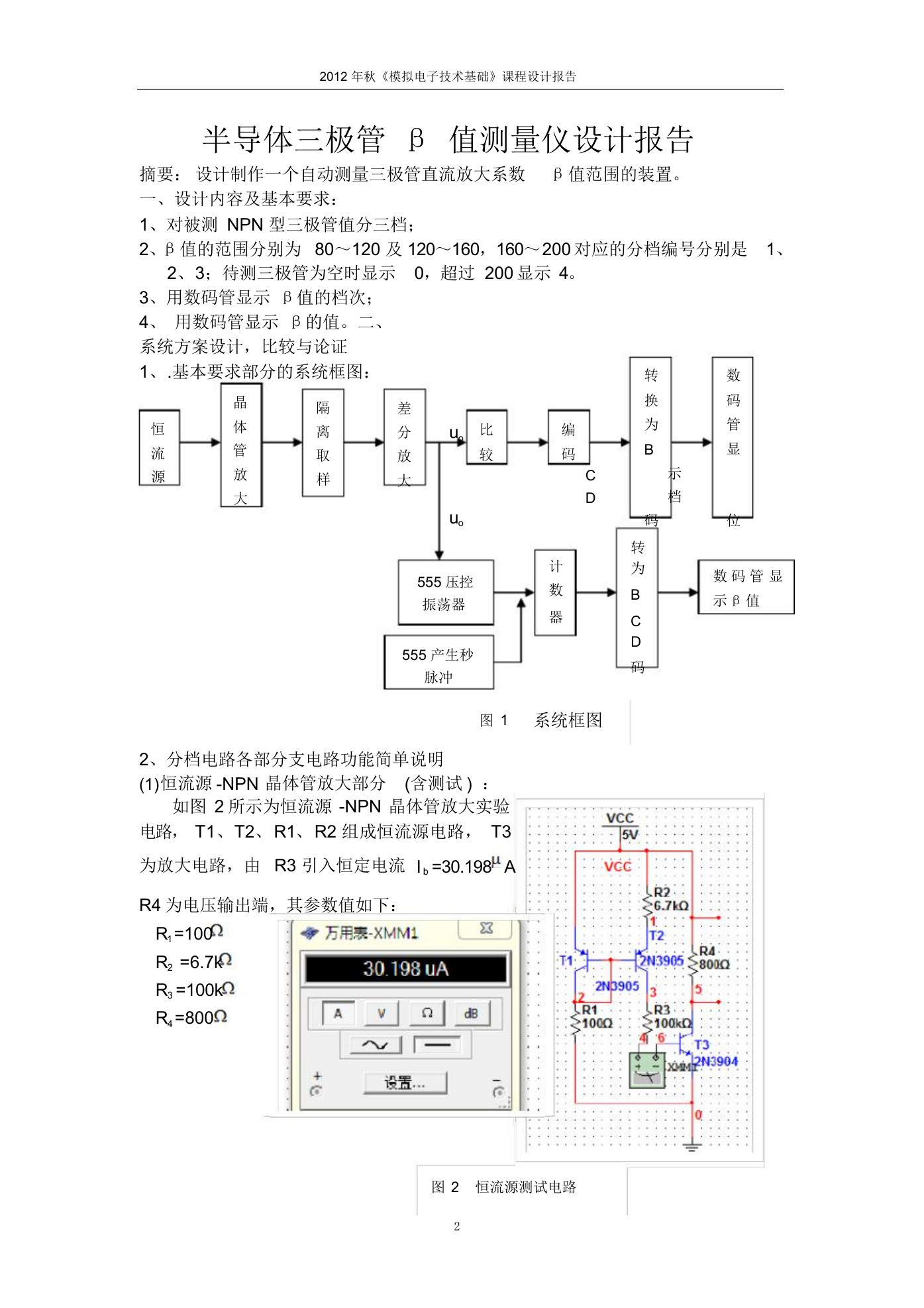

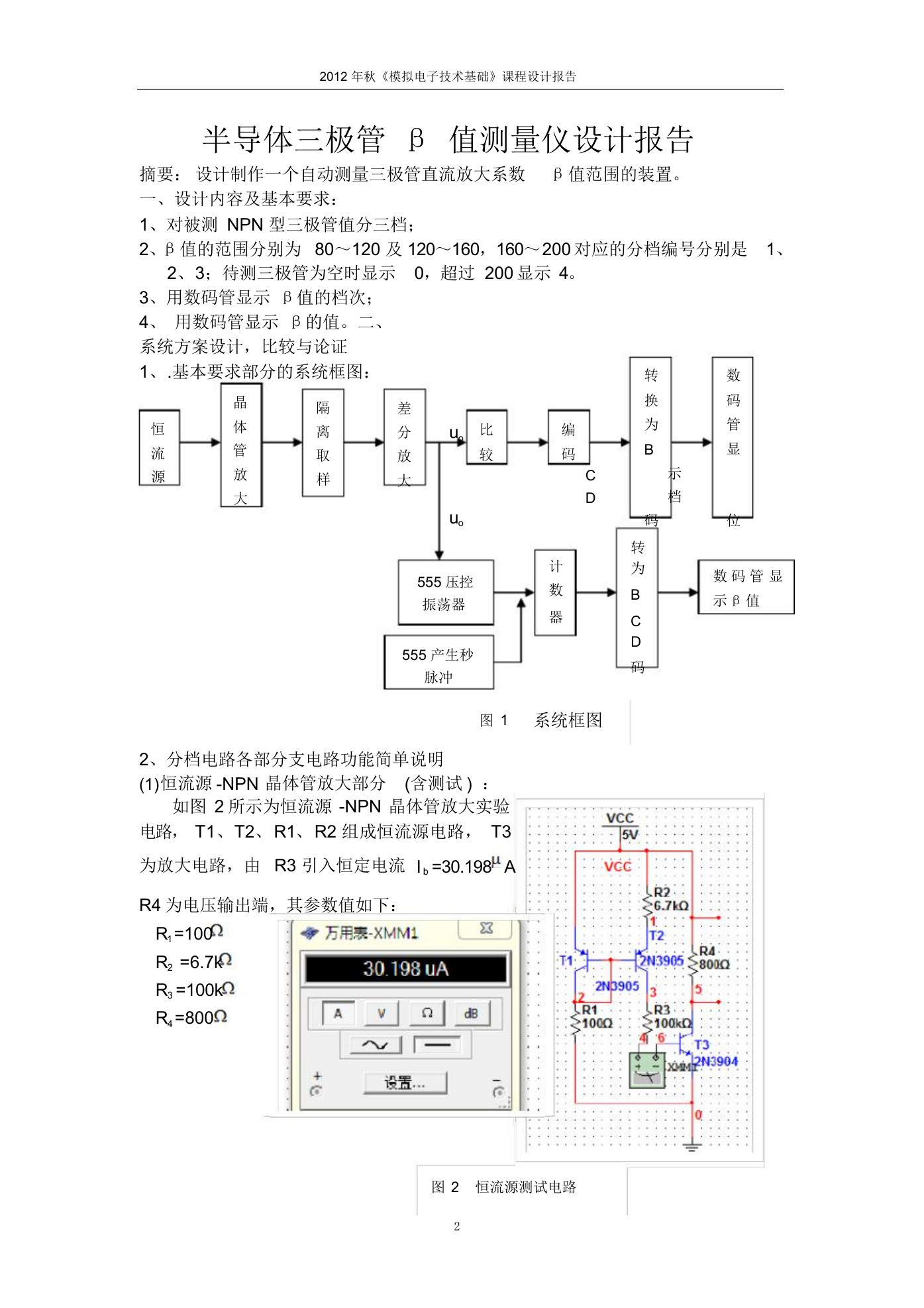

1、.基本要求部分的系统框图:

恒

流

源

晶

体

管

放

大

隔

离

取

样

差

分

放

大

比

较

uo

uo

555 压控

振荡器

555 产生秒

脉冲

编

码

C

D

计

数

器

转

换

为

B

码

示

档

数

码

管

显

位

数 码 管 显

示 β 值

转

为

B

C

D

码

图 1 系统框图

2、分档电路各部分支电路功能简单说明

(1)恒流源 -NPN 晶体管放大部分 (含测试 ) :

如图 2 所示为恒流源 -NPN 晶体管放大实验

电路, T1、T2、R1、R2 组成恒流源电路, T3

为放大电路,由 R3 引入恒定电流

I b =30.198 A

R4 为电压输出端,其参数值如下:

R1=100

R2 =6.7k

R3 =100k

R4=800

图 2 恒流源测试电路

2

�

2012 年秋《模拟电子技术基础》课程设计报告

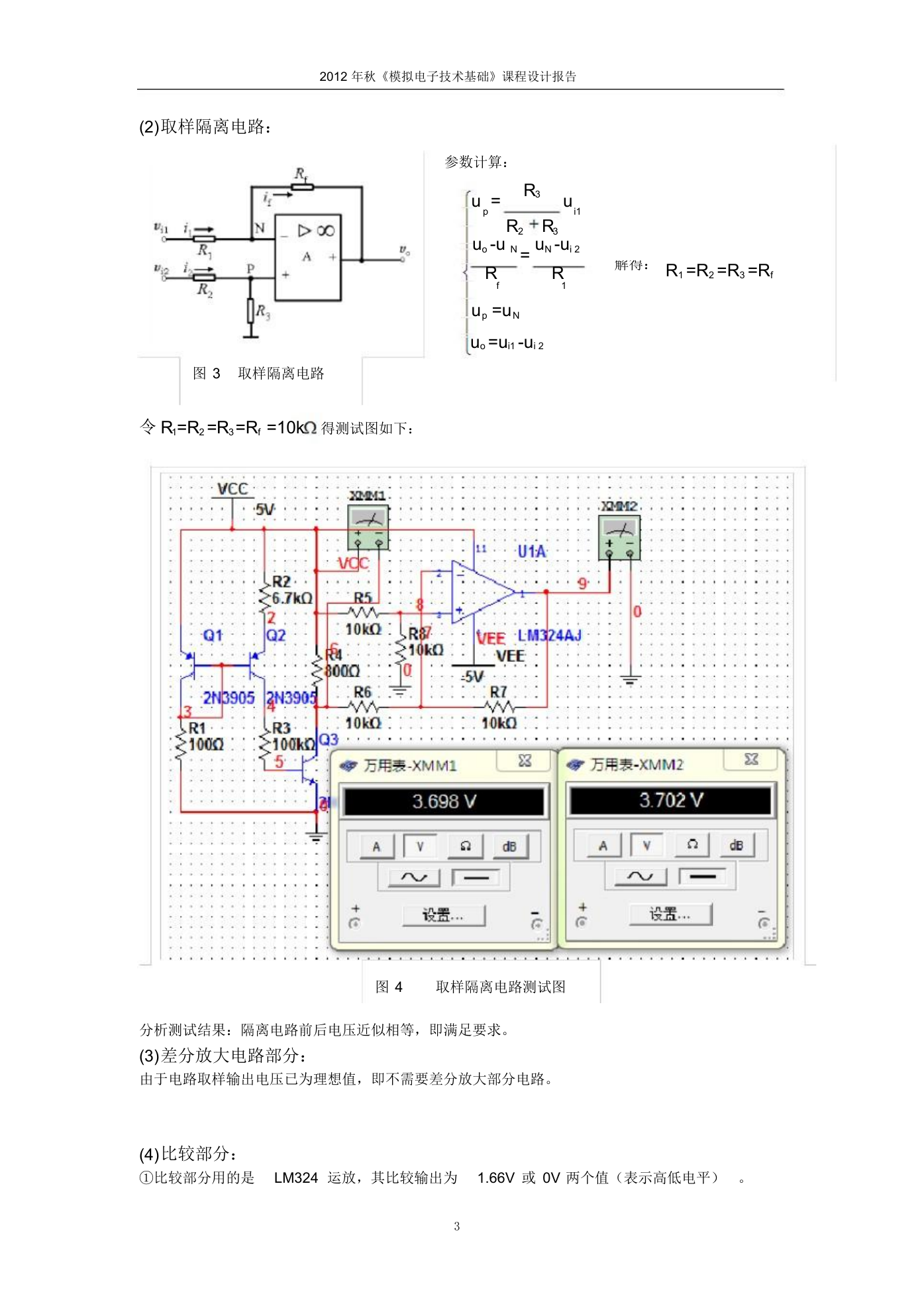

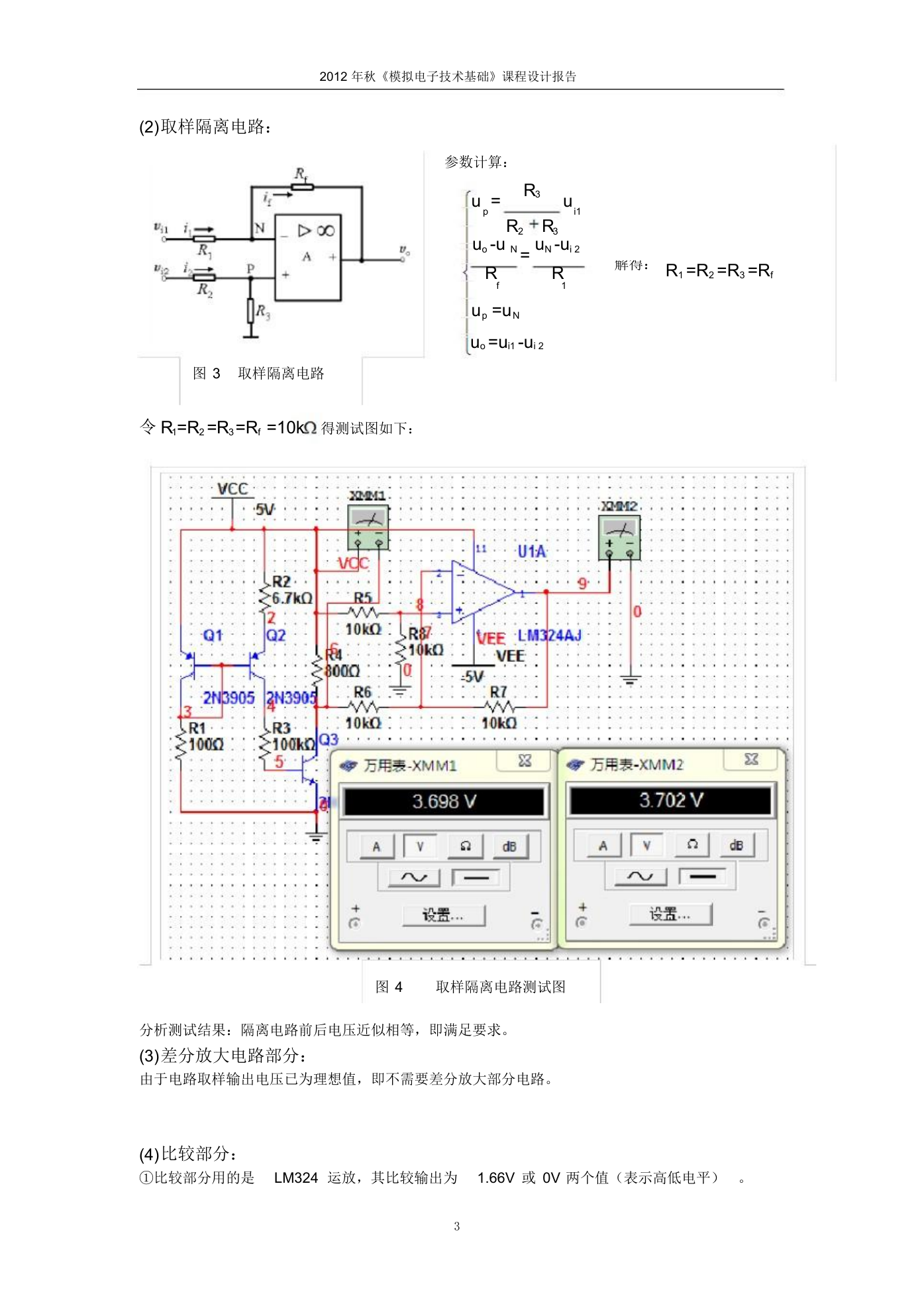

(2)取样隔离电路:

参数计算:

u = R3

p

u

i1

R2 R3

uo -u N = uN -ui 2

R

R

1

f

解得: R1 =R2 =R3 =Rf

up =uN

uo =ui1 -ui 2

图 3 取样隔离电路

令 R1=R2 =R3=Rf =10k 得测试图如下:

图 4

取样隔离电路测试图

分析测试结果:隔离电路前后电压近似相等,即满足要求。

(3)差分放大电路部分:

由于电路取样输出电压已为理想值,即不需要差分放大部分电路。

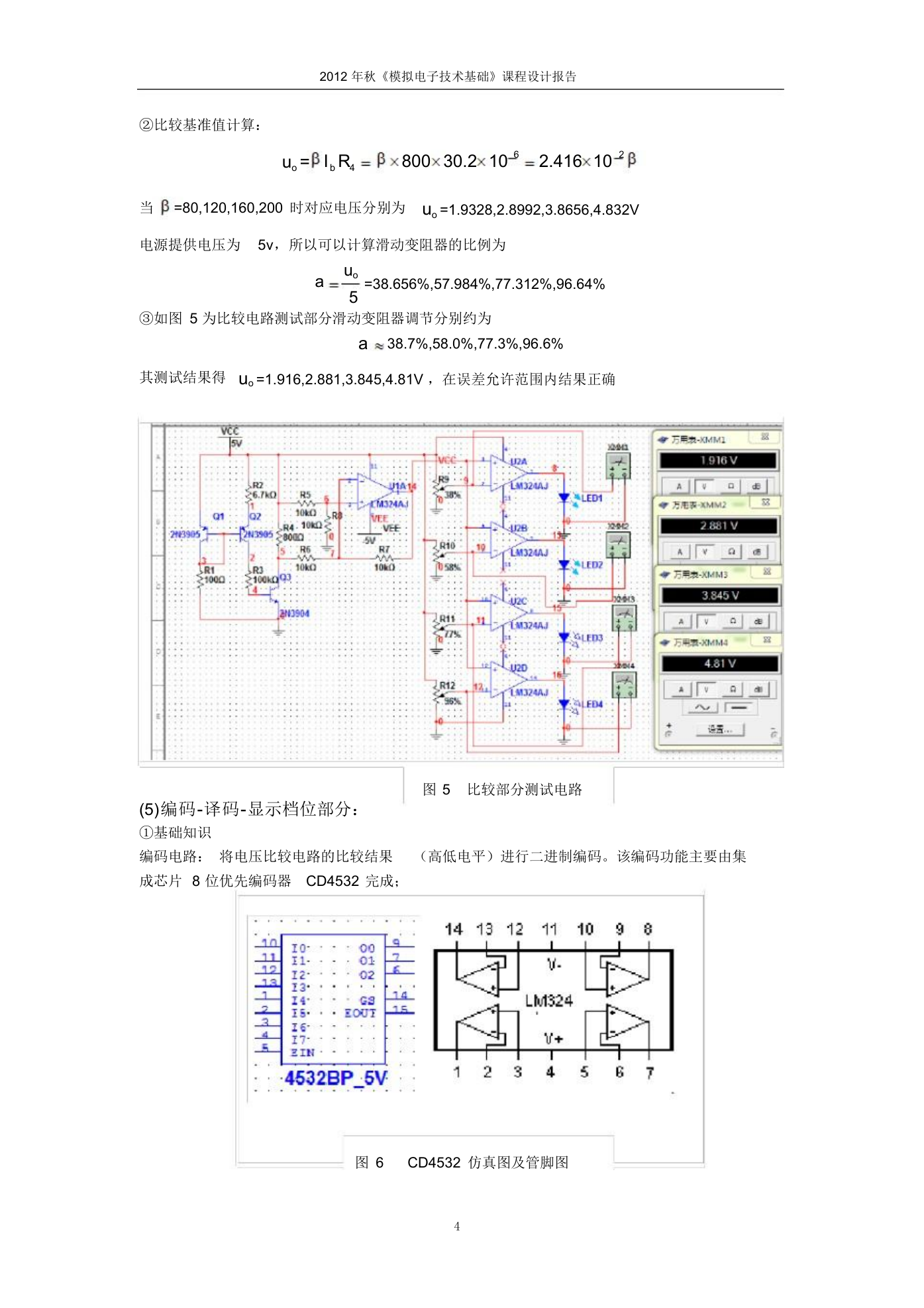

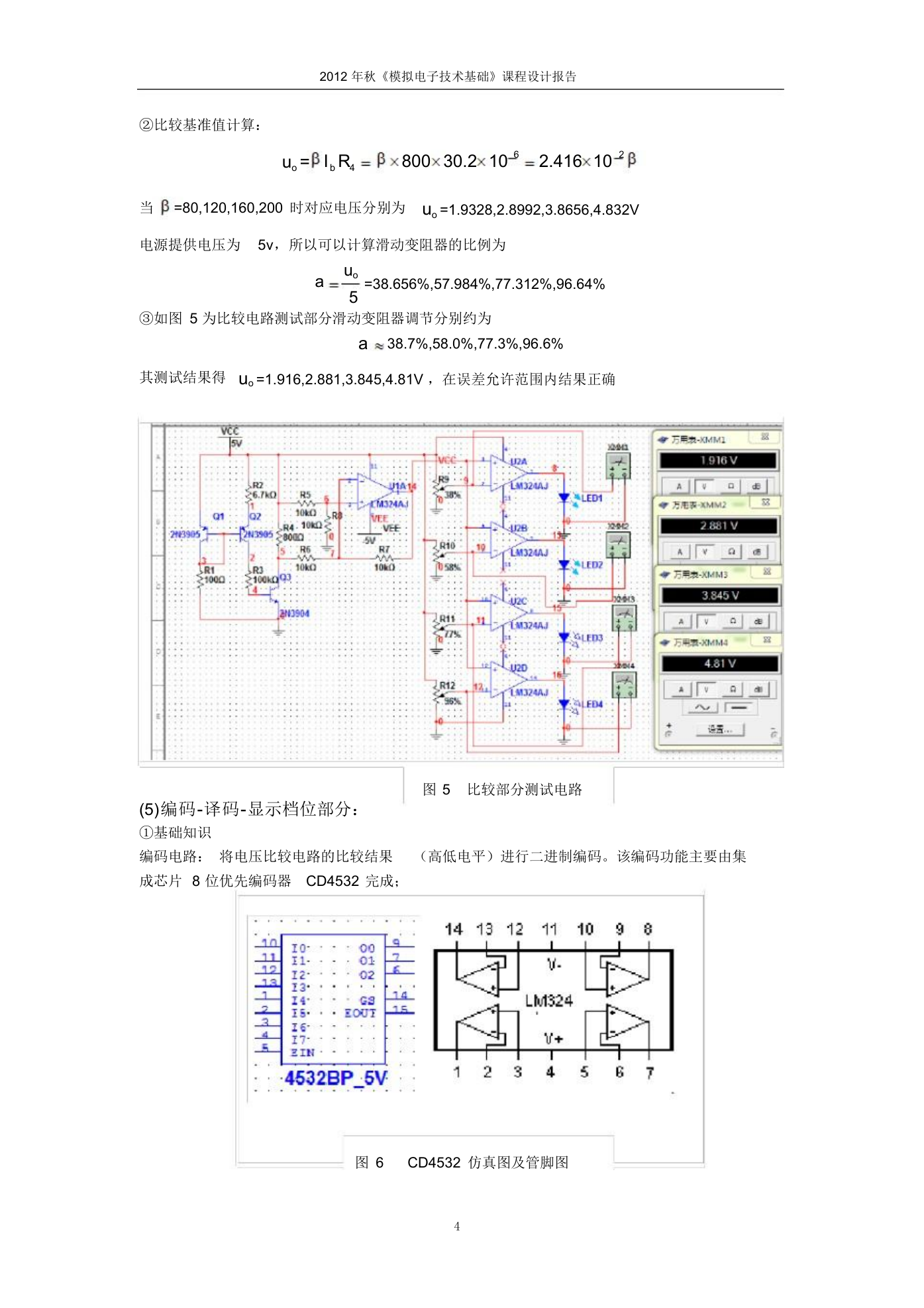

(4)比较部分:

①比较部分用的是 LM324 运放,其比较输出为 1.66V 或 0V 两个值(表示高低电平) 。

3

�

2012 年秋《模拟电子技术基础》课程设计报告

②比较基准值计算:

uo = I b R4

800 30.2 10 6

2.416 10 2

当 =80,120,160,200 时对应电压分别为 uo =1.9328,2.8992,3.8656,4.832V

电源提供电压为 5v,所以可以计算滑动变阻器的比例为

a

uo

5

=38.656%,57.984%,77.312%,96.64%

③如图 5 为比较电路测试部分滑动变阻器调节分别约为

其测试结果得 uo =1.916,2.881,3.845,4.81V ,在误差允许范围内结果正确

a 38.7%,58.0%,77.3%,96.6%

(5)编码-译码-显示档位部分:

①基础知识

图 5 比较部分测试电路

编码电路: 将电压比较电路的比较结果 (高低电平)进行二进制编码。该编码功能主要由集

成芯片 8 位优先编码器 CD4532 完成;

图 6

CD4532 仿真图及管脚图

4

�

2012 年秋《模拟电子技术基础》课程设计报告

编码器的真值表如下表

输入

EI D7 D6 D5 D4 D3 D2 D1 D0

0

1

1

1

1

1

1

1

1

1

X X X X X X X X

0 0 0 0 0 0 0 0

1 X X X X X X X

0 1 X X X X X X

0 0 1 X X X X X

0 0 0 1 X X X X

0 0 0 0 1 X X X

0 0 0 0 0 1 X X

0 0 0 0 0 0 1 X

0 0 0 0 0 0 0 1

输出

GS Q2 Q1 Q0 EO

0 0 0 0 0

0 0 0 0 1

1 1 1 1 0

1 1 1 0 0

1 1 0 1 0

1 1 0 0 0

1 0 1 1 0

1 0 1 0 0

1 0 0 1 0

1 0 0 0 0

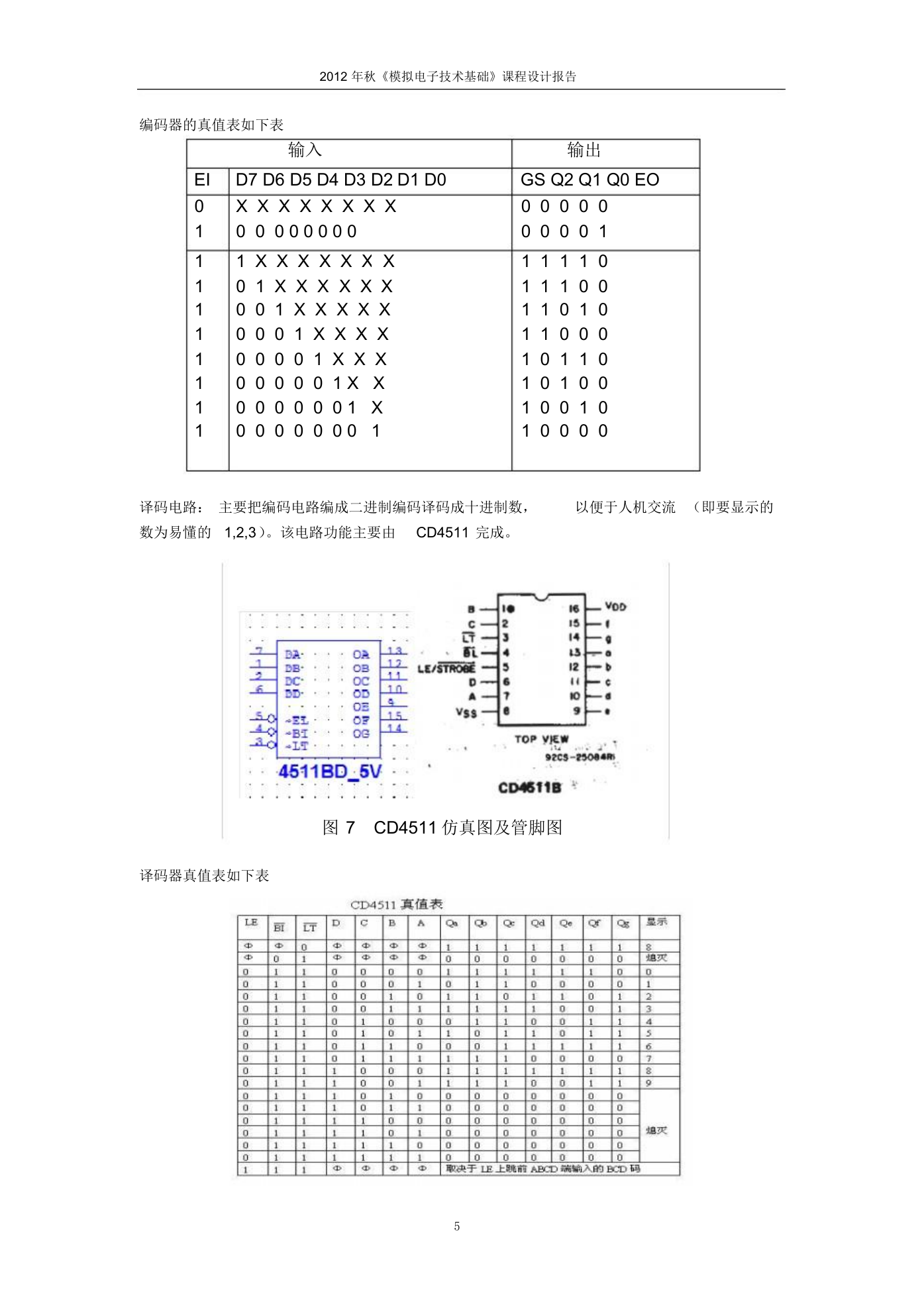

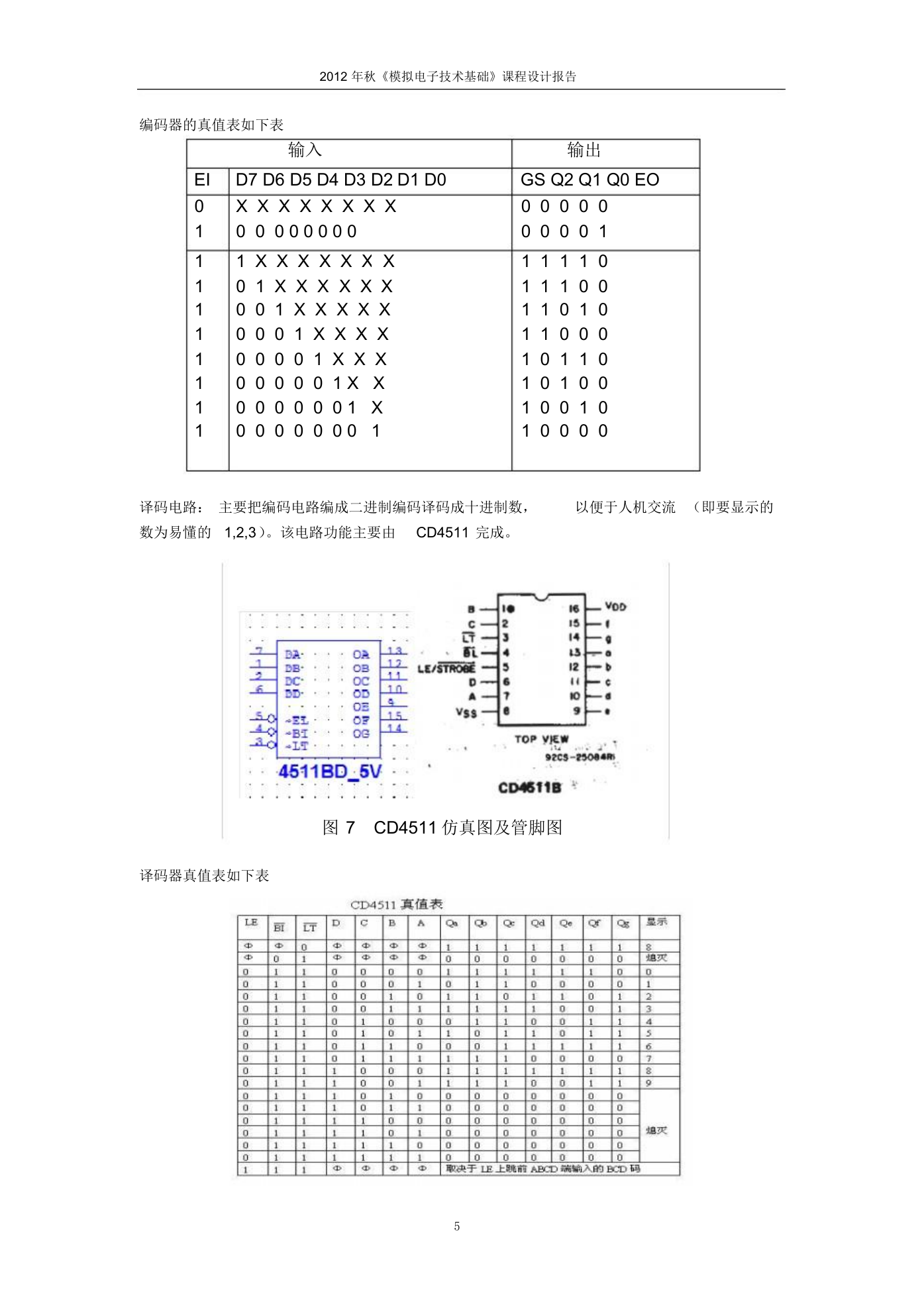

译码电路: 主要把编码电路编成二进制编码译码成十进制数,

数为易懂的 1,2,3 )。该电路功能主要由 CD4511 完成。

以便于人机交流 (即要显示的

图 7 CD4511 仿真图及管脚图

译码器真值表如下表

5

�

2012 年秋《模拟电子技术基础》课程设计报告

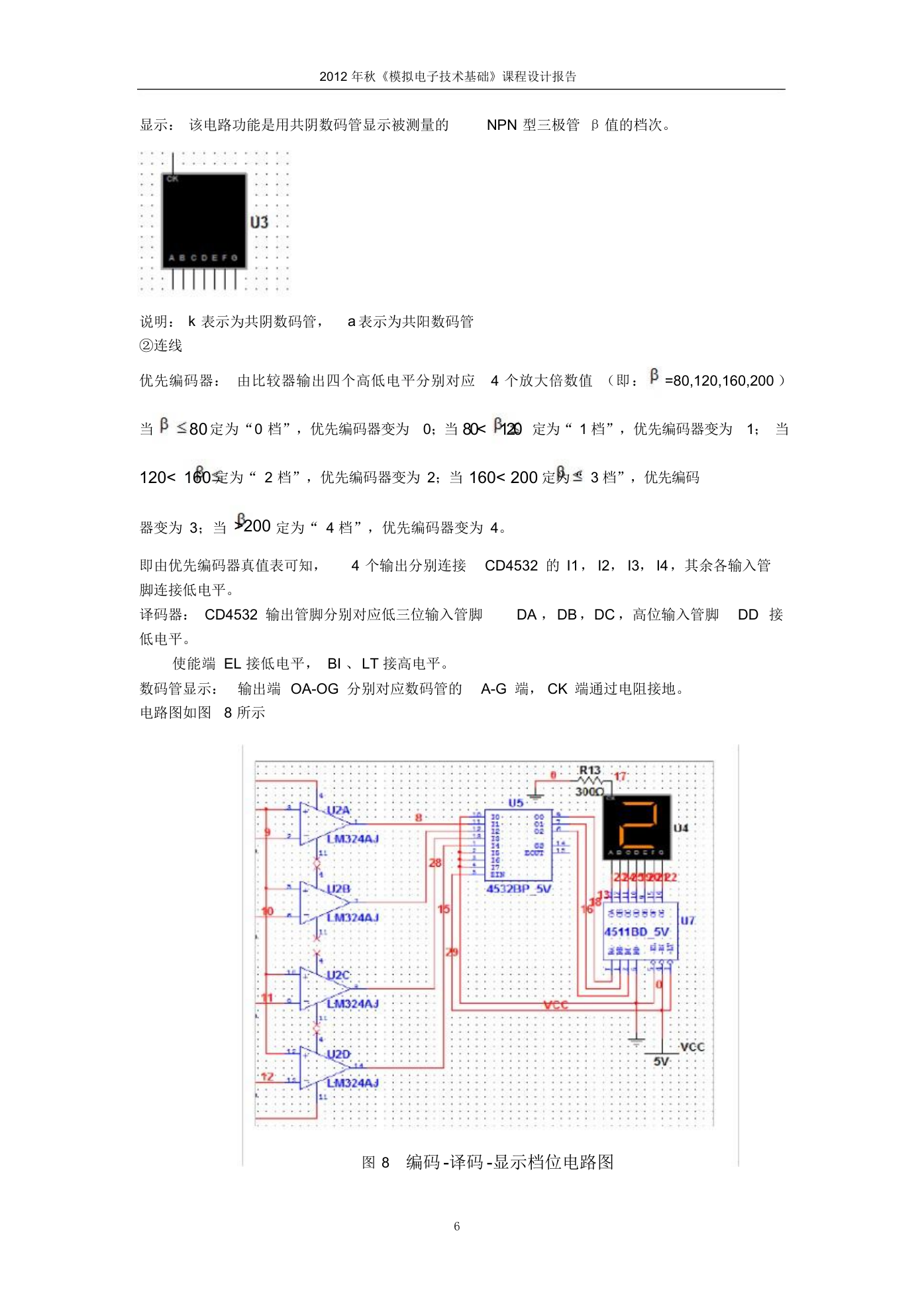

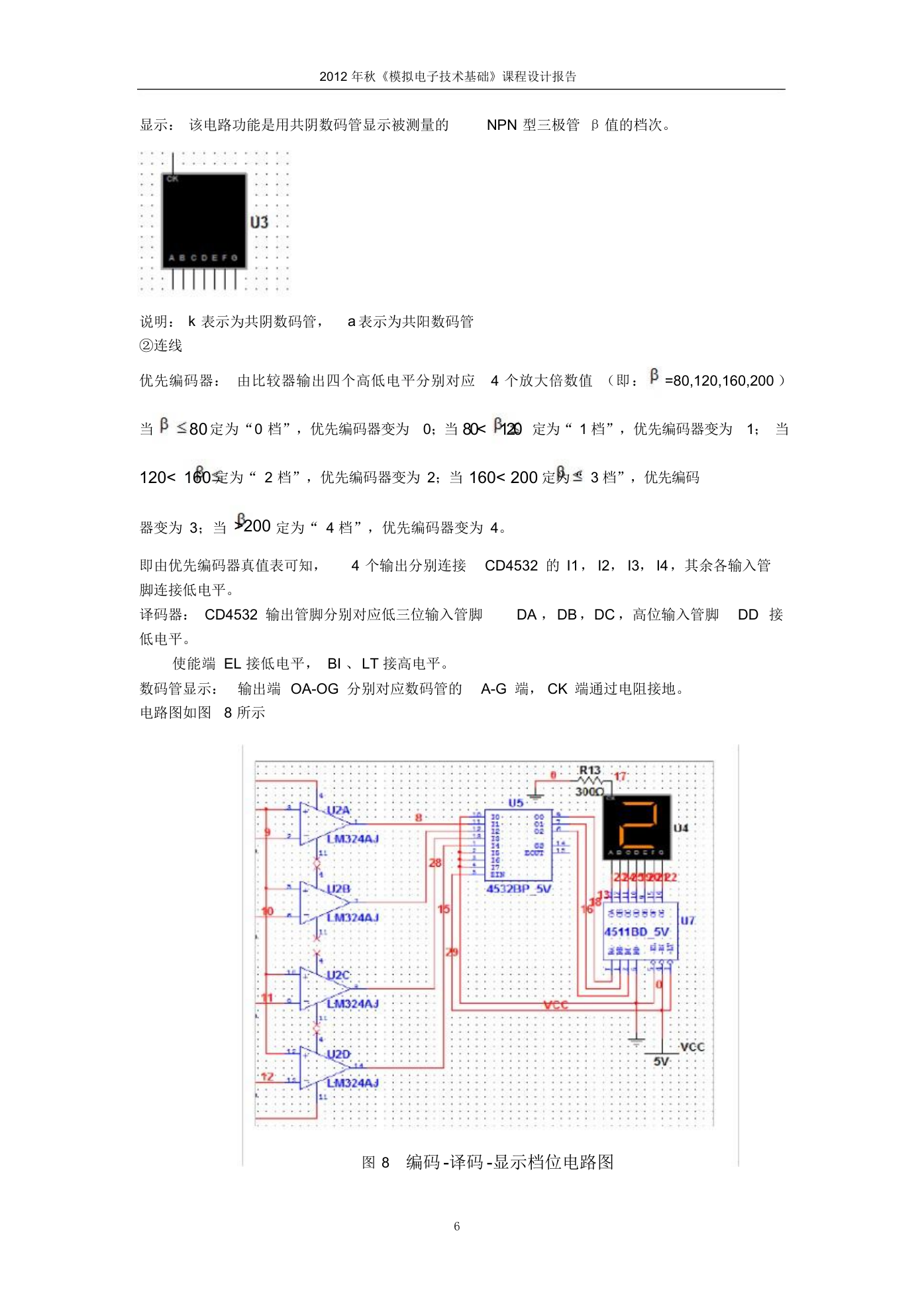

显示: 该电路功能是用共阴数码管显示被测量的

NPN 型三极管 β 值的档次。

说明: k 表示为共阴数码管, a 表示为共阳数码管

②连线

优先编码器: 由比较器输出四个高低电平分别对应 4 个放大倍数值 (即: =80,120,160,200 )

当

80 定为“0 档”,优先编码器变为 0;当 80< 120 定为“ 1 档”,优先编码器变为 1; 当

120< 160 定为“ 2 档”,优先编码器变为 2;当 160< 200 定为“ 3 档”,优先编码

器变为 3;当 >200 定为“ 4 档”,优先编码器变为 4。

即由优先编码器真值表可知, 4 个输出分别连接 CD4532 的 I1, I2, I3, I4,其余各输入管

脚连接低电平。

译码器: CD4532 输出管脚分别对应低三位输入管脚

低电平。

DA ,DB ,DC ,高位输入管脚 DD 接

使能端 EL 接低电平, BI 、LT 接高电平。

数码管显示: 输出端 OA-OG 分别对应数码管的 A-G 端, CK 端通过电阻接地。

电路图如图 8 所示

图 8 编码 -译码 -显示档位电路图

6

�

2012 年秋《模拟电子技术基础》课程设计报告

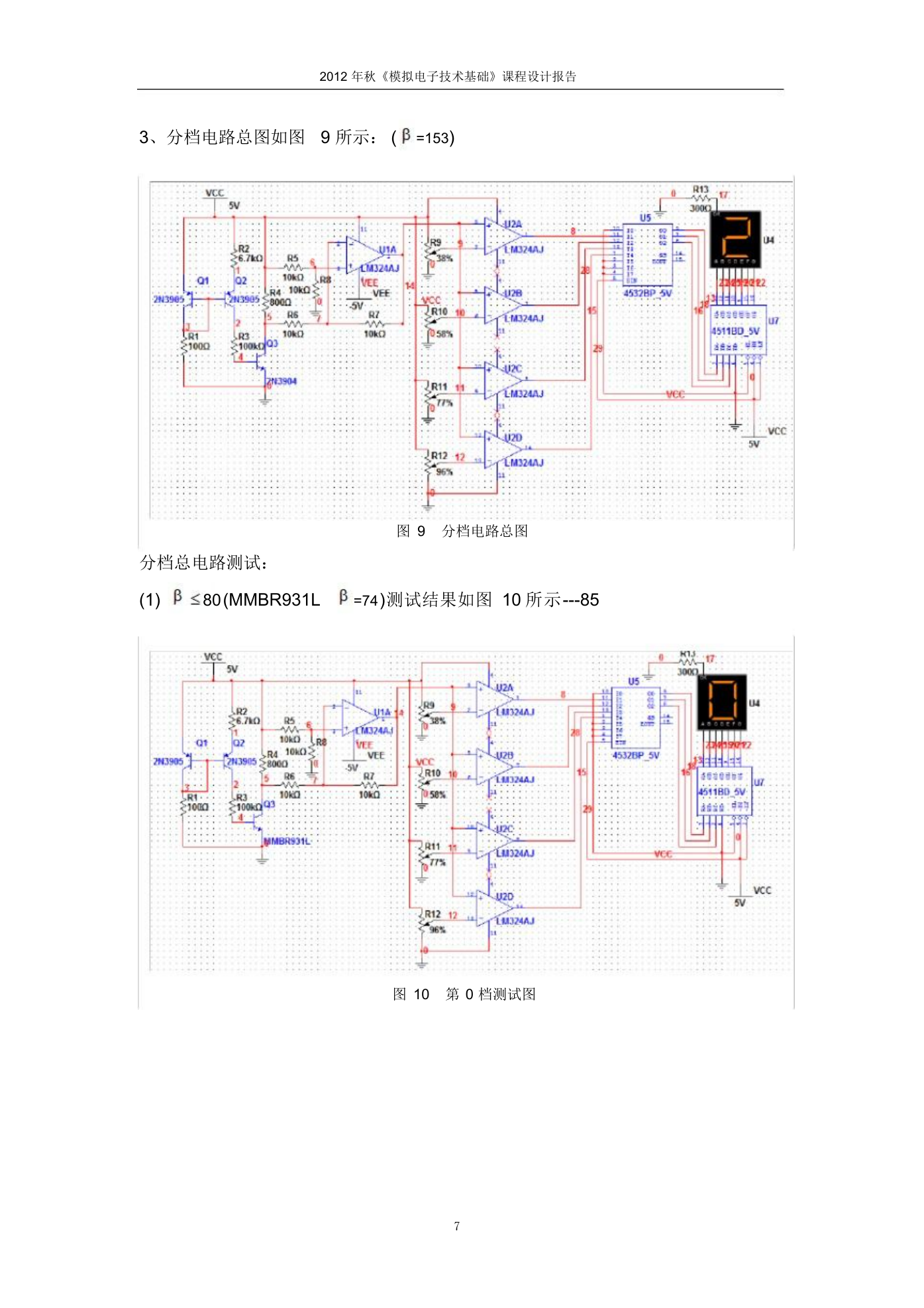

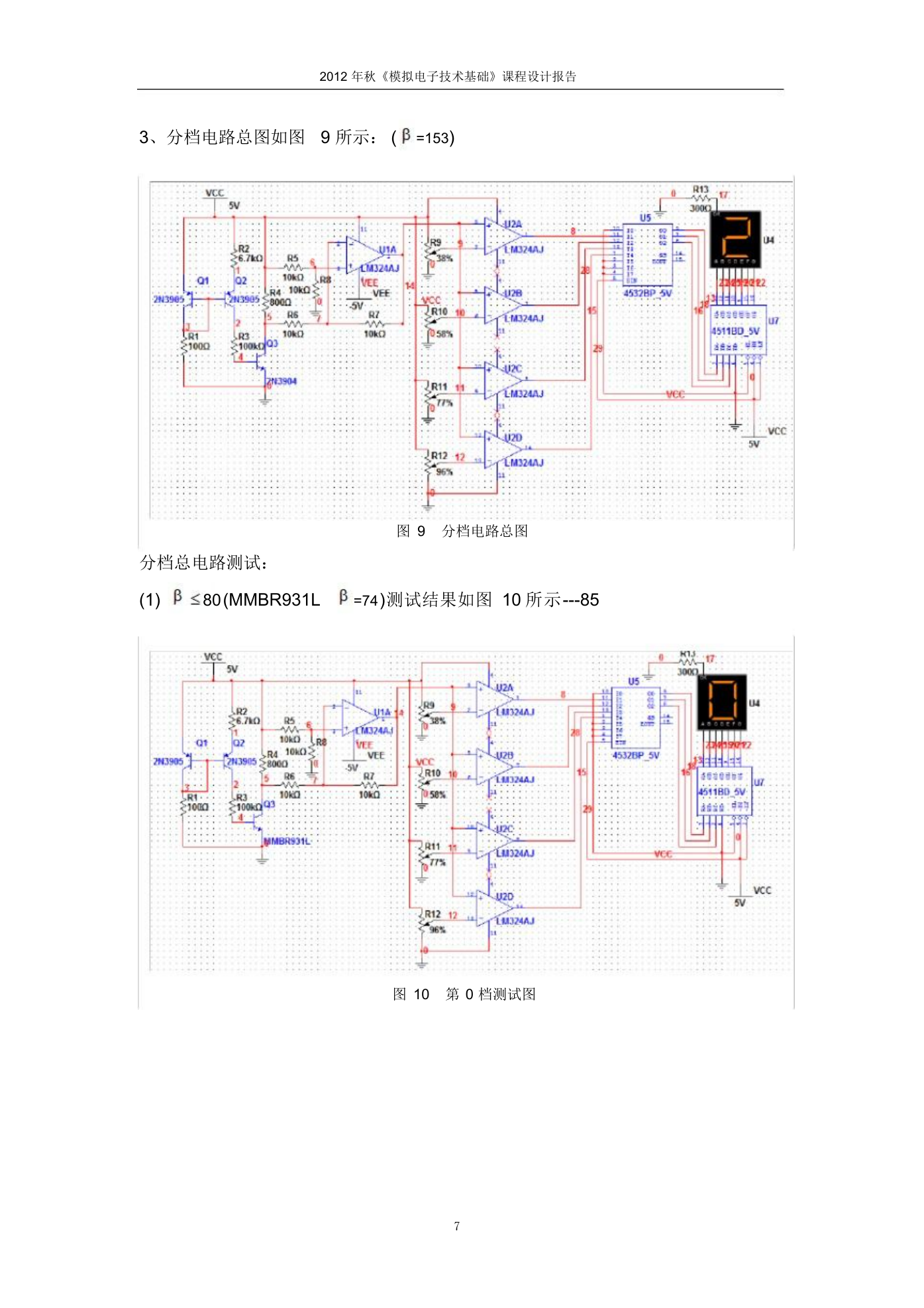

3、分档电路总图如图 9 所示: (

=153)

图 9 分档电路总图

分档总电路测试:

(1)

80(MMBR931L

=74)测试结果如图 10 所示---85

图 10 第 0 档测试图

7

�

2012 年秋《模拟电子技术基础》课程设计报告

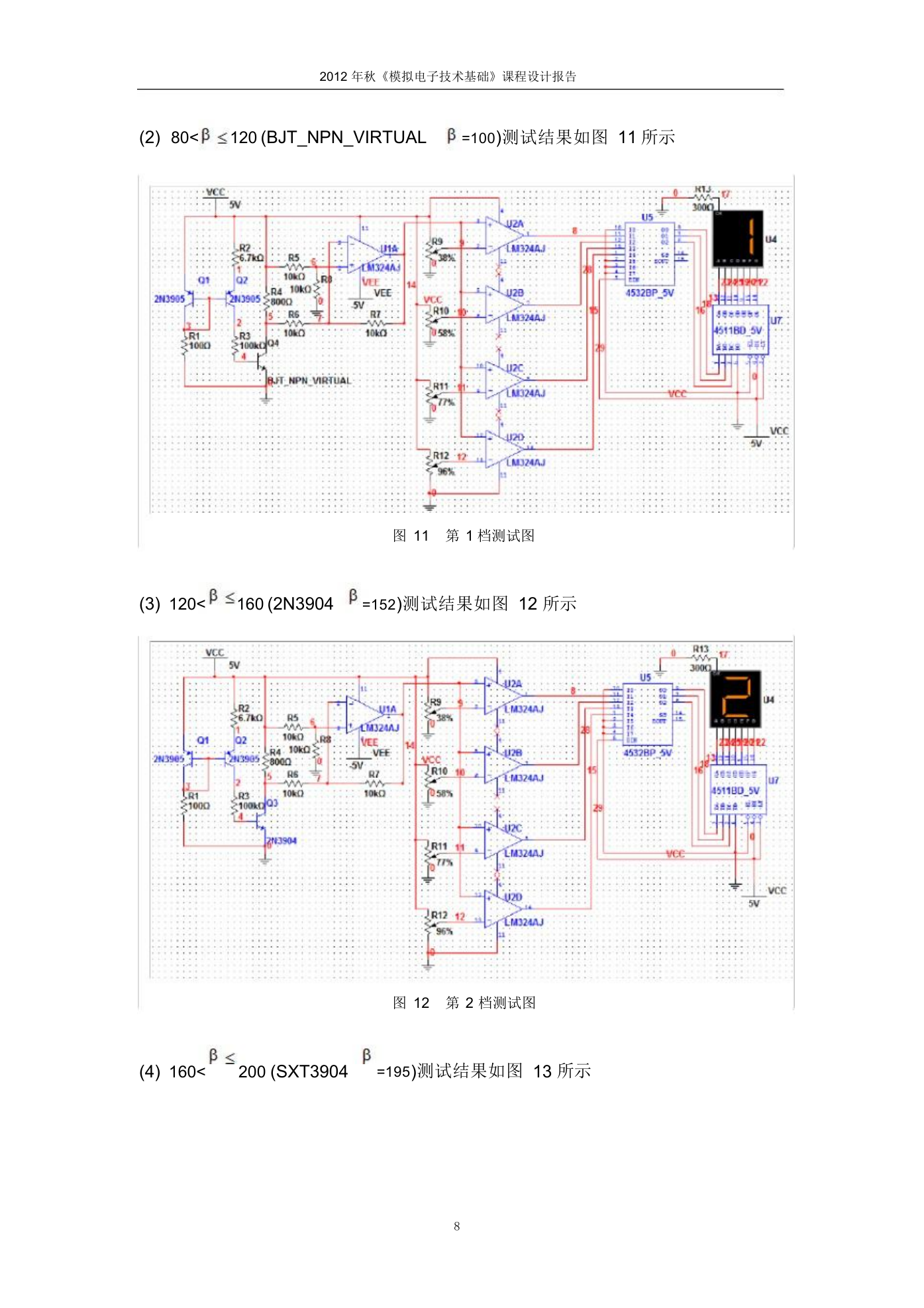

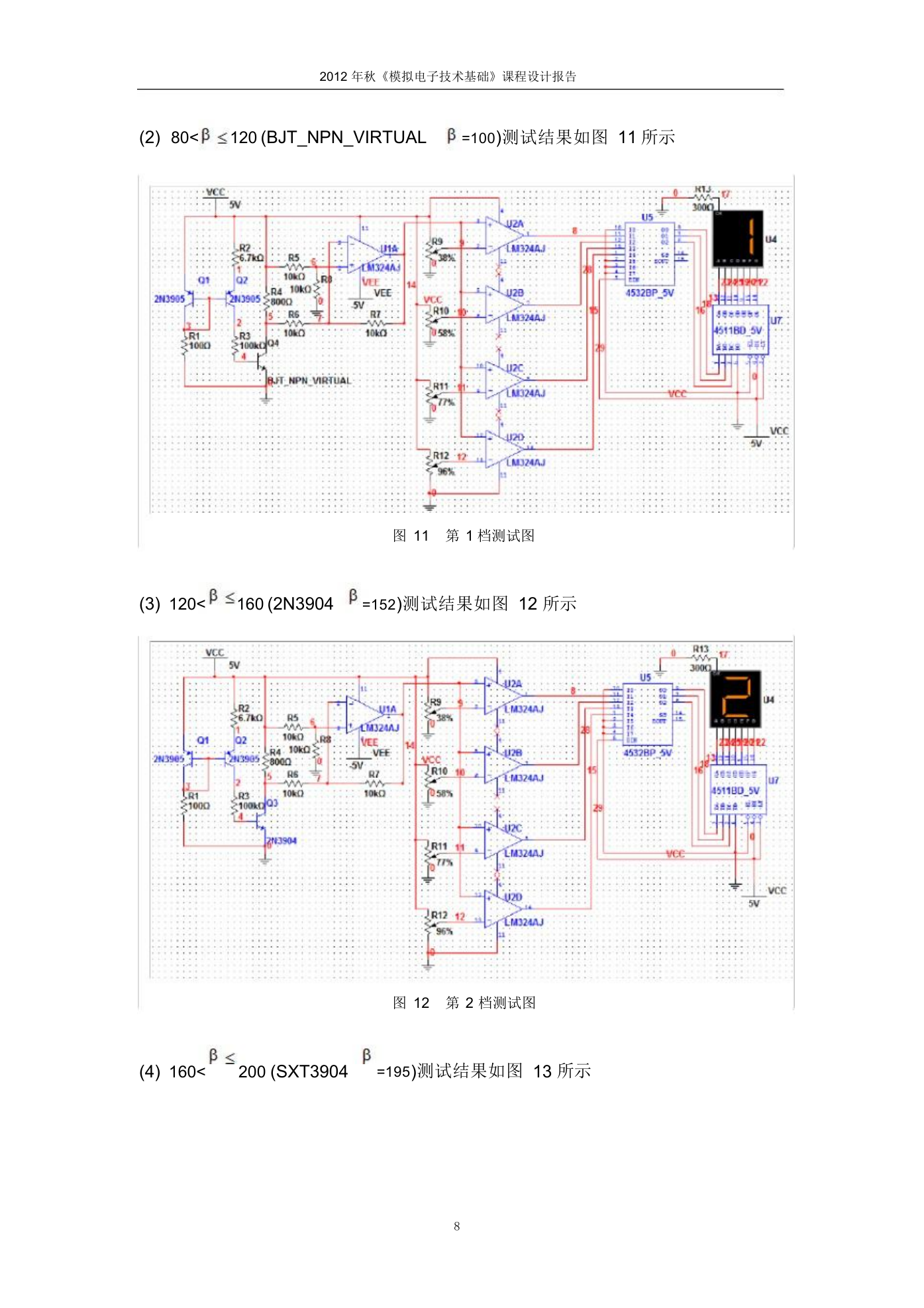

(2) 80<

120 (BJT_NPN_VIRTUAL

=100)测试结果如图 11 所示

图 11 第 1 档测试图

(3) 120<

160 (2N3904

=152)测试结果如图 12 所示

图 12 第 2 档测试图

(4) 160<

200 (SXT3904

=195)测试结果如图 13 所示

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc