长沙理工大学

《通信原理》课程设计报告

郭林

学

班

院 计算机与通信工程 专

级

540802

学

业

号

通信工程

11

学生姓名

郭 林

指导教师

龙 敏

课程成绩

完成日期 2008 年 1 月 11 日

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 1页 共 17 页

基于 Matlab 的卷积码译码器的

设计与仿真

学生姓名:郭 林 指导老师:**

摘 要 本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,

并通过 Matlab 软件进行设计与仿真,并进行误码率分析。在课程设计中,系统

开发平台为 Windows Vista Ultimate,程序设计与仿真均采用 Matlab R2007a(7.4),

最后仿真详单与理论分析一致。

关键词 课程设计;卷积码译码器;Matlab;Simulink;设计与仿真

1 引 言

本课程设计主要解决对一个卷积码序列进行维特比(Viterbi)译码输出,并通

过 Matlab 软件进行设计与仿真。卷积码的译码有两种方法——软判决和硬判决,

此课程设计采用硬判决的维特比译码。

1.1 课程设计目的

卷积码是一种向前纠错控制编码。它将连续的信息比特序列映射为连续的编

码器输出符号。这种映射是高度结构化的,使得卷积码的译码方法与分组码译码

所采用的方法完全不同。可以验证的是在同样复杂度情况下,卷积码的编码增益

要大于分组码的编码增益。对于某个特定的应用,采用分组编码还是采用卷积编

码哪一种更好则取决于这一应用的具体情况和进行比较时可用的技术[1]。

本课程设计便是通过 Matlab 设计一个硬判决维特比译码输出的完整电路,并

进行误码率分析。

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 2页 共 17 页

1.2 课程设计的原理

卷积码,又称连环码,是由伊莱亚斯(P.elias)于 1955 年提出来的一种非分组

码。

卷积编码的最佳译码准则为:在给定已知编码结构、信道特性和接收序列的

情况下,译码器将把与已经发送的序列最相似的序列作为传送的码字序列的估

值。对于二进制对称信道,最相似传送序列就是在汉明距离上与接收序列最近的

序列。

卷积码的译码方法有两大类:一类是大数逻辑译码,又称门限译码(硬判决,

编者注);另一种是概率译码(软判决,编者注),概率译码又分为维特比译码和序

列译码两种。门限译码方法是以分组码理论为基础的,其译码设备简单,速度快,

但其误码性能要比概率译码法差[2]。

当卷积码的约束长度不太大时,与序列译码相比,维特比译码器比较简单,

计算速度快。维特比译码算法是 1967 年由 Viterbi 提出,近年来有大的发展。目

前在数字通信的前向纠错系统中用的较多,而且在卫星深空通信中应用更多,该

算法在卫星通信中已被采用作为标准技术。

2 维特比译码原理

采用概率译码的基本思想是:把已接收序列与所有可能的发送序列做比较,

选择其中码距最小的一个序列作为发送序列。如果发送 L 组信息比特,那么对

于(n,k)卷积码来说,可能发送的序列有 2kL 个,计算机或译码器需存储这些序列

并进行比较,以找到码距最小的那个序列。当传信率和信息组数 L 较大时,使

得译码器难以实现。维特比算法则对上述概率译码做了简化,以至成为了一种实

用化的概率算法。它并不是在网格图上一次比较所有可能的 2kL 条路径(序列),

而是接收一段,计算和比较一段,选择一段最大似然可能的码段,从而达到整个

码序列是一个最大似然值得序列。

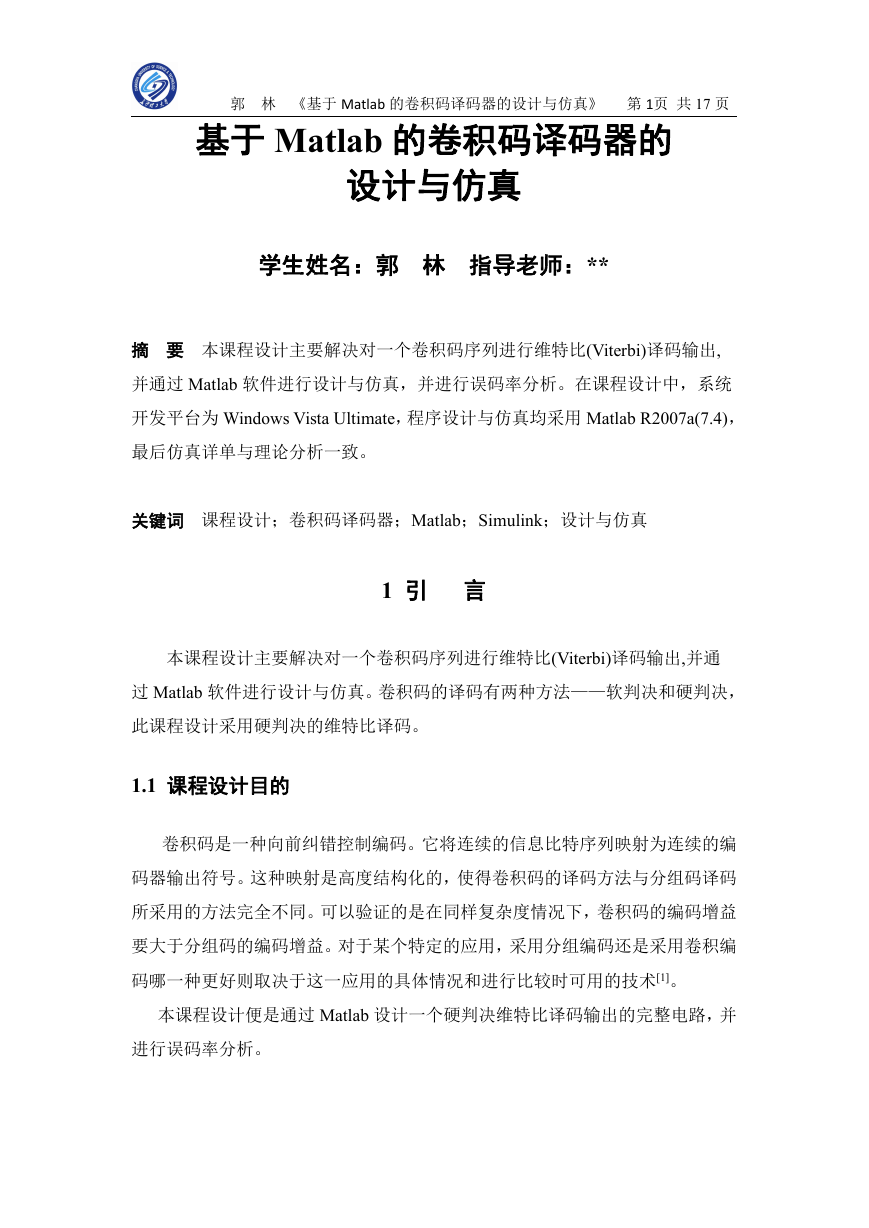

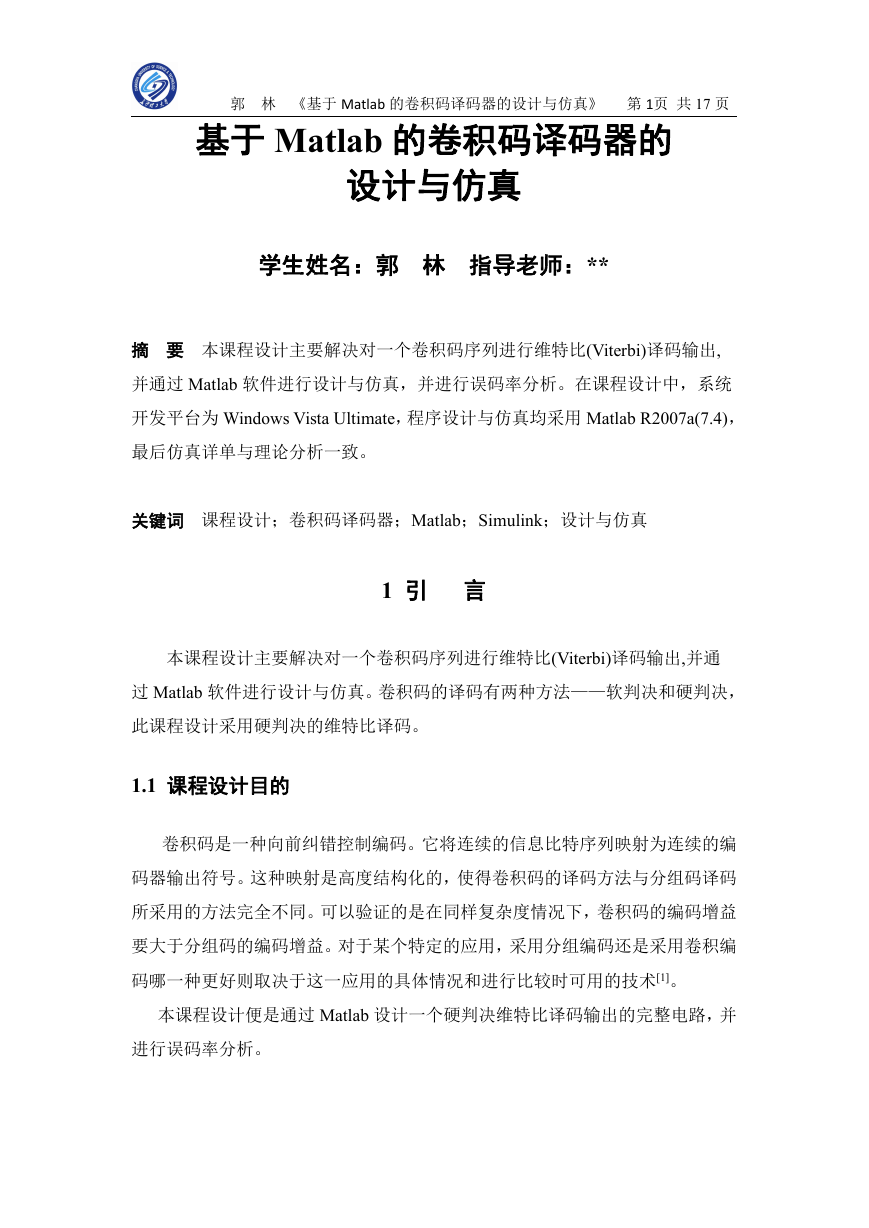

下面以图 2.1 的(2,1,3)卷积码编码器所编出的码为例,来说明维特比解码

的方法和运作过程。为了能说明解码过程,这里给出该码的状态图,如图 2.2 所

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 3页 共 17 页

输入序列

m1,m2,…mj,…

mj mj-1 mj-2

y1j

y2j

00

a

11

11

输

出

序

列

b

01

01

d

00

10

c

图 2.1

(2,1,3)卷积码编码器

图 2.2

(2,1,3)卷积码状态图

示。维特比译码需要利用图来说明移码过程。根据卷积码画网格的方法,我们可

以画出该码的网格图,如图 2.3 所示。该图设输入信息数目 L=5,所以画 L+N=8

个时间单位,图中分别标以 0 至 7。这里设编码器从 a 状态开始运作。该网格图

的每一条路径都对应着不同的输入信息序列。由于所有可能输入信息序列共有

2kL 个,因而网格图中所有可能的路径也为 2kL 条。这里节点 a=00,b=01,c=10,

d=11。

节点号 0

a

b

c

d

1

00

11

2

00

11

5

4

3

00

11

11

00

11

11

00

11

11

6

00

11

7

00

11

00

10

10

10

00

10

01

01

01

01

01

01

01

01

01

01

01

图 2.3

(2,1,3)卷积码网格图

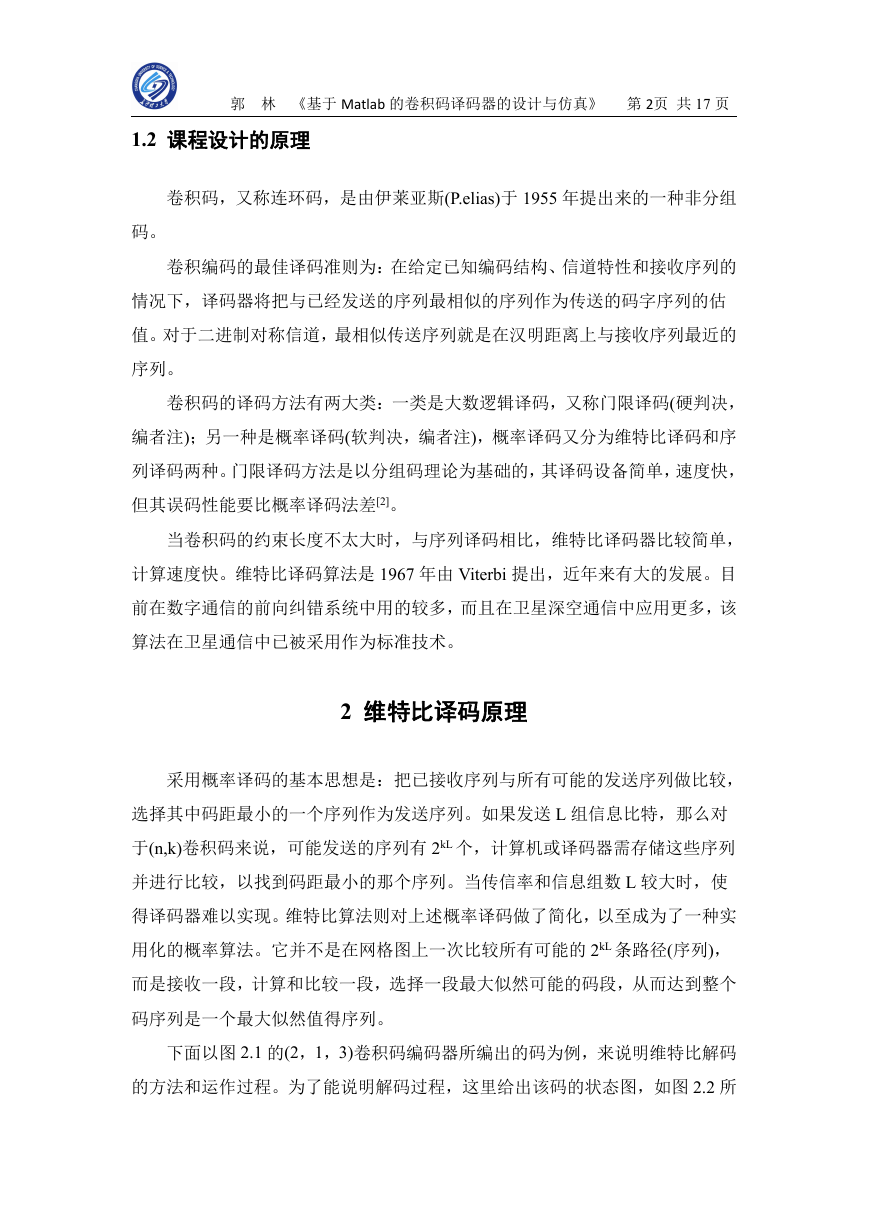

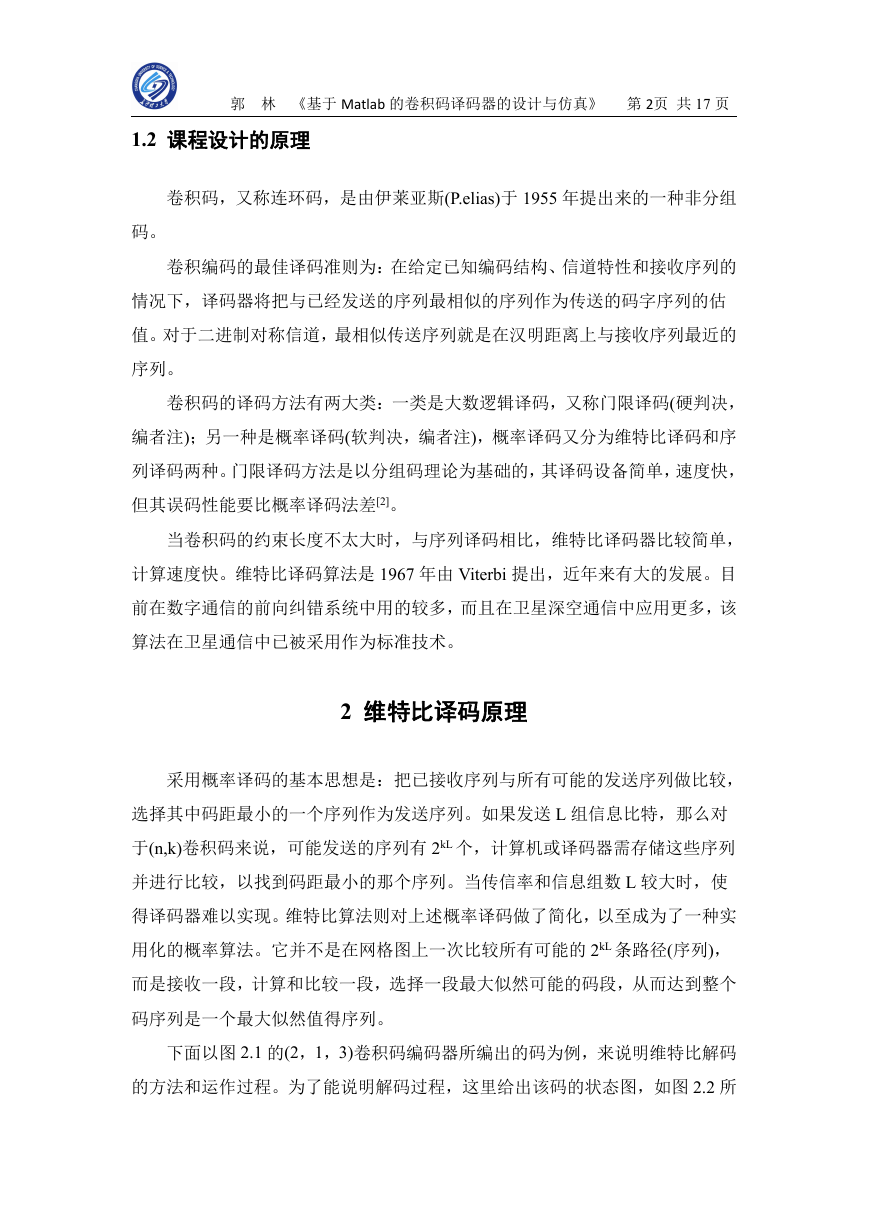

设输入编码器的信息序列为(11011000),则由编码器对应输出的序列为

Y=(1101010001011100),编码器的状态转移路线为 abdcbdca。若收到的序列

R=(0101011001011100),对照网格图来说明维特比译码的方法。

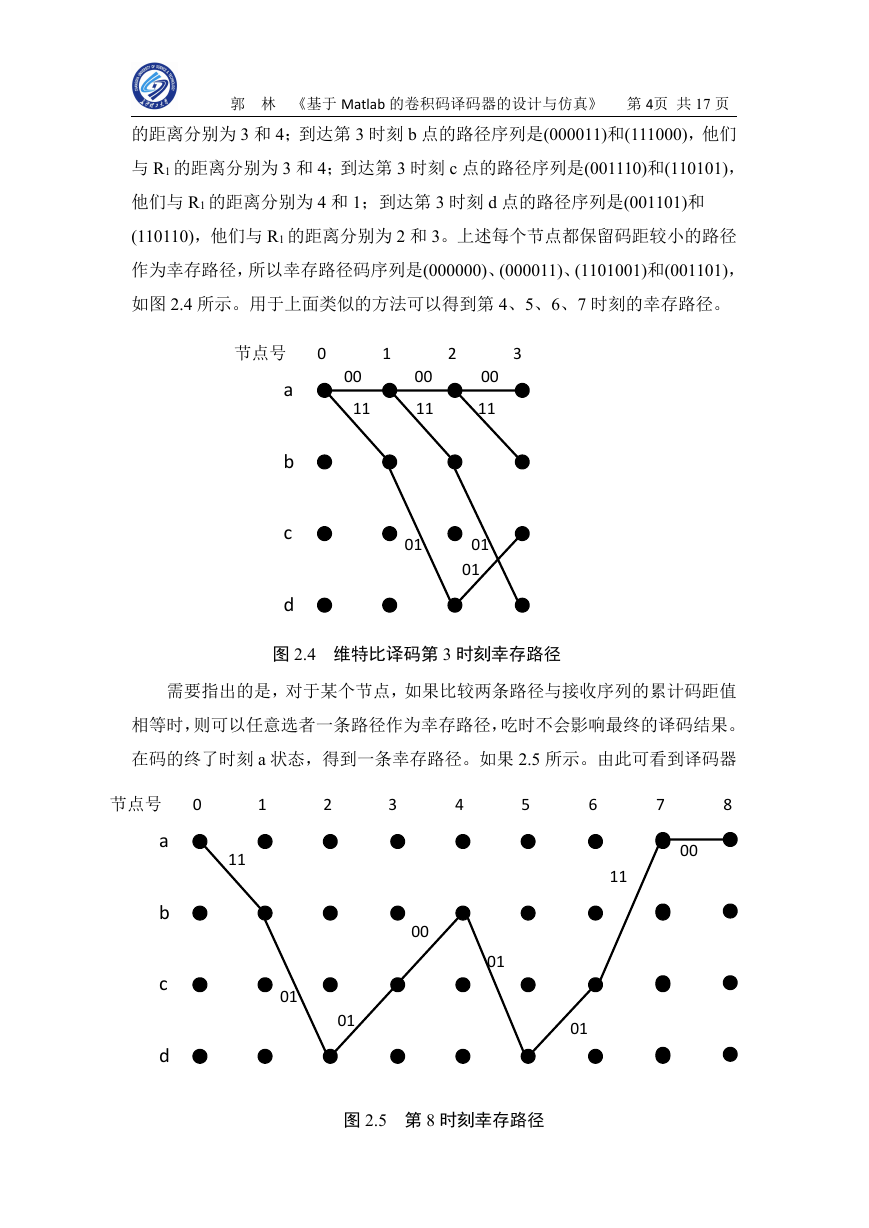

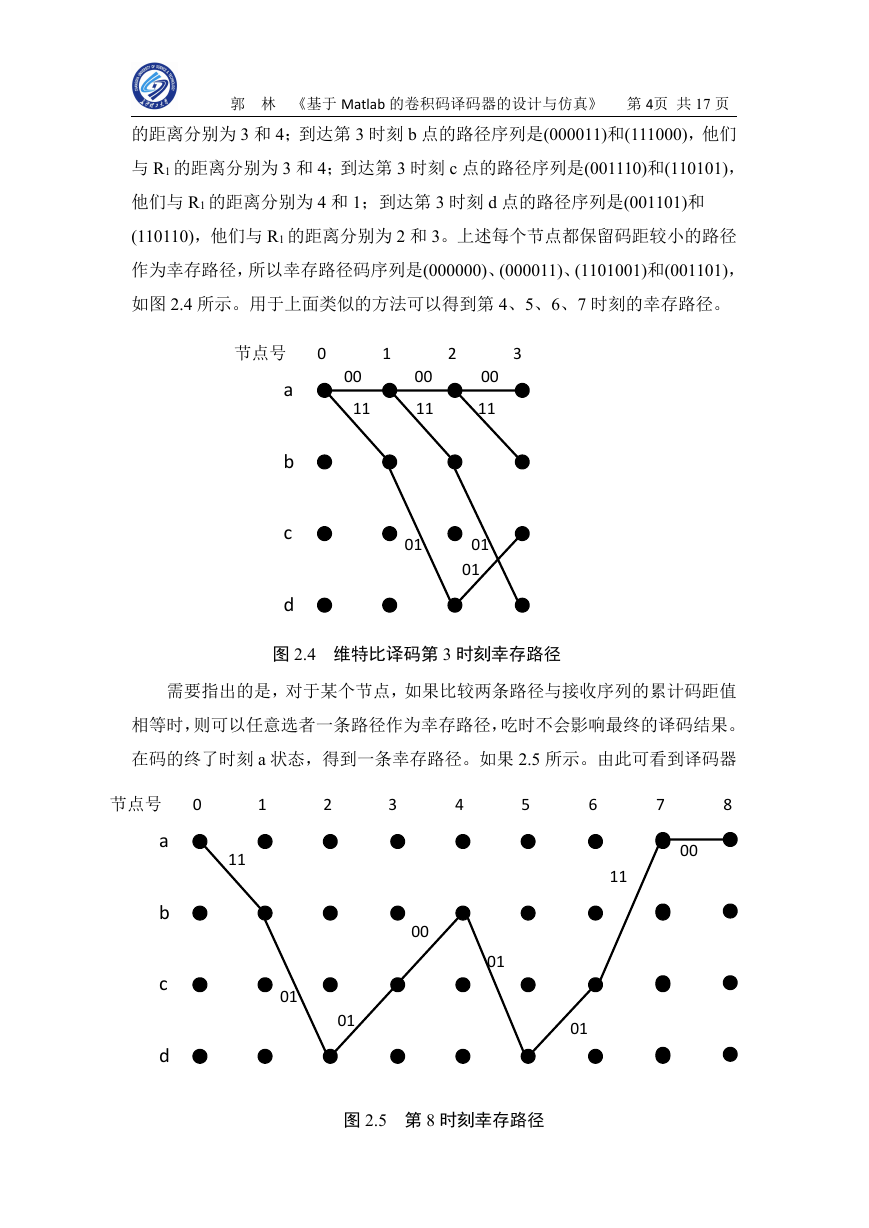

由于该卷积码的约束长度为 6 位,因此先选择接收序列的前 6 位序列

R1=(010101)同到达第 3 时刻的可能的 8 个码序列(即 8 条路径)进行比较,并计算

出码距。该例中到达第 3 时刻 a 点的路径序列是(000000)和(111011),他们与 R1

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 4页 共 17 页

的距离分别为 3 和 4;到达第 3 时刻 b 点的路径序列是(000011)和(111000),他们

与 R1 的距离分别为 3 和 4;到达第 3 时刻 c 点的路径序列是(001110)和(110101),

他们与 R1 的距离分别为 4 和 1;到达第 3 时刻 d 点的路径序列是(001101)和

(110110),他们与 R1 的距离分别为 2 和 3。上述每个节点都保留码距较小的路径

作为幸存路径,所以幸存路径码序列是(000000)、(000011)、(1101001)和(001101),

如图 2.4 所示。用于上面类似的方法可以得到第 4、5、6、7 时刻的幸存路径。

1

00

11

2

00

11

3

00

11

01

01

01

节点号 0

a

b

c

d

图 2.4 维特比译码第 3 时刻幸存路径

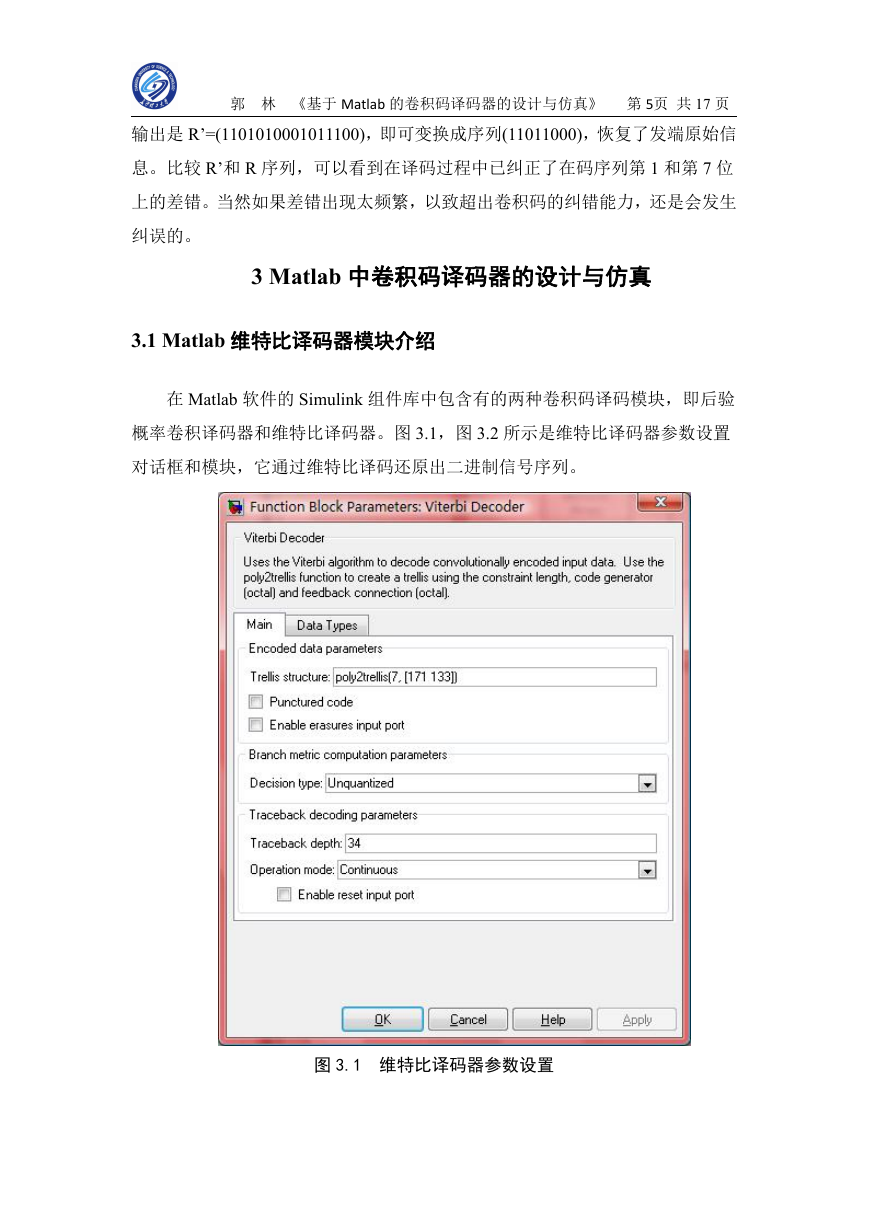

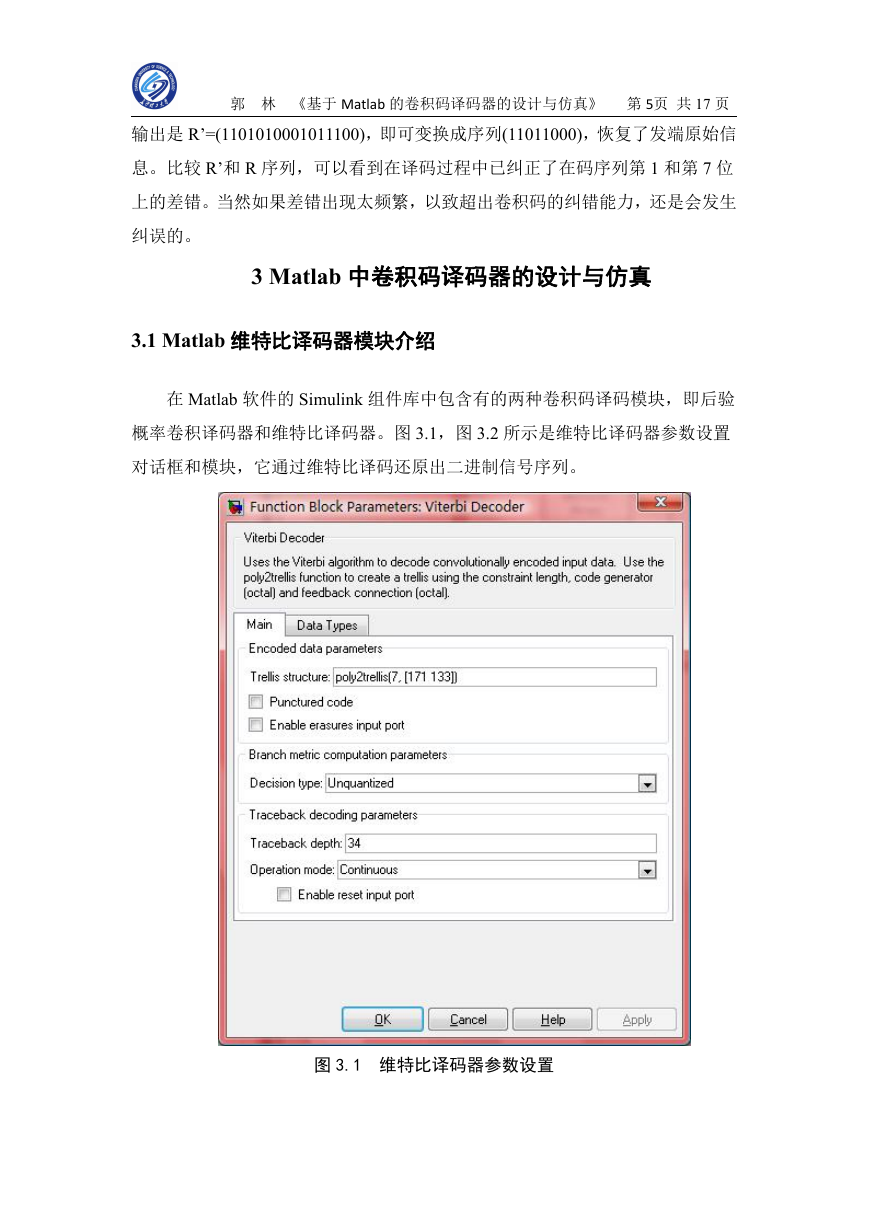

需要指出的是,对于某个节点,如果比较两条路径与接收序列的累计码距值

相等时,则可以任意选者一条路径作为幸存路径,吃时不会影响最终的译码结果。

在码的终了时刻 a 状态,得到一条幸存路径。如果 2.5 所示。由此可看到译码器

节点号 0

1

2

3

4

5

6

7

8

00

11

11

a

b

c

d

00

01

01

01

01

图 2.5 第 8 时刻幸存路径

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 5页 共 17 页

输出是 R’=(1101010001011100),即可变换成序列(11011000),恢复了发端原始信

息。比较 R’和 R 序列,可以看到在译码过程中已纠正了在码序列第 1 和第 7 位

上的差错。当然如果差错出现太频繁,以致超出卷积码的纠错能力,还是会发生

纠误的。

3 Matlab 中卷积码译码器的设计与仿真

3.1 Matlab 维特比译码器模块介绍

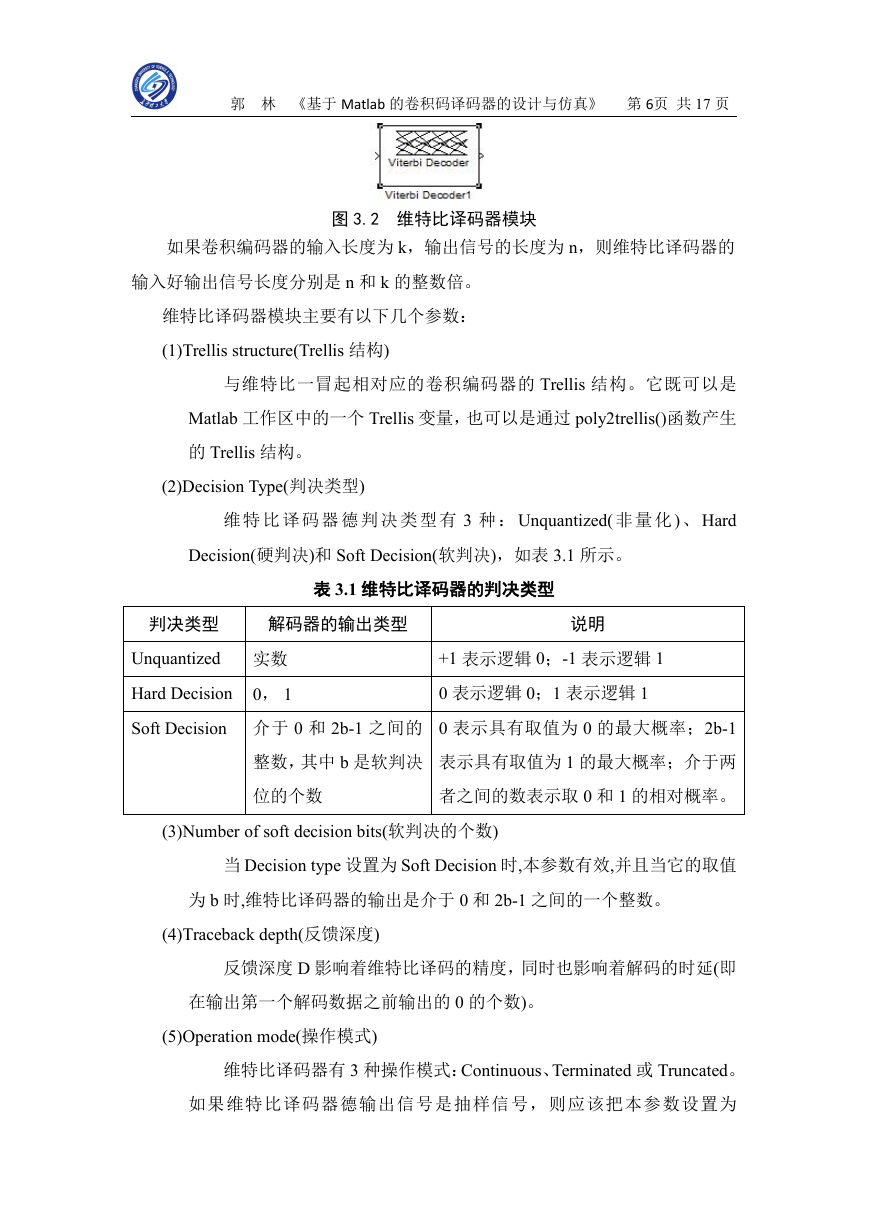

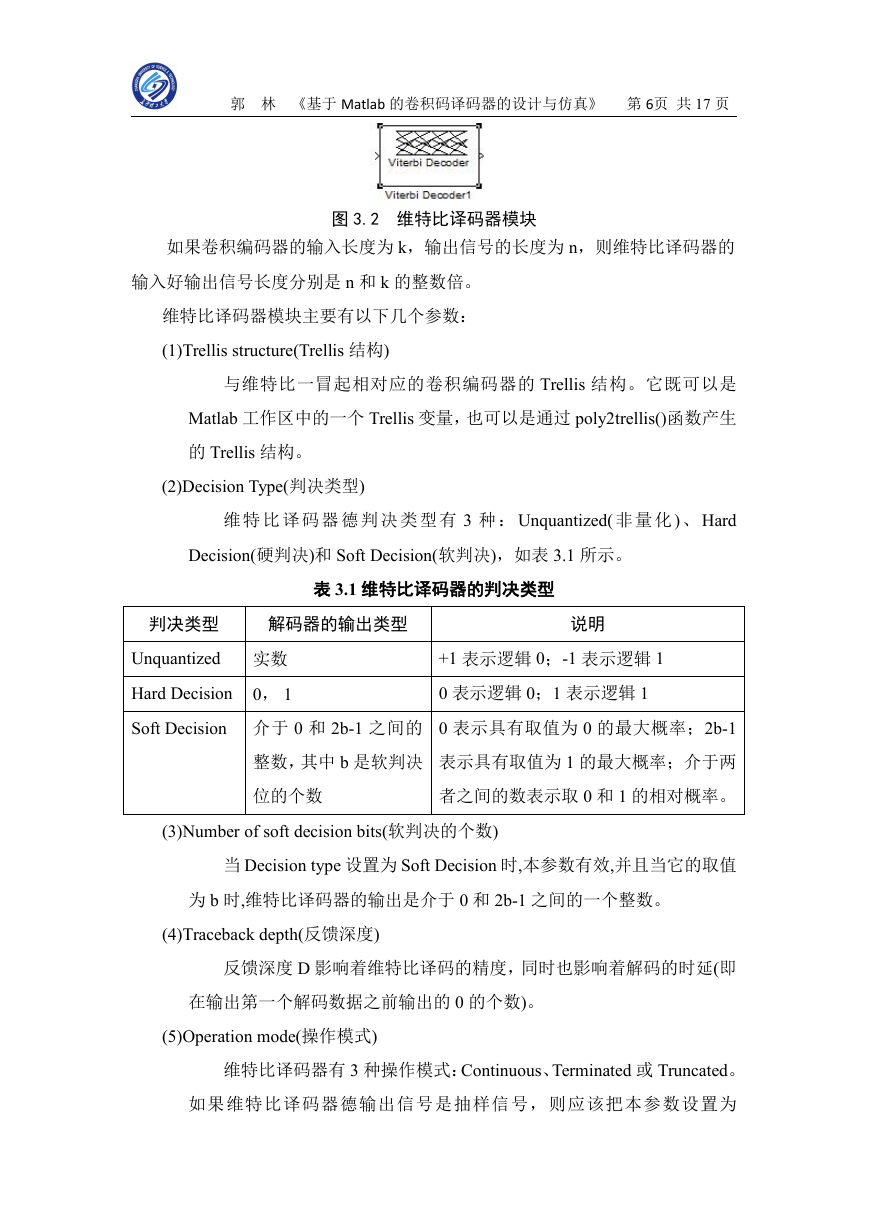

在 Matlab 软件的 Simulink 组件库中包含有的两种卷积码译码模块,即后验

概率卷积译码器和维特比译码器。图 3.1,图 3.2 所示是维特比译码器参数设置

对话框和模块,它通过维特比译码还原出二进制信号序列。

图 3.1 维特比译码器参数设置

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 6页 共 17 页

图 3.2 维特比译码器模块

如果卷积编码器的输入长度为 k,输出信号的长度为 n,则维特比译码器的

输入好输出信号长度分别是 n 和 k 的整数倍。

维特比译码器模块主要有以下几个参数:

(1)Trellis structure(Trellis 结构)

与维特比一冒起相对应的卷积编码器的 Trellis 结构。它既可以是

Matlab 工作区中的一个 Trellis 变量,也可以是通过 poly2trellis()函数产生

的 Trellis 结构。

(2)Decision Type(判决类型)

维 特 比 译 码 器 德 判 决 类 型 有 3 种 :Unquantized( 非 量 化) 、Hard

Decision(硬判决)和 Soft Decision(软判决),如表 3.1 所示。

表 3.1 维特比译码器的判决类型

判决类型

解码器的输出类型

说明

Unquantized 实数

Hard Decision

Soft Decision 介于 0 和 2b-1 之间的

整数,其中 b 是软判决

0, 1

位的个数

+1 表示逻辑 0;-1 表示逻辑 1

0 表示逻辑 0;1 表示逻辑 1

0 表示具有取值为 0 的最大概率;2b-1

表示具有取值为 1 的最大概率;介于两

者之间的数表示取 0 和 1 的相对概率。

(3)Number of soft decision bits(软判决的个数)

当 Decision type 设置为 Soft Decision 时,本参数有效,并且当它的取值

为 b 时,维特比译码器的输出是介于 0 和 2b-1 之间的一个整数。

(4)Traceback depth(反馈深度)

反馈深度 D 影响着维特比译码的精度,同时也影响着解码的时延(即

在输出第一个解码数据之前输出的 0 的个数)。

(5)Operation mode(操作模式)

维特比译码器有 3 种操作模式:Continuous、Terminated 或 Truncated。

如果维特比译码器德输出信号是抽样信号,则应该把本参数设置为

�

郭 林 《基于 Matlab 的卷积码译码器的设计与仿真》 第 7页 共 17 页

Continuous 模式;当输入信号时帧数据时,操作模式可以是 Continuous、

Terminated 或 Truncated。对于 Continuous 模式,维特比译码器在每帧数

据结束时保存译码器的内部状态,用于对下一帧实施解码;在 Truncated

模式下,解码器在每帧数据结束的时候总能恢复到全零状态,它对应于

卷积编码器的 On each frame 复位方式;Terminated 模式适用于卷积编码

器的每帧输入信号的末尾有足够多的零,能够把卷积编码器在完成一帧

数据的编码之后把内部状态恢复为 0。

(6)Enable rest input port(启用复位信号端口)

当 Operation mode 参数设置为 Continuous 并且选中了本选项前面的

复选框之后,维特比译码器增加一个输出信号端口 Rst。同时当 Rst 的输

入信号不等于 0 时,维特比译码器复位到初始状态。[3]

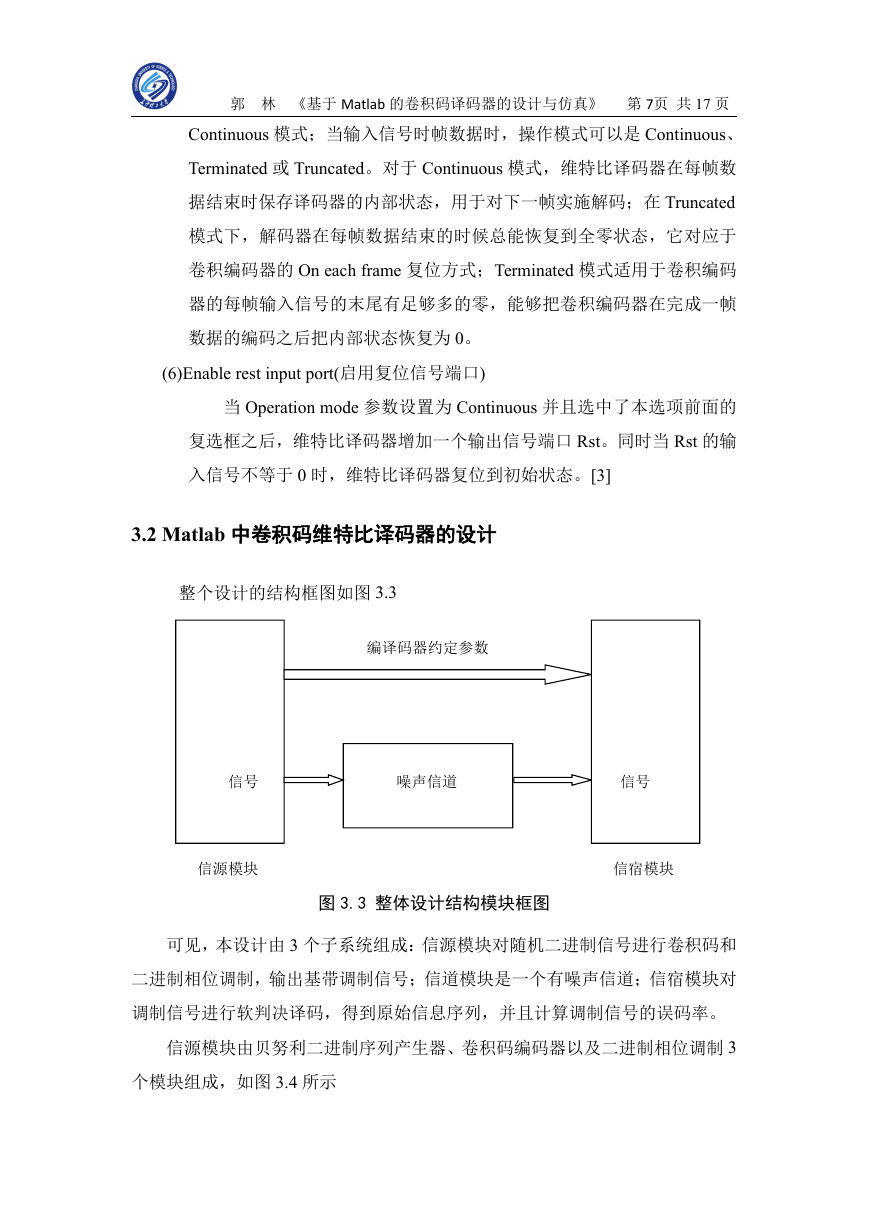

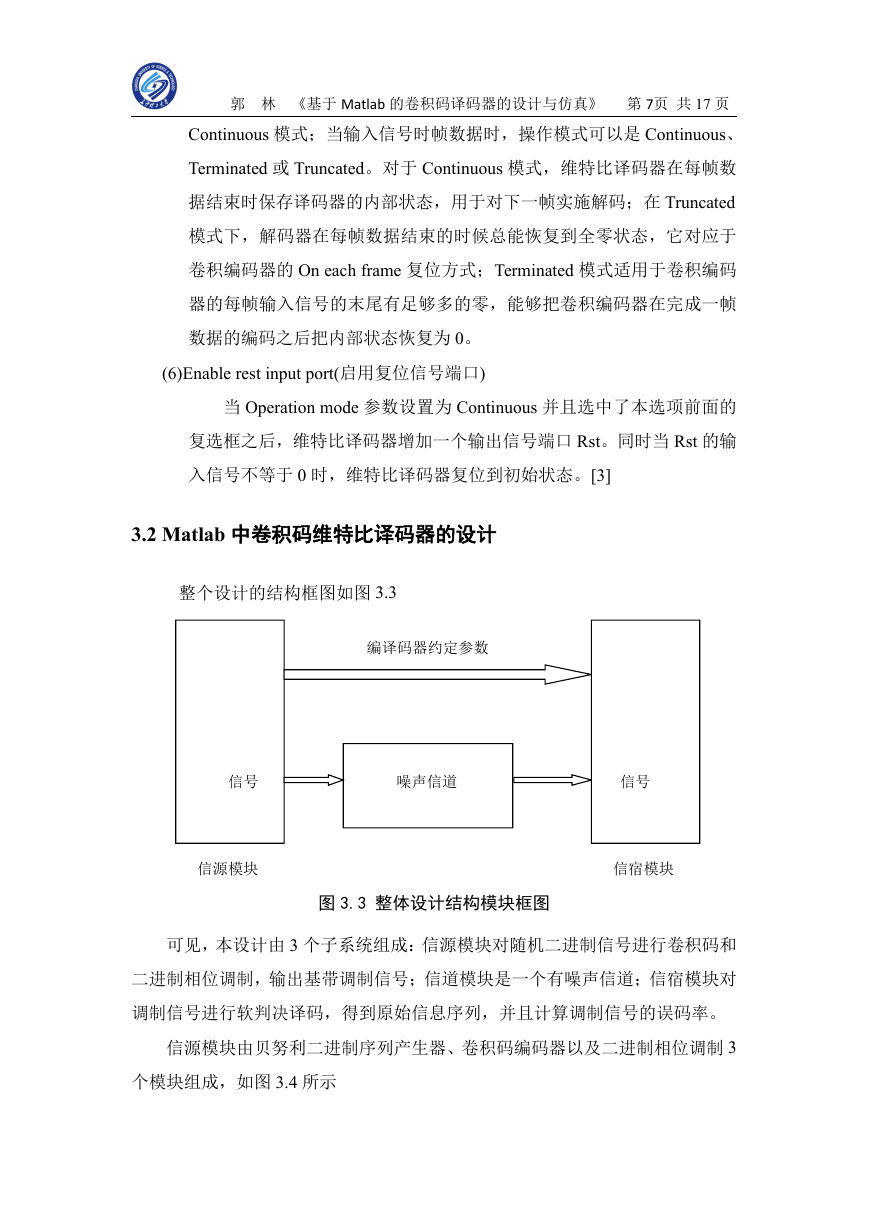

3.2 Matlab 中卷积码维特比译码器的设计

整个设计的结构框图如图 3.3

编译码器约定参数

信号

噪声信道

信号信号

信源模块

信宿模块

图 3.3 整体设计结构模块框图

可见,本设计由 3 个子系统组成:信源模块对随机二进制信号进行卷积码和

二进制相位调制,输出基带调制信号;信道模块是一个有噪声信道;信宿模块对

调制信号进行软判决译码,得到原始信息序列,并且计算调制信号的误码率。

信源模块由贝努利二进制序列产生器、卷积码编码器以及二进制相位调制 3

个模块组成,如图 3.4 所示

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc