....................................................................................................................... 2

10.2.2 DDR3

IP

10.3

UART

DDR3

10.2.1

10.2.3

10.2.4

10.2.5

10.3.1

10.3.2

10.3.3

第

10.1.1 DDR3 IP

10.1.2 DDR3 IP

10.1.3 DDR3 IP

.............................................................................. 41

DDR3

..................................................................................... 23

................................................................................... 24

................................................................................................. 38

................................................................................................. 36

............................................................................................................. 2

............................................................................................................ 16

.............................................................................................................. 3

.............................................................................................................. 2

..................................................................................................................... 46

..................................................................................................................... 42

..................................................................................................................... 41

..................................................................................................................... 28

..................................................................................................................... 23

............................................................................................................................ 2

章

存储最重要

实例篇

核配置与仿真

核概述

核配置

核仿真

基于在线逻辑调试

数据读写

功能概述

控制器

接口时序解析

代码解析

在线逻辑分析仪配置

在线逻辑分析仪调试

批量数据读写

命令的

基于

功能概述

代码解析

板级调试

本章导读本章导读本章导读本章导读 高速时代,越来越高的带宽和数据吞吐量要求,使得用于协助FPGA做大数据缓存的存

储器也必须与时俱进,SDRAM存储器从SDR、DDR、DDR2一路升级,如今已是DDR3甚至DDR4

满天飞的时代。本章通过Xilinx FPGA配置并例化使用DDR3存储器控制器IP核,引领读者

掌握使用FPGA控制DDR3存储器进行基本的开发设计。

目录目录目录目录

10

DDR3

10.1 DDR3 IP

10.2

1

�

第第第第 10 章章章章 存储最重要

存储最重要

存储最重要

存储最重要

DDR3 实例篇实例篇实例篇实例篇

10.1 DDR3 IP 核配置与仿真

核配置与仿真

核配置与仿真

核配置与仿真

10.1.1 DDR3 IP 核概述核概述核概述核概述

本实例对Xilinx Vivado中提供的DDR3控制器IP核模块进行例化,实现基本的DDR3

读写操作。通过IP核自动生成的测试脚本实例实现对DDR3 IP核的仿真。本实例对应工程

文件夹at7_ex17。

DDR3控制器IP核内部模块及其与FPGA逻辑、DDR3芯片的接口框图如图10.1所示。DDR3

控制器包括用户接口(User Interface)模块、存储器控制器(Memory Controller)模块、

初始化和校准(Initialization/Calibration)模块、物理层(Physical Layer)模块。用

户接口模块用于连接FPGA内部逻辑;存储器控制器模块实现DDR3的主要读写时序和数据缓

存交互;初始化和校准模块实现DDR3芯片的上电初始化配置以及时序校准;物理层模块则

实现和DDR3芯片的接口。

图10.1 DDR3控制器IP核

2

�

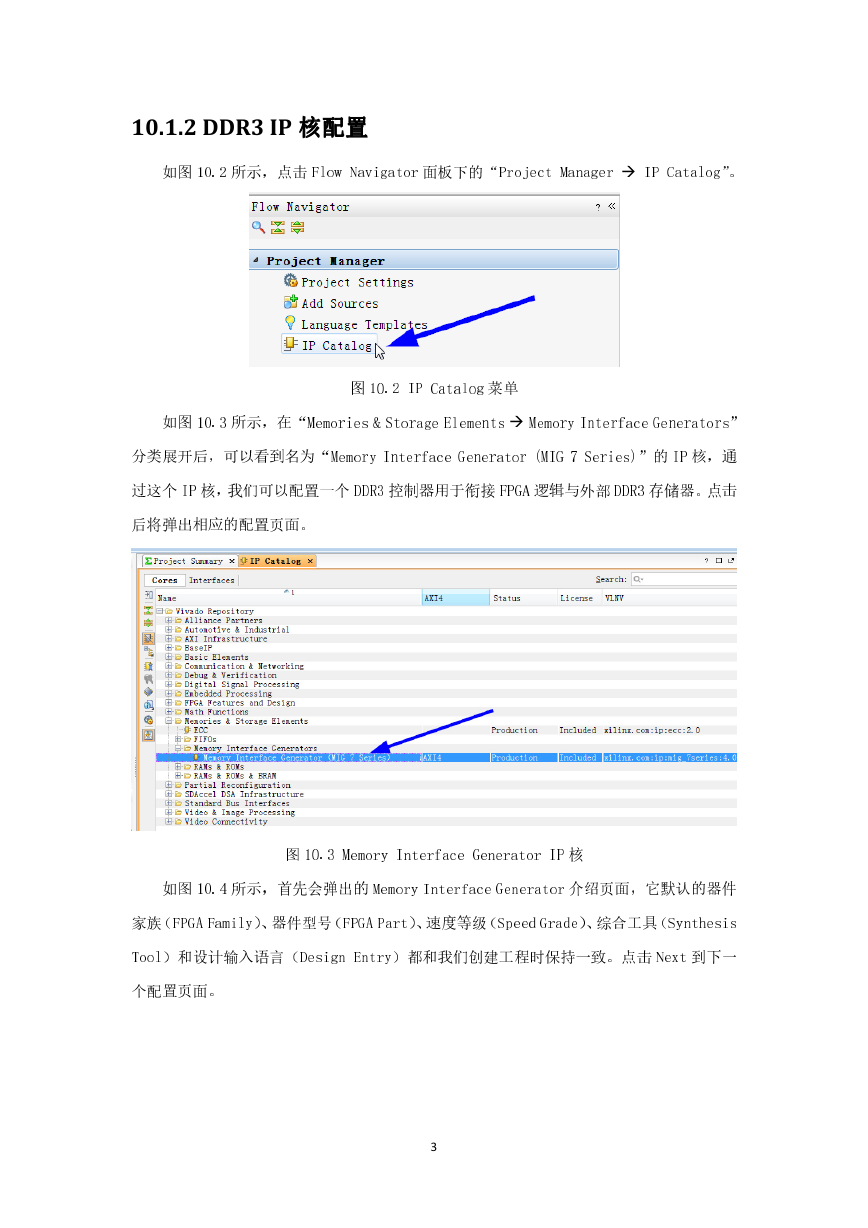

10.1.2 DDR3 IP 核配置核配置核配置核配置

�

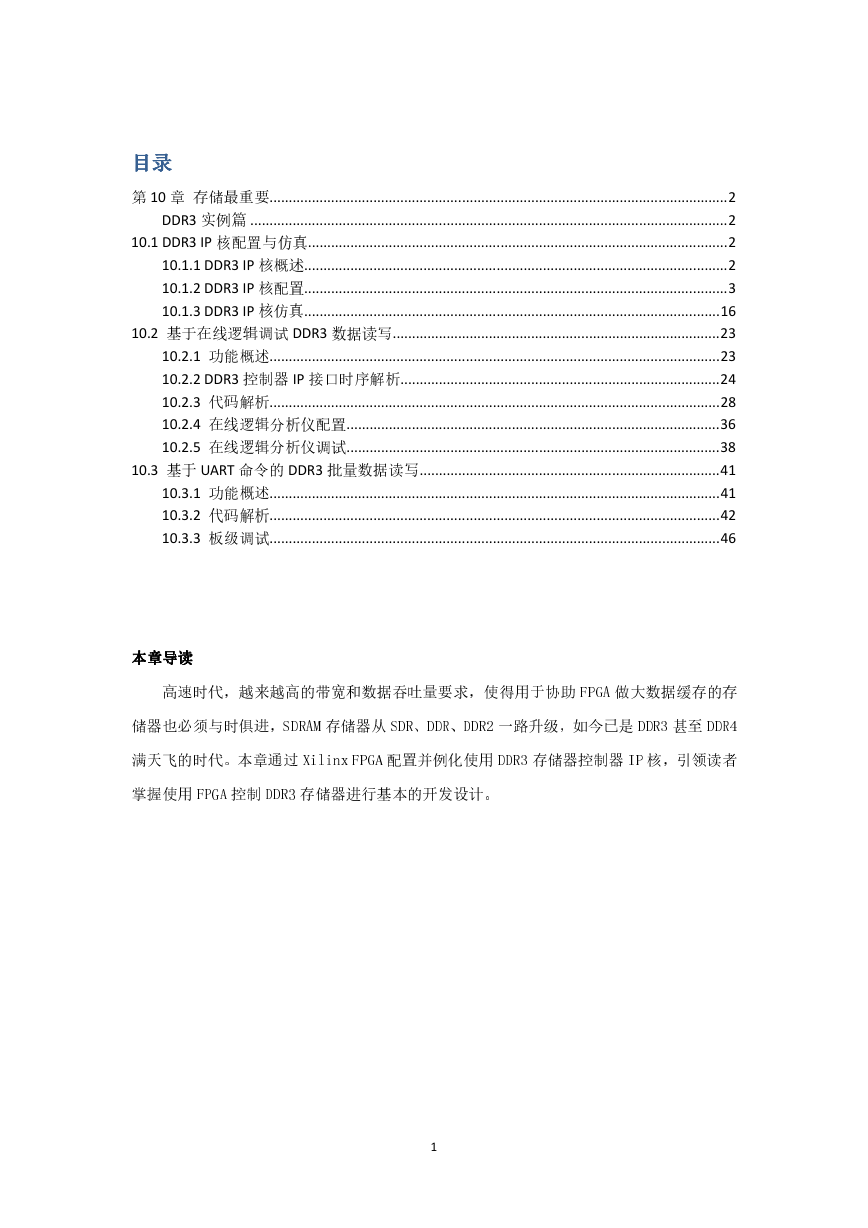

如图10.2所示,点击Flow Navigator面板下的“Project Manager

IP Catalog”。

图10.2 IP Catalog菜单

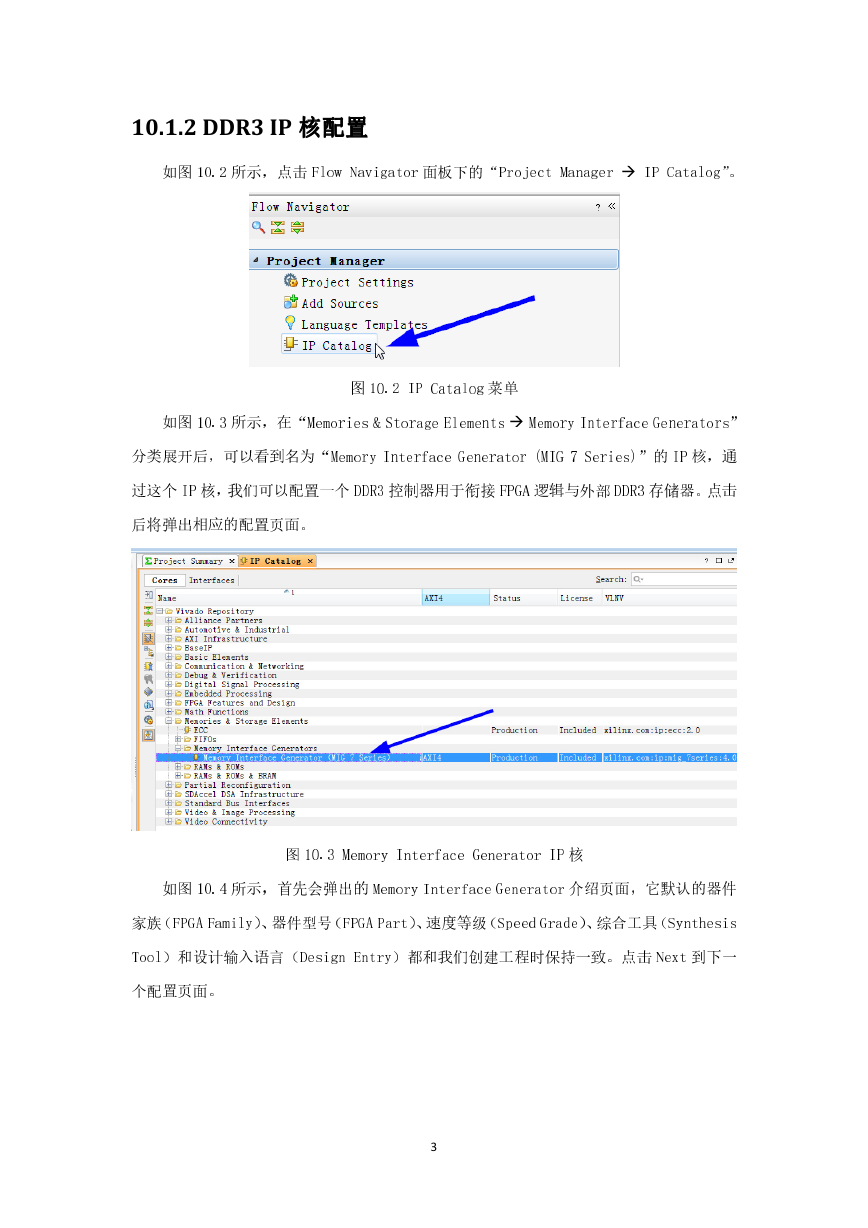

如图10.3所示,在“Memories & Storage Elements

Memory Interface Generators”

分类展开后,可以看到名为“Memory Interface Generator (MIG 7 Series)”的IP核,通

过这个IP核,我们可以配置一个DDR3控制器用于衔接FPGA逻辑与外部DDR3存储器。点击

后将弹出相应的配置页面。

�

图10.3 Memory Interface Generator IP核

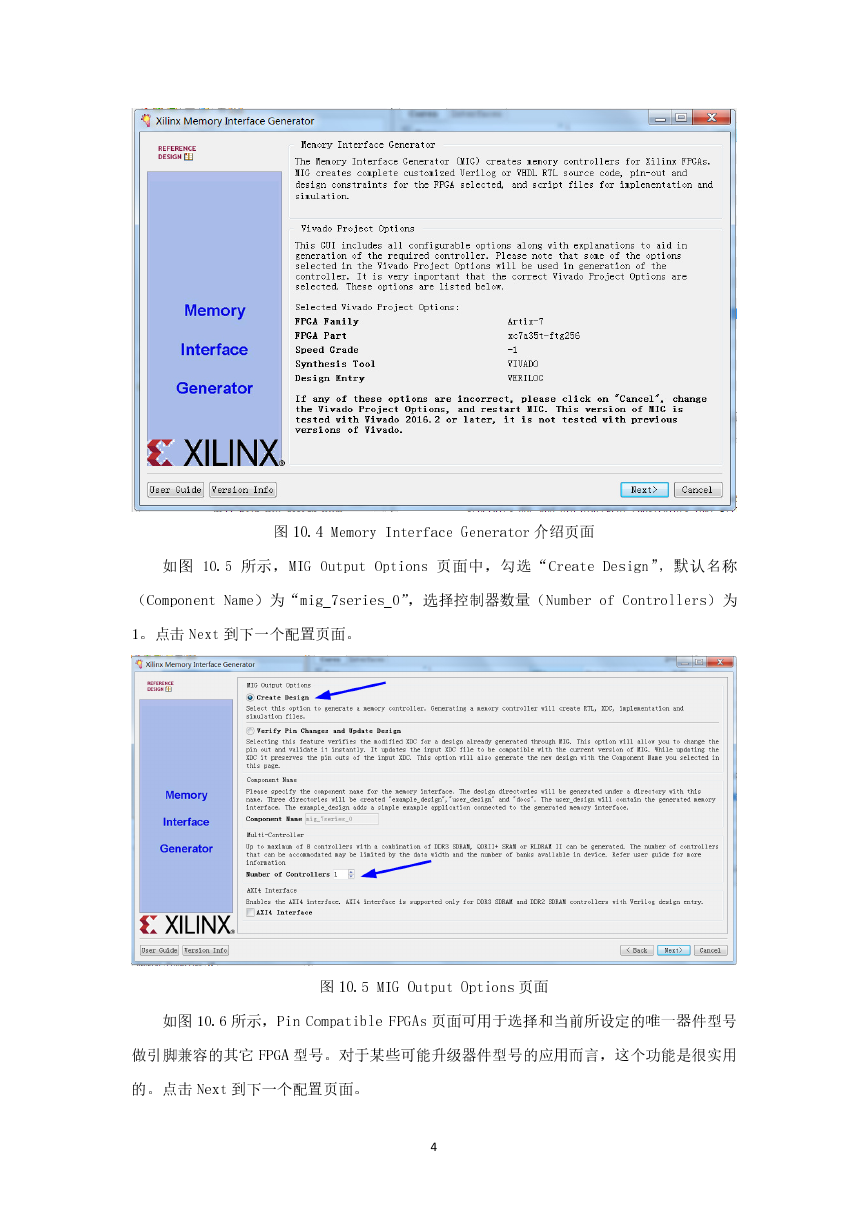

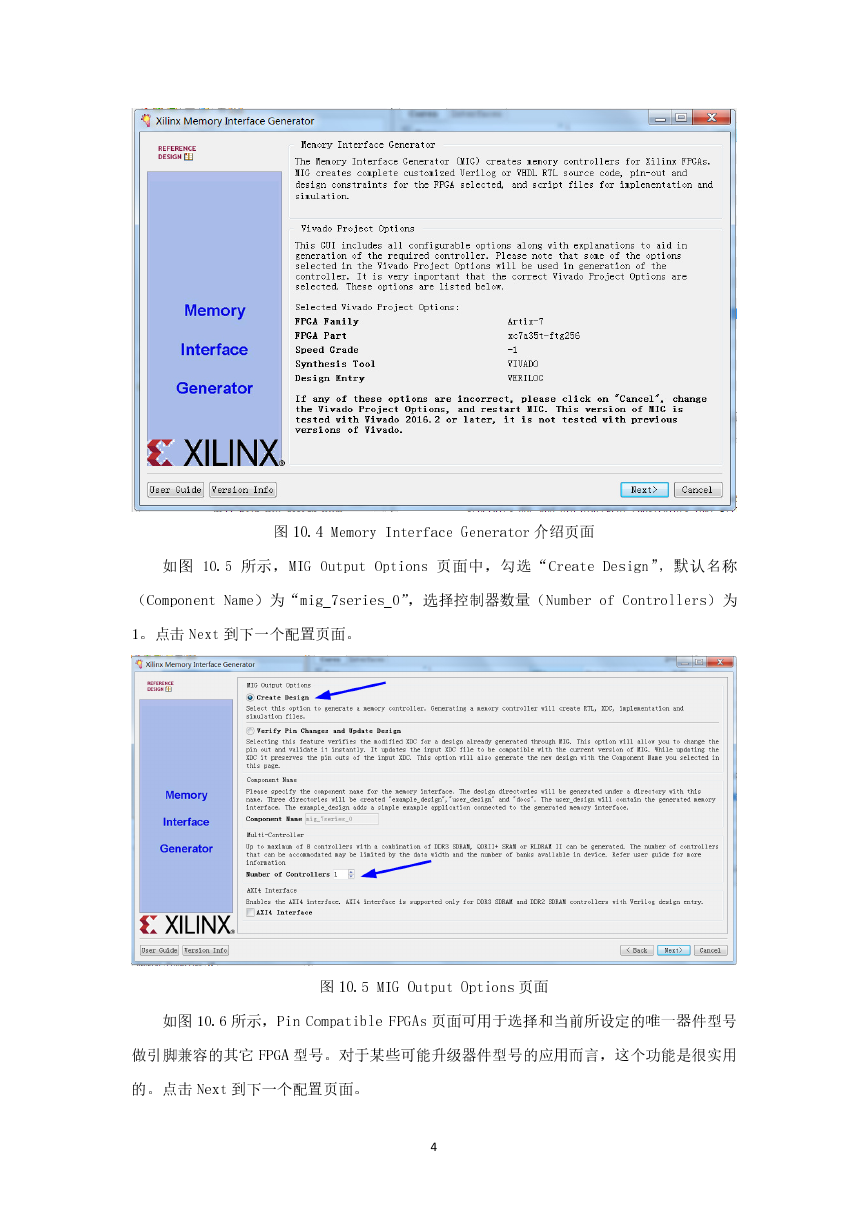

如图10.4所示,首先会弹出的Memory Interface Generator介绍页面,它默认的器件

家族(FPGA Family)、器件型号(FPGA Part)、速度等级(Speed Grade)、综合工具(Synthesis

Tool)和设计输入语言(Design Entry)都和我们创建工程时保持一致。点击Next到下一

个配置页面。

3

�

图10.4 Memory Interface Generator介绍页面

如图10.5所示,MIG Output Options页面中,勾选“Create Design”,默认名称

(Component Name)为“mig_7series_0”,选择控制器数量(Number of Controllers)为

1。点击Next到下一个配置页面。

图10.5 MIG Output Options页面

如图10.6所示,Pin Compatible FPGAs页面可用于选择和当前所设定的唯一器件型号

做引脚兼容的其它FPGA型号。对于某些可能升级器件型号的应用而言,这个功能是很实用

的。点击Next到下一个配置页面。

4

�

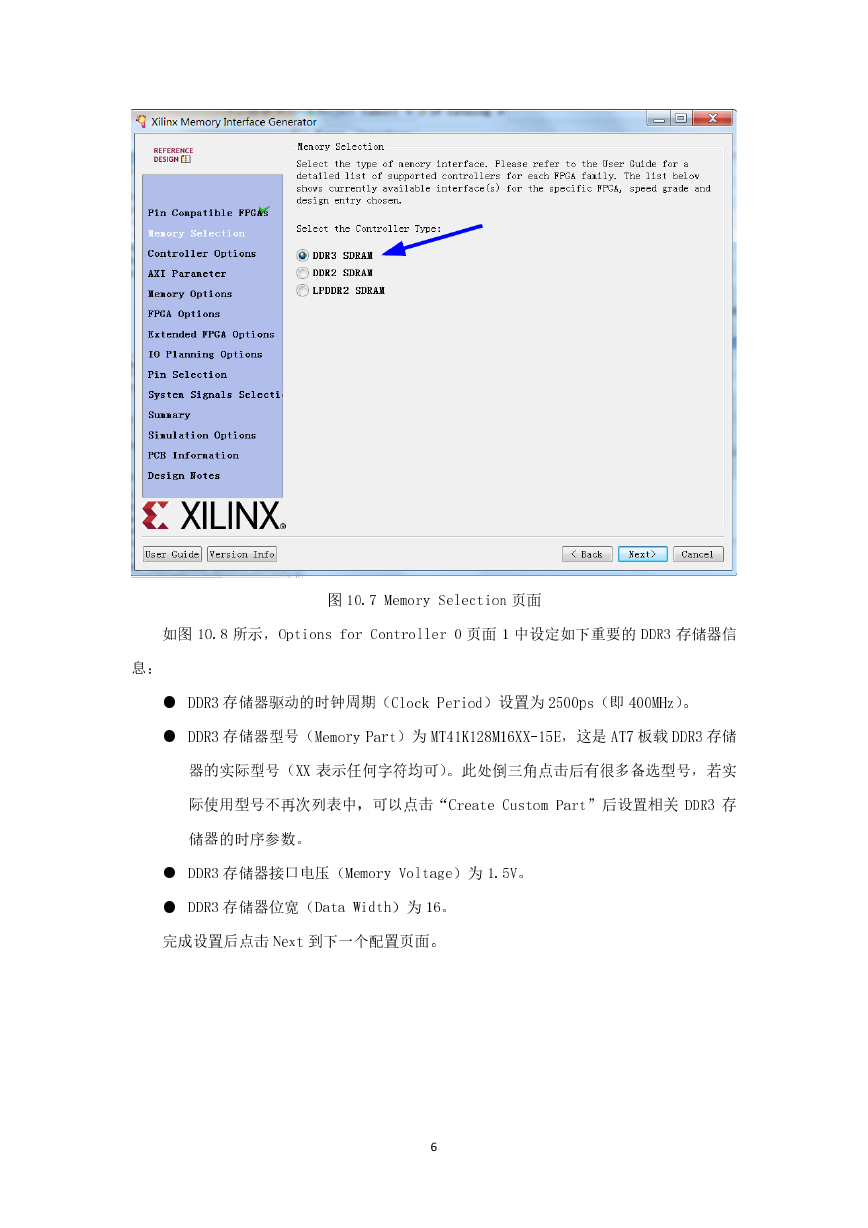

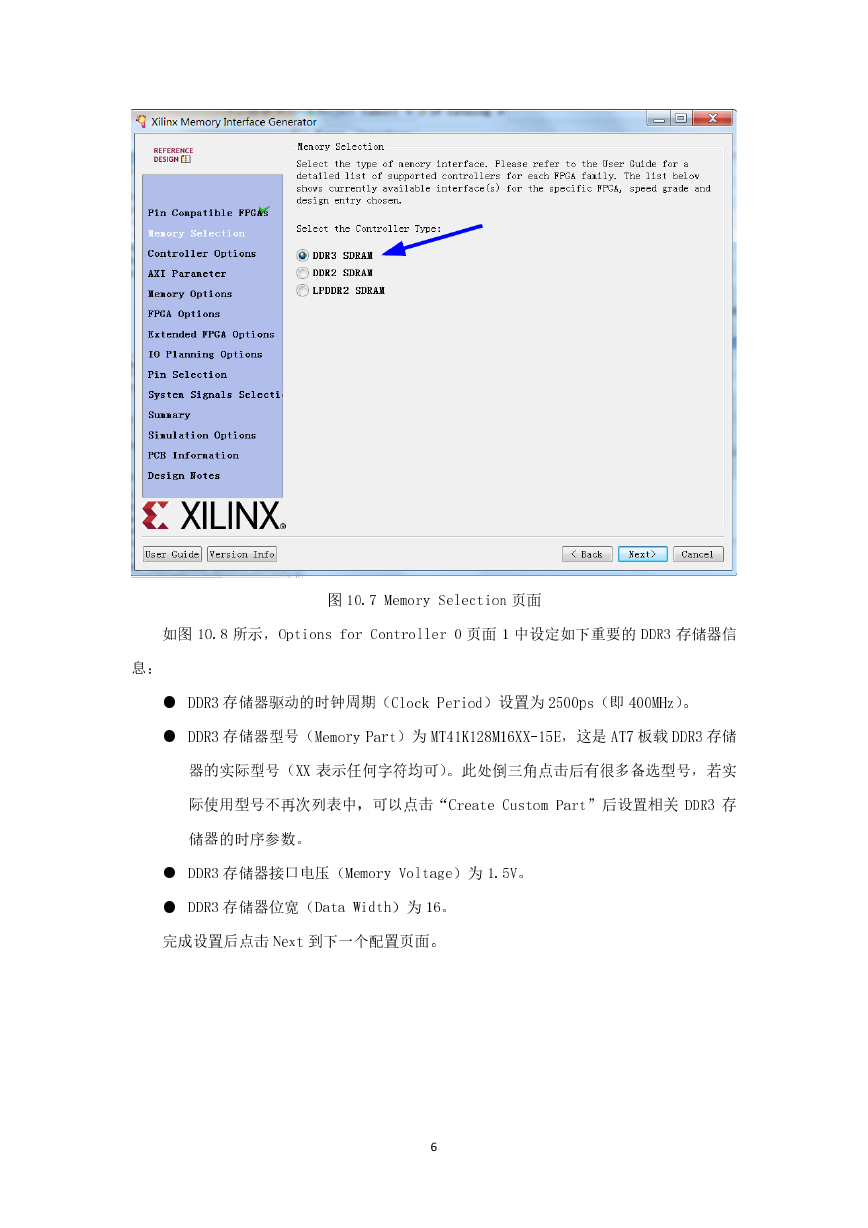

如图10.7所示,Memory Selection页面选择“DDR3 SDRAM”。 点击Next到下一个配

置页面。

图10.6 Pin Compatible FPGAs页面

5

�

图10.7 Memory Selection页面

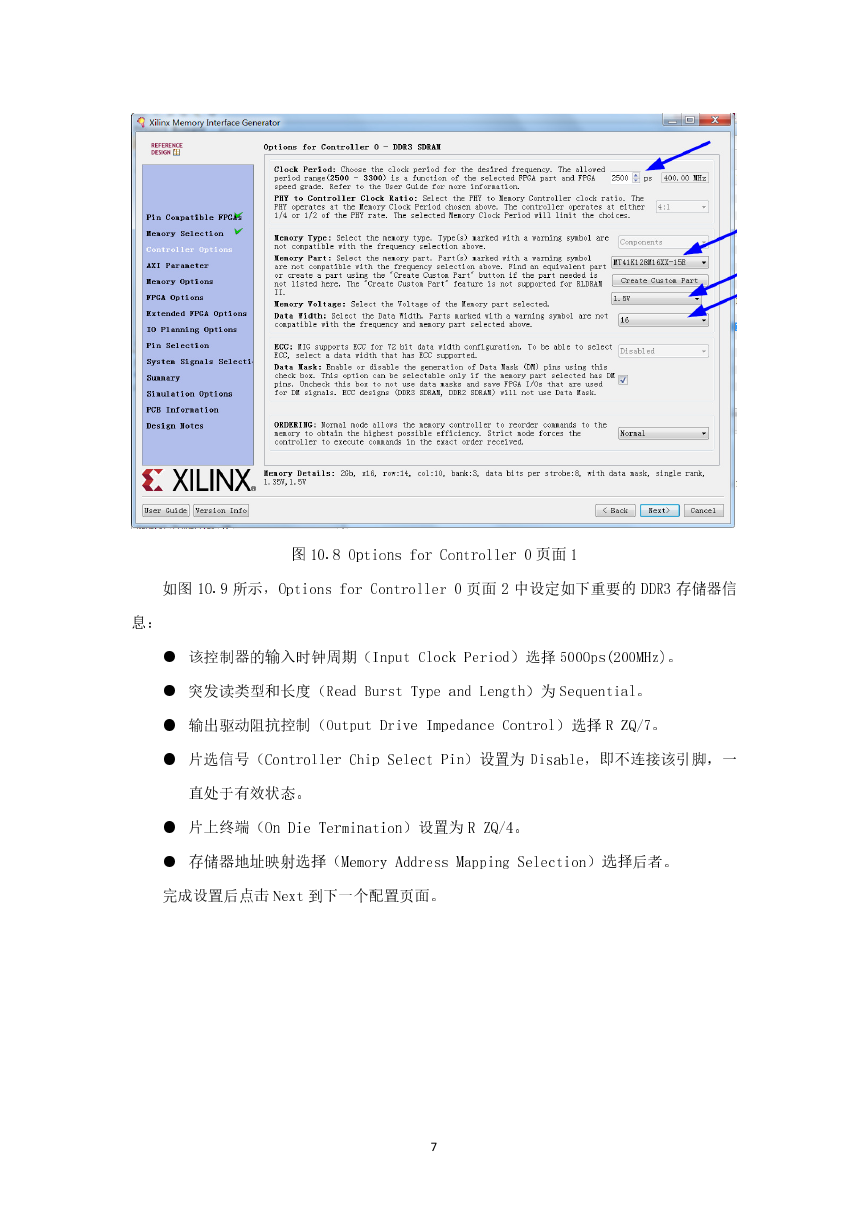

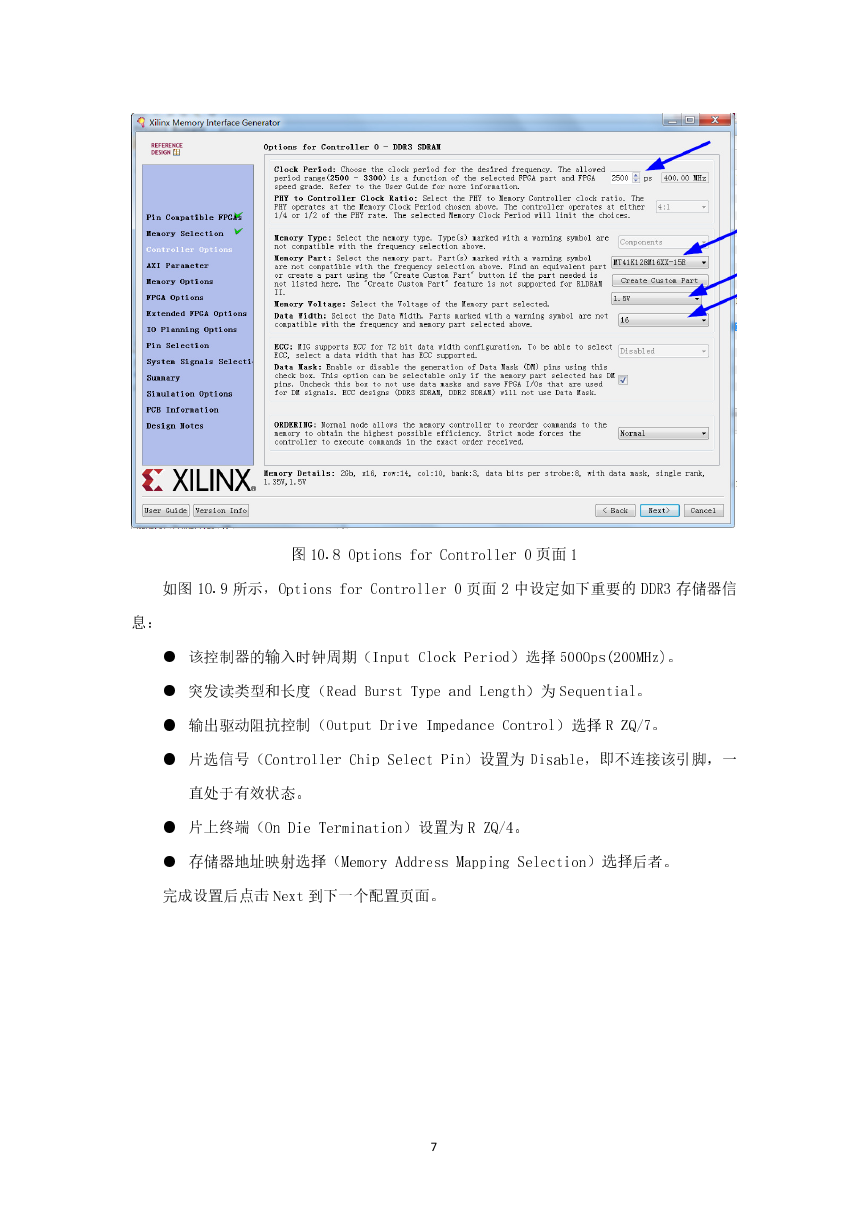

如图10.8所示,Options for Controller 0页面1中设定如下重要的DDR3存储器信

息: ● DDR3存储器驱动的时钟周期(Clock Period)设置为2500ps(即400MHz)。

● DDR3存储器型号(Memory Part)为MT41K128M16XX-15E,这是AT7板载DDR3存储

器的实际型号(XX表示任何字符均可)。此处倒三角点击后有很多备选型号,若实

际使用型号不再次列表中,可以点击“Create Custom Part”后设置相关DDR3存

储器的时序参数。

● DDR3存储器接口电压(Memory Voltage)为1.5V。

● DDR3存储器位宽(Data Width)为16。

完成设置后点击Next到下一个配置页面。

6

�

图10.8 Options for Controller 0页面1

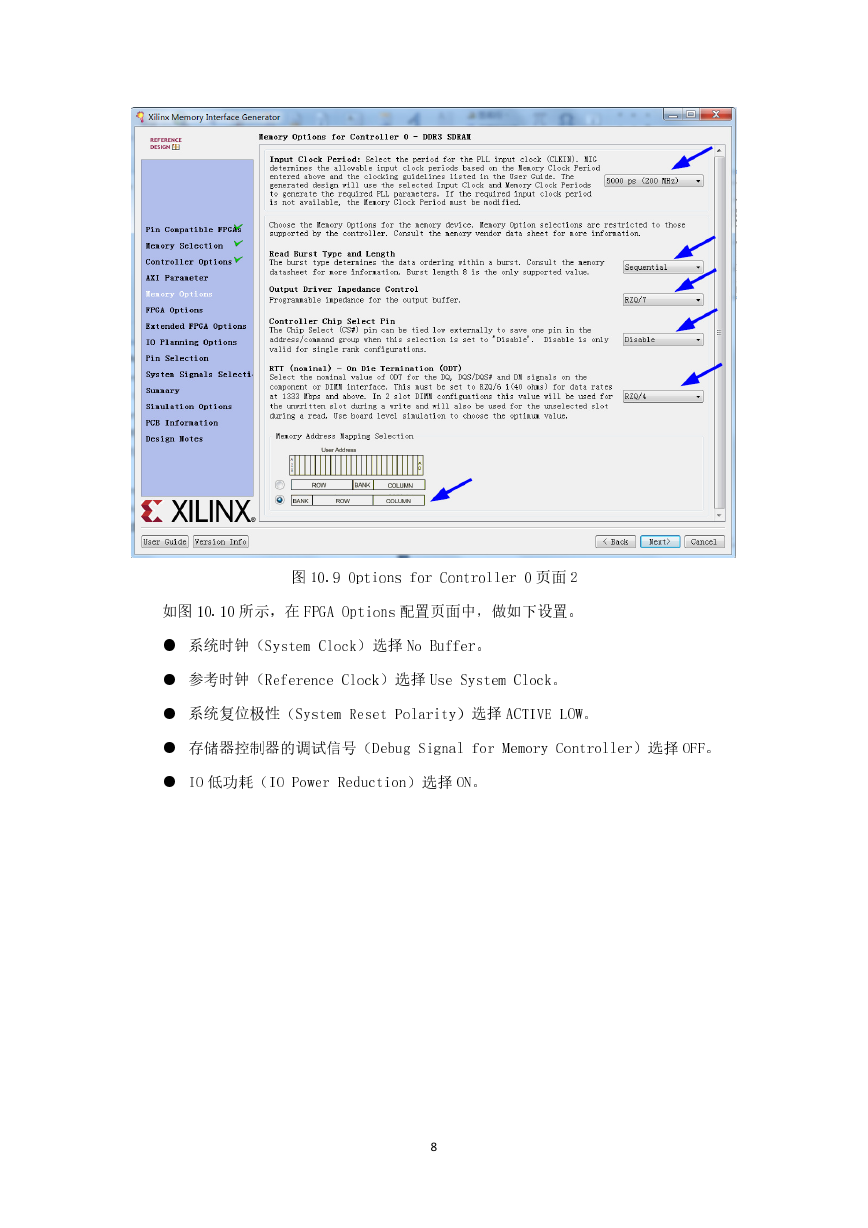

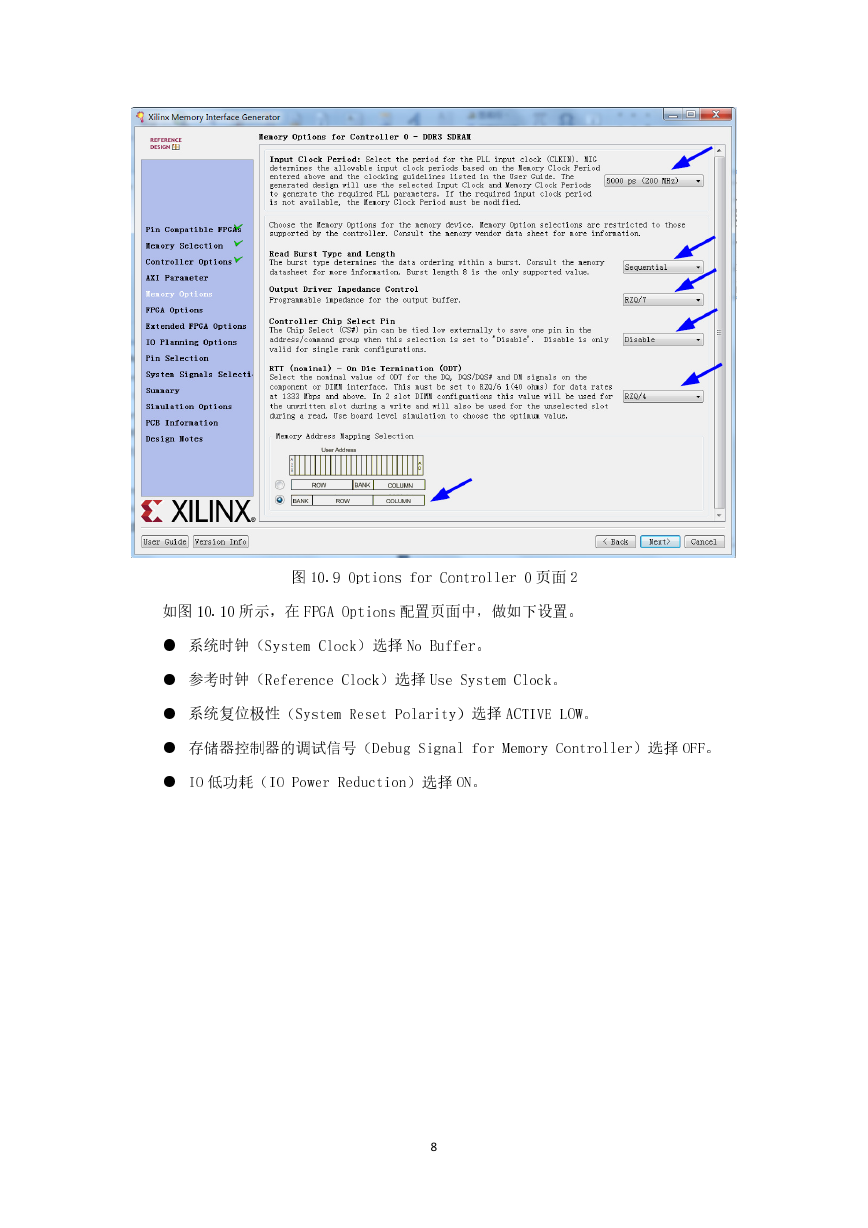

如图10.9所示,Options for Controller 0页面2中设定如下重要的DDR3存储器信

息: ● 该控制器的输入时钟周期(Input Clock Period)选择5000ps(200MHz)。

● 突发读类型和长度(Read Burst Type and Length)为Sequential。

● 输出驱动阻抗控制(Output Drive Impedance Control)选择R ZQ/7。

● 片选信号(Controller Chip Select Pin)设置为Disable,即不连接该引脚,一

直处于有效状态。

● 片上终端(On Die Termination)设置为R ZQ/4。

● 存储器地址映射选择(Memory Address Mapping Selection)选择后者。

完成设置后点击Next到下一个配置页面。

7

�

图10.9 Options for Controller 0页面2

如图10.10所示,在FPGA Options配置页面中,做如下设置。

● 系统时钟(System Clock)选择No Buffer。

● 参考时钟(Reference Clock)选择Use System Clock。

● 系统复位极性(System Reset Polarity)选择ACTIVE LOW。

● 存储器控制器的调试信号(Debug Signal for Memory Controller)选择OFF。

● IO低功耗(IO Power Reduction)选择ON。

8

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc