Cover

Title Page

Copyright Page

Contents

Preface

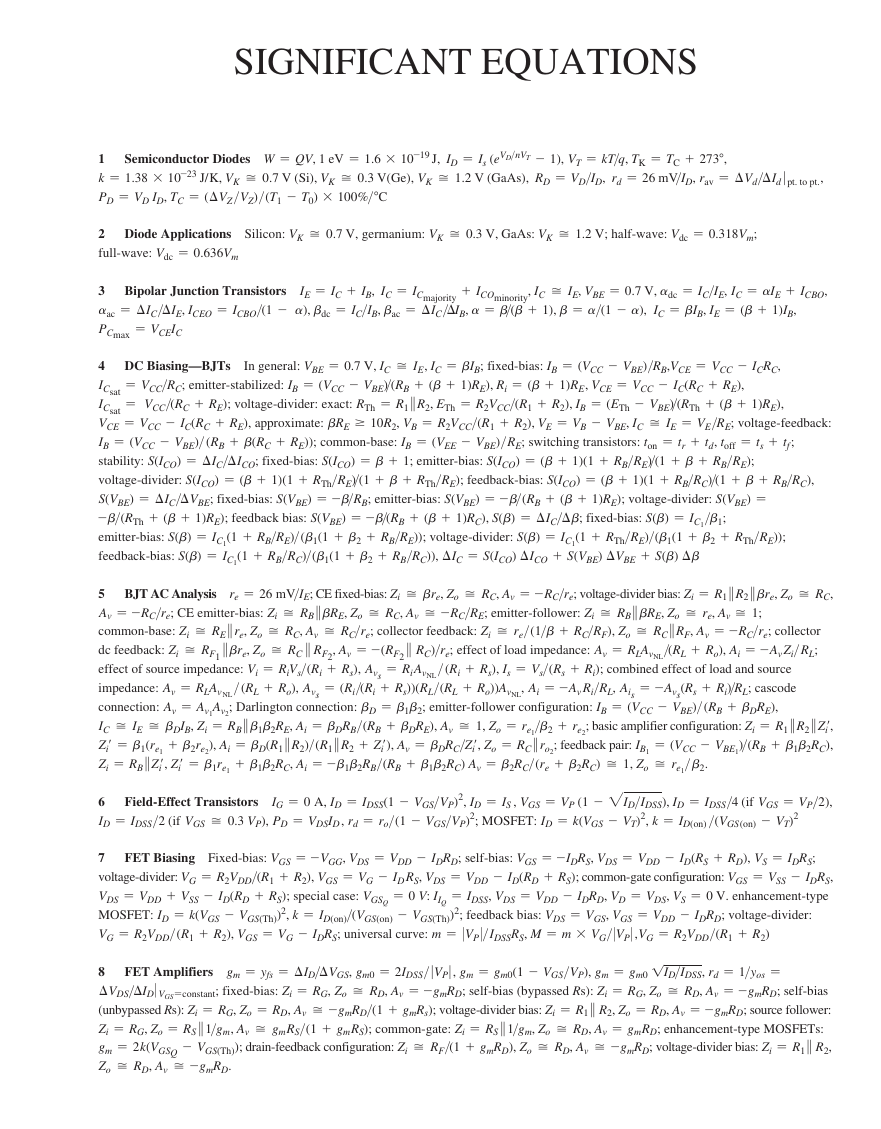

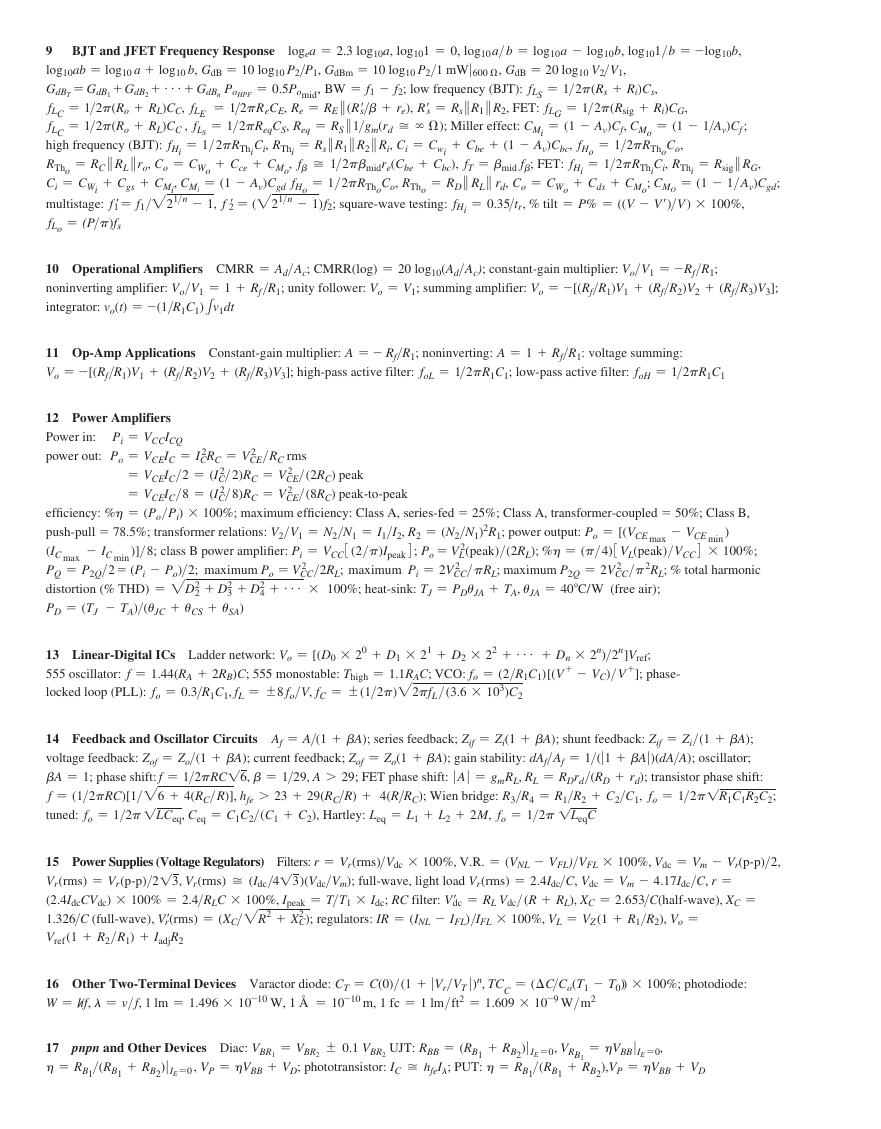

CHAPTER 1: Semiconductor Diodes

1.1 Introduction

1.2 Semiconductor Materials: Ge, Si, and GaAs

1.3 Covalent Bonding and Intrinsic Materials

1.4 Energy Levels

1.5 n-Type and p-Type Materials

1.6 Semiconductor Diode

1.7 Ideal Versus Practical

1.8 Resistance Levels

1.9 Diode Equivalent Circuits

1.10 Transition and Diffusion Capacitance

1.11 Reverse Recovery Time

1.12 Diode Specification Sheets

1.13 Semiconductor Diode Notation

1.14 Diode Testing

1.15 Zener Diodes

1.16 Light-Emitting Diodes

1.17 Summary

1.18 Computer Analysis

CHAPTER 2: Diode Applications

2.1 Introduction

2.2 Load-Line Analysis

2.3 Series Diode Configurations

2.4 Parallel and Series–Parallel Configurations

2.5 AND/OR Gates

2.6 Sinusoidal Inputs; Half-Wave Rectification

2.7 Full-Wave Rectification

2.8 Clippers

2.9 Clampers

2.10 Networks with a dc and ac Source

2.11 Zener Diodes

2.12 Voltage-Multiplier Circuits

2.13 Practical Applications

2.14 Summary

2.15 Computer Analysis

CHAPTER 3: Bipolar Junction Transistors

3.1 Introduction

3.2 Transistor Construction

3.3 Transistor Operation

3.4 Common-Base Configuration

3.5 Common-Emitter Configuration

3.6 Common-Collector Configuration

3.7 Limits of Operation

3.8 Transistor Specification Sheet

3.9 Transistor Testing

3.10 Transistor Casing and Terminal Identification

3.11 Transistor Development

3.12 Summary

3.13 Computer Analysis

CHAPTER 4: DC Biasing—BJTs

4.1 Introduction

4.2 Operating Point

4.3 Fixed-Bias Configuration

4.4 Emitter-Bias Configuration

4.5 Voltage-Divider Bias Configuration

4.6 Collector Feedback Configuration

4.7 Emitter-Follower Configuration

4.8 Common-Base Configuration

4.9 Miscellaneous Bias Configurations

4.10 Summary Table

4.11 Design Operations

4.12 Multiple BJT Networks

4.13 Current Mirrors

4.14 Current Source Circuits

4.15 pnp Transistors

4.16 Transistor Switching Networks

4.17 Troubleshooting Techniques

4.18 Bias Stabilization

4.19 Practical Applications

4.20 Summary

4.21 Computer Analysis

CHAPTER 5: BJT AC Analysis

5.1 Introduction

5.2 Amplification in the AC Domain

5.3 BJT Transistor Modeling

5.4 The r[sub(e)] Transistor Model

5.5 Common-Emitter Fixed-Bias Configuration

5.6 Voltage-Divider Bias

5.7 CE Emitter-Bias Configuration

5.8 Emitter-Follower Configuration

5.9 Common-Base Configuration

5.10 Collector Feedback Configuration

5.11 Collector DC Feedback Configuration

5.12 Effect of R[sub(L)] and R[sub(s)]

5.13 Determining the Current Gain

5.14 Summary Tables

5.15 Two-Port Systems Approach

5.16 Cascaded Systems

5.17 Darlington Connection

5.18 Feedback Pair

5.19 The Hybrid Equivalent Model

5.20 Approximate Hybrid Equivalent Circuit

5.21 Complete Hybrid Equivalent Model

5.22 Hybrid π Model

5.23 Variations of Transistor Parameters

5.24 Troubleshooting

5.25 Practical Applications

5.26 Summary

5.27 Computer Analysis

CHAPTER 6: Field-Effect Transistors

6.1 Introduction

6.2 Construction and Characteristics of JFETs

6.3 Transfer Characteristics

6.4 Specification Sheets (JFETs)

6.5 Instrumentation

6.6 Important Relationships

6.7 Depletion-Type MOSFET

6.8 Enhancement-Type MOSFET

6.9 MOSFET Handling

6.10 VMOS and UMOS Power and MOSFETs

6.11 CMOS

6.12 MESFETs

6.13 Summary Table

6.14 Summary

6.15 Computer Analysis

CHAPTER 7: FET Biasing

7.1 Introduction

7.2 Fixed-Bias Configuration

7.3 Self-Bias Configuration

7.4 Voltage-Divider Biasing

7.5 Common-Gate Configuration

7.6 Special Case V[Sub(GS)][Sub(Q)] = 0 V

7.7 Depletion-Type MOSFETs

7.8 Enhancement-Type MOSFETs

7.9 Summary Table

7.10 Combination Networks

7.11 Design

7.12 Troubleshooting

7.13 p-Channel FETs

7.14 Universal JFET Bias Curve

7.15 Practical Applications

7.16 Summary

7.17 Computer Analysis

CHAPTER 8: FET Amplifiers

8.1 Introduction

8.2 JFET Small-Signal Model

8.3 Fixed-Bias Configuration

8.4 Self-Bias Configuration

8.5 Voltage-Divider Configuration

8.6 Common-Gate Configuration

8.7 Source-Follower (Common-Drain) Configuration

8.8 Depletion-Type MOSFETs

8.9 Enhancement-Type MOSFETs

8.10 E-MOSFET Drain-Feedback Configuration

8.11 E-MOSFET Voltage-Divider Configuration

8.12 Designing FET Amplifier Networks

8.13 Summary Table

8.14 Effect of R[sub(L)] and R[sub(sig)]

8.15 Cascade Configuration

8.16 Troubleshooting

8.17 Practical Applications

8.18 Summary

8.19 Computer Analysis

CHAPTER 9: BJT and JFET Frequency Response

9.1 Introduction

9.2 Logarithms

9.3 Decibels

9.4 General Frequency Considerations

9.5 Normalization Process

9.6 Low-Frequency Analysis—Bode Plot

9.7 Low-Frequency Response—BJT Amplifier with R[sub(L)]

9.8 Impact of R[sub(s)] on the BJT Low-Frequency Response

9.9 Low-Frequency Response—FET Amplifier

9.10 Miller Effect Capacitance

9.11 High-Frequency Response—BJT Amplifier

9.12 High-Frequency Response—FET Amplifier

9.13 Multistage Frequency Effects

9.14 Square-Wave Testing

9.15 Summary

9.16 Computer Analysis

CHAPTER 10: Operational Amplifiers

10.1 Introduction

10.2 Differential Amplifier Circuit

10.3 BiFET, BiMOS, and CMOS Differential Amplifier Circuits

10.4 Op-Amp Basics

10.5 Practical Op-Amp Circuits

10.6 Op-Amp Specifications—DC Offset Parameters

10.7 Op-Amp Specifications—Frequency Parameters

10.8 Op-Amp Unit Specifications

10.9 Differential and Common-Mode Operation

10.10 Summary

10.11 Computer Analysis

CHAPTER 11: Op-Amp Applications

11.1 Constant-Gain Multiplier

11.2 Voltage Summing

11.3 Voltage Buffer

11.4 Controlled Sources

11.5 Instrumentation Circuits

11.6 Active Filters

11.7 Summary

11.8 Computer Analysis

CHAPTER 12: Power Amplifiers

12.1 Introduction—Definitions and Amplifier Types

12.2 Series-Fed Class A Amplifier

12.3 Transformer-Coupled Class A Amplifier

12.4 Class B Amplifier Operation

12.5 Class B Amplifier Circuits

12.6 Amplifier Distortion

12.7 Power Transistor Heat Sinking

12.8 Class C and Class D Amplifiers

12.9 Summary

12.10 Computer Analysis

CHAPTER 13: Linear-Digital ICs

13.1 Introduction

13.2 Comparator Unit Operation

13.3 Digital–Analog Converters

13.4 Timer IC Unit Operation

13.5 Voltage-Controlled Oscillator

13.6 Phase-Locked Loop

13.7 Interfacing Circuitry

13.8 Summary

13.9 Computer Analysis

CHAPTER 14: Feedback and Oscillator Circuits

14.1 Feedback Concepts

14.2 Feedback Connection Types

14.3 Practical Feedback Circuits

14.4 Feedback Amplifier—Phase and Frequency Considerations

14.5 Oscillator Operation

14.6 Phase-Shift Oscillator

14.7 Wien Bridge Oscillator

14.8 Tuned Oscillator Circuit

14.9 Crystal Oscillator

14.10 Unijunction Oscillator

14.11 Summary

14.12 Computer Analysis

CHAPTER 15: Power Supplies (Voltage Regulators)

15.1 Introduction

15.2 General Filter Considerations

15.3 Capacitor Filter

15.4 RC Filter

15.5 Discrete Transistor Voltage Regulation

15.6 IC Voltage Regulators

15.7 Practical Applications

15.8 Summary

15.9 Computer Analysis

CHAPTER 16: Other Two-Terminal Devices

16.1 Introduction

16.2 Schottky Barrier (Hot-Carrier) Diodes

16.3 Varactor (Varicap) Diodes

16.4 Solar Cells

16.5 Photodiodes

16.6 Photoconductive Cells

16.7 IR Emitters

16.8 Liquid-Crystal Displays

16.9 Thermistors

16.10 Tunnel Diodes

16.11 Summary

CHAPTER 17: pnpn and Other Devices

17.1 Introduction

17.2 Silicon-Controlled Rectifier

17.3 Basic Silicon-Controlled Rectifier Operation

17.4 SCR Characteristics and Ratings

17.5 SCR Applications

17.6 Silicon-Controlled Switch

17.7 Gate Turn-Off Switch

17.8 Light-Activated SCR

17.9 Shockley Diode

17.10 Diac

17.11 Triac

17.12 Unijunction Transistor

17.13 Phototransistors

17.14 Opto-Isolators

17.15 Programmable Unijunction Transistor

17.16 Summary

Appendix A: Hybrid Parameters—Graphical Determinations and Conversion Equations (Exact and Approximate)

A.1 Graphical Determination of the h-Parameters

A.2 Exact Conversion Equations

A.3 Approximate Conversion Equations

Appendix B: Ripple Factor and Voltage Calculations

B.1 Ripple Factor of Rectifier

B.2 Ripple Voltage of Capacitor Filter

B.3 Relation of V[sub(dc)] and V[sub(m)] to Ripple r

B.4 Relation of V[sub(r)](rms) and V[sub(m)] to Ripple r

B.5 Relation Connecting Conduction Angle, Percentage Ripple, and I[sub(peak)] /I[sub(dc)] for Rectifier-Capacitor Filter Circuits

Appendix C: Charts and Tables

Appendix D: Solutions to Selected Odd-Numbered Problems

Index

A

B

C

D

E

F

G

H

I

J

K

L

M

N

O

P

Q

R

S

T

U

V

W

Z

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc