SD Specifications

Part 1

UHS-II Simplified Addendum

Version 1.02

July 25, 2018

Addendum to:

SD Specifications

Part 1 Physical Layer Simplified Specification

Version 6.00 July 25, 2018, or later

Technical Committee

SD Card Association

�

©Copyright 2010-2018 SD Card Association

UHS-II Simplified Addendum Version 1.02

Revision History

Date

Version

Changes compared to previous issue

November 8, 2013

1.01

May 28, 2014

July 25, 2018

1.02

1.02

The first release of UHS-II Simplified Addendum

(Created by the UHS-II Addendum Version 1.01)

Fixed Section number from 3.2 to 3.5

Revised Disclaimers

i

�

UHS-II Simplified Addendum Version 1.02

Release of SD Simplified Specification/Addendum

The following conditions apply to the release of the SD Simplified Specification/Addendum by the SD

Card Association. The Simplified Specification/Addendum is a subset of the complete version of SD

Specification/Addendum which is owned by the SD Card Association.

©Copyright 2010-2018 SD Card Association

Conditions for publication

Publisher and Copyright Holder:

SD Card Association

2400 Camino Ramon, Suite 375

San Ramon, CA 94583 USA

Telephone: +1 (925) 275-6615,

Fax: +1 (925) 886-4870

E-mail: help@sdcard.org

Disclaimers

is made available by

This Simplified Specification

the SD Card Association (the “SDA”) at

https://www.sdcard.org/downloads/pls/index.html (the “Site”) and your access to and/or use of this Simplified

Specification is subject to the SIMPLIFIED SPECIFICATION TERMS AND CONDITIONS (the “Terms”) that

are displayed by clicking the "Download" button at https://www.sdcard.org/downloads/pls/index.html.

If you are viewing or have accessed this Simplified Specification via any source, medium, or in any other

way other than directly from the Site pursuant your acceptance of the Terms, then your access to, viewing

of, and/or use of the Simplified Specification is in violation of the SDA’s and its licensors’ intellectual property

rights. Accordingly, unless obtained directly from the Site pursuant to the Terms, immediately cease and

desist all viewing, using, or accessing the Simplified Specification; destroy any copies of the Simplified

Specification in your possession, custody or control; and, if you desire access to the Simplified Specification,

proceed to the Site to obtain access and use of the Simplified Specification in an authorized manner

pursuant to the Terms.

Distribution of the Simplified Specification, other than through the Site, is a violation of the Terms and the

intellectual property rights of the SDA and its licensors. The only rights granted in the Simplified Specification

are those expressly granted in the Terms. All rights not expressly granted pursuant to your acceptance of the

Terms are reserved to the SDA and its licensors. Notice is also hereby provided that notwithstanding any

rights granted by the Terms, any implementation of the Simplified Specifications or any portions thereof may

require a separate license from the SDA, SD Group, SD-3C, LLC or other third parties.

ii

�

©Copyright 2010-2018 SD Card Association

UHS-II Simplified Addendum Version 1.02

Conventions Used in This Document

Naming Conventions

Some terms are capitalized to distinguish their definition from their common English meaning. Words

not capitalized have their common English meaning.

Numbers and Number Bases

Hexadecimal numbers are written with a lower case "h" suffix, e.g., FFFFh and 80h.

Binary numbers are written with a lower case "b" suffix (e.g., 10b).

Binary numbers larger than four digits are written with a space dividing each group of four digits, as

in 1000 0101 0010b.

All other numbers are decimal.

Key Words

May:

Shall:

Should:

Indicates flexibility of choice with no implied recommendation or requirement.

Indicates a mandatory requirement. Designers shall

requirements to ensure interchangeability and to claim conformance with the specification.

Indicates a strong recommendation but not a mandatory requirement. Designers should

give strong consideration to such recommendations, but there is still a choice in

implementation.

implement such mandatory

Application Notes

Some sections of this document provide guidance to the host implementers as follows:

Application Note:

This is an example of an application note.

iii

�

UHS-II Simplified Addendum Version 1.02

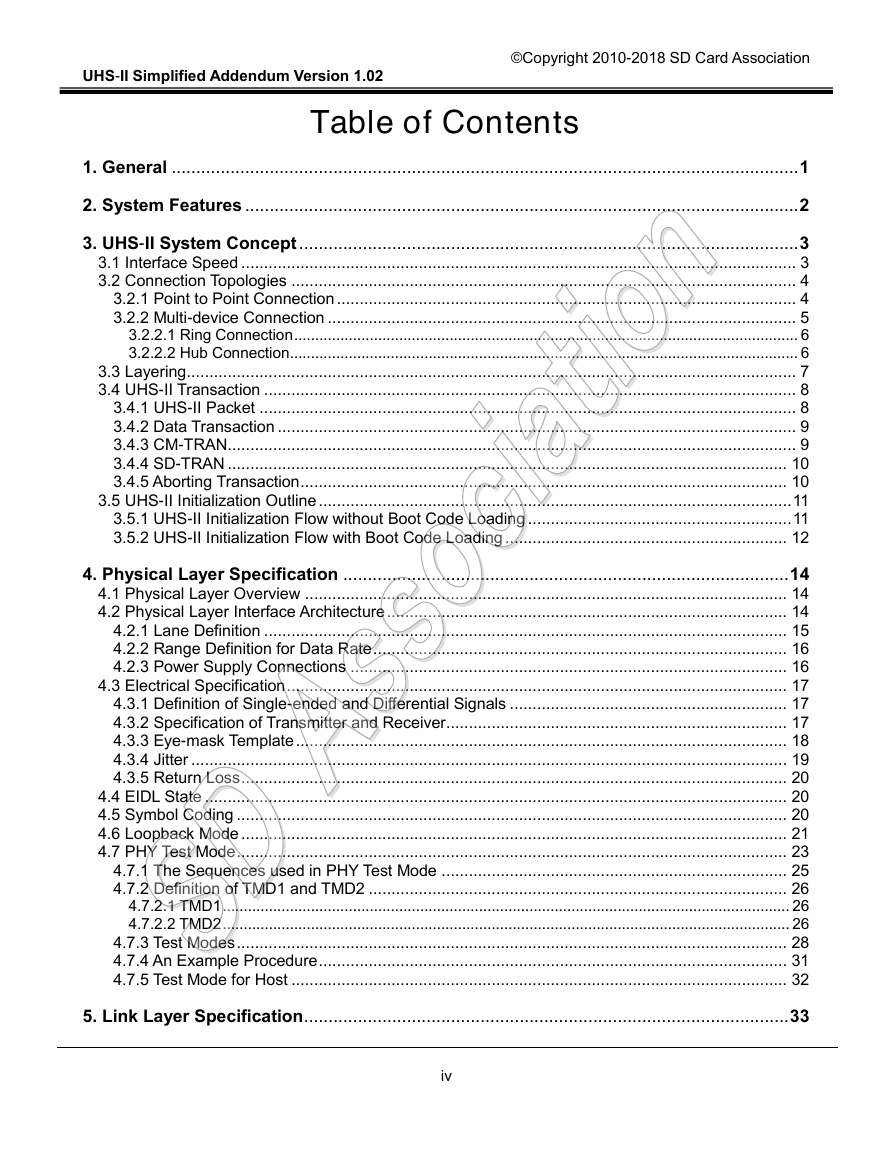

Table of Contents

©Copyright 2010-2018 SD Card Association

1. General ................................................................................................................................ 1

2. System Features ................................................................................................................. 2

3. UHS-II System Concept ...................................................................................................... 3

3.1 Interface Speed .......................................................................................................................... 3

3.2 Connection Topologies ............................................................................................................... 4

3.2.1 Point to Point Connection ..................................................................................................... 4

3.2.2 Multi-device Connection ....................................................................................................... 5

3.2.2.1 Ring Connection ........................................................................................................................ 6

3.2.2.2 Hub Connection ......................................................................................................................... 6

3.3 Layering ...................................................................................................................................... 7

3.4 UHS-II Transaction ..................................................................................................................... 8

3.4.1 UHS-II Packet ...................................................................................................................... 8

3.4.2 Data Transaction .................................................................................................................. 9

3.4.3 CM-TRAN ............................................................................................................................. 9

3.4.4 SD-TRAN ........................................................................................................................... 10

3.4.5 Aborting Transaction ........................................................................................................... 10

3.5 UHS-II Initialization Outline ........................................................................................................ 11

3.5.1 UHS-II Initialization Flow without Boot Code Loading .......................................................... 11

3.5.2 UHS-II Initialization Flow with Boot Code Loading .............................................................. 12

4. Physical Layer Specification ........................................................................................... 14

4.1 Physical Layer Overview .......................................................................................................... 14

4.2 Physical Layer Interface Architecture ........................................................................................ 14

4.2.1 Lane Definition ................................................................................................................... 15

4.2.2 Range Definition for Data Rate ........................................................................................... 16

4.2.3 Power Supply Connections ................................................................................................ 16

4.3 Electrical Specification .............................................................................................................. 17

4.3.1 Definition of Single-ended and Differential Signals ............................................................. 17

4.3.2 Specification of Transmitter and Receiver........................................................................... 17

4.3.3 Eye-mask Template ............................................................................................................ 18

4.3.4 Jitter ................................................................................................................................... 19

4.3.5 Return Loss ........................................................................................................................ 20

4.4 EIDL State ................................................................................................................................ 20

4.5 Symbol Coding ......................................................................................................................... 20

4.6 Loopback Mode ........................................................................................................................ 21

4.7 PHY Test Mode ......................................................................................................................... 23

4.7.1 The Sequences used in PHY Test Mode ............................................................................ 25

4.7.2 Definition of TMD1 and TMD2 ............................................................................................ 26

4.7.2.1 TMD1 ....................................................................................................................................... 26

4.7.2.2 TMD2 ....................................................................................................................................... 26

4.7.3 Test Modes ......................................................................................................................... 28

4.7.4 An Example Procedure ....................................................................................................... 31

4.7.5 Test Mode for Host ............................................................................................................. 32

5. Link Layer Specification ................................................................................................... 33

iv

�

©Copyright 2010-2018 SD Card Association

UHS-II Simplified Addendum Version 1.02

5.1 Link Layer Overview ................................................................................................................. 33

5.2 Link Layer Protocol ................................................................................................................... 33

5.2.1 Protocol Overview .............................................................................................................. 33

5.2.2 Link Symbol Set (LSS) ....................................................................................................... 33

5.2.3 Header for UHS-II Packet ................................................................................................... 34

5.2.4 Message Packet (MSG) ..................................................................................................... 35

5.2.4.1 Overview.................................................................................................................................. 35

5.2.4.2 CODE Definition for Each IDX ................................................................................................ 36

5.2.4.3 MSG Duplication ..................................................................................................................... 36

5.2.5 Error Identifier .................................................................................................................... 36

5.2.6 Framing Rules .................................................................................................................... 37

5.2.7 Symbol Encoding and Byte Ordering in 8b/10b .................................................................. 37

5.2.8 Physical Lane State Machine (PLSM) ................................................................................ 38

5.2.8.1 Overview.................................................................................................................................. 38

5.2.9 Data Link State Machine (DLSM) ....................................................................................... 39

5.2.9.1 Overview.................................................................................................................................. 39

6. Transaction Layer Specification ...................................................................................... 40

6.1 Transaction Layer Overview ..................................................................................................... 40

6.1.1 Packet Types and Format Overview ................................................................................... 41

6.2 Transaction Layer Protocol ....................................................................................................... 43

6.2.1 UHS-II I/O Space and Memory Address Space .................................................................. 43

6.2.2 Packet Format Details ........................................................................................................ 44

6.2.2.1 Header ..................................................................................................................................... 44

6.2.2.2 CCMD ...................................................................................................................................... 44

6.2.2.3 Broadcast CCMD .................................................................................................................... 47

6.2.2.4 DCMD ...................................................................................................................................... 48

6.2.2.5 RES (NACK = 0) ..................................................................................................................... 50

6.2.2.6 RES (NACK = 1) ..................................................................................................................... 53

6.2.2.7 DATA ........................................................................................................................................ 53

6.2.2.8 Operation of Reserved Bits in the Packet ............................................................................... 54

6.2.3 Supplements of UHS-II Initialization ................................................................................... 55

6.2.4 Transition to Dormant State ................................................................................................ 56

6.2.4.1 General .................................................................................................................................... 56

6.2.4.2 Hibernate Mode ....................................................................................................................... 57

6.2.4.2.1 Overview ........................................................................................................................... 57

6.2.5 Reset .................................................................................................................................. 57

6.2.6 Device Initialization Mechanism .......................................................................................... 58

6.2.6.1 General .................................................................................................................................... 58

6.2.7 Enumeration Mechanism .................................................................................................... 60

6.2.7.1 General .................................................................................................................................... 60

6.2.8 Configuration Mechanism ................................................................................................... 61

6.2.8.1 Basic Specification .................................................................................................................. 61

6.2.8.2 Determination of Block Length ................................................................................................ 61

6.2.8.3 Quick Configuration ................................................................................................................. 61

6.2.9 Configuration Register (CFG_REG) ................................................................................... 63

6.2.9.1 Register Map ........................................................................................................................... 63

6.2.9.2 CFG_REG Description ............................................................................................................ 64

6.2.9.2.1 Generic Capabilities Register ........................................................................................... 65

6.2.9.2.2 PHY Capabilities Register ................................................................................................ 66

6.2.9.2.3 LINK/TRAN Capabilities Register ..................................................................................... 67

v

�

UHS-II Simplified Addendum Version 1.02

©Copyright 2010-2018 SD Card Association

6.2.9.2.4 Generic Settings Register................................................................................................. 68

6.2.9.2.5 PHY Settings Register ...................................................................................................... 69

6.2.9.2.6 LINK/TRAN Settings Register .......................................................................................... 71

6.2.9.2.7 Preset Register ................................................................................................................. 71

6.2.10 Status Register (ST_REG) ............................................................................................... 72

6.2.10.1 Register Map ......................................................................................................................... 72

6.2.10.2 ST_REG Description ............................................................................................................. 72

6.2.10.2.1 Status in TRANS_ABORT Register................................................................................ 72

6.2.11 Interrupt Register (INT_REG) ........................................................................................... 74

6.2.11.1 Register Map ......................................................................................................................... 74

6.2.11.2 INT_REG Description ............................................................................................................ 74

6.2.11.2.1 INT Enable ...................................................................................................................... 74

6.2.11.2.2 INT Status ....................................................................................................................... 74

6.2.12 Command Register (CMD_REG)...................................................................................... 75

7. SD-TRAN Specification .................................................................................................... 76

7.1 SD-TRAN Overview .................................................................................................................. 76

7.1.1 Packet Types and Format Overview ................................................................................... 76

7.1.2 Registers for Legacy SD ..................................................................................................... 77

7.2 SD-TRAN Protocol.................................................................................................................... 77

7.2.1 Packet Format Details ........................................................................................................ 77

7.2.1.1 CCMD ...................................................................................................................................... 77

7.2.1.2 DCMD ...................................................................................................................................... 79

7.2.1.3 RES ......................................................................................................................................... 80

7.2.1.4 RES (NACK = 1) ..................................................................................................................... 82

7.2.1.5 DATA ........................................................................................................................................ 82

7.2.2 DATA Burst Framing Rules in SD-TRAN ............................................................................. 83

7.2.3 Interface Selection for UHS-II Card and Initialization .......................................................... 83

7.2.3.1 Overview.................................................................................................................................. 83

7.2.3.2 Interface Selection after Power Up ......................................................................................... 83

7.2.3.3 Interface Selection after FULL_RESET or GO_DORMANT_STATE...................................... 84

7.2.4 Transaction Control and Management State Machine ........................................................ 85

7.2.4.1 Card Identification Mode ......................................................................................................... 85

7.2.4.2 Data Transfer Mode ................................................................................................................ 87

8. 2L-HD Mode (optional) ...................................................................................................... 89

8.1 Overview .................................................................................................................................. 89

9. Additional Lanes Support (optional) ............................................................................... 90

9.1 Overview .................................................................................................................................. 90

Appendix A (Normative) : Reference ................................................................................... 91

A.1 Related Documentation ............................................................................................................ 91

Appendix B (Normative) : Special Terms ............................................................................ 92

B.1 Terminology .............................................................................................................................. 92

B.2 Abbreviations ............................................................................................................................ 93

Appendix C (Normative) : Test Condition of Measuring Output Signals ......................... 96

C.1 Test Condition for Host Output Signal at TP2 ........................................................................... 96

C.2 Test Condition for Card Output Signal at TP2 ........................................................................... 96

vi

�

UHS-II Simplified Addendum Version 1.02

Appendix D (Normative) : Register ..................................................................................... 98

D.1 Register Summary ................................................................................................................... 98

D.1.1 Register Types ................................................................................................................... 98

D.1.2 Register Initial Values ........................................................................................................ 98

©Copyright 2010-2018 SD Card Association

Appendix E (Informative) : Design Guide ........................................................................... 99

Appendix F (Informative) : PHY-LINK I/F .......................................................................... 100

Appendix G (Informative) : Host's Operation in Detecting Timeout ............................... 101

vii

�

2023年江西萍乡中考道德与法治真题及答案.doc

2023年江西萍乡中考道德与法治真题及答案.doc 2012年重庆南川中考生物真题及答案.doc

2012年重庆南川中考生物真题及答案.doc 2013年江西师范大学地理学综合及文艺理论基础考研真题.doc

2013年江西师范大学地理学综合及文艺理论基础考研真题.doc 2020年四川甘孜小升初语文真题及答案I卷.doc

2020年四川甘孜小升初语文真题及答案I卷.doc 2020年注册岩土工程师专业基础考试真题及答案.doc

2020年注册岩土工程师专业基础考试真题及答案.doc 2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc

2023-2024学年福建省厦门市九年级上学期数学月考试题及答案.doc 2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc

2021-2022学年辽宁省沈阳市大东区九年级上学期语文期末试题及答案.doc 2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc

2022-2023学年北京东城区初三第一学期物理期末试卷及答案.doc 2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc

2018上半年江西教师资格初中地理学科知识与教学能力真题及答案.doc 2012年河北国家公务员申论考试真题及答案-省级.doc

2012年河北国家公务员申论考试真题及答案-省级.doc 2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc

2020-2021学年江苏省扬州市江都区邵樊片九年级上学期数学第一次质量检测试题及答案.doc 2022下半年黑龙江教师资格证中学综合素质真题及答案.doc

2022下半年黑龙江教师资格证中学综合素质真题及答案.doc